SoC设计方法超深亚微米工艺下以时延、耦合效应、串扰为.pptx

- 格式:pptx

- 大小:297.33 KB

- 文档页数:58

超深亚微米SOC芯片的低功耗后端设计的开题报告一、选题背景和意义近年来,随着移动终端、物联网、云计算等技术的快速发展,计算机系统对功耗、性能和功能的要求变得越来越高。

尤其是在移动终端领域,用户对续航能力和低功耗的需求不断提升。

为了满足这些需求,SOC (System on Chip,片上系统)芯片的设计成为了必不可少的一环。

SOC芯片在细节方面有着诸多考虑,其中之一就是后端设计。

后端设计不仅决定了芯片的功耗、面积和时序性能,还会直接影响到芯片的设计周期和成本。

对于超深亚微米SOC芯片,更是需要考虑工艺、设备、信噪比等问题,这都将对后端设计带来更大的挑战。

因此,本文拟以超深亚微米SOC芯片的低功耗后端设计为研究方向,探索如何在后端设计中实现低功耗、高性能和低成本的平衡,以及如何有效地解决面对超深亚微米SOC芯片的各种问题。

二、研究内容和方法本文将以超深亚微米SOC芯片的低功耗后端设计作为研究内容,主要包括以下几个方面:1.低功耗逻辑综合:低功耗逻辑综合是实现超深亚微米SOC芯片低功耗的关键。

本文将研究低功耗逻辑综合的原理和实现方法,探索如何在保证逻辑功能正确的前提下,尽可能地降低功耗。

2.低功耗物理设计:低功耗物理设计是后端设计中一个重要的环节,它决定了芯片的面积和功耗。

本文将研究低功耗物理设计中的各种技术和算法,探索如何降低功耗、减小芯片面积和提高性能。

3.时序约束:在超深亚微米工艺下,时序约束会面临更大的挑战,因此本文将研究如何针对超深亚微米SOC芯片的工艺特点设计出合理的时序约束,保证芯片能够在各种复杂场景下正常运行。

4.DRC和LVS:DRC和LVS是后端设计中一项重要的检查工具,用于检查芯片设计是否符合工艺规则和逻辑规则。

本文将研究如何有效地使用DRC和LVS工具,规避后端设计中的各种缺陷。

本文将采用理论研究、仿真实验和工程实践相结合的方法进行研究。

通过对不同方法的对比与评估,力求找到最佳的方案,并运用到实际的超深亚微米SOC芯片设计中。

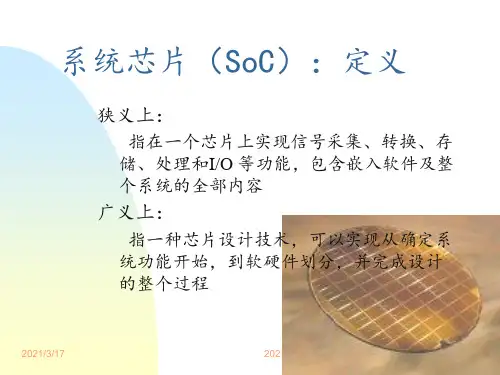

SOC设计方法本文通过对集成电路IC 技术发展现状的讨论和历史回顾,特别是通过对电子整机设计技术发展趋势的探讨,引入系统芯片(System on Chip,简称SOC)的定义,主要特点及其设计方法学等基本概念,并着重探讨面向SOC 的新一代集成电路设计方法学的主要研究内容和发展趋势。

关键词:引言人类进入21 世界面临的一个重要课题就是如何面对国民经济和社会发展信息化的挑战。

以网络通信、软件和微电子为主要标志的信息产业的飞速发展既为我们提供了一个前所未有的发展机遇”>SOC软硬件协同设计超深亚微米高层次综合IP 核设计再利用引言人类进入21 世界面临的一个重要课题就是如何面对国民经济和社会发展信息化的挑战。

以网络通信、软件和微电子为主要标志的信息产业的飞速发展既为我们提供了一个前所未有的发展机遇,集成电路作为电子工业乃至整个信息产业的基础得益于这一难得的机遇”>也营造了一个难得的市场与产业环境。

集成电路作为电子工业乃至整个信息产业的基础得益于这一难得的机遇,呈现出快速发展的态势。

以软硬件协同设计(Software/Hardware Co-Design)、具有知识产权的内核(IP 核)复用和超深亚微米(Very Deep Sub-M 集成电路ron, 简称VDSM)技术为支撑的SOC 是国际超大规模集成电路(VLSI)的发展趋势和新世纪集成电路的主流。

与此同时,集成电路设计技术的进步滞后于集成电路制造技术的进步已成为制约未来集成电路工业进一步健康发展的关键。

传统的、基于标准单元库的设计方法已被证明不能胜任SOC 的设计;现行的面向逻辑的集成电路设计方法在深亚微米集成电路设计中遇到了难以逾越的障碍;芯。