WCVD在集成电路中的应用

- 格式:doc

- 大小:107.50 KB

- 文档页数:3

WCVD在集成电路中的应用

wsx 发表于: 2005-9-01 15:21 来源: 半导体技术天地

作者:康健Applied Materials China

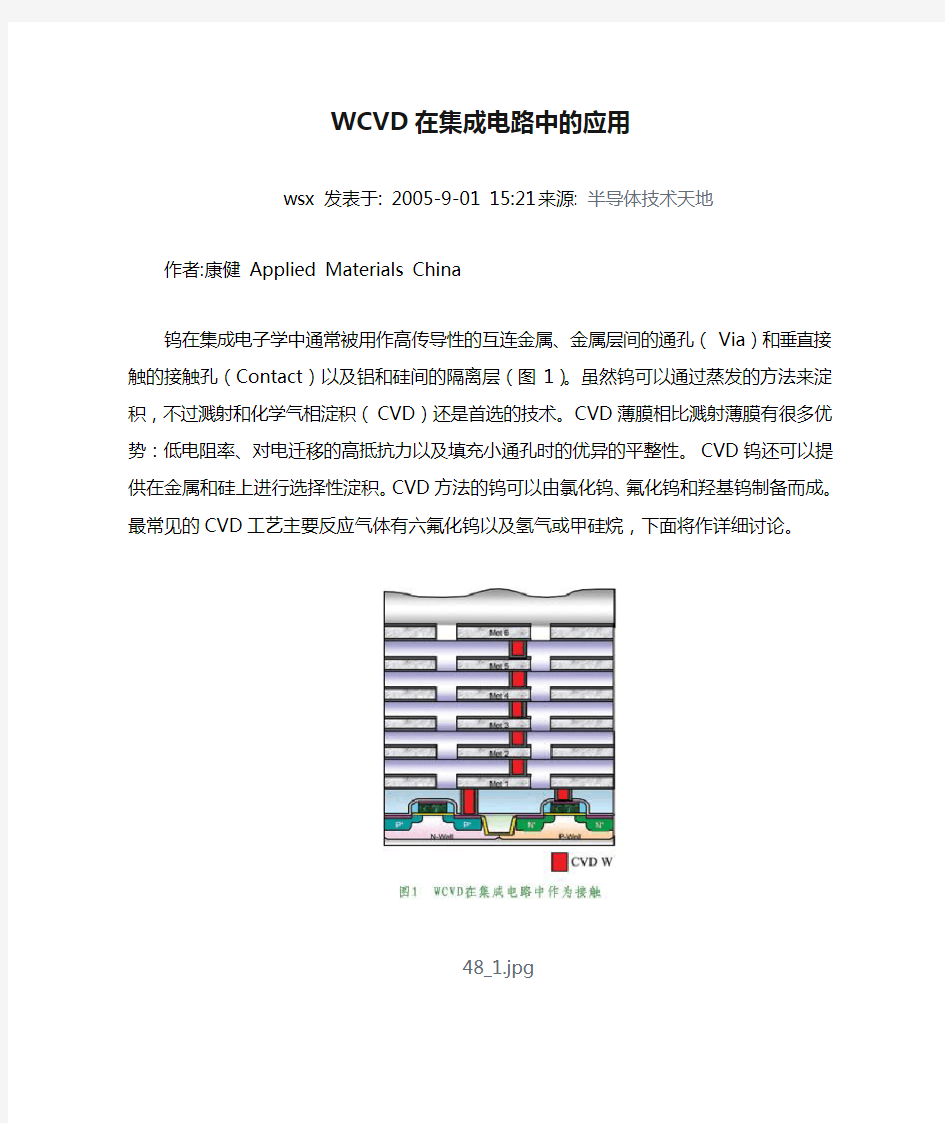

钨在集成电子学中通常被用作高传导性的互连金属、金属层间的通孔(Via)和垂直接触的接触孔(Contact)以及铝和硅间的隔离层(图1)。虽然钨可以通过蒸发的方法来淀积,不过溅射和化学气相淀积(CVD)还是首选的技术。CVD薄膜相比溅射薄膜有很多优势:低电阻率、对电迁移的高抵抗力以及填充小通孔时的优异的平整性。CVD钨还可以提供在金属和硅上进行选择性淀积。CVD方法的钨可以由氯化钨、氟化钨和羟基钨制备而成。最常见的CVD工艺主要反应气体有六氟化钨以及氢气或甲硅烷,下面将作详细讨论。

48_1.jpg

48_2.jpg

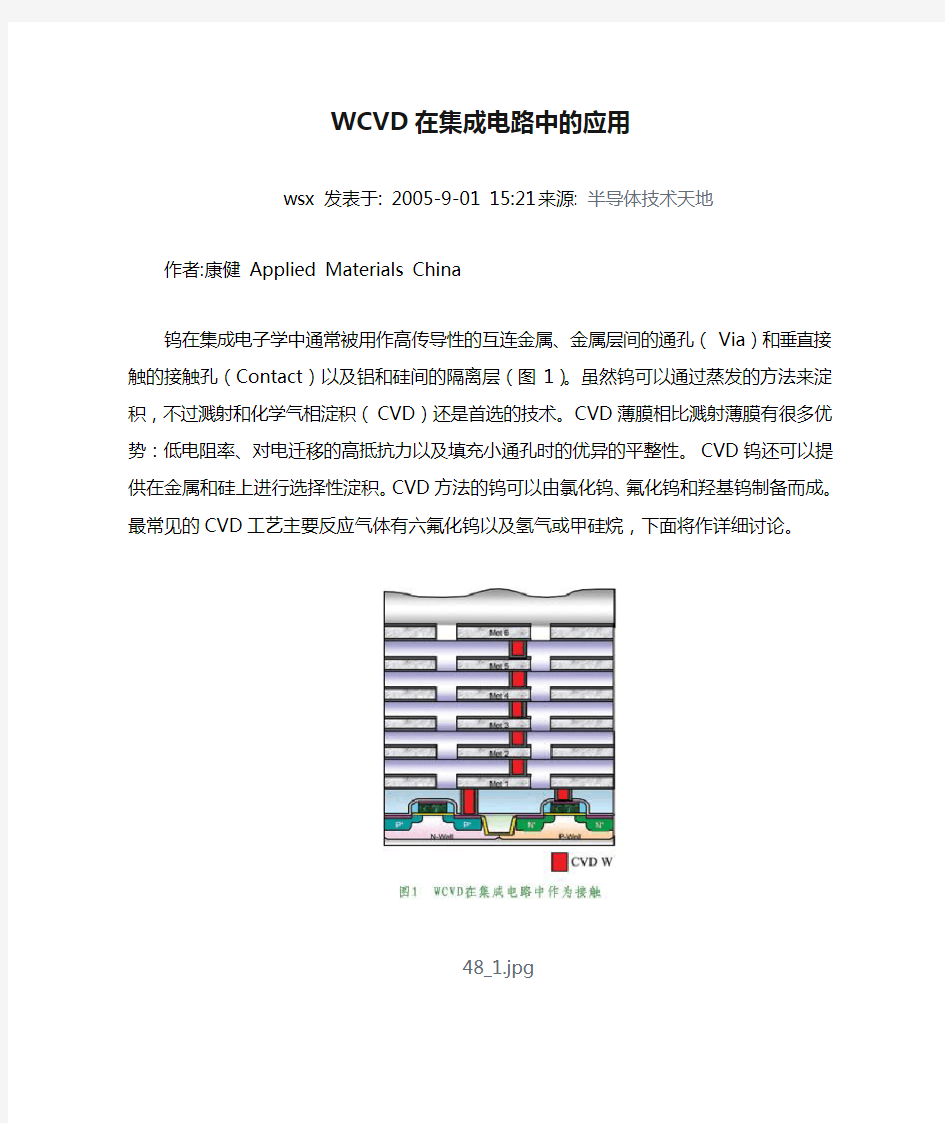

SiH4浸泡时的反应:SiH4 => W + H2

成核时:SiH4 + WF6 => W + SiH4 + HF

Si + WF6 => W + SiH4

大批淀积时:WF6 + H2 => W + HF

WCVD工艺一般由四个步骤组成:加热并用SiH4浸泡(Soak),成核(Nucleation),大批淀积(Bulk Deposition)和残余气清洗(Purge)。(图2)

因为WCVD受热激发或化学反应的限制,所以晶圆需要先充分加热为后续反应做准备。SiH4浸泡在一些技术文章中也被称作SiH4引发。在这一步中SiH4分解成Si和H2形成一薄层的无定形硅。

在成核这一步中,SiH4和氢气的混合气体与WF6源气体反应形成了一薄层钨,这一薄层钨作为后续钨层的生长点。成核层的均匀度和淀积速率取决于前期加热是否充分或预热时间是否足够长。通过增加反应压强,可以缩短预热时间。成核是整个淀积过程中非常关键的一步,并且对后续膜的均匀度和其他特征有强烈的影响。因为钨与氧化物粘着力不强并且WF6会和硅发生反应,所以在WCVD淀积之前必须先淀积一层粘着层和一层阻挡层,例如,Ti/TiN或TiW。Ti和氧化物有非常好的粘连性,并能够在源/漏区和硅反应形成TiSix,这样大大减小了接触电阻。而且,Ti一般通过物理气相方法(PVD)制取,标准PVD淀积的Ti的阶梯覆盖性能很差,而且会和WF6反应。因此,在接触孔或通孔上有必要在WCVD前淀积第二层TiN阻挡层。

这个粘着层/阻挡层使得钨能够完全地粘连在接触孔或通孔的氧化物上,并有效地防止WF6与硅衬底和氧化物发生反应。如果没有粘着层/阻挡层而钨淀积反应直接在硅上进行,WF6与下层的硅反应导致硅的消耗以及对衬底的侧向侵蚀。另外,形成的Wsix的电阻率相对TiSix也很高。目前,在工业界Ti/TiN是防止钨与硅衬底反应的最好阻挡,所以它是首选的粘着层/阻挡层。

因为WF6和H2反应的压强大,淀积速率高,所以大批淀积这一步生长的钨占整个反应钨量的90%以上。

清洗步骤是为了把未反应的气体和副产品清出反应腔,通常的方法是用大量Ar和N2充入反应腔借助真空泵抽走。

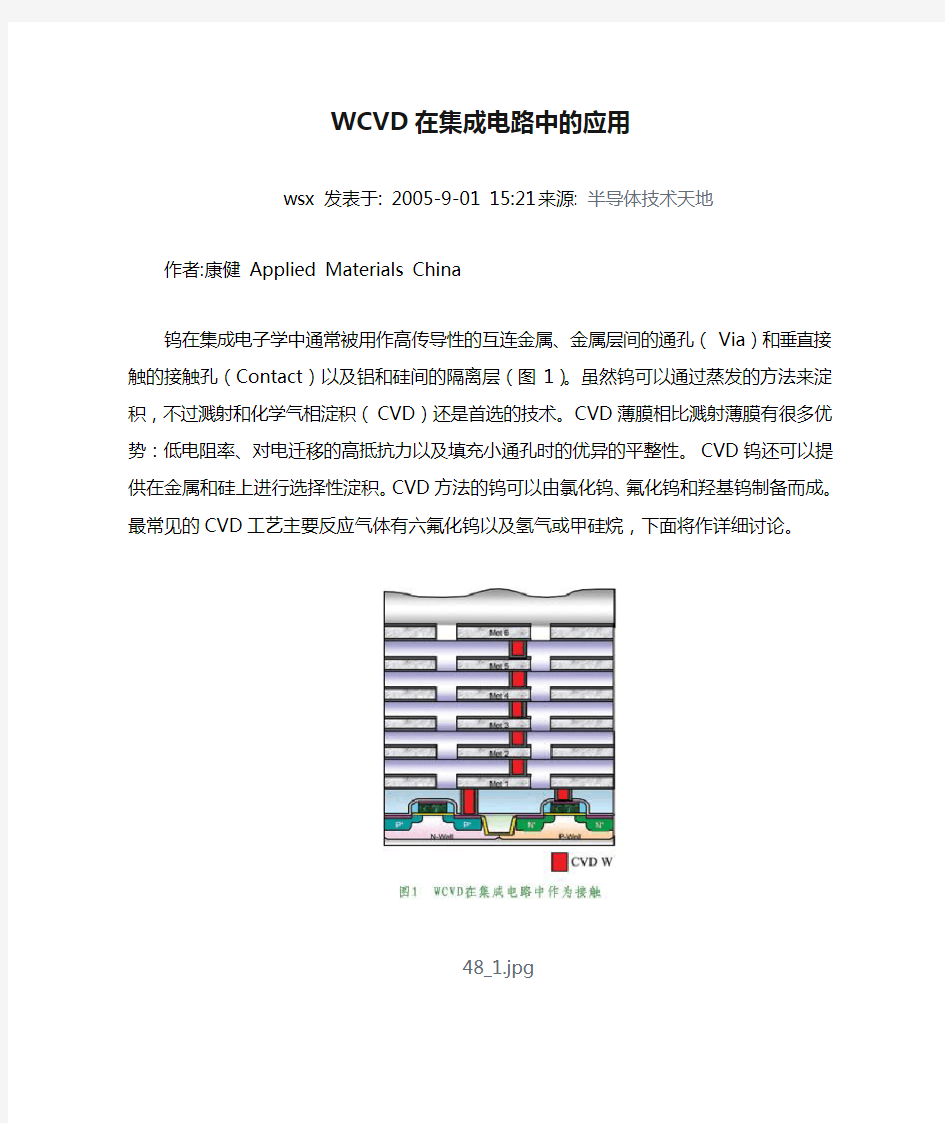

WCVD主要有两个问题:气相反应(GPR)和WF6腐蚀。(图3)GPR是因为在SiH4/WF6混合气体中SiH4比例很高,这使得SH4和WF6在未到达晶圆表面前就发生反应。这可以通过控制SiH4的比例来控制。当高浓度的WF6暴露在Ti/TiN堆叠膜上方时,如果TiN阻挡层不足于阻止WF6的扩散,WF6将会直接和Ti反应形成“火山”,这就是WF6腐蚀。

48_3.jpg

随着Cu工艺的发展,尤其是单镶嵌和双镶嵌流程的引入,在0.13微米及后续技术节点中,Cu由于其极低的电阻率在互联金属应用中取代了W。不过到目前为止,由于Cu的迁移问题以及在CMOS中的中毒效应,W仍然是接触应用中唯一的候选者。