ARM指令集详解(超详细!带实例!)

- 格式:doc

- 大小:122.00 KB

- 文档页数:24

![[转]ARM指令集详解[很好]](https://uimg.taocdn.com/65af3afc541810a6f524ccbff121dd36a32dc4e6.webp)

[转]ARM指令集详解[很好]1. 汇编1.1. 通⽤寄存器通⽤寄存器37个寄存器,31个通⽤寄存器,6个状态寄存器,R13堆栈指针sp,R14返回指针,R15为PC 指针, cpsr_c代表的是这32位中的低8位,也就是控制位CPSR有4个8位区域:标志域(F)、状态域(S)、扩展域(X)、控制域(C)MSR - Load specified fields of the CPSR or SPSR with an immediate constant, orfrom the contents of a general-purpose register. Syntax: MSR{cond} _, #immed_8rMSR{cond} _, Rm where: cond is an optional condition code. is either CPSR orSPSR. specifies the field or fields to be moved. can be one or more of: ccontrol field mask byte (PSR[7:0]) x extension field mask byte (PSR[15:8]) sstatus field mask byte (PSR[23:16) f flags field mask byte(PSR[31:24]).immed_8r is an expression evaluating to a numeric constant. The constant mustcorrespond to an 8-bit pattern rotated by an even number of bits within a32-bit word. Rm is the source register.C 控制域屏蔽字节(psr[7:0])X 扩展域屏蔽字节(psr[15:8])S 状态域屏蔽字节(psr[23:16])F 标志域屏蔽字节(psr[31:24])CPSR寄存器FIQ和IRQ的区别?MODE(以下为⼆进制)10000⽤户模式PC,CPSR,R0~R1410001FIQ PC,CPSR,SPSR_fiq,R14_fiq~R8_fiq,R7~R010010IRQ PC,CPSR,SPSR_irq,R14_irq~R13_irq,R12~R010011管理模式(svc)PC,CPSR,SPSR_svc,R14_svc~R13_svc,R12~R010111终⽌模式PC,CPSR,SPSR_abt,R14_abt~R13_abt,R12~R011011未定义PC,CPSR,SPSR_und,R14_und~R13_und,R2~R011111系统模式(sys)PC,CPSR,R14 ~R01.2. 指令格式1) 基本格式<opcode>{<cond>}{S} <Rd>,<Rn>{,<opcode2>}其中,<>内的项是必须的,{}内的项是可选的,如<opcode>是指令助记符,是必须的,⽽{<cond>}为指令执⾏条件,是可选的,如果不写则使⽤默认条件AL(⽆条件执⾏)。

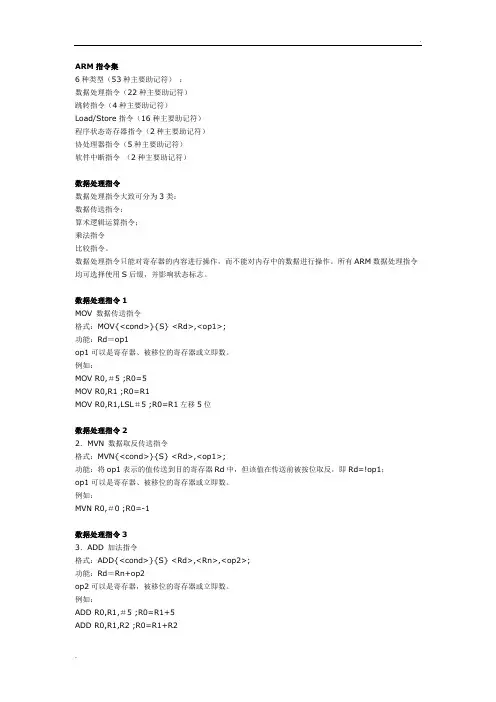

ARM指令集6种类型(53种主要助记符):数据处理指令(22种主要助记符)跳转指令(4种主要助记符)Load/Store指令(16种主要助记符)程序状态寄存器指令(2种主要助记符)协处理器指令(5种主要助记符)软件中断指令(2种主要助记符)数据处理指令数据处理指令大致可分为3类:数据传送指令;算术逻辑运算指令;乘法指令比较指令。

数据处理指令只能对寄存器的内容进行操作,而不能对内存中的数据进行操作。

所有ARM数据处理指令均可选择使用S后缀,并影响状态标志。

数据处理指令1MOV 数据传送指令格式:MOV{<cond>}{S} <Rd>,<op1>;功能:Rd=op1op1可以是寄存器、被移位的寄存器或立即数。

例如:MOV R0,#5 ;R0=5MOV R0,R1 ;R0=R1MOV R0,R1,LSL#5 ;R0=R1左移5位数据处理指令22.MVN 数据取反传送指令格式:MVN{<cond>}{S} <Rd>,<op1>;功能:将op1表示的值传送到目的寄存器Rd中,但该值在传送前被按位取反,即Rd=!op1;op1可以是寄存器、被移位的寄存器或立即数。

例如:MVN R0,#0 ;R0=-1数据处理指令33.ADD 加法指令格式:ADD{<cond>}{S} <Rd>,<Rn>,<op2>;功能:Rd=Rn+op2op2可以是寄存器,被移位的寄存器或立即数。

例如:ADD R0,R1,#5 ;R0=R1+5ADD R0,R1,R2 ;R0=R1+R2ADD R0,R1,R2,LSL#5 ;R0=R1+R2左移5位数据处理指令44.ADC 带进位加法指令格式:ADC{<cond>}{S} <Rd>,<Rn>,<op2>;功能:Rd=Rn+op2+carryop2可以是寄存器、被移位的寄存器或立即数;carry为进位标志值。

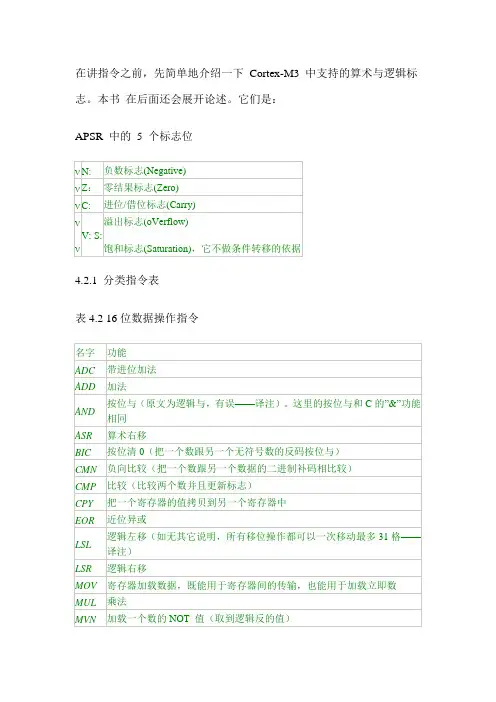

在讲指令之前,先简单地介绍一下Cortex-M3 中支持的算术与逻辑标志。

本书在后面还会展开论述。

它们是:APSR 中的5 个标志位4.2.1 分类指令表表4.2 16位数据操作指令表4.3 16位转移指令IT If-Then表4.4 16位存储器数据传送指令16 数据传送指令没有任何新内容,因为它们是Thumb 指令,在v4T 时就已经定格了——译注表4.5 其它16位指令表4.6 32位数据操作指令UXTH 半字被无符号扩展到32 位(高16 位清0——译注)表4.7 32位存储器数据传送指令表4.8 32位转移指令表4.9 其它32位指令4.2.2 未支持的指令有若干条Thumb 指令没有得到Cortex-M3 的支持,下表列出了未被支持的指令,以及不支持的原因。

表4.10 因为不再是传统的架构,导致有些指令已失去意义未支持的指令以前的功能BLX #im 在使用立即数做操作数时,BLX 总是要切入ARM 状态。

因为Cortex-M3 只在Thumb 态下运行,故以此指令为代表的,凡是试图切入ARM 态的操作,都将引发一个用法fault。

SETEND由ARMv6 引入的,在运行时改变处理器端设置的指令(大端或小端)。

因为Cortex-M3 不支持动态端的功能,所以此指令也将引发faultCM3 也不支持有少量在ARMv7-M 中列出的指令。

比如,ARMv7M 支持Thumb2 的协处理器指令,但是CM3 却不能挂协处理器。

表4.11 列出了这些与协处理器相关的指令。

如果试图执行它们,则将引发用法fault(NVIC 中的NOCP (No CoProcessor)标志置位)。

表4.11 不支持的协处理器相关指令未支持的指令以前的功能MCR 把通用寄存器的值传送到协处理器的寄存器中MCR2把通用寄存器的值传送到协处理器的寄存器中MCRR 把通用寄存器的值传送到协处理器的寄存器中,一次操作两个MRC把协处理器寄存器的值传送到通用寄存器中MRC2 把协处理器寄存器的值传送到通用寄存器中MRRC把协处理器寄存器的值传送到通用寄存器中,一次操作两个LDC 把某个连续地址空间中的一串数值传送至协处理器中STC从协处理器中传送一串数值到地址连续的一段地址空间中还有一个是改变处理器状态指令(CPS),它的一些用法也不再支持。

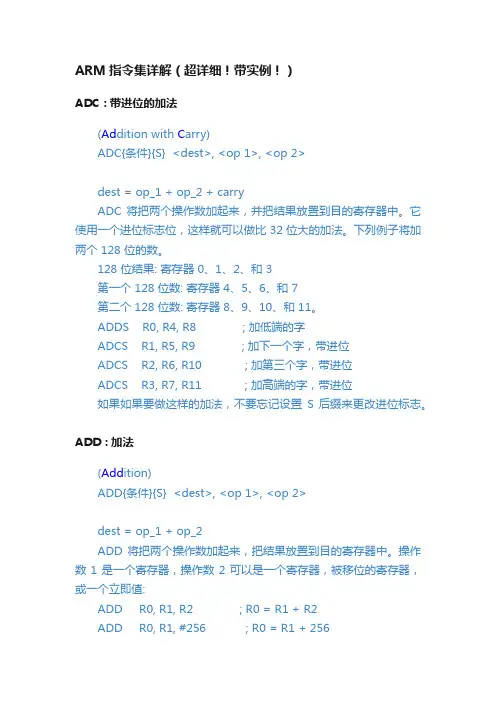

ARM指令集详解(超详细!带实例!)ADC : 带进位的加法(Ad dition with C arry)ADC{条件}{S} <dest>, <op 1>, <op 2>dest = op_1 + op_2 + carryADC 将把两个操作数加起来,并把结果放置到目的寄存器中。

它使用一个进位标志位,这样就可以做比 32 位大的加法。

下列例子将加两个 128 位的数。

128 位结果: 寄存器 0、1、2、和 3第一个 128 位数: 寄存器 4、5、6、和 7第二个 128 位数: 寄存器 8、9、10、和 11。

ADDS R0, R4, R8 ; 加低端的字ADCS R1, R5, R9 ; 加下一个字,带进位ADCS R2, R6, R10 ; 加第三个字,带进位ADCS R3, R7, R11 ; 加高端的字,带进位如果如果要做这样的加法,不要忘记设置S 后缀来更改进位标志。

ADD : 加法(Add ition)ADD{条件}{S} <dest>, <op 1>, <op 2>dest = op_1 + op_2ADD 将把两个操作数加起来,把结果放置到目的寄存器中。

操作数 1 是一个寄存器,操作数 2 可以是一个寄存器,被移位的寄存器,或一个立即值:ADD R0, R1, R2 ; R0 = R1 + R2ADD R0, R1, #256 ; R0 = R1 + 256ADD R0, R2, R3,LSL#1 ; R0 = R2 + (R3 << 1)加法可以在有符号和无符号数上进行。

AND : 逻辑与(logical AND)AND{条件}{S} <dest>, <op 1>, <op 2>dest = op_1 AND op_2AND 将在两个操作数上进行逻辑与,把结果放置到目的寄存器中;对屏蔽你要在上面工作的位很有用。

ARM指令集ARM(Advanced RISC Machines)是微处理器行业的一家知名企业。

设计了大量高性能、廉价、耗能低的RISC处理器、相关技术及软件。

1985年,第一个ARM原型在英国剑桥诞生。

ARM公司的特点是只设计芯片,而不生产。

ARM将其技术授权给世界上许多著名的半导体、软件和OEM厂商,每个厂商得到的都是一套独一无二的ARM相关技术及服务。

利用这种合伙关系,ARM很快成为许多全球性RISC标准的缔造者。

ARM公司定义了6种主要的指令集体系结构版本。

V1---V6。

ARMV1:该版本的原型机是ARM1,没有用于商业产品。

ARMV2:对V1版进行了扩展,包含了对32位结果的乘法指令和协处理器指令的支持。

ARMV3:ARM公司第一个微处理器ARM6核心是版本3的,它作为IP核、独立的处理器、具有片上高速缓存、MMU和写缓冲的集成CPU。

ARMV4:当前应用最广泛的ARM指令集版本。

ARM7TDMI、ARM720T、ARM9TDMI、ARM940T、ARM920T、Intel的StrongARM等是基于ARMv4T 版本。

ARMv5:ARM9E-S、ARM966E-S、ARM1020E、ARM 1022E以及XScale是ARMv5TE的。

ARM9EJ-S、ARM926EJ-S、ARM7EJ-S、ARM1026EJ-S是基于ARMv5EJ的。

ARM10也采用。

其中后缀意义如下:E:增强型DSP指令集。

包括全部算法和16位乘法操作。

J:支持新的Java。

ARMv6:采用ARMv6核的处理器是ARM11系列。

ARM1136J(F)-S基于ARMv6主要特性有SIMD、Thumb、Jazelle、DBX、(VFP)、MMU。

ARM1156T2(F)-S基于ARMv6T2 主要特性有SIMD、Thumb-2、(VFP)、MPU。

ARM1176JZ(F)-S基于ARMv6KZ 在ARM1136EJ(F)-S 基础上增加MMU、TrustZone。

ARM汇编指令集一、跳转指令跳转指令用于实现程序流程的跳转,在ARM程序中有两种方法可以实现程序流程的跳转:Ⅰ.使用专门的跳转指令。

Ⅱ.直接向程序计数器PC写入跳转地址值。

通过向程序计数器PC写入跳转地址值,可以实现在4GB的地址空间中的任意跳转,在跳转之前结合使用MOV LR,PC等类似指令,可以保存将来的返回地址值,从而实现在4GB连续的线性地址空间的子程序调用。

ARM指令集中的跳转指令可以完成从当前指令向前或向后的32MB的地址空间的跳转,包括以下4条指令:1、B指令B指令的格式为:B{条件} 目标地址B指令是最简单的跳转指令。

一旦遇到一个B 指令,ARM 处理器将立即跳转到给定的目标地址,从那里继续执行。

注意存储在跳转指令中的实际值是相对当前PC值的一个偏移量,而不是一个绝对地址,它的值由汇编器来计算(参考寻址方式中的相对寻址)。

它是24 位有符号数,左移两位后有符号扩展为32 位,表示的有效偏移为26 位(前后32MB的地址空间)。

以下指令:B Label ;程序无条件跳转到标号Label处执行CMP R1,#0 ;当CPSR寄存器中的Z条件码置位时,程序跳转到标号Label 处执行BEQ Label2、BL指令BL指令的格式为:BL{条件} 目标地址BL 是另一个跳转指令,但跳转之前,会在寄存器R14中保存PC的当前内容,因此,可以通过将R14 的内容重新加载到PC中,来返回到跳转指令之后的那个指令处执行。

该指令是实现子程序调用的一个基本但常用的手段。

以下指令:BL Label ;当程序无条件跳转到标号Label处执行时,同时将当前的PC值保存到R14中3、BLX指令BLX指令的格式为:BLX 目标地址BLX指令从ARM指令集跳转到指令中所指定的目标地址,并将处理器的工作状态有ARM 状态切换到Thumb状态,该指令同时将PC的当前内容保存到寄存器R14中。

因此,当子程序使用Thumb指令集,而调用者使用ARM指令集时,可以通过BLX指令实现子程序的调用和处理器工作状态的切换。

ARM指令集详解(超详细!带实例!)算术和逻辑指令ADC : 带进位的加法(Ad dition with C arry)ADC{条件}{S} <dest>, <op 1>, <op 2>dest = op_1 + op_2 + carryADC 将把两个操作数加起来,并把结果放置到⽬的寄存器中。

它使⽤⼀个进位标志位,这样就可以做⽐ 32 位⼤的加法。

下列例⼦将加两个 128 位的数。

128 位结果: 寄存器 0、1、2、和 3第⼀个 128 位数: 寄存器 4、5、6、和 7第⼆个 128 位数: 寄存器 8、9、10、和 11。

ADDS R0, R4, R8 ; 加低端的字ADCS R1, R5, R9 ; 加下⼀个字,带进位ADCS R2, R6, R10 ; 加第三个字,带进位ADCS R3, R7, R11 ; 加⾼端的字,带进位如果如果要做这样的加法,不要忘记设置 S 后缀来更改进位标志。

这两个指令与普通指令在对操作数的限制上有所不同:1. 给出的所有操作数、和⽬的寄存器必须为简单的寄存器。

2. 你不能对操作数 2 使⽤⽴即值或被移位的寄存器。

3. ⽬的寄存器和操作数 1 必须是不同的寄存器。

4. 最后,你不能指定 R15 为⽬的寄存器。

译注:CMP 和 CMP 是算术指令,TEQ 和 TST 是逻辑指令。

把它们归⼊⼀类的原因是它们的 S 位总是设置的,就是说,它们总是影响标志位。

CMN : ⽐较取负的值(C o m pare N egative)CMN{条件}{P} <op 1>, <op 2>status = op_1 - (- op_2)CMN 同于 CMP,但它允许你与⼩负值(操作数 2 的取负的值)进⾏⽐较,⽐如难于⽤其他⽅法实现的⽤于结束列表的 -1。

这样与 -1 ⽐较将使⽤:CMN R0, #1 ; 把 R0 与 -1 进⾏⽐较详情参照 CMP 指令。

ARM指令集讲解ARM指令和指令系统:指令是指示计算机某种操作的命令,指令的集合称为指令系统。

指令系统的功能强弱很大程度上决定了这类计算机智能的高低,它集中地反应了微处理器的硬件功能和属性。

ARM指令在机器中的表示格式是用32位的二进制数表示。

如ARM中有一条指令为ADDEQS R0,R1,#8;其二进制代码形式为:31~28 | 27~25 | 24~21 | 20 | 19~16 | 15~12 | 11~0 0000 | 001 | 0100 | 1 | 0001 | 0000 | 0000 0000 1000cond | opcode | Rn | Rd | Op2ARM指令格式一般如下:{}{s},{,}格式中< >的内容是必不可少的,{ }中的内容可忽略表示操作码。

如ADD表示算术加法{} 表示指令执行的条件域。

如EQ、NE等,缺省为AL。

{S} 决定指令的执行结果是否影响CPSR的值,使用该后缀则指令执行结果影响CPSR的值,否则不影响表示目的寄存器表示第一个操作数,为寄存器表示第二个操作数,可以是立即数。

寄存器和寄存器移位操作数ARM指令后缀:S、!S后缀:指令中使用S后缀时,指令执行后程序状态寄存器的条件标志位将被刷新,不使用S后缀时,指令执行后程序状态寄存器的条件标志将不会发生变化。

S后缀常用于对条件进行测试,如是否有溢出,是否进位等,根据这些变化,就可以进行一些判断,如是否大于,相等,从而影响指令执行的顺序。

!后缀:如果指令地址表达式中不含!后缀,则基址寄存器中的地址值不会发生变化。

加上此后缀后,基址寄存器中的值(指令执行后)= 指令执行前的值+ 地址偏移量(1)!后缀必须紧跟在地址表达式后面,而地址表达式要有明确的地址偏移量(2)!后缀不能用于R15(PC)的后面(3)当用在单个地址寄存器后面时,必须确信这个寄存器有隐性的偏移量,例如“STMDB R1!,{R3,R5,R7}”。

算术和逻辑指令ADC : 带进位的加法(Ad dition with C arry)ADC{条件}{S} <dest>, <op 1>, <op 2>dest = op_1 + op_2 + carryADC将把两个操作数加起来,并把结果放置到目的寄存器中。

它使用一个进位标志位,这样就可以做比32 位大的加法。

下列例子将加两个128 位的数。

128 位结果: 寄存器0、1、2、和3第一个128 位数: 寄存器4、5、6、和7第二个128 位数: 寄存器8、9、10、和11。

ADDS R0, R4, R8 ; 加低端的字ADCS R1, R5, R9 ; 加下一个字,带进位ADCS R2, R6, R10 ; 加第三个字,带进位ADCS R3, R7, R11 ; 加高端的字,带进位如果如果要做这样的加法,不要忘记设置S 后缀来更改进位标志。

ADD : 加法(Add ition)ADD{条件}{S} <dest>, <op 1>, <op 2>dest = op_1 + op_2ADD将把两个操作数加起来,把结果放置到目的寄存器中。

操作数 1 是一个寄存器,操作数2 可以是一个寄存器,被移位的寄存器,或一个立即值:ADD R0, R1, R2 ; R0 = R1 + R2ADD R0, R1, #256 ; R0 = R1 + 256ADD R0, R2, R3,LSL#1 ; R0 = R2 + (R3 << 1)加法可以在有符号和无符号数上进行。

AND : 逻辑与(logical AND)AND{条件}{S} <dest>, <op 1>, <op 2>dest = op_1 AND op_2AND将在两个操作数上进行逻辑与,把结果放置到目的寄存器中;对屏蔽你要在上面工作的位很有用。

操作数1 是一个寄存器,操作数2 可以是一个寄存器,被移位的寄存器,或一个立即值:AND R0, R0, #3 ; R0 = 保持 R0 的位0和 1,丢弃其余的位。

AND 的真值表(二者都是1 则结果为1):Op_1 Op_2 结果0 0 00 1 01 0 01 1 1BIC : 位清除(Bi t C lear)BIC{条件}{S} <dest>, <op 1>, <op 2>dest = op_1 AND (!op_2)BIC是在一个字中清除位的一种方法,与OR 位设置是相反的操作。

操作数2 是一个32 位位掩码(mask)。

如果如果在掩码中设置了某一位,则清除这一位。

未设置的掩码位指示此位保持不变。

BIC R0, R0, #%1011 ; 清除 R0 中的位 0、1、和 3。

保持其余的不变。

BIC 真值表:Op_1 Op_2 结果0 0 00 1 01 0 11 1 0译注:逻辑表达式为 Op_1 AND NOT Op_2EOR : 逻辑异或(logical E xclusive OR)EOR{条件}{S} <dest>, <op 1>, <op 2>dest = op_1 EOR op_2EOR将在两个操作数上进行逻辑异或,把结果放置到目的寄存器中;对反转特定的位有用。

操作数1 是一个寄存器,操作数2 可以是一个寄存器,被移位的寄存器,或一个立即值:EOR R0, R0, #3 ; 反转 R0 中的位 0 和 1EOR 真值表(二者不同则结果为1):Op_1 Op_2 结果0 0 00 1 11 0 11 1 0MOV : 传送(Mov e)MOV{条件}{S} <dest>, <op 1>dest = op_1MOV从另一个寄存器、被移位的寄存器、或一个立即值装载一个值到目的寄存器。

你可以指定相同的寄存器来实现NOP 指令的效果,你还可以专门移位一个寄存器:MOV R0, R0 ; R0 = R0... NOP 指令MOV R0, R0, LSL#3 ; R0 = R0 * 8如果R15 是目的寄存器,将修改程序计数器或标志。

这用于返回到调用代码,方法是把连接寄存器的内容传送到R15:MOV PC, R14 ; 退出到调用者MOVS PC, R14 ; 退出到调用者并恢复标志位(不遵从 32-bit 体系)MVN : 传送取反的值(M o v e N egative)MVN{条件}{S} <dest>, <op 1>dest = !op_1MVN从另一个寄存器、被移位的寄存器、或一个立即值装载一个值到目的寄存器。

不同之处是在传送之前位被反转了,所以把一个被取反的值传送到一个寄存器中。

这是逻辑非操作而不是算术操作,这个取反的值加1 才是它的取负的值:MVN R0, #4 ; R0 = -5MVN R0, #0 ; R0 = -1ORR : 逻辑或(logical OR)ORR{条件}{S} <dest>, <op 1>, <op 2>dest = op_1 OR op_2OR将在两个操作数上进行逻辑或,把结果放置到目的寄存器中;对设置特定的位有用。

操作数1 是一个寄存器,操作数2 可以是一个寄存器,被移位的寄存器,或一个立即值:ORR R0, R0, #3 ; 设置 R0 中位 0 和 1OR 真值表(二者中存在1 则结果为1):Op_1 Op_2 结果0 0 00 1 11 0 11 1 1RSB : 反向减法(R everse S u b traction)RSB{条件}{S} <dest>, <op 1>, <op 2>dest = op_2 - op_1SUB用操作数two 减去操作数one,把结果放置到目的寄存器中。

操作数1 是一个寄存器,操作数2 可以是一个寄存器,被移位的寄存器,或一个立即值:RSB R0, R1, R2 ; R0 = R2 - R1RSB R0, R1, #256 ; R0 = 256 - R1RSB R0, R2, R3,LSL#1 ; R0 = (R3 << 1) - R2反向减法可以在有符号或无符号数上进行。

RSC : 带借位的反向减法(R everse S ubtraction with C arry)RSC{条件}{S} <dest>, <op 1>, <op 2>dest = op_2 - op_1 - !carry同于SBC,但倒换了两个操作数的前后位置。

SBC : 带借位的减法(S u b traction with C arry)SBC{条件}{S} <dest>, <op 1>, <op 2>dest = op_1 - op_2 - !carrySBC做两个操作数的减法,把结果放置到目的寄存器中。

它使用进位标志来表示借位,这样就可以做大于32 位的减法。

SUB和SBC生成进位标志的方式不同于常规,如果需要借位则清除进位标志。

所以,指令要对进位标志进行一个非操作- 在指令执行期间自动的反转此位。

SUB : 减法(Sub traction)SUB{条件}{S} <dest>, <op 1>, <op 2>dest = op_1 - op_2SUB用操作数one 减去操作数 two,把结果放置到目的寄存器中。

操作数1 是一个寄存器,操作数2 可以是一个寄存器,被移位的寄存器,或一个立即值:SUB R0, R1, R2 ; R0 = R1 - R2SUB R0, R1, #256 ; R0 = R1 - 256SUB R0, R2, R3,LSL#1 ; R0 = R2 - (R3 << 1)减法可以在有符号和无符号数上进行。

移位指令ARM 处理器组建了可以与数据处理指令(ADC、ADD、AND、BIC、CMN、CMP、EOR、MOV、MVN、ORR、RSB、SBC、SUB、TEQ、TST)一起使用的桶式移位器(barrel shifter)。

你还可以使用桶式移位器影响在LDR/STR 操作中的变址值。

译注:移位操作在ARM 指令集中不作为单独的指令使用,它是指令格式中是一个字段,在汇编语言中表示为指令中的选项。

如果数据处理指令的第二个操作数或者单一数据传送指令中的变址是寄存器,则可以对它进行各种移位操作。

如果数据处理指令的第二个操作数是立即值,在指令中用8 位立即值和4 位循环移位来表示它,所以对大于255 的立即值,汇编器尝试通过在指令中设置循环移位数量来表示它,如果不能表示则生成一个错误。

在逻辑类指令中,逻辑运算指令由指令中S 位的设置或清除来确定是否影响进位标志,而比较指令的S 位总是设置的。

在单一数据传送指令中指定移位的数量只能用立即值而不能用寄存器。

下面是给不同的移位类型的六个助记符:LSL 逻辑左移ASL 算术左移LSR 逻辑右移ASR 算术右移ROR 循环右移RRX 带扩展的循环右移ASL和LSL是等同的,可以自由互换。

你可以用一个立即值(从0 到31)指定移位数量,或用包含在0 和31 之间的一个值的寄存器指定移位数量。

逻辑或算术左移(L ogical or A rithmetic S hift L eft)Rx, LSL #n orRx, ASL #n orRx, LSL Rn orRx, ASL Rn接受Rx 的内容并按用‘n’或在寄存器Rn 中指定的数量向高有效位方向移位。

最低有效位用零来填充。

除了概念上的第33 位(就是被移出的最小的那位)之外丢弃移出最左端的高位,如果逻辑类指令中S 位被设置了,则此位将成为从桶式移位器退出时进位标志的值。

考虑下列:MOV R1, #12MOV R0, R1, LSL#2在退出时,R0 是48。

这些指令形成的总和是R0 = #12, LSL#2等同于BASIC 的R0 = 12 << 2逻辑右移(L ogical S hift R ight)Rx, LSR #n orRx, LSR Rn它在概念上与左移相对。

把所有位向更低有效位方向移动。

如果逻辑类指令中S 位被设置了,则把最后被移出最右端的那位放置到进位标志中。

它同于BASIC 的register = value >>> shift。

算术右移(A rithmetic S hift R ight)Rx, ASR #n orRx, ASR Rn类似于LSR,但使用要被移位的寄存器(Rx)的第31 位的值来填充高位,用来保护补码表示中的符号。