封装标准JEDEC标准

- 格式:doc

- 大小:119.00 KB

- 文档页数:6

jesd标准JESD标准。

JESD标准是指由美国电子工业协会(JEDEC)制定的一系列关于集成电路(IC)封装和封装材料的标准。

这些标准对于确保IC产品的质量、可靠性和互操作性至关重要,因此在整个电子行业中具有重要的地位。

首先,JESD标准涵盖了封装材料的物理和化学特性。

这些特性包括热稳定性、机械强度、导热性能等。

通过规定这些特性的测试方法和标准数值,JESD标准确保了封装材料的质量和稳定性,从而保障了IC产品的可靠性。

其次,JESD标准还规定了IC封装的设计和制造要求。

这些要求涵盖了封装的尺寸、引脚排布、焊接工艺等方面。

通过遵循这些标准,IC制造商可以确保其产品在不同设备上的互操作性,从而提高了整个电子系统的稳定性和可靠性。

此外,JESD标准还包括了关于封装材料和封装工艺的环境友好性要求。

这些要求主要涉及到封装材料的有害物质限制、回收利用要求等。

通过遵循这些环保要求,IC制造商可以降低其产品对环境的影响,符合国际环保标准,同时也提升了企业的社会责任形象。

总的来说,JESD标准在整个电子行业中具有重要的意义。

它不仅保障了IC产品的质量和可靠性,同时也促进了电子行业的可持续发展。

因此,作为电子工程师和IC制造商,我们都应当深入了解JESD标准,并严格遵循这些标准,以确保我们的产品在市场上获得更多的认可和信任。

在实际应用中,我们需要密切关注JESD标准的更新和变化,及时调整我们的生产工艺和材料选择,以适应市场和行业的变化。

同时,我们也应当积极参与JESD标准的制定和修订工作,为整个行业的发展贡献自己的力量。

总之,JESD标准是电子行业中不可或缺的一部分,我们应当充分认识到其重要性,并在日常工作中严格遵循这些标准,以推动整个行业朝着更加可靠、环保和可持续的方向发展。

半导体封装根据不同的用途,半导体的封装可以分为多种类型。

半导体的封装标准包括 JEDEC 和JEITA 标准,但有许多来自不同半导体制造商的封装不属于上述标准。

另外,JEDEC 和JEITA 这两种标准的名称也并非总是被用于制造商的产品目录和数据表中,除此以外,不同制造商之间的描述系统也不统一。

本页提供关于以下半导体封装描述规则的基本信息。

• 对那些明显具有相同封装的产品必须尽可能提供统一的一般性描述;如DIL →DIP 等。

• 如果制造商无法使用通用的名称,或者如果封装类型是众所周知的情况,则可使用制造商的描述;如PENTAWATT 等。

•作为一般性规则,必须在封装描述之后加上标有指示针脚数量的数字;如DIP24、SOT23-5等。

注:本页中所提供的信息仅供参考。

请在使用前确认制造商数据表中的所有数据。

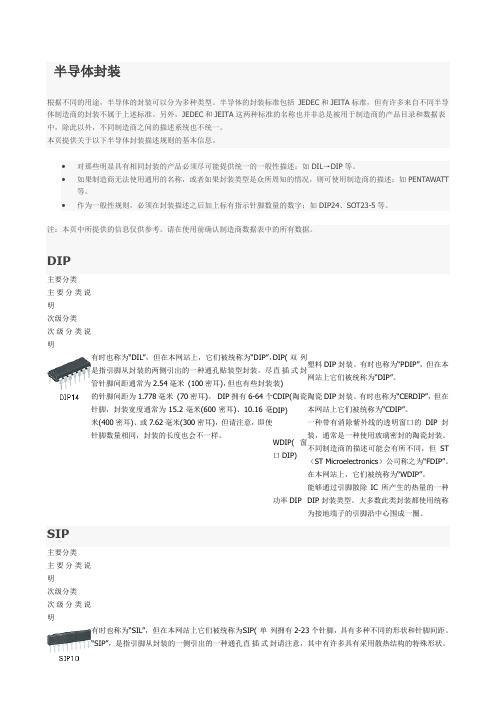

DIP主要分类 主要分类说明 次级分类 次级分类说明有时也称为“DIL”,但在本网站上,它们被统称为“DIP”,是指引脚从封装的两侧引出的一种通孔贴装型封装。

尽管针脚间距通常为2.54毫米 (100密耳),但也有些封装的针脚间距为1.778毫米 (70密耳)。

DIP 拥有6-64个针脚,封装宽度通常为15.2毫米(600密耳)、10.16毫米(400密耳)、或7.62毫米(300密耳),但请注意,即使针脚数量相同,封装的长度也会不一样。

DIP(双列直插式封装) 塑料DIP 封装。

有时也称为“PDIP”,但在本网站上它们被统称为“DIP”。

CDIP(陶瓷DIP) 陶瓷DIP 封装。

有时也称为“CERDIP”,但在本网站上它们被统称为“CDIP”。

WDIP(窗口DIP)一种带有消除紫外线的透明窗口的DIP 封装,通常是一种使用玻璃密封的陶瓷封装。

不同制造商的描述可能会有所不同,但ST (ST Microelectronics )公司称之为“FDIP”。

在本网站上,它们被统称为“WDIP”。

功率DIP 能够通过引脚散除IC 所产生的热量的一种DIP 封装类型。

IPC-JEDEC 9704标准简介1. IPC-JEDEC 9704标准是什么?IPC-JEDEC 9704标准是一项由IPC和JEDEC联合制定的关于电子设备可靠性测试的标准。

它是为了评估电子产品在实际使用过程中的可靠性和耐久性而制定的。

2. IPC-JEDEC 9704标准的内容IPC-JEDEC 9704标准包括了对电子设备可靠性测试的各个方面的要求,包括测试的流程、测试的方法、测试的标准、测试的环境等方面的要求。

它对于不同类型的电子产品都有相应的测试要求,包括芯片、电路板、连接器、封装等。

3. IPC-JEDEC 9704标准的重要性电子产品在使用过程中需要经受各种复杂的环境和条件,例如温度、湿度、振动、冲击等,而IPC-JEDEC 9704标准的制定正是为了保证电子产品在这些条件下的可靠性和耐久性。

它对于提高电子产品的质量、减少产品故障率、提升产品竞争力具有重要意义。

4. IPC-JEDEC 9704标准的适用范围IPC-JEDEC 9704标准适用于各种类型的电子产品,包括但不限于移动通信设备、智能家居设备、汽车电子设备、工业控制设备等。

不同类型的电子产品可能有不同的测试要求,但IPC-JEDEC 9704标准给出了统一的框架和要求。

5. IPC-JEDEC 9704标准的意义IPC-JEDEC 9704标准的制定为电子产品的设计、生产、测试提供了具体的指导,使得电子产品可以更好地适应复杂的使用环境。

它也为电子产品的质量管理、质量检验提供了依据,为用户提供了可靠的保障。

6. 总结IPC-JEDEC 9704标准的制定是为了保证电子产品在实际使用过程中的可靠性和耐久性,它对于电子产品的设计、生产、测试具有重要意义。

通过遵守IPC-JEDEC 9704标准,可以提高电子产品的质量,减少产品故障率,提升产品竞争力。

IPC-JEDEC 9704标准的适用范围广泛,为各种类型的电子产品提供了统一的测试要求和标准,对电子产品行业的发展起到了积极的推动作用。

jedec标准测试JEDEC标准测试。

JEDEC标准测试是指由半导体行业标准化组织JEDEC制定的一系列测试标准,旨在确保半导体器件的质量和性能达到一定的标准要求。

这些测试标准涵盖了从材料、工艺到器件性能的各个方面,对半导体行业具有重要的指导意义。

本文将对JEDEC标准测试进行详细介绍,以便读者对其有更深入的了解。

首先,JEDEC标准测试涵盖了半导体器件的多个方面。

其中包括器件的静态和动态电特性测试、热特性测试、可靠性测试、封装测试等。

这些测试项目涵盖了半导体器件的各个关键性能指标,如电压、电流、功耗、温度、可靠性等。

通过这些测试,可以全面评估半导体器件的性能和可靠性,为其在实际应用中提供参考依据。

其次,JEDEC标准测试对于半导体行业具有重要的指导意义。

由于半导体器件的应用领域广泛,要求的性能和可靠性也很高,因此对其进行全面的测试是非常必要的。

JEDEC标准测试作为行业内的权威标准,为半导体器件的设计、制造、测试提供了统一的规范,有利于提高产品的质量和性能,推动整个行业的发展。

再次,JEDEC标准测试的实施对于企业具有重要的意义。

在实际生产中,企业需要遵循JEDEC标准测试的要求,对半导体器件进行全面的测试和验证。

这不仅有助于确保产品的质量和性能达到标准要求,还有助于提高产品的市场竞争力,赢得客户的信赖。

因此,企业应当重视JEDEC标准测试的实施,将其作为提升产品质量和技术水平的重要手段。

最后,JEDEC标准测试的不断完善和更新对于行业发展具有积极的促进作用。

随着半导体技术的不断进步和应用领域的不断拓展,对器件性能和可靠性的要求也在不断提高。

因此,JEDEC标准测试需要不断进行更新和完善,以适应行业的发展需求。

只有如此,才能更好地推动半导体行业的发展,为社会和经济发展做出更大的贡献。

综上所述,JEDEC标准测试是半导体行业不可或缺的一部分,对于确保器件质量和性能具有重要的意义。

通过全面的测试和验证,可以有效提高产品的质量和可靠性,推动整个行业的发展。

芯片焊接强度测试标准

芯片焊接强度测试标准通常是指用于评估芯片封装焊接强度的一组规范和方法。

以下是一些常见的芯片焊接强度测试标准:

1.IPC/JEDEC Joint Electron Device Engineering Council(IPC/JEDEC):IPC/JEDEC是一个由电子工业协会联合组成的组织,其发布的标准涵盖了电子元件的各个方面,包括芯片封装焊接强度测试标准。

IPC/JEDEC发布的焊接强度测试标准包括

J-STD-001F、J-STD-002A、J-STD-003等。

2.AEC-Q100:AEC-Q100是汽车电子委员会发布的一组可靠性测试标准,其中包括焊接强度测试标准。

AEC-Q100焊接强度测试标准主要针对汽车电子元件的封装焊接强度进行测试。

-STD-883K Method 1016:MIL-STD-883K Method 1016是美国国防部发布的一项测试标准,其中包括焊接强度测试方法。

MIL-STD-883K Method 1016焊接强度测试方法主要用于评估芯片封装焊接强度。

以上是一些常见的芯片焊接强度测试标准。

不同的标准可能会有不同的测试方法和要求,因此在进行芯片焊接强度测试时,需要根据具体的标准要求进行测试。

jesd标准JESD标准。

JESD标准是指由半导体行业协会(JEDEC)制定的一系列关于集成电路封装和封装材料的标准。

这些标准涵盖了从封装材料的物理特性到封装工艺的规范,对于半导体行业的发展起着至关重要的作用。

首先,JESD标准对于封装材料的物理特性进行了详细的规定。

这些物理特性包括材料的热稳定性、机械强度、导热性等,这些特性的规范对于确保封装材料的质量和可靠性至关重要。

通过JESD标准规定的物理特性,半导体行业可以选择更加适合自己产品的封装材料,从而提高产品的性能和可靠性。

其次,JESD标准还对封装工艺进行了严格的规范。

这些规范涵盖了从封装设计到封装过程中的各个环节,确保了封装工艺的稳定性和可靠性。

通过遵循JESD标准,半导体厂商可以更加准确地控制封装工艺,提高产品的一致性和可靠性。

除此之外,JESD标准还对封装材料和封装工艺进行了严格的测试方法的规定。

这些测试方法包括了各种物理特性的测试方法和封装工艺的测试方法,确保了产品在各种环境下的可靠性和稳定性。

通过JESD标准规定的测试方法,半导体厂商可以更加准确地评估产品的性能和可靠性,为产品的研发和生产提供了重要的依据。

总的来说,JESD标准对于半导体行业的发展起着非常重要的作用。

通过JESD标准的规范,半导体厂商可以更加准确地选择封装材料、控制封装工艺,提高产品的性能和可靠性。

同时,JESD标准也为半导体行业的技术创新提供了重要的依据和支持,推动了整个行业的发展。

总之,JESD标准是半导体行业不可或缺的重要标准,它的制定和执行对于行业的发展起着至关重要的作用。

希望未来JESD标准能够不断完善和更新,为半导体行业的发展提供更加有力的支持和保障。

半导体元器件检测标准

半导体元器件检测标准是指针对半导体元器件进行质量检测和性

能测试的相关规范和要求。

以下是常见的半导体元器件检测标准:

1. MIL-STD-883:美国部队电子工程院(DOD)制定的军事标准,用于对半导体元器件进行可靠性测试和可靠性评估。

2. JEDEC标准:由半导体行业标准化组织JEDEC制定的标准,包括对

芯片、封装和测试的各个环节进行规范。

3. ISO 9001:国际质量管理体系标准,也适用于半导体元器件制造商。

该标准要求建立完善的质量管理体系,包括质量计划、质量控制、质

量改进等方面。

4. IPC标准:由国际电子工业协会(IPC)制定的标准,包括对印刷电路板、封装和组装过程的各个环节进行规范,也适用于半导体元器件

的制造和测试。

5. JESD47:由JEDEC制定的标准,用于对半导体器件在高温环境下的

性能进行测试和评估。

6. AEC-Q101:由美国汽车工程师协会(SAE)制定的汽车电子元器件

可靠性测试和评估的标准。

这些标准适用于汽车用途的半导体元器件。

7. GB/T标准:中国国家标准化管理委员会制定的标准,包括了对半导体元器件的质量、性能和可靠性等方面进行规范和要求。

以上标准只是常见的一些,具体的半导体元器件检测标准还需根

据具体产品和应用场景进行选择和遵守。

jedec 标准

JEDEC(Joint Electron Device Engineering Council)是一个由美国电子工程师协会和国际电子工程师协会组成的行业协会,专注于发展电子设备标准和规范。

它是全球最大的半导体行业协会,致力于制定、发布和维护全球最新的电子设备标准和规范,以提高电子设备的效率和可靠性。

JEDEC的标准可以分为三大类:一是元件标准,专注于半导体器件,包括存储器、芯片组、数字、模拟、微控制器和晶体管;二是接口和封装标准,专注于封装和接口类型,包括电源接口、传感器接口、电磁兼容性、模拟信号接口、数据传输接口和电路板封装;第三是测试标准,主要关心半导体部件的测试和评估,包括测试程序、测试方法和测试设备。

JEDEC的标准在全球范围内获得了广泛的接受和应用,是全球半导体行业的核心标准,在推动半导体技术发展和改善电子设备的可靠性方面发挥着至关重要的作用。

JEDEC的标准不仅影响了半导体行业的发展,也影响了其他行业,例如计算机、消费电子产品和汽车电子设备等行业,其影响力已遍布全球各地。

此外,PC100是由JEDEC和英特尔共同制订的一个SDRAM内存条的标准,符合该标准的内存都称为PC100,其中的100代表该内存工作频率可达

100MHz。

如需更多关于“JEDEC标准”的信息,建议访问JEDEC官网或咨询专业技

术人员。

jedec标准中文版JEDEC标准中文版。

JEDEC标准是一系列关于半导体集成电路和微电子器件的行业标准,由美国电子元件工业协会(JEDEC)制定和发布。

这些标准对于半导体行业的发展和规范起着至关重要的作用,也为全球半导体行业的技术和产品提供了统一的标准和规范。

本文将对JEDEC标准的中文版进行介绍和解读,以便更好地理解和应用这些标准。

首先,JEDEC标准中文版涵盖了多个方面的内容,包括但不限于半导体器件的封装、测试、质量和可靠性标准,以及半导体生产和设计的相关规范。

这些标准的制定经过了严格的技术讨论和实践验证,确保了其科学性和实用性。

通过遵循JEDEC标准,半导体行业可以实现产品的互操作性和互换性,提高生产效率和产品质量。

其次,JEDEC标准中文版对于半导体行业的发展起着重要的推动作用。

在全球化的市场环境下,各国的半导体企业需要遵循统一的标准和规范,以便更好地参与国际竞争。

JEDEC标准的中文版为中国半导体企业提供了参考和借鉴的依据,有助于提高中国半导体行业的技术水平和国际影响力。

此外,JEDEC标准中文版还对半导体行业的技术交流和合作起着促进作用。

在全球范围内,各国的半导体企业可以通过遵循JEDEC标准,实现技术的共享和合作,共同推动半导体行业的发展。

JEDEC标准中文版的发布和应用,有助于促进全球半导体行业的合作交流,推动技术创新和产业发展。

最后,JEDEC标准中文版的制定和发布离不开全球半导体行业的共同努力和支持。

各国的半导体企业和研究机构可以通过积极参与JEDEC标准的制定和修订,共同推动半导体行业的技术发展和规范化。

同时,半导体行业的从业人员也可以通过学习和应用JEDEC标准中文版,不断提升自身的专业技能和素质,为行业的发展做出更大的贡献。

综上所述,JEDEC标准中文版是全球半导体行业的重要参考和依据,对于促进行业发展、推动技术交流和合作、提高产品质量和国际竞争力起着重要作用。

通过深入理解和应用JEDEC标准中文版,可以更好地推动半导体行业的发展,实现技术的共享和合作,促进全球半导体行业的繁荣和稳定发展。

jedec标准jep95 -回复Jedec标准JEP95,为了更好地理解这一标准的内容,我们需要从头开始了解它的背景、目的、特点以及它在电子行业中的应用。

一、背景介绍在电子行业中,一切工作都必须依赖于标准。

标准化是确保产品和系统之间兼容性的关键因素,同时也有助于提高效率和降低成本。

Jedec(Joint Electron Device Engineering Council)是一个全球性的电子行业标准化组织,致力于推动半导体和电子器件领域的技术标准制定工作。

Jedec的标准被广泛应用于各种电子设备和系统。

二、Jedec标准JEP95的目的Jedec标准JEP95,全称为"Standard for Development and Documentation of Electronic Products, Packaging, and Systems",是Jedec为了提供一种规范的方法,用于开发和记录电子产品、封装和系统的过程而制定的标准。

它旨在通过确保规范和一致的方法,促进电子产品开发和封装的效率和可靠性,同时降低成本和风险。

三、Jedec标准JEP95的特点1. 综合性:JEP95 不仅仅关注电子产品的开发,还包括了电子封装和系统的开发。

它提供了一个完整的流程指南,从设计到生产,全面涵盖了整个产品生命周期。

2. 易用性:JEP95 采用简单明了的语言,易于理解和使用。

它提供了规范的模板和常见的术语定义,有助于用户快速入门并应用标准。

3. 灵活性:JEP95 能够灵活地适应不同的项目需求,可以根据具体的应用场景进行调整和修改。

它提供了一系列的指南和建议,但并不限制开发人员的自由创新。

4. 兼容性:JEP95 与Jedec其他标准保持一致,并与全球各个国际标准组织的标准相兼容。

这保证了系统和组件之间的一致性和互操作性。

四、Jedec标准JEP95在电子行业中的应用JEP95在电子行业中发挥了重要的作用,对产品的开发、封装和系统的设计有着深远的影响。

半导体封装根据不同的用途,半导体的封装可以分为多种类型。

半导体的封装标准包括 JEDEC 和JEITA 标准,但有许多来自不同半导体制造商的封装不属于上述标准。

另外,JEDEC 和JEITA 这两种标准的名称也并非总是被用于制造商的产品目录和数据表中,除此以外,不同制造商之间的描述系统也不统一。

本页提供关于以下半导体封装描述规则的基本信息。

• 对那些明显具有相同封装的产品必须尽可能提供统一的一般性描述;如DIL →DIP 等。

• 如果制造商无法使用通用的名称,或者如果封装类型是众所周知的情况,则可使用制造商的描述;如PENTAWATT 等。

•作为一般性规则,必须在封装描述之后加上标有指示针脚数量的数字;如DIP24、SOT23-5等。

注:本页中所提供的信息仅供参考。

请在使用前确认制造商数据表中的所有数据。

DIP主要分类 主要分类说明 次级分类 次级分类说明有时也称为“DIL”,但在本网站上,它们被统称为“DIP”,是指引脚从封装的两侧引出的一种通孔贴装型封装。

尽管针脚间距通常为2.54毫米 (100密耳),但也有些封装的针脚间距为1.778毫米 (70密耳)。

DIP 拥有6-64个针脚,封装宽度通常为15.2毫米(600密耳)、10.16毫米(400密耳)、或7.62毫米(300密耳),但请注意,即使针脚数量相同,封装的长度也会不一样。

DIP(双列直插式封装) 塑料DIP 封装。

有时也称为“PDIP”,但在本网站上它们被统称为“DIP”。

CDIP(陶瓷DIP) 陶瓷DIP 封装。

有时也称为“CERDIP”,但在本网站上它们被统称为“CDIP”。

WDIP(窗口DIP)一种带有消除紫外线的透明窗口的DIP 封装,通常是一种使用玻璃密封的陶瓷封装。

不同制造商的描述可能会有所不同,但ST (ST Microelectronics )公司称之为“FDIP”。

在本网站上,它们被统称为“WDIP”。

功率DIP 能够通过引脚散除IC 所产生的热量的一种DIP 封装类型。

大多数此类封装都使用统称为接地端子的引脚沿中心围成一圈。

SIP主要分类 主要分类说明 次级分类 次级分类说明有时也称为“SIL”,但在本网站上它们被统称为“SIP”,是指引脚从封装的一侧引出的一种通孔SIP(单列直插式封拥有2-23个针脚,具有多种不同的形状和针脚间距。

请注意,其中有许多具有采用散热结构的特殊形状。

贴装型封装。

当贴装到印刷电路板时,它与电路板垂直。

装) 另外,它与TO220无明显差别。

ZIP(Z 形直插式封装) 从封装的一侧引出的引脚在中间被弯曲成交错的形状。

封装一侧的针脚间距为1.27毫米 (50密耳),但在插入印刷电路板时会变成2.54毫米(100密耳)。

拥有12-40个针脚。

QFP主要分类 主要分类说明 次级分类 次级分类说明表面贴装型封装的一种,引脚从封装的四个侧面引出。

其特征是引线为鸥翼形(“L”形)。

拥有多种针脚间距:1.0毫米、0.8毫米、0.65毫米、0.5毫米、0.4毫米和0.3毫米。

其名称有时会被混淆。

QFP 封装的缺点是针脚间距缩小时,引脚非常容易弯曲。

QFP(四侧引脚扁平封装)该描述常用于标准QFP 封装。

FQFP(细密间距 QFP) 指针脚的间距小于0.65毫米。

一些制造商使用该名称。

HQFP(带散热器的QFP) 带散热器的QFP 封装 。

LQFP(薄型QFP)厚度为1.4毫米的薄型QFP 封装 。

MQFP(公制QFP)符合JEDEC(美国联合电子设备委员会)标准的一种QFP 分类。

它是指针脚间距介于1.0~0.65毫米,本体厚度为3.8~2.0毫米的标准QFP 封装。

MQFP(超薄QFP)在贴装至印刷电路板上时,所采用的一种高度为1.27毫米(50密耳)或更小的超薄QFP 封装。

封装主体的厚度约为1.00毫米,拥有多种针脚间距:0.8毫米、0.65毫米、0.5毫米和0.4毫米。

拥有44 - 120个针脚。

VQFP(微型QFP)小型QFP 封装的一种,针脚间距为 0.5毫米。

封装主体的厚度约为1.5毫米。

目前它被包括在LQFP 分类中,但有些制造商仍然使用该名称。

J 形引线主要分类 主要分类说明 次级分类 次级分类说明表面贴装型封装的一种。

其特征是引线为“J”形。

与QFP 等封装相比,J 形引线不容易变形并且易于操SOJ(小外形J形引线封装)引脚从封装的两侧引出。

之所以叫此名称,是因为引线的形状如同字母“J”。

通常由塑料制成,常用于LSI 存储器,如DRAM 、SRAM 等。

针脚间距为1.27毫米(50密耳)。

拥有20 - 40个针作。

脚。

PLCC(带引线的塑料芯片载体)J 形引脚从封装的四个侧面引出的一种塑料封装类型。

针脚间距 为1.27毫米(50密耳),拥有18-84个针脚。

在QFJ 和 JEITA 标准中也使用该名称。

CLCC(带引线的陶瓷芯片载体) J 形引脚从封装的四个侧面引出的一种陶瓷封装类型。

带有窗口的封装用于紫外线消除型EPROM 微机电路以及带有EPROM 的微机电路等。

TSOC一种具有较少针脚的SOJ 封装。

针脚间距与SOJ 一样,均为1.27毫米(50密耳),但主体尺寸较小。

格栅阵列主要分类 主要分类说明 次级分类 次级分类说明引线在封装的一侧被排列成格栅状的一种封装类型,可分为两种:通孔贴装PGA 型和表面贴装BGA 型。

PGA(针栅阵列)通孔贴装型封装之一。

这是一种使用阵列式引脚垂直贴装在封装底部(象指甲刷一样)的一种封装类型。

当材料的名称未作具体规定时,经常使用陶瓷PGA 封装。

用于高速和大规模逻辑LSI ,针脚间距为 2.54毫米(100密耳),拥有64 - 447个针脚。

另外还有塑料PGA 封装,为降低成本,可用作替代玻璃环氧树脂印刷电路板的封装基材。

PGA(球栅阵列)表面贴装型封装的一种,在印刷电路板的背面使用球状焊点来代替阵列式引线。

LSI 芯片被贴装至印刷电路板的表面,并用塑形树脂或填充材料密封。

它是一种不少于 200个针脚的 LSI 封装,封装主体的尺寸能够比QFP 更小,并且无需担心引线发生变形。

因为其引线电感小于QFP ,所以能够用于高速LSI 封装。

它目前被用于逻辑 LSI(225-350个针脚)和高速SRAM (119个针脚,等)等。

微型 SMD由美国的国家半导体(National Semiconductor )公司开发的一种小型BGA 封装,拥有4 - 42个针脚。

SO主要分类 主要分类说明 次级分类 次级分类说明“SO”代表“小外形”(Small Outline)。

它是指鸥翼形(L 形)引线从封装的两个侧面引出的一种表面贴装型封装。

对于这些封装类型,有各种不同的描述。

请注意,即使是名称相同的封装也可能拥有不同的形状。

SOP(小外型封装)在JEITA 标准中,针脚间距为1.27毫米 (50密耳)的此类封装被称为“SOP”封装。

请注意,JEDEC 标准中所称的“SOP”封装具有不同的宽度。

SOIC(小外形集成电路) 有时也称为“SO”或“SOL”,但在本网站上,它们被统称为“SOIC”。

在JEDEC 标准中,针脚间距为1.27毫米 (50密耳)的此类封装被称为“SOIC”封装。

请注意,JEITA 标准中所称的“SOIC”封装具有不同的宽度。

MSOP(迷你 (微型) SOP) 针脚间距为 0.65毫米或 0.5毫米的一种小型SOP 封装。

Analog Devices 公司将其称为“microSOIC”,Maxim 公司称其-为“SO/uMAX”,而国家半导体(National Semiconductor )公司则称之为“MiniSO”。

另外,也可以被认为是 SSOP 或TSSOP 。

QSOP(1/4尺寸SOP) 针脚间距为0.635毫米(25密耳)的一种小型SOP 封装。

SSOP(缩小型SOP)针脚间距为1.27毫米(50密耳)的一种细小型SOP 封装。

SSOP 的针脚间距为1.0毫米、0.8毫米、0.65毫米和0.5毫米,拥有5 - 80个针脚。

它们被广泛用作小型表面贴装型封装。

TSOP(超薄SOP)一种超薄的小外形封装。

贴装高度为1.27毫米(50密耳)或更低,针脚间距为1.27毫米或更低的一种SOP 封装。

拥有24 - 64个针脚。

TSOP 分为两种类型:一种是引线端子被贴装到封装的较短一侧(针脚间距为 0.6毫米、0.55毫米或0.5毫米),另一种是引线端子被贴装到封装的较长一侧(针脚间距通常为1.27毫米)。

在 JEITA 标准中,前者被称为“I 型”,后者被称为“II 型”。

TSSOP(超薄缩小型SOP) 厚度为1.0毫米的一种超薄型SSOP 封装 。

针脚间距为0.65毫米或0.5毫米,拥有8-56个针脚。

HTSSOP(散热片TSSOP) 在TSSOP 板贴装端的表面上提供了一个被称为“散热片”的散热面。

CERPAC 一种陶瓷密封型封装,针脚间距为 1.27毫米(50密耳)。

DMPNew Japan Radio (本网站简称为“NJR&rdquo 所开发的一种封装。

针脚间距为 1.27毫米(50密耳),与SOP 和 SOIC 类似,但封装宽度不同。

SC70也可被视为SSOP 封装的一种,是针脚间距为0.65毫米的小型表面贴装型封装。

大部分拥有5 个针脚,但也有些拥有6个针脚。

根据制造商的不同,它也被称为“USV”或“CMPAK”。

SOT主要分类 主要分类说明 次级分类 次级分类说明“SOT”代表“小外形晶体管”(Small Outline Transistor),最初为小型晶体管表面贴装型封装。

即便它拥有与SOT 相同的形状,但不同的制造商也可能使用不同的名称。

SOT23 针脚间距为0.95毫米的小型表面贴装型封装。

拥有3 - 6个针脚。

根据制造商的不同,它也被称为“SC74A”、“MTP5”、“MPAK”或“SMV”。

SOT89针脚间距为1.5毫米并且带有散热片的小型表面贴装型封装。

大部分拥有3 个针脚,但也有些拥有5个针脚。

根据制造商的不同,它也被称为“UPAK”。

SOT143针脚间距为1.9毫米的小型表面贴装型封装。

拥有4个针脚,其中一个针脚的宽度大于其他针脚。

SOT223针脚间距为2.3毫米并且带有散热片的小型表面贴装型封装。

拥有3个针脚。

TO (塑料)主要分类 主要分类说明 次级分类 次级分类说明“TO”代表“晶体管外壳”(Transistor Outline)。

它最初是一种晶体管封装,旨在使引线能够被成型加工并用于表面贴装。

即便它拥有与TO 相同的形状,但不同的制造商也可能使用不同的名称。

TO3P 稳压器等所采用的一种封装,最初为晶体管封装的一种。