UDA1341TS音频驱动开发

- 格式:pdf

- 大小:105.21 KB

- 文档页数:7

IIS 使用手册南京博芯电子技术有限公司2009-04This document contains information on a product under development. Prochip Corp reserves theright to change or discontinue this product without notice.Prochip Crop, 2009. All rights reserved.版权说明版权所有,未经南京博芯电子技术有限公司的授权,本说明文挡不可以被复制或以任何形式或方式(电子的或是机械的)传播,包括影印,记录或是用其他任何信息存储及检索系统。

文挡所描述的任何一种电路对于第三方没有专利权及专利特许权。

否认书:南京博芯电子技术有限公司保留对文档随时进行修改的权利,无须任何申明。

南京博芯电子技术有限公司所提供的信息是精确可靠的。

对于它的应用以及由于应用而导致违反专利权或是第三方的其他权利,本公司不负任何责任。

版本历史日期版本描述备注2009-4-22 1.0 初稿李宾目录版本历史 (2)目录 (3)一、IIS模块简介 (4)1.1 概述 (4)1.2 IIS结构 (4)二、IIS模块功能介绍 (6)2.1 IIS功能介绍 (6)2.2 IIS工作模式 (6)2.3 IIS寄存器介绍 (6)三、IIS模块实现原理 (9)3.1 IIS硬件实现原理 (9)3.2 IIS软件实现原理 (11)四、IIS模块测试流程及结果说明 (14)4.1 IIS测试流程图 (14)4.2 IIS测试结果说明 (14)五、其他注意事项 (15)5.1 CODEC设置 (15)5.2 DMA设置 (15)5.3 IIS设置 (16)5.4需要注意的问题 (16)一、 IIS模块简介1.1 概述IIS(Inter IC Sound)是常用的音频接口标准,用于数字音频设备。

基于UDA1341数字音频接口嵌入式电路的设计

黄会雄

【期刊名称】《山西电子技术》

【年(卷),期】2007(000)001

【摘要】介绍UDA1341数字音频接口嵌入式电路结构和引脚功能,给出在嵌入式系统中采用UDA1341与S3C2410硬件接口实现方法,同时介绍基于嵌入式系统IIS总线格式及应用设计.

【总页数】3页(P25-27)

【作者】黄会雄

【作者单位】湖南商务职业技术学院,湖南,长沙,410205

【正文语种】中文

【中图分类】TN710.9

【相关文献】

1.基于S3C2410型微处理器和UDA1341型立体声音频编解码器的嵌入式音频系统设计 [J], 高建华;王殊

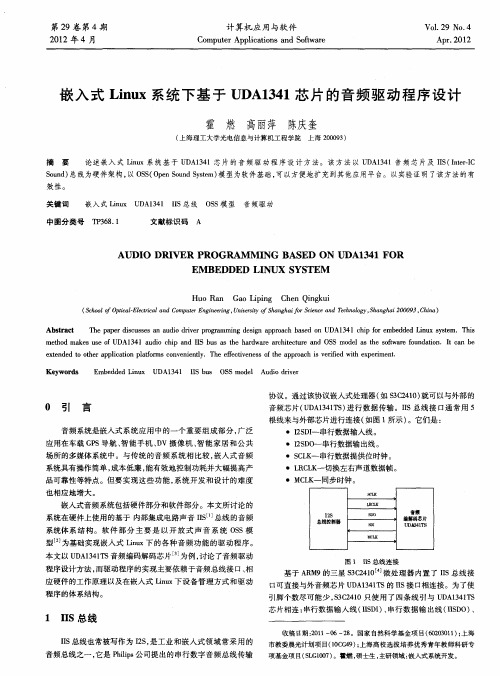

2.嵌入式Linux系统下基于UDA1341芯片的音频驱动程序设计 [J], 霍燃;高丽萍;陈庆奎

3.基于UDA1341和FM1182的嵌入式语音网络传输系统设计 [J], 孙锐;徐骏;李景;张红星;凌强;王嵩

4.基于数字音频接口的地震数据采集电路板快速评估方法 [J], 高尚华;薛兵;李际弘;李江

5.携手行业领袖齐聚数字论坛——安捷伦数字测试论坛成功实现数字电路与嵌入式系统的设计 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

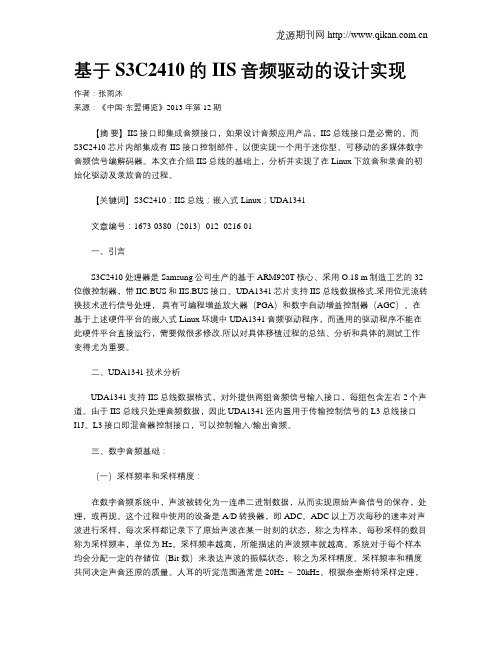

基于S3C2410的IIS音频驱动的设计实现作者:张雨沐来源:《中国·东盟博览》2013年第12期【摘要】IIS接口即集成音频接口,如果设计音频应用产品,IIS总线接口是必需的。

而S3C2410芯片内部集成有IIS接口控制部件,以便实现一个用于迷你型、可移动的多媒体数字音频信号编解码器。

本文在介绍IIS总线的基础上,分析并实现了在Linux下放音和录音的初始化驱动及录放音的过程。

【关键词】S3C2410;IIS总线;嵌入式Linux;UDA1341文章编号:1673-0380(2013)012 -0216-01一、引言S3C2410处理器是Samsung公司生产的基于ARM920T核心、采用O.18 m制造工艺的32位微控制器,带IIC.BUS和IIS.BUS接口。

UDA1341芯片支持IIS总线数据格式.采用位元流转换技术进行信号处理,具有可编程增益放大器(PGA)和数字自动增益控制器(AGC)。

在基于上述硬件平台的嵌入式Linux环境中UDA1341音频驱动程序,而通用的驱动程序不能在此硬件平台直接运行,需要做很多修改.所以对具体移植过程的总结、分析和具体的测试工作变得尤为重要。

二、UDA1341技术分析UDA1341支持IIS总线数据格式,对外提供两组音频信号输入接口,每组包含左右2个声道。

由于IIS总线只处理音频数据,因此UDA1341还内置用于传输控制信号的L3总线接口I1J。

L3接口即混音器控制接口,可以控制输入/输出音频。

三、数字音频基础:(一)采样频率和采样精度:在数字音频系统中,声波被转化为一连串二进制数据,从而实现原始声音信号的保存,处理,或再现。

这个过程中使用的设备是A/D转换器,即ADC。

ADC以上万次每秒的速率对声波进行采样,每次采样都记录下了原始声波在某一时刻的状态,称之为样本。

每秒采样的数目称为采样频率,单位为Hz。

采样频率越高,所能描述的声波频率就越高。

河南理工大学计算机科学与技术学院毕业设计材料清单2008—2009学年第二学期设计题目基于ARM的音频播放器学生姓名刘金龙专业班级计算机05--1班学号0502010113指导教师安吉宇2009年5月25日毕业设计(论文)任务书专业班级计算机05—1班学生姓名刘金龙一、题目基于ARM的音频播放器二、主要任务与要求三、起止日期2009 年3月12 日至2009 年 5 月25 日指导教师签字(盖章)系主任签字(盖章)年月日毕业设计(论文)评阅人评语专业班级学生姓名题目评阅人签字(盖章)职称工作单位年月日毕业设计(论文)评定书专业班级学生姓名题目指导教师签字(盖章)职称年月日毕业设计(论文)答辩许可证经审查,专业班同学所提交的毕业设计(论文),符合学校本科生毕业设计(论文)的相关规定,达到毕业设计(论文)任务书的要求,根据学校教学管理的有关规定,同意参加毕业设计(论文)答辩。

指导教师签字(盖章)年月日根据审查,准予参加答辩。

答辩委员会主席(组长)签字(盖章)年月日毕业设计(论文)答辩委员会(小组)决议院(系)专业班同学的毕业设计(论文)于年月日进行了答辩。

题目答辩委员会成员主席(组长)委员(成员)委员(成员)委员(成员)委员(成员)委员(成员)委员(成员)答辩前向毕业设计答辩委员会(小组)提交了如下资料:1、设计(论文)说明共页2、图纸共张3、评阅人意见共页4、指导教师意见共页根据学生所提供的毕业设计(论文)材料、评阅人和指导教师意见以及在答辩过程中学生回答问题的情况,毕业设计(论文)答辩委员会(小组)做出如下决议。

一、毕业设计(论文)的总评语二、毕业设计(论文)的总评成绩毕业设计答辩委员会主席(组长)签名委员(组员)签名年月日摘要在信息化程度很高的今天,ARM 微处理器以其小型、快速、低能耗、集成式的32位的RISC 架构内核的优势,使其技术的应用几乎已经深入到各个领域,如工业控制领域,无线通讯领域,成像和安全产品以及消费电子产品领域。

UDA1341TS学习wince音频驱动开发 2009-04-02 14:02:58 阅读48 评论0 字号:大中小7. 功能描述(FUNCTIONAL DESCRIPTION)7.1 系统时钟(System clock)UDA1341TS 只能使用从片模式,这就意味着在所有应用中系统设备必须给它提供系统时钟.系统时钟频率是可选择的,可为了256fs,384fs或512fs.系统时钟必须对数字接口信号锁定频率(The system clock must be locked in frequency to the digital interface signals)7.2 针脚兼容性(Pin compatibility)UDA1341TS部分针脚与UDA1340M和UDA1344TS兼容,印刷电路板从UDA1340M升级到UDA1341TS比较简单.与UDA1340M兼容的针脚在FIG.3中标明.7.3 模拟前端(Analog front end)UDA1341TS的模拟前端由两个立体声模数转换器组成,每个转换器有两个通道,通道2有一个可编程增益放大器(PGA),PGA被用来预放大输入通道2的麦克风信号.输入通道1有一个可选择的0或6dB的增益级,通过L3-接口来控制.在这种方式下,1V或2V(有效值)的输入信号(如从一个CD源中输出)可以在输入通道1上串联一个12千欧的外部电阻来支持.下表给出了它的应用模式.使用输入增益级的应用模式--------------------------------------------------------------------------------------------------------电阻(12千欧) 输入增益开关最大输入电压使用0 dB 2V(有效值)输入信号 ps:如果这里没有必要支持2V输入信号,外接电阻就不应被使用使用6 dB 1V(有效值)输入信号不使用 0 dB 1V(有效值)输入信号不使用 6 dB 0.5V(有效值)输入信号---------------------------------------------------------------------------------------------------------7.4 可编程增益放大器(Programmable Gain Amplifier(PGA))PGA可以通过L3接口设置为-3,0,3,9,15,21或27dB7.5 模数转换器(Analog-to-Digital Converter(ADC))UDA1341TS的立体声模数转换器由两个三阶增量调制器组成.它们有一个改进的里齐码结构使用不同的开关电容.过取样率为128.7.6 数字自动增益控制(Digital Automatic Gain Control(AGC))当有一个麦克风信号输入到通道2时,输入通道2有一个数字自动增益控制来压缩动态范围.数字AGC可以用L3接口打开.在打开的状态下压缩动态范围.通过L3接口用户可以设置AGC的参数:启动时间,衰减时间和输出电平.当AGC设置为关时,输入通道2的增益可以手工设置.在这种情况下PGA和AGC组合在一起.输入通道2的范围从-3到60.5dB以0.5dB步进.7.7 自动增益控制状态检测(AGC status detection)当自动增益控制的增益级低于8dB时,数字自动增益中的自动增益状态信号变为高,这个信号可以被用来通过L3接口给PGA一个新的增益设置,或者驱动一个LED.7.8 数字混音器(digital Mixer)两个立体声模数转换器(包括AGC)有四种模式:*只使用ADC1(用做线路输入);输入通道2关闭*只使用ADC2,包括PGA和数字AGC(用做麦克风输入);输入通道1关闭*ADC1+ADC2混合模式,包括PGA和AGC*ADC1+ADC2 double differential 模式(提升ADC性能)要点:为了防止线路输入间串扰,在double differential模式下不应该有信号应用到麦克风输入.在所有模式下(除了double differential模式)一个参考电压一直在ADC的输入上有效,而在double differential模式下却没有.在混合模式下,通道1和通道2的ADC的输出信号可以经L3接口通过一定系数混合.混合系数的范围从0到负无穷dB以1.5dB步进.7.9 抽取滤波器(Decimation filter(ADC))从128fs开始的抽取可以分两阶段进行.第一个阶段实现3阶sin x/x 特性. (The first stage realizes 3rd order sinx/x characteristic), 以16为基抽取.第二个步骤由3个半带滤波器组成,每一个以2为因子抽取.抽取滤波器特性--------------------------------------------------------------------------------项(ITEM) 条件(CONDITIONS) 值(V ALUE(db))通频带波纹0到0.45fs ±0.05抑制频带 >0.55fs -60动态范围0到0.45fs 108总增益输入通道1;0 dB输入 -1.16--------------------------------------------------------------------------------7.10 过载检测(Overload detection(ADC))过载检测这个名字虽合适但有一点不正确.实际上,它的输出表明输出数据比最大可能的数字变化大-1dB(实际上是-1.16dB).无论何时,在何声道.在这种条件下OVERFL输出被强制为高电平持续至少512fs时钟周期(当fs=44.1 kHZ时为11.6ms).每次过载后超时被复位.7.11 静音(Mute(ADC))在从掉电模式后恢复或打开系统时钟时,引脚DATAO的串行数据输出保持低电平直到从抽取滤波器来的有效数据可用.这个时间取决于是否选择了直流消除滤镜.*直流消除关闭 t=1021/fs; 当fs=44.1kHZ时t=23.2ms*直流消除开启 t=12288/fs;当fs=44.1kHZ时t=279ms7.12 内插滤波器(Interpolation filter(DAC))数字滤波器插值从1fs到128fs用一个级联的递归滤波器和一个有限推进响应滤镜.插值滤镜特性-------------------------------------------------项条件值(dB)通带波纹0到0.45fs ±0.03抑制频带 >0.55fs -50动态范围0到0.45fs 108------------------------------------------------7.13峰值检波器(Peak detector)在再现时,内置了峰值检波器.峰值检测位置可以在声音特征设置之前或之后通过L3-接口来设置.峰值检波器实现成像是一个峰值保持检波器,这就表明最高的音级被保存直到被L3-接口读出.在读出后峰值电平寄存器被复位.7.14 快速静音(Quick mute)一个硬件静音可能通过固定的QMUTE引脚激活.当QMUTE设置为高电平时,输出信号被减弱为0.设置QMUTE为低电平时, 快速静音无效.7.15 噪音整形器(Noise shaper(DAC))三阶噪音整形器运行频率为128fs.它将频带内的量化噪声转换成音频带之上的频率.这种噪音整形技术可以提供高信噪比.噪音整形器输出通过一个DAC流滤波器转换成模拟信号. 7.16 DAC流滤波器(Filter Stream Digital-to-Analog Converter(FSDAC))DAC滤波器是一个半数字重构滤镜,可将噪音整形器的一位数据流转换成模拟电压输出.滤镜系数采取当前源并且合计在运算放大器的虚拟地上.这种方法可以达到很高的信噪比和低时钟抖动敏感.因为DAC的内置滤波功能,所以不需要一个后置滤波器.板上放大器将DAC流滤波器的当前输出转换成一个能驱动线路输入的输出电压信号.7.17 多格式输入/输出接口(Multiple format input/output interface)UDA1341TS 支持下列数据格式:*IIS总线,字长可以达到20bits*最高有效位有效的串行格式,字长可达20位.*最低有效位有效的串行格式,字长为16,18或20位*最高有效位有效的输出和最低有效位有效的16,18,20位输入.左声道和右声道字长是时间多工化的.格式如图FIG4所示UDA1341TS允许双倍速数据检测.在这种情况下,重低音,高音和去加重特性不能被使用.然而,音量控制和软静音仍可控.双倍速检测可以通过L3接口设置.位时钟频率必须小于等于64倍字选频率.7.18 L3接口(L3-interface)信息按照L3格式通过微控制器总线进行传输,在这种格式下有两种不同的操作模式,地址模式和传输模式.地址模式需要通过L3总线选择一个设备并且为数据传输模式定义目的寄存器.数据传输可以有两个方向:输入到UDA1341TS中以编码它的声音处理和系统控制特性,或从UDA1341TS中输出来提供峰值.7.19地址模式地址模式用来选择一个设备为了之后的数据传输,并且定义目的寄存器,地址模式被描述为L3MODE保持低电平并且经过8个L3CLOCK脉冲.伴随着8个数据位.基本时序如图FIG.5所示.(L3CLOCK为低电平时进行同步)数据位7到2表示了一个六位的设备地址,第7位为最高有效位,第2位为最低有效位.UDA1341TS的地址是000101.数据位0到1表示之后传输的数据类型(表4).如果UDA1341TS接收了一个不同的地址命令,它会取消所作的选择BIT1 BIT0 MODE TRANSFER0 0 DATA0 直接编址寄存器:音量,重低音,高音,峰值检测位置,去加重,静音和模式扩展编址寄存器:数字混音器控制,自动增益控制,麦克灵敏度控制,输入增益,自动增益时间常数及输出等级0 1 DATA1 读出峰值(从UDA1341TS读到微控制器)1 0 STATUS 复位,系统时钟频率,数据输入格式,直流滤波器,输入增益开关,输出增益开关极性控制,双倍速和电源控制1 1 未使用7.20 数据传输模式在址址模式下激活的选择仍然有效,直到UDA1341TS接收到一个新的地址指令.数据传输的基本时序本质上与地址模式相同,在FIG6中给出 (L3MODE保持高电平,L3CLOCK高电平同步),注意"L3DATA写"指出数据传输从微控制器到UDA1341TS并且"L3DATA峰值读" 指出数据以相反的方向传输.最大的输入时钟和数据传输速率为64fs.所有的传输都是基于8位字节,数据在接收到一个字节的第八位后存储到UDA1341TS中.多字节传输可参照Fig.77.21 编码音频处理及其它特性音频处理和其它特性值存储在独立的寄存器中,通过选择传输的数据类型来对寄存器进行第一道选取,这通过地址模式中的第0位和第1位来完成,第二道选取由数据字节的2或3个最高有效位(第7-6位或7-5位)完成.数据字节中的其它位(BIT5-0,BIT4-0)表示要被存放到已选寄存器的值.对于UDA1341TS 来说可以选取以下模式.*STATUS在这种模式下,复位,系统时钟频率,数据输入格式,直流滤波器,输入增益开关,输出增益开关,极性控制,双倍速和电源控制等特性可以被设置.*DATA0在这种模式下有两种地址模式:直接编址模式和扩展编址模式.直接编址模式使用数据字节的两个最高有效位.在这种地址模式下,音量,重底音,高音,峰值位置, 去加重,静音,模式等特性可以被直接控制.扩展编址模式被用来控制数字混音器,自动增益控制,麦克灵敏度,输入增益,自动增益控制时间系数,自动增益控制输出等级等特性,一个扩展地址可以通过EA寄存器(3位)来设置,扩展寄存器中的值可以通过写数据到ED寄存器(5位)来设置.*DATA1在这种模式下,检测到的峰值可以被读出.Table 5 默认设置符号(SYMBOL) 特性(FEATURE) 设置或值(SETTING OR V ALUE)******Status******OGS 输出增益开关(Output gain switch) 0 dBIGS 输入增益开关(Input gain switch) 0 dBPAD 模数转换极性(Polarity of ADC) 不反转(non-inverting)PDA 数模转换极性(Polarity of DAC) 不反转(non-inverting)DS 双倍速(Double speed) 单倍速(single speed)PC 电源控制(Power control ADC and DAC) 开启(on)******直接控制(Direct control)*******VC 音量控制(V olume control) 0 dBBB 重低音(Bass boost) 0 dBTR 高音(Treble) 0 dBPP 峰值检测位置(Peak detection position) 在音调特性之后(after the tone features)DE 去加重(De-emphasis) 无去加重(no de-emphasis)MT 静音(Mute) 不静音(no mute)M 模式开关(Mode switch) 平坦(flat)******扩展地址编码(Extended programming)******MA 混音器增益通道1(Mixer gain channel 1) -6 dBMB 混音器增益通道2(Mixer gain channel 2) -6 dBMS 麦克敏感度(MIC sensitivity) 0 dBMM 混音器模式开关双微分模式?(double differential mode)AG 自动增益控制(AGC control) 关闭自动增益(disable AGC)AT 自动增益控制启动及衰减时间(AGC attack and decay time) 11ms 和100msAL 自动增益控制输出等级(AGC output level) -9 dB FS7.21.1 STATUS 控制'STATUS'类型数据传输BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 | 寄存器选择(REGISTERSELECTED)------------------------------------------------------------------------------------------------------ 0 RST SC1 SC0 IF2 IF1 IF0 DC RST= 复位(reset)SC=系统时钟频率(system clock frequency(2位))IF=数据输入格式(data input format(3位)) DC=直流滤波器(DC-filter)------------------------------------------------------------------------------------------------------- 1 OGS IGS PAD PDA DS PC1 PC0 OGS=输出增益(6dB)开关(output gain switch) IGS=输入增益(6dB)开关(input gain switch)PAD=ADC极性(polarity of ADC)PDA=DAC极性(polarity of DAC)DS=双倍速(double speed)PC=电源控制(power control)(2位)-------------------------------------------------------------------------------------------------------- 7.21.1.1 复位(Reset)1位值,使用默认设置(系统时钟频率除外)初始化L3寄存器.0: 不复位 1: 复位7.21.1.2 系统时钟频率(System clock frequency)两位值,用来选择外部时钟频率.-----------------------------------------SC1 | SC0 | FUNCTION0 0 512fs0 1 384fs1 0 256fs1 1 未使用------------------------------------------7.21.1.3 直流滤波器(DC-filter)一位值用来使能数字直流滤波器0: 不使用 1:使用7.21.1.4 数据输入格式(Data input format)3位值用来选择数据输入格式-------------------------------------------------------------------------------------IF2 IF1 IF0 FUNCTION0 0 0 IIS总线(IIS-BUS)0 0 1 最低有效位对齐的16位(LSB-justified 16 bits)0 1 0 最低有效位对齐的18位(LSB-justified 18 bits)0 1 1 最低有效位对齐的20位(LSB-justified 20 bits)1 0 0 最高有效位对齐(MSB-justified)1 0 1 最低有效位对齐的16位输入和最高有效位对齐的输出(LSB-justified 16 bits input and MSB-justified output)1 1 0 最低有效位对齐的18位输入和最高有效位对齐的输出(LSB-justified 18 bits input and MSB-justified output)1 1 1 最低有效位对齐的20位输入和最高有效位对齐的输出(LSB-justified 20 bits input and MSB-justified output)---------------------------------------------------------------------------------------7.21.1.5 输出增益开关(Output gain switch)一位值用来控制数模转换器输出增益开关0: 0 dB 1: 6 dB7.21.1.6 输入增益开关(Input gain switch)一位值用来控制模数转换器开关0: 0 dB 1: 6 dB7.21.1.7 模数转换器极性(Polarity of ADC)一位值用来控制模数转换器极性.0: 不反转 1: 反转7.21.1.8 数模转换器极性(Polarrity of DAC)一位值用来控制数模转换器极性.0: 不反转 1: 反转7.21.1.9 双倍速(Double speed)一位值用来使能双倍速再现(playback)0: 单倍速 1: 双倍速7.21.1.10 电源控制(Power control)两位值用来禁用数模转换器和/或模数转换器节电模式.--------------------------------------FUNCTIONPC1 PC0ADC DAC--------------------------------------0 0 off off0 1 off on1 0 on off1 1 on on--------------------------------------7.21.2 DATA0 直接控制DATA0类型数据传输( Data transfer of type ‘DATA0’)------------------------------------------------------------------BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0 REGISTER SELECTED0 0 VC5 VC4 VC3 VC2 VC1 VC0 VC = 音量控制(volume control (6 bits))0 1 BB3 BB2 BB1 BB0 TR1 TR0 BB = 低音增强(bass boost (4 bits))TR = 高音(treble (2 bits))1 0 PP DE1 DE0 MT M1 M0 PP = 峰值检测位置(peak detection position)DE = 去加重(de-emphasis (2 bits))MT = 静音(mute)M = 模式选择(mode switch (2 bits))1 1 0 0 0 EA2 EA1 EA0 EA=扩展地址(extended address (3 bits))1 1 1 ED4 ED3 ED2 ED1 ED0 ED = 扩展数据(extended data (5 bits))7.21.3 DATA0扩展编程寄存器(DATA0 EXTENDED PROGRAMMING REGISTERS) 扩展控制寄存器(Extended control registers)EA2 EA1 EA0 ED4 ED3 ED2 ED1 ED0 REGISTER SELECTED0 0 0 MA4 MA3 MA2 MA1 MA0 MA=混音器增益通道1(mixer gain channel 1 (5 bits)) 0 0 1 MB4 MB3 MB2 MB1 MB0 MB=混音器增益通道2(mixer gain channel 2 (5 bits)) 0 1 0 MS2 MS1 MS0 MM1 MM0 MS=麦克风敏感度(MIC sensitivity (3 bits))MM=混音器模式(mixer mode (2 bits))1 0 0 AG 0 0 IG1 IG0 AG=自动增益控制(AGC control)IG=输入放大器增益通道2(input amplifier gain channel 2 (2 bits))1 0 1 IG6 IG5 IG4 IG3 IG2 IG=输入放大器增益通道2(input amplifier gain channel 2 (5 bits))1 1 0 AT2 AT1 AT0 AL1 AL0 AT=自动增益控制时间常数(AGC time constant (3 bits))AL=自动增益控制输出电平(AGC output level (2 bits))7.21.4 DATA1 控制(DATA1 CONTROL)'DATA1'数据传输类型BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0 读出数据(READ-OUT DATA)PL5 PL4 PL3 PL2 PL1 PL0 峰值电平(peak level value(6 bits))。

USB声卡和USB音频解码方案原理近年来USB产品层出不穷,USB音频类在USB开发者论坛的努力下,成为一种标准的规范,USB声卡也开始在市场上悄然出现。

因为USB声卡内置了DAC和有源功放,音频数据以数字方式进入USB声卡,完全杜绝了PC的内部干扰,所以,USB声卡将有可能成为现有内置声卡的替代品。

本文介绍了一种基于ARM处理器的USB声卡设计。

USB声卡原理由USB声卡数据流图(见图1)可以看出USB声卡的工作原理。

在主机端播放音乐时,应用软件或驱动程序把各类音频信号转换为统一的格式,如PCM、MPEG等格式的数据流,通过主机的USB接口发送给USB声卡。

声卡的USB 接口接收到数据后,通过I2S接口把并行音频数据转为串行,再发送给音频编解码芯片进行D/A转换,即可在音频芯片连接的扬声器中发音。

录音过程和播放过程正好相反。

图1 USB 声卡数据流硬件设计USB声卡硬件主要包括MCU和音频编解码芯片。

MCU采用三星公司的处理器S3C2410,S3C2410内置I2S总线控制器和USB Slaver控制器。

S3C2410的I2S控制器实现了一个外部8/16位立体声音频CODEC IC的接口,支持I2S 总线数据格式和MSB-justified数据格式,并且支持DMA传输模式。

音频芯片采用UDA1341TS。

UDA1341TS提供标准的I2S接口,可以直接和SSS1630的I2S引脚连接。

另外,此芯片还提供标准的L3、麦克风和扬声器接口。

L3接口的引脚分别连到S3C2410的3个GPIO输出引脚上,通过GPIO 控制L3接口。

UDA1341TS音频芯片集成数字化音频和混频器功能。

数字化音频功能可以播放数字化声音或录制声音,因为包括这个功能,所以常把此类芯片称为CODEC设备。

混频器用来控制各种输入/输出的音量大小等,在本芯片中通过L3接口进行控制。

图2 USB声卡拓扑图软件设计软件设计包括两部分:USB声卡固件程序设计和主机端Windows驱动设计。

基于IIS总线旳嵌入式音频系统设计嵌入式音频系统广泛应用于GPS自动导航、PDA.3G 等嵌入式领域, 但目前国内在这方面旳研究较少。

音频系统设计包括软件设计和硬件设计两方面, 在硬件上使用了基于IIS总线旳音频系统体系构造。

IIS(Inter-IC Sound bus)是菲利浦企业提出旳串行数字音频总线协议。

目前诸多音频芯片和MCU都提供了对IIS旳支持。

在软件上, 作为一种功能复杂旳嵌入式系统, 需要有嵌入式操作系统支撑。

Linux是一种源代码开放旳类UNIX系统, 由于其具有内核可裁剪性, 且提供对包括ARM、PPC在内旳多种嵌入式处理器旳支持, 因此广泛应用于嵌入式高端产品中。

虽然Linux提供了众多API来减少驱动程序制作旳复杂度, 不过由于音频应用对实时性有很高旳规定, 且需要处理旳数据量较大, 因此必须合理分派资源, 使用合适旳算法。

本文针对三星企业旳S3C44B0 ARM处理器构造了基于IIS旳音频系统, 并简介了该音频系统基于Linux内核旳驱动程序构造技术。

1 硬件体系构造IIS总线只处理声音数据。

其他信号(如控制信号)必须单独传播。

为了使芯片旳引出管脚尽量少, IIS只使用了三根串行总线。

这三根线分别是: 提供分时复用功能旳数据线、字段选择线(声道选择)、时钟信号线。

在三星企业旳ARM芯片中, 为了实现全双工模式, 使用了两条串行数据线, 分别作为输入和输出。

此外三星企业旳IIS接口提供三种数据传播模式:·正常传播模式。

此模式基于FIFO寄存器。

该模式下CPU将通过轮询方式访问FIFO寄存器, 通过IISCON 寄存器旳第七位控制FIFO。

·DMA模式。

此模式是一种外部设备控制方式。

它使用窃取总线控制权旳措施使外部设备与主存互换数据, 从而提高系统旳吞吐能力。

在三星企业旳ARM芯片中有4个通道DMA控制器用于控制多种外部设备, 其中IIS与其他串行外设共用两个桥联DMA(BDMA)类型旳DMA通道。

UDA1341TS学习wince音频驱动开发 2009-04-02 14:02:58 阅读48 评论0 字号:大中小7. 功能描述(FUNCTIONAL DESCRIPTION)7.1 系统时钟(System clock)UDA1341TS 只能使用从片模式,这就意味着在所有应用中系统设备必须给它提供系统时钟.系统时钟频率是可选择的,可为了256fs,384fs或512fs.系统时钟必须对数字接口信号锁定频率(The system clock must be locked in frequency to the digital interface signals)7.2 针脚兼容性(Pin compatibility)UDA1341TS部分针脚与UDA1340M和UDA1344TS兼容,印刷电路板从UDA1340M升级到UDA1341TS比较简单.与UDA1340M兼容的针脚在FIG.3中标明.7.3 模拟前端(Analog front end)UDA1341TS的模拟前端由两个立体声模数转换器组成,每个转换器有两个通道,通道2有一个可编程增益放大器(PGA),PGA被用来预放大输入通道2的麦克风信号.输入通道1有一个可选择的0或6dB的增益级,通过L3-接口来控制.在这种方式下,1V或2V(有效值)的输入信号(如从一个CD源中输出)可以在输入通道1上串联一个12千欧的外部电阻来支持.下表给出了它的应用模式.使用输入增益级的应用模式--------------------------------------------------------------------------------------------------------电阻(12千欧) 输入增益开关最大输入电压使用0 dB 2V(有效值)输入信号 ps:如果这里没有必要支持2V输入信号,外接电阻就不应被使用使用6 dB 1V(有效值)输入信号不使用 0 dB 1V(有效值)输入信号不使用 6 dB 0.5V(有效值)输入信号---------------------------------------------------------------------------------------------------------7.4 可编程增益放大器(Programmable Gain Amplifier(PGA))PGA可以通过L3接口设置为-3,0,3,9,15,21或27dB7.5 模数转换器(Analog-to-Digital Converter(ADC))UDA1341TS的立体声模数转换器由两个三阶增量调制器组成.它们有一个改进的里齐码结构使用不同的开关电容.过取样率为128.7.6 数字自动增益控制(Digital Automatic Gain Control(AGC))当有一个麦克风信号输入到通道2时,输入通道2有一个数字自动增益控制来压缩动态范围.数字AGC可以用L3接口打开.在打开的状态下压缩动态范围.通过L3接口用户可以设置AGC的参数:启动时间,衰减时间和输出电平.当AGC设置为关时,输入通道2的增益可以手工设置.在这种情况下PGA和AGC组合在一起.输入通道2的范围从-3到60.5dB以0.5dB步进.7.7 自动增益控制状态检测(AGC status detection)当自动增益控制的增益级低于8dB时,数字自动增益中的自动增益状态信号变为高,这个信号可以被用来通过L3接口给PGA一个新的增益设置,或者驱动一个LED.7.8 数字混音器(digital Mixer)两个立体声模数转换器(包括AGC)有四种模式:*只使用ADC1(用做线路输入);输入通道2关闭*只使用ADC2,包括PGA和数字AGC(用做麦克风输入);输入通道1关闭*ADC1+ADC2混合模式,包括PGA和AGC*ADC1+ADC2 double differential 模式(提升ADC性能)要点:为了防止线路输入间串扰,在double differential模式下不应该有信号应用到麦克风输入.在所有模式下(除了double differential模式)一个参考电压一直在ADC的输入上有效,而在double differential模式下却没有.在混合模式下,通道1和通道2的ADC的输出信号可以经L3接口通过一定系数混合.混合系数的范围从0到负无穷dB以1.5dB步进.7.9 抽取滤波器(Decimation filter(ADC))从128fs开始的抽取可以分两阶段进行.第一个阶段实现3阶sin x/x 特性. (The first stage realizes 3rd order sinx/x characteristic), 以16为基抽取.第二个步骤由3个半带滤波器组成,每一个以2为因子抽取.抽取滤波器特性--------------------------------------------------------------------------------项(ITEM) 条件(CONDITIONS) 值(V ALUE(db))通频带波纹0到0.45fs ±0.05抑制频带 >0.55fs -60动态范围0到0.45fs 108总增益输入通道1;0 dB输入 -1.16--------------------------------------------------------------------------------7.10 过载检测(Overload detection(ADC))过载检测这个名字虽合适但有一点不正确.实际上,它的输出表明输出数据比最大可能的数字变化大-1dB(实际上是-1.16dB).无论何时,在何声道.在这种条件下OVERFL输出被强制为高电平持续至少512fs时钟周期(当fs=44.1 kHZ时为11.6ms).每次过载后超时被复位.7.11 静音(Mute(ADC))在从掉电模式后恢复或打开系统时钟时,引脚DATAO的串行数据输出保持低电平直到从抽取滤波器来的有效数据可用.这个时间取决于是否选择了直流消除滤镜.*直流消除关闭 t=1021/fs; 当fs=44.1kHZ时t=23.2ms*直流消除开启 t=12288/fs;当fs=44.1kHZ时t=279ms7.12 内插滤波器(Interpolation filter(DAC))数字滤波器插值从1fs到128fs用一个级联的递归滤波器和一个有限推进响应滤镜.插值滤镜特性-------------------------------------------------项条件值(dB)通带波纹0到0.45fs ±0.03抑制频带 >0.55fs -50动态范围0到0.45fs 108------------------------------------------------7.13峰值检波器(Peak detector)在再现时,内置了峰值检波器.峰值检测位置可以在声音特征设置之前或之后通过L3-接口来设置.峰值检波器实现成像是一个峰值保持检波器,这就表明最高的音级被保存直到被L3-接口读出.在读出后峰值电平寄存器被复位.7.14 快速静音(Quick mute)一个硬件静音可能通过固定的QMUTE引脚激活.当QMUTE设置为高电平时,输出信号被减弱为0.设置QMUTE为低电平时, 快速静音无效.7.15 噪音整形器(Noise shaper(DAC))三阶噪音整形器运行频率为128fs.它将频带内的量化噪声转换成音频带之上的频率.这种噪音整形技术可以提供高信噪比.噪音整形器输出通过一个DAC流滤波器转换成模拟信号. 7.16 DAC流滤波器(Filter Stream Digital-to-Analog Converter(FSDAC))DAC滤波器是一个半数字重构滤镜,可将噪音整形器的一位数据流转换成模拟电压输出.滤镜系数采取当前源并且合计在运算放大器的虚拟地上.这种方法可以达到很高的信噪比和低时钟抖动敏感.因为DAC的内置滤波功能,所以不需要一个后置滤波器.板上放大器将DAC流滤波器的当前输出转换成一个能驱动线路输入的输出电压信号.7.17 多格式输入/输出接口(Multiple format input/output interface)UDA1341TS 支持下列数据格式:*IIS总线,字长可以达到20bits*最高有效位有效的串行格式,字长可达20位.*最低有效位有效的串行格式,字长为16,18或20位*最高有效位有效的输出和最低有效位有效的16,18,20位输入.左声道和右声道字长是时间多工化的.格式如图FIG4所示UDA1341TS允许双倍速数据检测.在这种情况下,重低音,高音和去加重特性不能被使用.然而,音量控制和软静音仍可控.双倍速检测可以通过L3接口设置.位时钟频率必须小于等于64倍字选频率.7.18 L3接口(L3-interface)信息按照L3格式通过微控制器总线进行传输,在这种格式下有两种不同的操作模式,地址模式和传输模式.地址模式需要通过L3总线选择一个设备并且为数据传输模式定义目的寄存器.数据传输可以有两个方向:输入到UDA1341TS中以编码它的声音处理和系统控制特性,或从UDA1341TS中输出来提供峰值.7.19地址模式地址模式用来选择一个设备为了之后的数据传输,并且定义目的寄存器,地址模式被描述为L3MODE保持低电平并且经过8个L3CLOCK脉冲.伴随着8个数据位.基本时序如图FIG.5所示.(L3CLOCK为低电平时进行同步)数据位7到2表示了一个六位的设备地址,第7位为最高有效位,第2位为最低有效位.UDA1341TS的地址是000101.数据位0到1表示之后传输的数据类型(表4).如果UDA1341TS接收了一个不同的地址命令,它会取消所作的选择BIT1 BIT0 MODE TRANSFER0 0 DATA0 直接编址寄存器:音量,重低音,高音,峰值检测位置,去加重,静音和模式扩展编址寄存器:数字混音器控制,自动增益控制,麦克灵敏度控制,输入增益,自动增益时间常数及输出等级0 1 DATA1 读出峰值(从UDA1341TS读到微控制器)1 0 STATUS 复位,系统时钟频率,数据输入格式,直流滤波器,输入增益开关,输出增益开关极性控制,双倍速和电源控制1 1 未使用7.20 数据传输模式在址址模式下激活的选择仍然有效,直到UDA1341TS接收到一个新的地址指令.数据传输的基本时序本质上与地址模式相同,在FIG6中给出 (L3MODE保持高电平,L3CLOCK高电平同步),注意"L3DATA写"指出数据传输从微控制器到UDA1341TS并且"L3DATA峰值读" 指出数据以相反的方向传输.最大的输入时钟和数据传输速率为64fs.所有的传输都是基于8位字节,数据在接收到一个字节的第八位后存储到UDA1341TS中.多字节传输可参照Fig.77.21 编码音频处理及其它特性音频处理和其它特性值存储在独立的寄存器中,通过选择传输的数据类型来对寄存器进行第一道选取,这通过地址模式中的第0位和第1位来完成,第二道选取由数据字节的2或3个最高有效位(第7-6位或7-5位)完成.数据字节中的其它位(BIT5-0,BIT4-0)表示要被存放到已选寄存器的值.对于UDA1341TS 来说可以选取以下模式.*STATUS在这种模式下,复位,系统时钟频率,数据输入格式,直流滤波器,输入增益开关,输出增益开关,极性控制,双倍速和电源控制等特性可以被设置.*DATA0在这种模式下有两种地址模式:直接编址模式和扩展编址模式.直接编址模式使用数据字节的两个最高有效位.在这种地址模式下,音量,重底音,高音,峰值位置, 去加重,静音,模式等特性可以被直接控制.扩展编址模式被用来控制数字混音器,自动增益控制,麦克灵敏度,输入增益,自动增益控制时间系数,自动增益控制输出等级等特性,一个扩展地址可以通过EA寄存器(3位)来设置,扩展寄存器中的值可以通过写数据到ED寄存器(5位)来设置.*DATA1在这种模式下,检测到的峰值可以被读出.Table 5 默认设置符号(SYMBOL) 特性(FEATURE) 设置或值(SETTING OR V ALUE)******Status******OGS 输出增益开关(Output gain switch) 0 dBIGS 输入增益开关(Input gain switch) 0 dBPAD 模数转换极性(Polarity of ADC) 不反转(non-inverting)PDA 数模转换极性(Polarity of DAC) 不反转(non-inverting)DS 双倍速(Double speed) 单倍速(single speed)PC 电源控制(Power control ADC and DAC) 开启(on)******直接控制(Direct control)*******VC 音量控制(V olume control) 0 dBBB 重低音(Bass boost) 0 dBTR 高音(Treble) 0 dBPP 峰值检测位置(Peak detection position) 在音调特性之后(after the tone features)DE 去加重(De-emphasis) 无去加重(no de-emphasis)MT 静音(Mute) 不静音(no mute)M 模式开关(Mode switch) 平坦(flat)******扩展地址编码(Extended programming)******MA 混音器增益通道1(Mixer gain channel 1) -6 dBMB 混音器增益通道2(Mixer gain channel 2) -6 dBMS 麦克敏感度(MIC sensitivity) 0 dBMM 混音器模式开关双微分模式?(double differential mode)AG 自动增益控制(AGC control) 关闭自动增益(disable AGC)AT 自动增益控制启动及衰减时间(AGC attack and decay time) 11ms 和100msAL 自动增益控制输出等级(AGC output level) -9 dB FS7.21.1 STATUS 控制'STATUS'类型数据传输BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 | 寄存器选择(REGISTERSELECTED)------------------------------------------------------------------------------------------------------ 0 RST SC1 SC0 IF2 IF1 IF0 DC RST= 复位(reset)SC=系统时钟频率(system clock frequency(2位))IF=数据输入格式(data input format(3位)) DC=直流滤波器(DC-filter)------------------------------------------------------------------------------------------------------- 1 OGS IGS PAD PDA DS PC1 PC0 OGS=输出增益(6dB)开关(output gain switch) IGS=输入增益(6dB)开关(input gain switch)PAD=ADC极性(polarity of ADC)PDA=DAC极性(polarity of DAC)DS=双倍速(double speed)PC=电源控制(power control)(2位)-------------------------------------------------------------------------------------------------------- 7.21.1.1 复位(Reset)1位值,使用默认设置(系统时钟频率除外)初始化L3寄存器.0: 不复位 1: 复位7.21.1.2 系统时钟频率(System clock frequency)两位值,用来选择外部时钟频率.-----------------------------------------SC1 | SC0 | FUNCTION0 0 512fs0 1 384fs1 0 256fs1 1 未使用------------------------------------------7.21.1.3 直流滤波器(DC-filter)一位值用来使能数字直流滤波器0: 不使用 1:使用7.21.1.4 数据输入格式(Data input format)3位值用来选择数据输入格式-------------------------------------------------------------------------------------IF2 IF1 IF0 FUNCTION0 0 0 IIS总线(IIS-BUS)0 0 1 最低有效位对齐的16位(LSB-justified 16 bits)0 1 0 最低有效位对齐的18位(LSB-justified 18 bits)0 1 1 最低有效位对齐的20位(LSB-justified 20 bits)1 0 0 最高有效位对齐(MSB-justified)1 0 1 最低有效位对齐的16位输入和最高有效位对齐的输出(LSB-justified 16 bits input and MSB-justified output)1 1 0 最低有效位对齐的18位输入和最高有效位对齐的输出(LSB-justified 18 bits input and MSB-justified output)1 1 1 最低有效位对齐的20位输入和最高有效位对齐的输出(LSB-justified 20 bits input and MSB-justified output)---------------------------------------------------------------------------------------7.21.1.5 输出增益开关(Output gain switch)一位值用来控制数模转换器输出增益开关0: 0 dB 1: 6 dB7.21.1.6 输入增益开关(Input gain switch)一位值用来控制模数转换器开关0: 0 dB 1: 6 dB7.21.1.7 模数转换器极性(Polarity of ADC)一位值用来控制模数转换器极性.0: 不反转 1: 反转7.21.1.8 数模转换器极性(Polarrity of DAC)一位值用来控制数模转换器极性.0: 不反转 1: 反转7.21.1.9 双倍速(Double speed)一位值用来使能双倍速再现(playback)0: 单倍速 1: 双倍速7.21.1.10 电源控制(Power control)两位值用来禁用数模转换器和/或模数转换器节电模式.--------------------------------------FUNCTIONPC1 PC0ADC DAC--------------------------------------0 0 off off0 1 off on1 0 on off1 1 on on--------------------------------------7.21.2 DATA0 直接控制DATA0类型数据传输( Data transfer of type ‘DATA0’)------------------------------------------------------------------BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0 REGISTER SELECTED0 0 VC5 VC4 VC3 VC2 VC1 VC0 VC = 音量控制(volume control (6 bits))0 1 BB3 BB2 BB1 BB0 TR1 TR0 BB = 低音增强(bass boost (4 bits))TR = 高音(treble (2 bits))1 0 PP DE1 DE0 MT M1 M0 PP = 峰值检测位置(peak detection position)DE = 去加重(de-emphasis (2 bits))MT = 静音(mute)M = 模式选择(mode switch (2 bits))1 1 0 0 0 EA2 EA1 EA0 EA=扩展地址(extended address (3 bits))1 1 1 ED4 ED3 ED2 ED1 ED0 ED = 扩展数据(extended data (5 bits))7.21.3 DATA0扩展编程寄存器(DATA0 EXTENDED PROGRAMMING REGISTERS) 扩展控制寄存器(Extended control registers)EA2 EA1 EA0 ED4 ED3 ED2 ED1 ED0 REGISTER SELECTED0 0 0 MA4 MA3 MA2 MA1 MA0 MA=混音器增益通道1(mixer gain channel 1 (5 bits)) 0 0 1 MB4 MB3 MB2 MB1 MB0 MB=混音器增益通道2(mixer gain channel 2 (5 bits)) 0 1 0 MS2 MS1 MS0 MM1 MM0 MS=麦克风敏感度(MIC sensitivity (3 bits))MM=混音器模式(mixer mode (2 bits))1 0 0 AG 0 0 IG1 IG0 AG=自动增益控制(AGC control)IG=输入放大器增益通道2(input amplifier gain channel 2 (2 bits))1 0 1 IG6 IG5 IG4 IG3 IG2 IG=输入放大器增益通道2(input amplifier gain channel 2 (5 bits))1 1 0 AT2 AT1 AT0 AL1 AL0 AT=自动增益控制时间常数(AGC time constant (3 bits))AL=自动增益控制输出电平(AGC output level (2 bits))7.21.4 DATA1 控制(DATA1 CONTROL)'DATA1'数据传输类型BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0 读出数据(READ-OUT DATA)PL5 PL4 PL3 PL2 PL1 PL0 峰值电平(peak level value(6 bits))。