秒计时器电路设计

- 格式:doc

- 大小:168.50 KB

- 文档页数:11

60秒计时器的数字电路设计

要设计一个60秒计时器的数字电路,可以使用数频分频器和

计数器来实现。

以下是一种可能的设计方案:

1. 使用一个数频分频器将输入的时钟信号分频为1Hz的信号。

数频分频器可以采用分频比为60的模块,将输入的时钟信号

分频为1Hz信号。

2. 使用一个4位计数器作为分钟计数器,用于计算经过的分钟数。

该计数器从0开始计数,当达到60时,将清零并输出溢

出信号。

3. 使用一个6位计数器作为秒计数器,用于计算经过的秒数。

该计数器从0开始计数,每次计数加1,当达到60时,将清

零并触发分钟计数器加1的操作。

4. 将计数器的输出和显示器连接,以显示当前的分钟和秒数。

通过以上设计,当输入的时钟信号为1Hz时,60秒计时器将

能够准确计时,并在经过60秒后清零重新开始计数。

任务1 指定功能电路器件选型、电路设计、仿真测试

一、任务描述

从元器件清单(附 1)中选择合适的元器件利用电路仿真软件(Multisim)完成指定功能电路的器件选型、仿真设计、仿真测试。

二、任务内容及要求

根据给定元件设计一个秒表电路,来实现物品检测系统内的计时功能。

仿真电路必须由按键控制,时钟信号不能由仿真软件内的信号发生器产生,必须由元件电路输出一个频率为80Hz-100Hz范围内的方波信号。

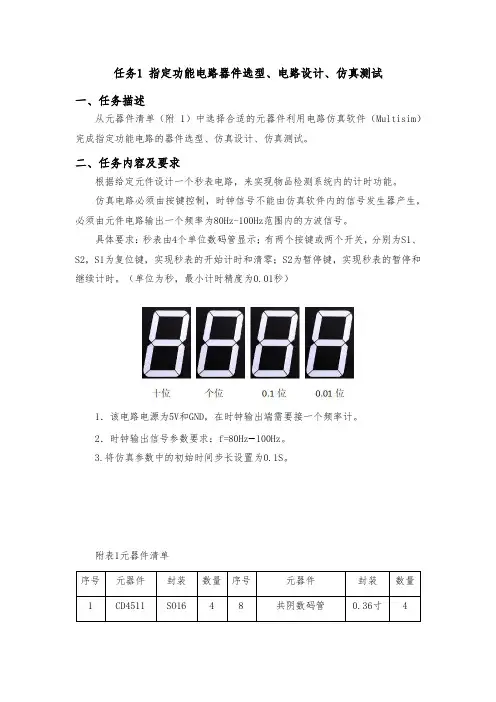

具体要求:秒表由4个单位数码管显示;有两个按键或两个开关,分别为S1、S2,S1为复位键,实现秒表的开始计时和清零;S2为暂停键,实现秒表的暂停和继续计时。

(单位为秒,最小计时精度为0.01秒)

1.该电路电源为5V和GND,在时钟输出端需要接一个频率计。

2.时钟输出信号参数要求:f=80Hz−100Hz。

3.将仿真参数中的初始时间步长设置为0.1S。

附表1元器件清单

三、提交文件

任务完成后,按照下发U盘中的《参赛队提交文件命名要求》文档,将本任务的文件存放在指定U盘中。

一.实验目的理解倒计时器工作原理,实现以中小规模集成电路设计计时器的方法,它是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。

它是由时钟脉冲产生电路、计数电路、译码驱动及显示电路、报时电路及电源电路组成。

时钟脉冲采用555定时器构成多谐振荡电路产生,通过EDA软件Multisim10绘制了电子电路仿真原理图,并进行仿真,同时用万能板焊接制作了硬件实现电路。

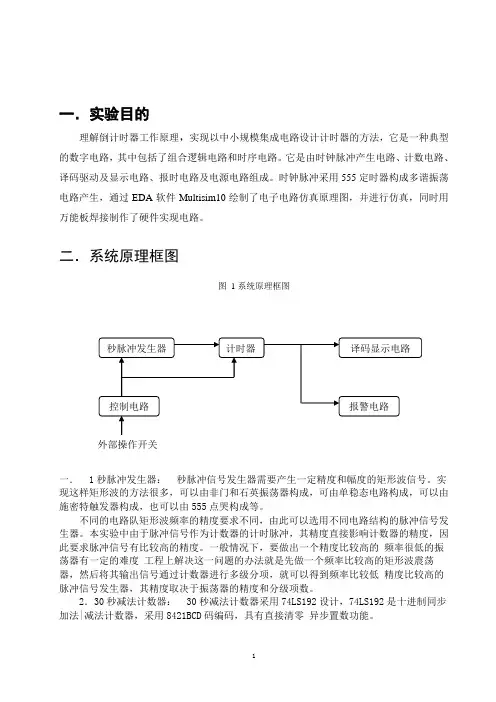

二.系统原理框图图1系统原理框图一.1秒脉冲发生器:秒脉冲信号发生器需要产生一定精度和幅度的矩形波信号。

实现这样矩形波的方法很多,可以由非门和石英振荡器构成,可由单稳态电路构成,可以由施密特触发器构成,也可以由555点哭构成等。

不同的电路队矩形波频率的精度要求不同,由此可以选用不同电路结构的脉冲信号发生器。

本实验中由于脉冲信号作为计数器的计时脉冲,其精度直接影响计数器的精度,因此要求脉冲信号有比较高的精度。

一般情况下,要做出一个精度比较高的频率很低的振荡器有一定的难度工程上解决这一问题的办法就是先做一个频率比较高的矩形波震荡器,然后将其输出信号通过计数器进行多级分项,就可以得到频率比较低精度比较高的脉冲信号发生器,其精度取决于振荡器的精度和分级项数。

2.30秒减法计数器: 30秒减法计数器采用74LS192设计,74LS192是十进制同步加法|减法计数器,采用8421BCD码编码,具有直接清零异步置数功能。

3.控制电路按照系统的要求,电路应该完成以下4个功能;1)当操作直接清零按键时,要求计数器清零。

2)当启动按键闭合时,控制电路应封锁时钟信号CP(秒脉冲信号),同时计数器完成置数功能,显示器显示30秒字样。

当启动按键释放时,计数器开始减法计数。

3)当暂停连续开关处于暂停状态时,控制电路封锁计数脉冲,计数器停止计数,显示器显示原来的数,而且保持不变,当暂停连续开关处于连续状态时,计数器正常计数,另外,外部操作开关都应该采取消抖措施,以防止机械抖动造成电路工作不稳定。

简易数字秒表的电路设计概述及解释说明1. 引言1.1 概述本文主要介绍了一种简易数字秒表的电路设计。

秒表是一种用于计算时间间隔的常见工具,广泛应用于日常生活和各行各业中。

传统的机械秒表用起来不够便捷,因此我们将使用电路设计来实现一个数字秒表,使其更加方便使用。

1.2 文章结构本文分为四个主要部分进行阐述。

首先,在“引言”部分中我们将对文章进行概述和介绍。

接下来,在“简易数字秒表的电路设计”部分中,我们将详细介绍设计原理、电路元件选择与说明以及电路连接与布局等内容。

然后,在“解释说明”部分中,我们将解释秒表功能的实现方法,并探讨其功能扩展可能性,并指出在电路设计过程中需要注意的问题。

最后,在“结论”部分中,我们对本次设计成果进行总结,并就可能存在的改进空间进行分析和未来应用进行展望和思考。

1.3 目的本文旨在通过详细描述并解释简易数字秒表的电路设计,提供一个清晰易懂、全面深入的指南,帮助读者了解该设计思路及其实现方法。

同时,通过对功能扩展可能性的探讨和对电路设计过程中需要注意的问题的分析,可以引导读者在实际应用和改进中做出更好的决策。

最后,通过总结和展望,为未来的研究和发展提供参考思路。

2. 简易数字秒表的电路设计2.1 设计原理:简易数字秒表的电路设计基于计时器和显示器组成。

其主要原理是利用计时器模块产生一个稳定的时间基准,然后将该时间以数字形式显示在显示器上。

2.2 电路元件选择与说明:在设计简易数字秒表的电路时,我们需要选取合适的电子元件来实现功能。

以下是一些常见的元件选择:- 计时器芯片:可选择集成型计时器芯片,如NE555等,它们具有稳定的时钟信号输出。

- 显示屏:一般选用7段LED数码管,由于它们能够直观地显示数字。

- 驱动芯片:如果使用多个7段LED数码管进行显示,则必须选择合适的驱动芯片,如74HC595等。

这些元件经过合理的选择和配套可以实现精确、稳定地测量和显示时间。

2.3 电路连接与布局:简易数字秒表电路连接和布局对功能稳定性有重要影响。

电子技术课程设计报告设计题目:数字显示30秒倒计时器电路设计1、课程设计目的、意义设计目的:(1)依照原理图分析各单元电路的功能;(2)熟悉电路中所用到的1各集成块的1管脚及其功能;(3)进行电路的装接、调试,直到电路能达到规定的设计要求;(4)写出完整、详细的课程设计报告。

设计意义:数字显示30秒倒计时器是一个简单的数字电路,但是它能够扩展到很多实际应用当中来,比如篮球倒计时器、交通灯倒计时器等等。

2、设计题方案比较、论证设计方案:分析设计任务,计数器和操纵电路是系统的要紧部份。

计数器完成30秒计时功能,而操纵电路具有直接操纵计数器的启动设计、译码显示电路的显示和灭灯功能。

当启动开关闭合时,操纵电路应封锁时钟信号CP,同时计数器完成置数功能,译码显示电路显示“30”字样;当启动开关断开时,计数器开始计数;处于维持状态。

系统设计框图如图2-1所示。

数字显示30秒倒计时器实验电路如图2-2所示。

图2-1图2-23、各单元电路设计,元器件参数计算、选择、电路图绘制,整体电路图递减计数器模块计数器选用汇总规模集成电路74LS192进行设计较为简单,74LS192是十进制可编程同步加锁计数器,它采纳8421码二-十进制编码,而且有直接清零、置数、加锁计数功能。

图2-3是74LS192外引脚。

图中CPU 、CPD别离加计数、减计数的时钟脉冲输入端(上升沿有效)。

LD是异步并行置数操纵端(低电平有效),CO、BO别离是进位、借位输出端(低电平有效),CR是异步清零端,D3-D是并行数据输入端,Q3-Q是输出端。

74LS192的功能表见下表所示。

秒信号产生器秒信号产生器的电路是利用 555 按时器(图3-1)组成的秒信号发生器。

NE555 芯片有单稳态电路功能,可发生方波信号,可适当的选择电阻、电容,使其输出信号的周期为 1 秒。

本电路输出脉冲的周期为:T=*(R1+2*R2)*C,假设 T=1s,令 C=10μF,R1=39kΩ,那么R2=51k Ω。

24秒倒计时器的设计和制作一、计时器概述1、计时器的特点及应用24秒倒计时。

24秒计数芯片的置数端清零端共用一个开关,比赛开始后,24秒的置数端无效,24秒的倒数计时器的倒数计时器开始进行倒计时,逐秒倒计到零。

选取“00”这个状态,通过组合逻辑电路给出截断信号,让该信号与时钟脉冲在与门中将时钟截断,使计时器在计数到零时停住。

2、设计任务及要求1、用小规模集成电路设计24秒倒计时电路;2、用555定时器产生1Hz的标准脉冲信号;3、当计时器显示00,同时报警;4、计时器应具有清零、启动、暂停/继续计时等控制功能。

二、电路设计原理及单元模块1、设计原理24秒计时器的总体参考方案框图如图1所示。

它包括秒脉冲发生器、计数器、译码显示电路、报警电路和辅助时序控制电路(简称控制电路)等五个模块组成。

图1—方案框图其中计数器和控制电路是系统的主要模块。

计数器完成24秒计时功能,而控制电路完成计数器的直接清零、启动计数、暂停/连续计数、译码显示电路的显示与灭灯、定时时间到报警等功能。

秒脉冲发生器产生的信号是电路的时钟脉冲和定时标准,但本设计对此信号要求并不太高,故电路可采用555集成电路或由TTL与非门组成的多谐振荡器构成。

译码显示电路由74LS48和共阴极七段LED显示器组成。

报警电路在实验中可用发光二极管和鸣蜂器代替。

2、设计方案此计时器的设计采用模块化结构,主要由以下3个组成,即计时模块、控制模块、以及译码显示模块。

在设计此计时器时,采用模块化的设计思想,使设计起来更加简单、方便、快捷。

此电路是一时钟产生,触发,倒计时计数,译码显示、报警为主要功能,在此结构的基础上,构造主体电路和辅助电路两个部分。

3、单元模块3.1各个元器件功能3.1.1、555定时器555 定时器的内部电路框图如图3-1-1所示。

图3-1-1 555内部电路框它内部包括两个电压比较器,三个等值串联电阻,一个RS 触发器,一个放电管T 及功率输出级。

计时器电路设计方案1 总体电路结构设计1.1 电路功能与性能计时器电路的功能主要集中在五方面。

一是对按键消抖的控制(电平检查、消抖命令延时、消抖完成前延时、完成消抖后平稳电平输出等)为主的输入信号的采集与处理;二是对输入全局时钟分频,获取所需时钟;三是进行时间的正常计时和可以调整时间,如正常的记录时、分、秒,可以准确调时、分、秒等;四是正常利用八位数码管进行译码显示;五是处理维护和配置信息,如层停留时间、运行速度等信息。

电路的具体功能细节罗列如下:1)计时电路输入10KHZ的基准时钟,利用10K计数器和200计时器进行计数分频,获取1HZ的自动扫描计时时钟及50Hz的数码管扫描时钟。

2)消抖模块分为电平检查和10ms延时;通过按键输入电平信号,检查模块对电平进行检测,发送所需脉冲,若10ms延时模块检测到所发脉冲,并对该脉冲进行触发10ms的过滤抖动,然后输出正常脉冲信号。

3)经过按键消抖发出的平稳电平信号,校时模块就会对获取相应管脚约束所发送的按键信号,并进行时、分、秒的调整。

4)计时模块采用24进制计数器,10进制计数器,6进制计数器分别对时分秒高低位计数,检测到时钟分频器所分的1HZ时钟信号便自动开始扫描计时,自动产生进位计数。

5)利用多路选择器,即多路复用器,进行对时分秒高位地位进行选通,并发送到译码显示器,进行数字输出。

6)利用八位数码管显示输出,采取七段数码管译码方式对0~9进行译码输出。

7)电路根据流水线设计方法,按键消抖和计时器运行状态……8)配置信息通过……,目的计时信号处理……。

1.2 主要按键消抖法本电路设计的主要难点在于按键的消抖及调整时分秒上,也就是如何获取稳定的电平信号进行时间调整。

经过功能分析,决定采用电平检查及消抖延时的方式进行调度与输出控制。

其中电平检测模块会根据电平发生变化产生的不同命令,然后进入延时模块当中。

接着,延时模块会根据输送进入的命令在执行相关的延时操作并且进一步决定输出。

赣南师院物理与电子信息学院数字电路课程设计报告书姓名:班级:学号:时间:图1 总原理框图1.1 555定时器555定时器是一种多用途的数字-模拟混合集成电路,用它可以构成施密特触发器、单稳态触发器和多谐振荡器。

本设计用LM555CM定时器设计一个多谐振荡器给电路提供脉冲信号,产生的脉冲信号用由74LS192进行计数,且设置周期为1秒。

1.1.1555定时器管脚名称和功能图2 555的管脚名称1脚为接地端,也是芯片的公共端。

2脚为C2比较器的信号输入端V2l又称为触发端。

它们输入的信号可以图3 555定时器的内部结构1.1.3 555定时器的功能表输入各级输出T 1状态D RV 1l V 2L V 1C V 2C触发器输出Q 1+n输出V OT 1状态0 ⨯ ⨯ ⨯ ⨯0 低电平 导通 1 (32)V CC (31V CC ) 0 1 0 低电平 导通 1 (32)V CC (31V CC ) 0 0 1 高电平 截止 1 (32)V CC (31V CC ) 1 0 0 高电平 截止 1(32)V CC (31V CC ) 11Q不变不变表1 555定时器的功能表1.274LS192十进制同步加减计数器图5 74LS192的内部结构图1.2.374LS192的功能表表2 74LS192的功能表1.374LS48七段译码器本设计中用共阴极七段显示数码管,为使七段显示数码管能正常工作,将74LS190连接到74LS48,74LS48将高低电平信号译成数码管可读信号,从而实现数字的显示。

1.3.174LS48的引脚排列图6 74LS48的引脚排列1.3.274LS48的真值表表3 74LS48的逻辑功能真值表1.4共阴极数码管数码管有共阴和共阳之分,本设计使用共阴数码管,因为译码器使用为74LS48,相应的数码管要用相应的译码器才能实现译码和显示数字。

1.4.1共阴数码管的引脚排列和简易符号图7 八段共阴数码管图8 数码管简易图1.4.2 共阴数码管的内部结构图9 共阴数码管内部结构2电路分析和仿真结果由上对各个元件进行的简介以及相关的原理图,下面对电路进行分部分析。

电子秒表的设计摘要:目前数字电子技术已经广泛地应用于计算机,自动控制,电子测量仪表,电视,雷达,通信等各个领域。

例如在现代测量技术中,数字测量仪表不仅比模拟测量仪表精度高,功能强,而且容易实现测量的自动化和智能化。

随着集成技术的发展,尤其是中、大规模和超大规模集成电路的发展,数字电子技术的应用围将会更广泛地渗透到国民经济的各个部门,并将产生越来越深刻的影响。

随着现代社会的电子科技的迅速发展,要求我们要理论联系实际,数字电路课题设计的进行使我们有了这个非常好的机会,通过这种综合性训练,我们的动手能力、实际操作能力、综合知识应用能力得到了更好的提升。

本次毕业设计的题目是电子秒表.电子秒表是用于测量较短且较精确的时间,它在体育运动项目上有着广泛的应用.本次设计中应用了多种数字电路中的单元电路,如基本RS触发器、单稳态触发器、时钟发生器及计数器,译码显示器等.我相信通过本次实验,将进一步加深对各数字单元电路的理解,同时也对基础电子设计有一定的了解,为今后的学习和工作打下一定的基础。

关键词:电子秒表;基本RS触发器;单稳态触发器;时钟发生器;计数器;译码显示器The Design of Digital StopwatchAbstract:Current digital electronics technology has been widely used in computers, automatic control, electronic measuring instruments, TV, radar, communications and other fields. For example, in the modern measurement technology, digital measuring instrument is not only accurate than analog gauges, powerful, and easy measurement of automation and intelligence. With the integration of technology, particularly in large-scale and ultra large scale integrated circuit development, application of digital electronic technology will be more widely infiltrated into all sectors of the national economy, and will have more profound impact. With modern society, the rapid development of electronic technology, requires us to integrate theory with practice, digital circuit design the project so that we have this great opportunity, through this comprehensive training, our ability, practical skills, ability of comprehensive knowledge applications get better promotion.The course design is the subject of electronic stopwatch. Stopwatch is a shorter and more accurate for measuring time, it projects in sports has been widely used. The design of the application of a variety of digital circuit elements in the circuit, such as basic RS flip-flop, one-shot, the clock generator and counter, decoder display. I believe that through this experiment, will further deepen the understanding of the digital cell circuits, but also on the basis of a certain electronic design understanding for future study and work to lay a certain foundation.Keywords: electronic stopwatch, the basic RS flip-flop, one-shot, the clock generator, counters, decoding display目录1 电子秒表介绍.................................... 错误!未定义书签。

一、概述及设计目的 (4)1.1 概述 (4)1.2 设计目的 (5)二、设计思路 (6)三、设计过程 (7)3.1 方案论证 (7)3.2 电路设计 (14)四、系统调试与结果 (16)五、主要仪器与设备 (18)六、设计体会 (19)数字时分秒计时器设计1、概述及设计目的1.1 概述近年来随着科技的飞速发展,EDA的应用正在不断地走向深入。

时分秒计时器的出现,解决了人们的时间意识问题,更是给人们提供了精确的时间观念,不会因为时间问题而发生纠纷。

时分秒计时器是日常学习生活、电器制造,工业自动化控制、国防、实验等等的理想计时器。

本设计的时分秒计时器系统采用EDA软件绘图,利用计数原理,结合显示电路、电源电路设计计时器,将软件和硬件有机地结合起来,使得系统能够实现数字显示,显示时间为时分秒计数,每秒自动加1,满59秒自动向分钟位进位,秒位清零,满59分钟自动向时位进1,分秒位清零,满12小时全部清零,重新计算,能够精确地进行时间计数。

其中硬件系统可以采用VHDL语言编写程序,也可以采用绘图形式,十二进制,六十进制并在EDA环境中进行观察,在仿真中就可以观察到实际的工作状态,调试波形就可以观察到程序运行结果。

系统主要功能:时钟功能,在数码管上显示小时,分钟,秒钟。

当其单位定位秒当期计数显示59秒时再来一个脉冲秒钟清零并向分钟进一,以此类推,当满59分59秒时,再来一个脉冲则分钟秒钟清零并向小时进一,当计数为11时59分59秒时,则全部清零,重新计数。

该时分秒计时器的显示有计数器的每位分别接给译码器再由显示管显示数字,以便观察。

1.2设计目的1、学习数字电路中的基本器件、计数器及译码显示等单元电路的综合应用。

2、学习电子钟的调试方法。

3、巩固和加深对MAXPLUSII CPLD开发系统的理解和应用。

4、掌握硬件实验装置的方法。

5、掌握综合性电路的设计、仿真、下载、调试方法。

1.3功能时分秒计时器集成了计数器、译码器和驱动等电路,能对时间进行精确地计时,具有清零等控制功能。

目录一、计时器概括 (1)1、计时器的特色及应用 (1)2、设计任务及要求 (1)二、电路设计原理及单元模块 (1)1、设计原理 (1)2、设计方案 (2)3、单元模块 (3)3.1、所用各个芯片功能 (3)3.2、各单元电路 (7)四、安装与调试 (11)1、电路的安装 (11)2、电路的调试 (12)五、结论与心得 (12)六、参照文件 (13)1、总电路图 (14)2、元件清单 (14)3、实物 (15)24秒倒计时器的设计和制作一、计时器概括1、计时器的特色及应用在很多领域上当时器均获得广泛应用,诸如在体育竞赛,准时报警器、游戏中的倒时器,交通讯号灯、红绿灯、行人灯、交通纤毫控制机,还能够用来做为各样药丸、药片,胶囊在指准时间提示用药等等,因而可知计时器在现代社会的应用是相当广泛的。

在篮球竞赛中,规定了球员的持球时间不可以超出24 秒,不然就违例了。

本课程设计“智能篮球竞赛倒计时器的设计”,可用于篮球竞赛中,用于对球员持球时间 24 秒限制。

一旦球员的持球时间超出了24 秒,它自动的报警进而判断此球员的违例。

2、设计任务及要求设计一个 24 秒倒计时器,详细功能要求以下:1、用小规模集成电路设计24 秒倒计时电路;2、用 555 准时器产生 1Hz 的标准脉冲信号;3、当计时器显示00,同时报警;4、计时器应拥有清零、启动、暂停/持续计时等控制功能。

二、电路设计原理及单元模块1、设计原理24 秒计时器的整体参照方案框图如图 1 所示。

它包含秒脉冲发生器、计数器、译码显示电路、报警电路和协助时序控制电路(简称控制电路)等五个模块构成。

其上当数器和控制电路是系统的主要模块。

计数器达成24 秒计时功能,而控制电路达成计数器的直接清零、启动计数、暂停 /连续计数、译码显示电路的显示与灭灯、准不时间到报警等功能。

秒脉冲发生器产生的信号是电路的时钟脉冲和准时标准,但本设计对此信号要求其实不太高,故电路可采纳555 集成电路或由TTL 与非门构成的多谐振荡器构成。

电子设计报告秒表倒计时电路小组成员:目录设计的任务 (3)设计方案选择 (4)设计思路 (5)电路仿真 (7)主要元器件与参数 (11)电路焊接 (12)失败与改进 (14)收获体会和想法 (15)设计的任务秒表倒计时电路设计要求:1.设计一个秒表倒计时电路,计时最大值为59秒,每隔一秒钟减1,最小值为0秒,接着再回到59秒,58秒,57秒,……,0秒,59秒,58秒,57秒,如此循环往复。

2.采用7段数码管显示时间。

3.可能的话,在上述要求的基础上进行相关扩展功能的设计。

4.先进行原理分析与方案选择,采用仿真软件(比如Proteus或Quartus)进行设计;功能实现后,设计并制作实际电路并进行调试,完成一份设计报告。

相关知识:1.计数器集成电路如74191的使用方法。

2.555电路的应用。

3.数码管、7段显示译码器电路的使用。

设计方案选择模块1、脉冲电路采用555电路构成多谐震荡器。

由于T=(2*R1+R2)*C。

经过计算采用R1=R2=1000K。

C=0.47UF。

再加上0.01uf的电容。

就设计出由555构成的多谐震荡器产生1秒的脉冲。

模块2、计数电路采用74LS190构成计数器。

通过74LS04等门电路构成反馈置数电路。

通过反馈回路使其计数到一定时候置数。

模块3、显示电路由计数器输出信号通过CD4511译码和驱动共阴数码管,由数码管显示数字。

设计思路题目要求:秒表倒计时基本设计:1、由振荡器产生脉冲输入到计数器2、计数器计数并将计数的信号输入到数码管驱动器。

3、由数码管驱动器CD4511驱动数码管现实当前数值。

4、计数器通过各种门电路产生反馈回路。

扩展设计:1、计时开始开关:由开关控制振荡器的脉冲输入到计数器即可实现。

2、正向与反向计时:通过开关的开合选着正向计时(1、2、3…59、0…)与反向计时(59、58、57…0、59…)。

由于正向计时置数是59到0。

反向计时的置数是0到59。

时、分、秒计时器的设计一、实验目的掌握数码管动态显示的基本方法;掌握键盘按键控制的实现方法;根据已知电路和设计要求在实验板上实现时、分、秒计时器。

二、实验内容1、在STC89C52实验平台上实现时、分、秒时钟,4位数码管上显示分、秒或者时、分。

2、应用键盘控制时间的显示。

键盘按键控制“切换时分、分秒显示”、“启动停止”、“加秒显示内容”、“加分显示内容”、“加时显示内容”。

3、根据已知电路和设计要求在PROTEUS平台仿真实现时钟系统。

三、实验原理流程图如下所示:11、主程序流程图2、定时器/计数器T0中断服务程序流程图5 仿真分析在Proteus ISIS的80C51中载入程序生成的HEX文件,按开始符号运行,在数码管上观察程序运行结果,系统仿真结果如图5.1所示。

设计功能如下:(1)、初始状态:未按键之前,上电,数码显示00-00-00。

程序运行后,从秒针开始自动运行。

当秒数到59后,下一秒自动变为00,分针变为01,以此类推。

(2)、调整状态:仿真运行过程中,按p0键,系统暂停,此时,继续按p0无效。

第三次按p0,又开始,如此循环。

(3)、设置状态:按下p0暂停后,按p1,则时针加一,按下p2,则时针减一;按两下p0,在按下p1,则分针加一,按下p2,则分针减一。

时间显示格式为:时分秒;误差分析:实际程序到实验板中的电子钟显示存在一定的误差,误差来源可能为三个方面:第一,在程序运行过程中,时钟周期的不精确导致机器周期与理论值存在一定的差别;第二在中断一秒显示过程中,一些指令需要消耗一定的机器周期,使得一秒延时比实际要长;第三在键抖动的反应程度在运行中比较慢。

25.1实例仿真总结通过这次的课程设计我认识到我对单片机的知识学的太少了,对于书本上很多知识还不能灵活运用,都需要去巩固加强,我会在以后的学习中弥补我的不足。

我也了解了80C51集成环境和PROTEUS仿真软件的使用,用此软件练习电子时钟的设计,不仅使我熟悉了软件的使用方法,而且复习了单片机编程的相关知识。

5秒倒计时电路设计

以下是一个5秒倒计时电路的设计方案:

1. 使用555定时器芯片作为计时核心。

将555定时器的R1和R2电阻设为100kΩ,C为0.1μF。

2. 使用CD4017计数器芯片作为计数器。

将计数器的CLOCK输入连接到555定时器的OUT 输出。

3. 将CD4017计数器的Q0-Q4输出依次连接到LED灯或蜂鸣器。

4. 设计一个简单的开关电路,将开关与555定时器的RESET引脚连接,使之在开始计时前将RESET引脚拉高。

实现方法如下:

1. 连接555定时器的1号脚和5号脚,形成一个内部电容充电电路。

2. 将100kΩ电阻连接到2号脚和6号脚之间。

将另一个100kΩ电阻与2号脚相连,并将它与C2电容相连。

将另一个端连接到6号脚。

3. 将10kΩ可变电阻连接到2号脚和电源正极之间。

4. 将0.1μF电容连接到5号脚和电源负极之间。

5. 将CD4017计数器的CLOCK脚连接到555定时器的OUT输出。

6. 将CD4017计数器的Q0-Q4输出依次连接到LED灯或蜂鸣器。

7. 将一个开关连接到555定时器的RESET引脚,使之在开始计时前将RESET引脚拉高。

以上是一个基础的5秒倒计时电路设计方案,具体实现时需要根据电路需求进行相应的调整。

100秒倒计时电路设计

想设计一个100秒计时的电路,到底要怎么做,那么你想知道100秒倒计时电路设计是怎么样的吗?下面就由店铺为你带来100秒倒计时电路设计,希望你喜欢。

100秒倒计时电路设计图

100秒倒计时电路设计步骤

1.打孔:4角及变压器固定孔直径3.2mm;按钮开关固定孔直径2mm,安装孔直径1.2mm;1N4001安装孔直径1.2mm;其它孔直径1mm。

2.集成电路注意缺口位置;

3.电解电容器及二极管注意正负极;

4.表贴电阻焊在PCB板的底层;

5.安装7805注意有字面向下;

6.电阻器和普通电容器没有极性;

7.变压器初级焊上带插头的电源线,并用绝缘胶布包好接头,次极焊上插头后插在2PIN插座上。

数字电路课程设计说明书学院名称:班级名称:学生姓名:学号:题目:指导教师姓名:起止日期:目录第一部分:正文部分 (1)一、选题背景 (1)二、方案论证 (1)2.1 功能要求 (1)2.2 实现方案 (1)三、过程论述 (1)3.1倒计时计数器 (2)3.2 秒脉冲产生电路 (3)3.3 信号转换器 (4)3.4 完整电路图 (5)四、结果分析 (5)五、结论 (7)第二部分:图纸部分 (7)一、电路图纸 (7)二、元件清单 (8)第三部分:参考文献 (8)第四部分:指导教师评语 (9)第五部分:成绩评定 (9)第一部分:正文部分一、选题背景随着“秒时代”的到来,人们的生活也更加精准和快捷,对计时准确性和可靠性的要求越来越高。

人类社会正处于高度发达的信息化社会,而信息化社会的进步又离不开电子产品的进步与革新。

随着工业水平的飞速发展,在很多领域需要集成数以万计的电子器件来控制和操作多种繁琐的操作和功能,从而提高生产的效率,促进经济的发展。

计时器在生活中的应用极其广泛,不胜枚举。

诸如各项运动赛事的计时,定时警报,交通信号灯,以及各种航空航天、智能家居等多领域的计时功能,它已经渗透到了我们生活的大大小小各个方面,成为科学技术发展不可或缺的重要组成之一。

本设计应用基本数字电路知识,用数码管作倒计时显示,最终实现从59s~00s的倒计时功能。

二、方案论证2.1 功能要求(1)能够实现从59到00的60秒倒计时计数功能,时间间隔为1秒,数码管显示计数值;(2)提供外部操作开关,控制计数器的开始计数功能;(3)计数器递减计时,到00时,发光二极管点亮提示计数结束。

2.2 实现方案依据功能要求,该秒计数器系统主要应由秒脉冲信号发生器、倒计时计数电路以及信号转换器组成,原理框图如图1所示。

秒脉冲信号发生器是该系统中的倒计时计数电路的标准时钟信号源。

倒计时计数器输出一组驱动信号T0,然后点亮发光二极管提示计数结束。

《电子技术》课程设计报告班级通信1131 学号 1131302202学生姓名于淼专业通信工程系别电子信息工程系指导教师电子技术课程设计指导小组淮阴工学院电子与电气工程学院2015年1月1.设计目的a) 培养理论联系实际的正确设计思想,训练综合运用已经学过的理论和生产实际知识去分析和解决工程实际问题的能力。

b)学习较复杂的电子系统设计的一般方法,了解和掌握模拟、数字电路等知识解决电子信息方面常见实际问题的能力,由学生自行设计、自行制作和自行调试。

c)进行基本技术技能训练,如基本仪器仪表的使用,常用元器件的识别、测量、熟练运用的能力,掌握设计资料、手册、标准和规范以及使用仿真软件、实验设备进行调试和数据处理等。

d)培养学生的创新能力。

2.设计要求1)电源+5V;2)主要单元电路和元器件参数计算、选择;要求计时电路递减计时,每隔1秒钟,计时器减1;3)设置外部操作开关,控制计时器的清零、启动和暂停/连续计时,报警;4)画出总体电路图;5)安装自己设计的电路,按照自己设计的电路,在通用板上焊接。

焊接完毕后,应对照电路图仔细检查,看是否有错接、漏接、虚焊的现象。

3.总体设计3.1篮球竞赛30秒定时器的设计流程图图1-1 设计流程图3.2组成部分及可选电路本实验主要由译码显示单元电路、三十进制计数器电路、多谐振荡器电路、辅助时序控制电路等组成。

译码显示单元电路由两个4511译码器和七段显示共阴极数码管来组成;三十进制计数电路选用两片74LS192进行设计;采用555器件构成多谐振荡器;辅助时序控制电路利用两个74HC00N器件构成多个与非门实现。

3.3总框图(如图1-2所示)图1-2 总框图3.4本设计主要的功能1)能够利用阴极数码管显示30秒倒计时功能;2)系统设置外部操作开关,控制定时器的清零、启动和暂停(或连续)功能;在清零时,数码管显示器灭灯;定时器为30秒递减计时,其计时间隔为1秒,也就是每隔1秒,定时器就减1,直到显示器的显示为00;定时器递减计时到零时,数码管显示器不灭灯。

数字电路课程设计说明书

学院名称:

班级名称:

学生姓名:

学号:

题目:

指导教师

姓名:

起止日期:

目录

第一部分:正文部分 (1)

一、选题背景 (1)

二、方案论证 (1)

2.1 功能要求 (1)

2.2 实现方案 (1)

三、过程论述 (1)

3.1倒计时计数器 (2)

3.2 秒脉冲产生电路 (3)

3.3 信号转换器 (4)

3.4 完整电路图 (5)

四、结果分析 (5)

五、结论 (7)

第二部分:图纸部分 (7)

一、电路图纸 (7)

二、元件清单 (8)

第三部分:参考文献 (8)

第四部分:指导教师评语 (9)

第五部分:成绩评定 (9)

第一部分:正文部分

一、选题背景

随着“秒时代”的到来,人们的生活也更加精准和快捷,对计时准确性和可靠性的要求越来越高。

人类社会正处于高度发达的信息化社会,而信息化社会的进步又离不开电子产品的进步与革新。

随着工业水平的飞速发展,在很多领域需要集成数以万计的电子器件来控制和操作多种繁琐的操作和功能,从而提高生产的效率,促进经济的发展。

计时器在生活中的应用极其广泛,不胜枚举。

诸如各项运动赛事的计时,定时警报,交通信号灯,以及各种航空航天、智能家居等多领域的计时功能,它已经渗透到了我们生活的大大小小各个方面,成为科学技术发展不可或缺的重要组成之一。

本设计应用基本数字电路知识,用数码管作倒计时显示,最终实现从59s~00s的倒计时功能。

二、方案论证

2.1 功能要求

(1)能够实现从59到00的60秒倒计时计数功能,时间间隔为1秒,数码管显示计数值;

(2)提供外部操作开关,控制计数器的开始计数功能;

(3)计数器递减计时,到00时,发光二极管点亮提示计数结束。

2.2 实现方案

依据功能要求,该秒计数器系统主要应由秒脉冲信号发生器、倒计时计数电路以及信号转换器组成,原理框图如图1所示。

秒脉冲信号发生器是该系统中的倒计时计数电路的标准时钟信号源。

倒计时计数器输出一组驱动信号T0,然后点亮发光二极管提示计数结束。

倒计时计时电路是系统的关键组成部分,由它来控制信号转换器的工作。

图1 秒计时器原理框图

三、过程论述

3.1倒计时计数器

该系统核心部分就是倒计时计数器。

具体工作方式为:事先置数后,按下开始开关,显示器显示初始值,然后以每秒减1的计数方式工作,直至减到两个数码管显示的值为“00”时,计数器计数工作停止,并向信号转换器提供T0信号,点亮发光二极管,提示计数结束。

倒计时显示采用七段数码管作为显示,它由计数器驱动并显示计数器的输出值。

计数器选用集成电路74LS192进行设计。

74LS192是一种典型的高性能、低功耗CMOS4位同步二进制加计数器,除了具有这个功能外还有并行数据的同步预置功能,时钟脉冲CLK是计数脉冲输入端,也是芯片内4个触发器的公共时钟输入端,CLR为异步清零端,当它为低电平时,无论其输入端为何种状态,都使片内所有触发器状态置0,LOAD为并行置数使能端,当它为低电平时,数据输入端D3~D0的逻辑值置入计数器。

B0为借位输出端。

CO为进位输出端。

其功能表如图2所示:

表1 74LS192功能表

要实现60秒的倒计时,需选用两个74LS192芯片级联成一个从99倒计到00的计数器,当清除端CR为高电平“1”时,计数器直接清零;CR置低电平则执行其它功能。

当CR为低电平,置数端LD也为低电平时,数据直接从置数端D0、D1、D2、D3置入计数器。

当CR为低电平,LD为高电平时,执行计数功能。

执行加计数时,减计数端CPD接高电平,计数脉冲由CPU输入;执行减计数时,加计数端CPU接高电平,计数脉冲由减计数端CPD输入。

因此该电路设计将用到的计数器由两片74LS192同步十进制可逆计数器构成。

利用借位输出端BO与下一级的CPD连接,实现计数器之间的级联。

利用预置数LD端实现异步置数。

当RD=0,且LD=0时,不管CPU和CPD时钟输入端的状态如何,将使计数器的输出等于并行输入数据,即Q3Q2Q1Q0=D3D2D1D0。

例如本设计要求60秒倒计时,故预置数为(01011001)2 =(59)10 。

电路连接如图3所示:

图2计时电路

3.2 秒脉冲产生电路

秒脉冲产生电路的功能是产生标准秒脉冲信号,主要由振荡器和分频器组成。

本方案采用555定时器与RC组成多谐振荡器。

555谐振电路能自发产生一定占空比的脉冲信号,调整其中R1、R2的值,从而得出本实验想要的输入脉冲。

接通VCC后,VCC经R1和R2对C充电。

当2号输入的VC上升到2VCC/3时,V0=0,T导通,C通过R2和T放电,VC下降。

当VC下降到VCC/3时,V0又由0变为1,T截止,VCC又经R1和R2对C充电。

如此重复上述过程,在输出端V0产生了连续的、周期为1秒的矩形脉冲,从而为计时器提供触发信号,其中,可以通过R1、R2、C1、C2来控制放电时间,相关参数计算为:

多谐振荡器的振荡周期T=0.7*((R1+R2)*C1)

各参数的值为:R1=200K,R2=200K C1=10nF C2=100nF

各参数的值带入上述公式得: T=0.9999s

其电路连接如图4所示:

图3振荡器电路

3.3 信号转换器

本方案采用三输入与门74LS11作为信号转换器,其功能表如下:

表2 74LS11功能表

输入输出

A B C Y

××L L

×L ×L

L ××L

H H H H

3.4 完整电路图

图4 倒计时电路设计四、结果分析

打开Multisim,连接好电路图后,仿真结果如下:

(1)初始置数为“59”,按下开关,开始计数:

图5 系统开始工作状态图

(2)倒计时直至显示为“00”,发光二极管亮提示计数结束:

图6 系统结束工作状态图

在仿真实验过程中,计时器以每秒减1的速度倒计时,并将实时结果显示在两个数码管上,直到数码管显示“00”,发光二极管被点亮,计时停止。

此过程中系统运行稳定,效果与预想基本吻合,说明该电路的设计是符合该课程设计的题目要求的,达到了实验目的。

在功能拓展上,因为生活中许多方面都有秒计时器的应用,故可以考虑很多种不同类型的功能设计,比如在此设计的基础上,构建一个信号灯控制器即可组成交通灯信号控制系统;增加一个蜂鸣器可组成定时报警系统;加上加、减、保持等操作可组成篮球计时系统等。

五、结论

在这次课程设计中,我学会了用Multisim软件画电路图,而且学会了设计一些简单的电路图,但是由于所学知识目前仍十分有限,因此对于复杂的电路理解起来还有很大的难度,对于一些芯片和工具的使用还是不熟练。

开始时我遇到的最大的问题就是选用什么样的元件了,看着这个也能用、却也不会用,再看那个也是如此。

可是经过几次的试验才发现同一个元件不同种用法会更简单,这也许是对其更深入的了解吧。

其次,通过这次的课程设计,让我加深了对模拟电子技术、数字电子技术的原理的理解。

仅仅通过课本和课堂的途径来汲取知识是远远不够的,自己一定要动手操作。

对于那些复杂的电路图,可以从图中的每一小部分去分析再了解整个电路。

虽然耗费的时间比较长,但是最终设计方案能够完全符合设计要求,让我有了极大的自豪感,也激发了我对这门课程的热情与兴趣。

在以后的日子,更应该着重自己动手能力的提高,专业本身就是一门需动手操作的,对那些复杂的电路图,一定要敢于去分析,并动手去操作。

但同时,在这次试验中发现了许多自身的不足,如理论知识不扎实,很多原理都不懂,希望老师在以后的教学中能够更多地结合实际操作来为我们解答疑难。

第二部分:图纸部分

一、电路图纸

图7完整电路图

二、元件清单

1.74LS192 *2

2.LM555C *1

3.74LS11 *1

开关 *1 5.七段数码管 *2 6.发光二极管 *1

7.电阻 *3 8.VCC 5V

第三部分:参考文献

1.王连英.基于Multisim 10的电子仿真实验与设计. 北京:北京邮电大学出版社,2009.8;

2.唐小华等. 数字电路与EDA实践教程. 北京:科学出版社,2010.8;

3.余孟尝. 数字电子技术基础简明教程(第三版).北京:高等教育出版社,2006.7。

学生签名:填表日期:年月日

第四部分:指导教师评语

第五部分:成绩评定

指导教师签名:填表日期:年月日

9。