一种雷达通用信号处理系统的实现与应用

- 格式:pdf

- 大小:111.10 KB

- 文档页数:8

雷达系统中的信号处理技术摘要本文介绍了雷达系统及雷达系统信号处理的主要内容,着重介绍与分析了雷达系统信号处理的正交采样、脉冲压缩、MTD和恒虚警检测几种现代雷达技术,雷达系统通过脉冲压缩解决解决雷达作用距离和距离分辨力之间的矛盾,通过MTD来探测动目标,通过恒虚警〔CFAR〕来实现整个系统对目标的检测。

关键词雷达系统正交采样脉冲压缩MTD 恒虚警检测1雷达系统概述雷达是Radar〔Radio Detection And Ranging〕的音译词,意为“无线电检测和测距”,即利用无线电波来检测目标并测定目标的位置,这也是雷达设备在最初阶段的功能。

雷达的任务就是测量目标的距离、方位和仰角,还包括目标的速度,以及从目标回波中获取更多有关目标的信息。

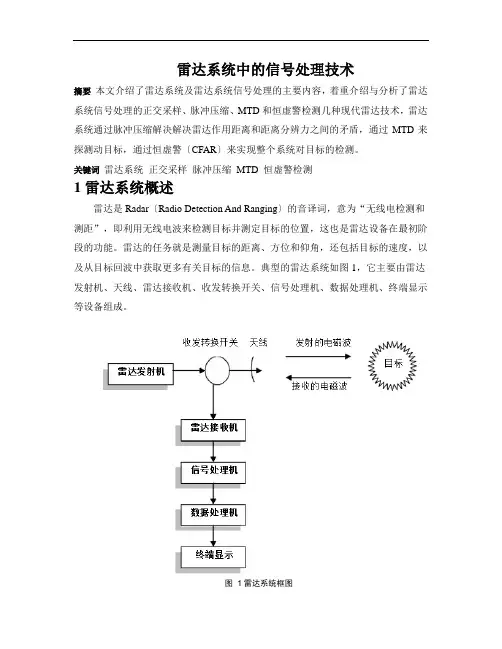

典型的雷达系统如图1,它主要由雷达发射机、天线、雷达接收机、收发转换开关、信号处理机、数据处理机、终端显示等设备组成。

图1雷达系统框图随着现代电子技术的不断发展,特别是数字信号处理技术、超大规模集成数字电路技术、电脑技术和通信技术的告诉发展,现代雷达信号处理技术正在向着算法更先进、更快速、处理容量更大和算法硬件化方向飞速发展,可以对目标回波与各种干扰、噪声的混叠信号进行有效的加工处理,最大程度低剔除无用信号,而且在一定的条件下,保证以最大发现概率发现目标和提取目标的有用信息。

雷达发射机产生符合要求的雷达波形,然后经馈线和收发开关由发射天线辐射出去,遇到目标后,电磁波一部分反射,经接收天线和收发开关由雷达接收机接收,然后对雷达回波信号依次进行信号处理、数据处理,就可以获知目标的相关信息。

雷达信号处理的流程如下:图 2 雷达信号处理流程2雷达信号处理的主要内容雷达信号处理是雷达系统的主要组成部分。

信号处理消除不需要的杂波,通过所需要的目标信号,并提取目标信息。

内容包括雷达信号处理的几个主要部分:正交采样、脉冲压缩、MTD和恒虚警检测。

正交采样是信号处理的第一步,担负着为后续处理提供高质量数据的任务。

雷达信号处理基础理论与应用雷达信号处理是现代雷达技术的核心,是将雷达接收到的回波信号转换为目标信息的过程。

因此,对于雷达信号处理的理论和应用的研究具有重要的现实意义和应用价值。

一、雷达基础理论1.1 雷达系统基础原理雷达系统的基础原理是通过发射电磁波,在目标物体上产生散射回波信号,并接收并处理回波信号,从而实现目标位置、速度、方位等信息的测量。

雷达系统的核心构成包括发射机、天线、接收机和信号处理器。

其中,发射机产生电磁信号,通过天线发射;接收机接收回波信号,信号处理器对回波信号进行处理后提取目标信息。

1.2 雷达信号理论雷达信号的理论表述是指雷达系统中涉及到各种信号处理算法的基础理论和应用。

雷达信号通常具有高频段、窄带和受干扰的特点,因此需要对信号进行复杂的处理。

雷达信号处理中涉及到的主要理论包括多普勒效应、回波信号分析、信号干扰、雷达成像等。

1.3 雷达系统性能参数雷达系统性能参数通常包括雷达探测能力、定位精度、分辨率、探测距离、反射截面等。

其中,雷达探测能力是指雷达系统可以发现目标的能力;定位精度是指雷达系统可以测量目标在空间中的位置;分辨率是指雷达系统可以将多个目标区分开来的能力;探测距离是指雷达系统可以探测到目标的最远距离;反射截面是指雷达系统接收到的目标回波信号对应的物体截面。

二、雷达信号处理应用2.1 雷达成像雷达成像是一种基于微波辐射的成像技术。

它通过对反射回波信号进行处理,实现目标在三维空间中的图像展示。

在雷达成像过程中,通常需要采用多个角度的发射和接收,以实现更准确的成像效果。

雷达成像技术在军事、航天、地质勘探等各个领域都得到了广泛的应用。

2.2 多普勒雷达多普勒雷达是一种测量目标速度的传感器。

它基于多普勒效应,利用目标运动产生的频移信息,对目标速度进行测量。

多普勒雷达的应用领域非常广泛,包括交通监控、地震预警、气象预报等。

2.3 监测雷达监测雷达是一种通过对目标进行连续观测,实时监测目标的运动和变化的雷达系统。

DSP在雷达方面的应用摘要:DSP是一种基于精简指令集的可编程数学计算芯片,可以对数字信号进行时频域变换、频谱分析、滤波、估值、增强、压缩等处理,广泛应用于家用电器、多媒体系统、雷达、卫星系统、移动通信、网络会议、医学仪器、实时图像识别与处理、语音处理、自适应制导控制、模式识别、定位、导航、联合战术无线电系统和智能基站等领域。

本文重点介绍通用DSP在雷达信号处理系统中的典型应用,以及研制基于DSP的雷达信号处理系统的关键技术。

关键词:DSP,军事,雷达;一、多核DSP在军事应用随着无人机(UAV)、声纳、雷达、信号情报(SIGINT)以及软件定义无线电(SDR) 等波形密集型应用中的信号处理需求不断攀升,多个数字信号处理器(DSP)内核的使用已成为重要的实现手段。

多核功能与不断丰富的IP内核及开发工具相结合可实现优异的系统架构。

所有这些应用都需要多核DSP来满足关键任务行业的各种需求,其中包括更强大的功能性(更快的处理速度)、更精细的分辨率以及更高的精度。

过去,处理器性能的改善是通过工艺节点升级及提高运行时钟频率来实现的。

然而,发展小型工艺节点和提高时钟频率并不是提高性能的低功耗捷径。

在单个裸片中集成多核的这个方法可在更低的时钟频率及功耗下实现所需的高性能。

当前的多核器件或采用同质内核,即所有处理内核都是相同的;或采用异质内核,即器件由不同类型的内核组成。

几乎所有应用都需要混合搭配的处理功能来满足行业需求。

从开发人员角度看,重点是支持同质内核,因为异质系统架构可通过同质器件创建。

反之,如果不牺牲性能就很难实现。

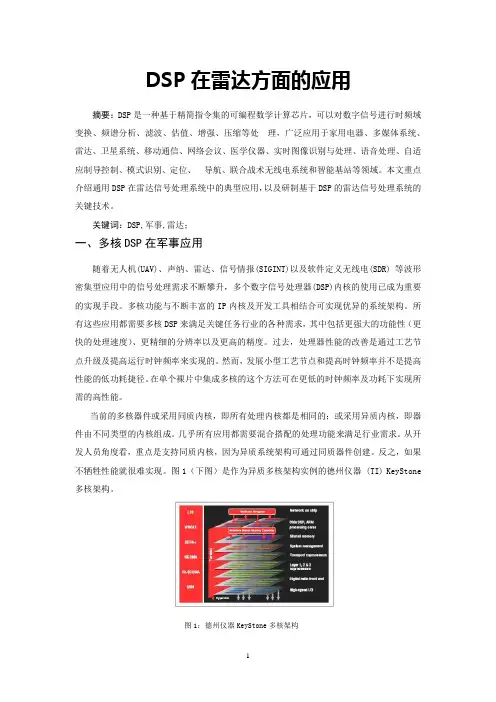

图1(下图)是作为异质多核架构实例的德州仪器 (TI) KeyStone 多核架构。

图1:德州仪器KeyStone多核架构TI KeyStone多内核架构拥有高度的灵活性,可同时集成定点与浮点运算、定向协处理与硬件加速,以及优化的内核间/组件间通信。

此架构包括多个 C66x DSP 内核,能够支持高达 256 GMAC 的定点运算性能以及 128GFLOP 的浮点运算性能。

一种雷达信号处理模块的设计和实现一种雷达信号处理模块的设计和实现现代雷达特别是机载雷达数字信号处理机的特点是输入数据多,工作模式复杂,信息处理量大。

因此,在一个实时信号处理系统中,雷达信号处理系统要同时进行高速数据分配、处理和大量的数据交换.而传统的雷达信号处理系统的设计思想是基于任务,设计者针对应用背景确定算法流程,确定相应的系统结构,再将结构划分为模块进行电路设计。

这种方法存在一定的局限性。

首先,硬件平台的确定会使算法的升级受到制约,由此带来运算量加大、数据存储量增加甚至控制流程变化等问题。

此外,雷达信号处理系统的任务往往不是单一的,目前很多原来由模拟电路完成的功能转由数字器件来处理。

系统在不同工作阶段的处理任务不同,需要兼顾多种功能。

这些问题都对通用性提出了进一步要求[2].随着大规模集成电路技术、高速串行处理及各种先进算法的飞速发展,利用高速DSP和FPGA相结合的系统结构是解决上述问题的有效途径。

1雷达信号处理机方案设计1.1雷达信号处理的目的现代机载雷达信号处理的任务繁重,主要功能是在空空方式下将AD 数据录取后进行数字脉压处理、数据格式转换和重排、加权降低频谱副瓣电平,然后进行匹配滤波或相参积累(FFT或DFT)、根据重复频率的方式进行一维或二维CFAR处理、跟踪时测角等运算后提取出点迹目标送给数据处理机。

空地方式下还要进行地图(如RBM和SAR)等相关图像成像处理,最后坐标转换成显示数据送给显控处理机。

上述任务需要基于百万门级可编程逻辑器件FPGA与高性能DSP芯片作为信号处理模块,以充分满足系统的实时性要求,同时为了缩短机载雷达系统的研制周期和减少开发经费,设计的基本指导思想是通用化的信号处理模块,可以根据不同要求,通过软件自由修改参数,方便用户使用。

1.2系统模块化设计方案的功能模块,除了信号处理所必需的脉冲压缩模块、为MTD模块作准备的数据重排模块、FIR滤波器组模块、求模模块、恒虚警处理模块和显示数据存储模块外,还包括雷达同步信号和内部处理同步产生模块、自检数据产生模块以及不同测试点测试数据采样存储模块。

基于TMS320C667x和VPX的雷达处理系统设计及应用宋玉霞;李贵;甘峰;邵江雨【摘要】针对基于CPCI或VME构建的雷达信号处理系统数传和处理能力的瓶颈,提出了一种以TI公司多核DSP TMS320C667x为核心处理器、基于VPX架构的高端高速雷达实时信号处理系统,介绍了系统的软硬件架构设计、电气结构设计、背板拓扑结构设计以及在雷达SAR成像处理模式、单脉冲处理模式的应用软件设计。

工程应用中的测试结果表明,该系统具有比传统信号处理系统更高的处理性能和与高性能相匹配的高速数传网络,应用前景广阔。

%For radar processing systems based on CPCI or VME,the data transmission and processing capability is a bottleneck.To address this issue,the design of a highlyreal⁃time processor based on multi⁃core DSP TMS320C667x from TI and VPX is presented,the design of software,hardware,electric structure and backplane topological structure is introduced,and the applications in SAR imaging and monopulse processing are proposed. The testing results in engineering application shown that this system has a better processing performance than traditional signal processor and a high⁃speed data transmission network matching with its high performance,and it has a good prospect of application.【期刊名称】《无线电工程》【年(卷),期】2016(046)011【总页数】4页(P71-74)【关键词】处理系统;TMS320C667x;VPX;SAR成像处理;单脉冲处理【作者】宋玉霞;李贵;甘峰;邵江雨【作者单位】中国西南电子技术研究所,四川成都610036;中国西南电子技术研究所,四川成都610036;中国西南电子技术研究所,四川成都610036;中国西南电子技术研究所,四川成都610036【正文语种】中文【中图分类】TN958.94过去10多年,雷达信号处理系统常采用TigerSHARC系列DSP或PowerPC系列CPU基于CPCI或VME总线进行构建。

通信中的雷达信号处理技术简介雷达信号处理技术是一种应用广泛的数字信号处理技术,它既可以用于军事领域,也可以用于民用领域。

雷达信号处理技术可以处理雷达系统接收到的复杂信号,获取目标的距离、速度和方向等信息,具有非常重要的意义。

本文将简要介绍通信中的雷达信号处理技术。

一、雷达系统的组成雷达系统通常由天线、发射器、接收器、数字信号处理器等组成。

天线用来发射和接收信号,发射器用来产生和放大雷达信号,接收器用来接收目标反射回来的信号,数字信号处理器用来处理接收到的信号,获取目标的相关信息。

二、雷达信号的处理过程雷达信号处理过程主要包括目标检测、目标跟踪和目标辨识等三个方面。

目标检测是指利用雷达系统接收到的信号,检测出存在的目标,目标跟踪是指追踪目标的运动状态,以便更加精确地估计目标的位置和速度,目标辨识是指对不同目标进行分类识别。

三、雷达信号处理技术1. 脉冲压缩技术脉冲压缩技术是一种常用的处理雷达信号的技术,它可以有效提高雷达系统的距离分辨率。

脉冲压缩技术的原理是在发射的频率宽带脉冲中引入码序列,在接收时与反射回来的信号相乘,经过积分后可以实现信号的压缩,从而提高信号的距离分辨率。

2. 最大似然法最大似然法是处理雷达信号的一种重要方法,它可以实现目标的检测和跟踪等功能。

最大似然法的基本思想是在给定的观测量下,找到最大可能性的参数估计值。

通过比较似然值的大小,可以确定目标的存在,并且估计目标的位置和速度等信息。

3. 相干积累法相干积累法是一种处理雷达信号的高精度预估方法,它可以通过对接收信号进行积累处理,实现对目标距离和速度的估计。

相干积累法在目标距离和速度较小的情况下,可以保证高精度的估计结果。

四、结论雷达信号处理技术在现代通信中广泛应用,不仅可以用于军事领域,还可以用于海洋探测、气象预报等领域。

本文简要介绍了通信中的雷达信号处理技术,其中包括脉冲压缩技术、最大似然法以及相干积累法等处理技术,这些技术具有重要的应用价值。

探讨雷达信号处理中对 DSP技术的应用摘要:DSP技术具有高精度、运算速度快、可编程、低功耗、抗干扰能力强等特点,可以用于雷达信号处理,提升雷达信号处理能力和效率。

本文首先简述了DSP技术以及雷达信号处理内容,然后分析了DSP技术在雷达信号处理中的具体应用,最后提出了基于DSP技术的雷达信号处理系统的构建设计方案。

本文重点研究DSP技术的含义、雷达信号处理的功能,做详细探讨,旨在为雷达信号处理工作的顺利开展提供理论参考。

关键词:雷达信号处理;应用;目标检测1DSP技术及雷达信号处理1.1 DSP技术1.1.1含义20世纪60年代以后,随着计算机技术的飞速发展,为了满足海量数据的处理要求,DSP技术应运而生。

DSP技术,即数字信号处理技术,涉及多个学科。

DSP技术与以往信号处理技术相比有了质的飞跃,在通信领域得到了广泛应用[1]。

在信号处理过程中,DSP技术需要使用专用的计算机设备进行采集、转换、滤波、预算等一系列处理,将信号转换成人们易于接受和需要的数字形式。

1.1.2特点DSP技术在处理数字信号时,通常需要进行大量的实时计算,计算方法一般包括两种:FFT计算方法和FIR滤波方法[2]。

在处理大量数据时,数字信号处理系统需要对信息数据进行反复处理,这对信号处理的准确性产生不利影响。

DSP技术在一定程度上是一种数字信号微处理器。

它具有精度高、稳定性高、运算速度快、功耗低、效率高等特点,可以有效弥补数字信号处理系统的不足[3]。

此外,DSP技术还具有实时性,具有通用处理器的特点,满足了数字信号处理算法的需要。

1.2雷达信号处理1.2.1雷达信号处理系统的功能雷达信号处理系统根据要求对雷达接收机的雷达回波信号进行模数转换,滤除杂波后,提高信号的稳定性和抗干扰性,从而在噪声环境中实现目标检测和所需信息数据,并在显示设备上显示目标信息。

此时,技术人员可以从数据中提取有效信息,例如目标的位置和距离。

1.2.2雷达信号处理系统的发展要求(1)预处理信号现代雷达信号处理系统具有高速、大数据量、实时性等特点。

雷达原理与雷达信号处理技术雷达(Radar)是一种用于探测和测量目标位置、速度和其他相关信息的电子设备。

雷达广泛应用于航空、军事、气象和监测领域等,它通过发射和接收电磁波来实现目标的探测和测量。

本文将介绍雷达的工作原理以及雷达信号处理技术。

一、雷达原理雷达的基本原理是利用电磁波在空间中的传播特性来实现对目标的探测。

雷达系统由发射系统、接收系统和信号处理系统组成。

(一)发射系统雷达的发射系统主要由一个高频发射器和一个天线组成。

高频发射器产生高频电磁波,并通过天线将电磁波辐射到空间中。

电磁波在空间中以光速传播,并在遇到目标后被目标散射回来。

(二)接收系统雷达的接收系统主要由一个接收天线和一个接收器组成。

接收天线接收到目标散射回来的电磁波,并将其导入接收器。

接收器对接收到的信号进行放大和处理,并将处理后的信号传送给信号处理系统。

(三)信号处理系统雷达的信号处理系统对接收到的信号进行处理和分析,提取目标的相关信息。

常见的信号处理技术包括脉冲压缩、MTI(移动目标指示)和MTD(移动目标检测)等。

二、雷达信号处理技术雷达信号处理技术是一系列用于提取目标信息的算法和方法。

下面介绍几种常见的雷达信号处理技术。

(一)脉冲压缩技术脉冲压缩是一种用于减小雷达接收信号的脉冲宽度,并提高雷达的距离分辨率的技术。

传统雷达的脉冲宽度较长,导致距离分辨率较低。

脉冲压缩技术通过发送一系列多个波形的脉冲信号,并在接收端将它们合并起来进行处理,从而减小脉冲宽度,提高距离分辨率。

(二)MTI技术MTI技术是一种用于抑制地面回波干扰的技术。

在雷达工作时,地面回波往往比目标回波要强,会对目标的探测产生干扰。

MTI技术通过比较连续两个脉冲序列之间的差别,将地面回波和目标回波区分开来,从而实现对目标的探测。

(三)MTD技术MTD技术是一种用于检测运动目标的技术。

雷达在探测目标时,如果目标静止不动,其回波信号的频率不会发生改变。

然而,如果目标发生运动,回波信号的频率将发生多普勒频移。

雷达通信系统的原理与应用雷达通信系统是一种广泛应用于军事、航空、海洋、气象等领域的高科技通信设备。

本文将围绕雷达通信系统的原理和应用展开阐述,旨在帮助读者深入了解该系统并掌握相关知识。

一、雷达通信系统的原理雷达通信系统利用电磁波与目标物之间的相互作用,通过探测和分析反射回来的信号来实现通信。

其基本原理如下:1. 发射器:雷达通信系统通过发射器产生电磁波,并将其发送到目标物上。

发射器通常采用一定频率的无线电波,如微波、毫米波等。

2. 目标物的反射:被发送的电磁波遇到目标物时,会发生反射,并将一部分能量回传给雷达通信系统。

目标物的反射特性会对回传信号产生影响。

3. 接收器:接收器是雷达通信系统中的重要组成部分,用于捕获目标物反射回来的信号。

接收器会将接收到的信号进行放大、滤波、解调等处理,以便后续的分析和处理。

4. 信号处理:接收到的信号经过一系列处理后,可以提取出目标物的相关信息,如距离、速度、方位等。

这些信息可以用于通信或其他应用领域。

二、雷达通信系统的应用雷达通信系统在多个领域都有广泛的应用。

以下是一些主要应用领域的简要介绍:1. 军事领域:雷达通信系统在军事领域起着至关重要的作用。

它可以用于目标探测、情报获取、导航引导、火力打击等方面,并在战争中具备重要的战略和战术价值。

2. 航空航天领域:雷达通信系统在航空航天领域中广泛应用。

它可以用于飞行员导航、飞行器定位、空中交通管制等任务,提高了航空器的飞行安全性和效率。

3. 海洋领域:雷达通信系统也在海洋领域发挥重要作用。

它可以用于船舶导航、渔业资源调查、海上救援等任务,对于保障海上行动的安全性和有效性起到了至关重要的作用。

4. 气象领域:雷达通信系统在气象领域中被广泛应用于天气预报、降水检测、风暴追踪等任务。

它可以通过对大气中的杂波和降水反射信号的探测和分析,提供准确的气象信息。

5. 地质勘探领域:雷达通信系统可以用于地质勘探领域,如矿产资源勘测、油气田勘探等。

信号处理在雷达系统上的应用信号处理作为电子技术领域中的一门重要学科,应用十分广泛。

在雷达系统中,信号处理技术的应用越来越成熟,为雷达探测和识别提供了较强的支持。

本文将介绍信号处理在雷达系统中的应用。

一、雷达系统概述雷达是一种利用电磁波对物体进行探测和成像的仪器,可以实现远距离探测和目标识别。

雷达系统由发射机、天线、接收机和信号处理器等组成。

发射机产生高频电磁波,天线把电磁波发射到空间中,遇到目标后,部分电磁波会被目标反射回来,接收机接收到反射回来的电磁波,经过信号处理器处理后,就可以得到目标的位置、速度、形状、材质等信息。

二、信号处理在雷达系统中的作用信号处理是雷达系统中最重要的环节之一,其主要作用是对接收到的信号进行处理,以实现目标的探测和识别。

信号处理器通常包括模拟信号处理和数字信号处理两个部分。

1. 模拟信号处理模拟信号处理主要涉及到雷达接收机的前端电路设计和信号滤波处理。

首先,为了能够在高频环境下提供稳定的性能,雷达前端要采用射频电路,包括射频放大器、混频器和局部振荡器。

其次,由于空间中的信号包含各种噪声和干扰,所以需要采用合适的滤波电路来抑制噪声和干扰,从而提高雷达系统的探测性能。

2. 数字信号处理数字信号处理技术已经被广泛应用于雷达系统中。

数字信号处理主要包括数字滤波、信号调制、谱估计等方面。

数字滤波可以对采集到的数据进行处理,抑制不相关的噪声和干扰。

信号调制可以改变信号的频率、相位和振幅等特性,从而提高系统的探测性能。

谱估计可以使用特殊的算法来检测雷达接收到的信号中的方向、速度、距离等参数。

三、信号处理在雷达系统中的具体应用1. 脉冲压缩技术脉冲压缩技术是一种有效的降低雷达系统瞬时带宽的技术。

其基本原理是,在雷达系统中采用短脉冲发射信号,通过压缩滤波器对接收到的信号进行压缩处理。

这种技术可以提高雷达的分辨率和探测能力,特别是在高噪声和弱信号情况下具有更好的效果。

2. 空时波束形成技术空时波束形成技术是利用多个天线对接收到的雷达信号进行合成,从而实现对目标的探测和识别。

航空导航工程技术中的雷达原理与应用雷达是航空导航工程技术中不可或缺的一项技术。

它通过利用电磁波探测目标物体并获取相关信息,具有广泛的应用范围。

本文将详细介绍雷达的原理、应用和未来发展趋势。

1. 雷达的原理雷达是一种利用无线电波进行探测和测距的设备。

其工作原理基于电磁波传播和回波的特性。

雷达主要由发射机、接收机、天线和信号处理系统组成。

具体工作过程如下:首先,发射机产生特定频率和脉冲宽度的电磁波信号,通过天线发射出去。

当这些电磁波遇到目标物体时,部分能量被目标反射回来形成回波。

接收机接收到回波信号,并将其放大、滤波和解调。

接着,信号处理系统对回波信号进行处理和分析,提取出目标物体的相关信息,如距离、速度和方位角等。

2. 雷达的应用航空导航工程中,雷达广泛应用于飞机导航、空中交通管制、天气预报等领域。

以下是其中几个重要应用的介绍:2.1 飞机导航雷达可用于飞机导航和着陆引导系统。

通过安装雷达设备在机场和飞行器上,可以实时监测飞机的位置、速度和航向等信息。

这样,飞行员可以更准确地进行导航和着陆操作,提高飞行安全性。

2.2 空中交通管制雷达在空中交通管制中起到关键作用。

空中交通管制雷达可以实时监测飞机的位置和高度,并提供给飞行员和航空管理人员相关信息。

这样,可以确保飞机的安全间隔,避免空中相撞的危险。

2.3 天气预报雷达还可以用于天气预报。

通过使用气象雷达,可以追踪和监测降水、风暴等天气系统的移动和发展趋势。

这样,气象部门可以提前预警并采取相应的措施,以保障公众安全。

3. 雷达的发展趋势随着科技的不断发展,雷达技术也在不断进步。

以下是雷达技术的一些未来发展趋势:3.1 多普勒雷达多普勒雷达是一种可以测量目标物体相对速度的雷达。

它可以用于检测飞机、车辆等物体的运动状态。

未来,多普勒雷达技术将进一步提高其精度和敏感度,并在交通监控、地质勘探等领域得到更广泛的应用。

3.2 相控阵雷达相控阵雷达是一种利用大量天线单元形成波束的雷达系统。

雷达通信一体化系统设计与实现摘要:雷达通信一体化通过一套共用的硬件设备实现雷达探测与通信传输,相比于传统单一的雷达或者通信设备,更易集成化、小型化和高效利用频谱。

该文系统地介绍了雷达通信一体化的原理与特点,指出了一体化研究中急需解决的问题,从典型的基于线性调频(LFM)的雷达通信一体化信号出发,全面梳理了国内外针对雷达通信一体化的相关研究,着重归纳了正交频分复用(OFDM)与多入多出(MIMO)技术在雷达通信一体化波形设计、信号处理、一体化系统设计等几个重点方向的研究进展,并分析了雷达通信一体化未来的可能发展趋势及其在军事领域和民用智能交通领域的重要应用前景。

关键词:雷达通信;一体化;源相控阵雷达一、雷达通信—体化的研究意义雷达通信一体化的研究是十分有必要的,其研究意义主要有以下三点:1.1雷达通信一体化的研究可以为战场中电子技术的运用方式提供更多的工作方式,给设备带来更大的利用空间。

现代战争与传统战争不同,信息化的要求越来越高,现代战争实际上就是信息的战争,谁能在信息的竞争上取得先机,谁就在战争中取得巨大的优势。

因此不断提高作战军队的信息化和技术化的程度,为赢得现代战争打下坚实的基础。

随着信息化程度而不断提高,作战的综合指挥方式也发生了巨大的变化,为了在指挥和执行上更好的交互,就要不断提高资源的利用率,提高信息化的程度,以达到现在作战信息化的要求。

1.2雷达通信一体化的研究可以极大地提升军队空中的作战能力。

如通过对雷达进行简单的基础改造,让雷达实现通讯,不仅可以减少通讯设备,简化通讯系统,节约空间资源和作战成本,是十分有意义的。

1.3雷达通信一体化的研究还可以实现通信设备的多样化,给信息的传递带来极大的便利,使得指挥部更具有智能性和灵活性。

将雷达与通信结合起来,不仅可以提高设备的工作效率,并且也简化了设备的开发过程。

开发者不用再研究一部新的设备,而把研究重点放到提高设备的功能多样性上来,利用雷达的优势,能实现设备的多样化。

雷达信号处理技术在航空航天中的应用实践随着航空航天事业的不断发展,雷达技术已成为现代航空航天中不可缺少的一部分。

雷达信号处理技术作为雷达系统的核心技术,大大提升了雷达系统的性能和可靠性,也为现代航空航天事业的发展注入了强劲动力。

在雷达系统中,雷达信号处理技术主要包括雷达信号探测、目标识别和信号重构等几个方面。

其中,雷达信号探测是确定目标存在与否的一个关键步骤。

通过对接收信号进行计算分析,雷达系统可以在背景杂波和噪声干扰中准确探测出目标信号,实现目标检测和跟踪。

目标识别则是确定目标类型和特征的一个重要环节。

通过对目标的回波信号进行时频分析和特征提取,可以实现目标识别和分类。

信号重构则是对接收信号进行数字处理和信号处理的一个关键步骤。

通过数值计算和数据分析,可以实现对接收信号的精确重构,并提高雷达系统的性能和精度。

雷达信号处理技术在航空航天中的应用实践非常广泛,主要体现在以下几个方面:一、航空航天导航和控制掌握精确的航空航天导航和控制技术,是现代航空航天事业的关键之一。

雷达信号处理技术在航空航天导航和控制中,具有重要的应用价值。

航空航天导航和控制系统中,利用雷达信号处理技术可以实现轨道控制、状态估计、航迹维持等重要功能,保障航空航天器的精准运行和安全着陆。

二、空间目标监测和识别随着全球经济的发展和国际竞争的加剧,空间目标监测和识别已成为各国空军军事装备必备的一项技术。

在空间目标监测和识别中,利用雷达信号处理技术可以识别目标运动状态、确定目标轨迹、预测目标行为等。

同时,雷达信号处理技术还可以克服天气和电磁环境等因素的干扰,提高目标监测和识别的精度和可靠性。

三、天气雷达探测天气雷达探测是气象学和气象预报中的重要技术之一。

通过分析雷达信号的反射和散射特征,可以确定天气系统的位置、范围和运动状态,预测天气状况和气象灾害。

天气雷达探测中,利用雷达信号处理技术可以实现天气系统的实时监测和预测,为人们的生产和生活提供及时和准确的气象预报服务。

雷达信号处理技术及其在军事应用中的应用一、引言雷达信号处理技术是一种应用广泛的信号处理技术,尤其是在军事领域得到了广泛的应用。

本文将详细介绍雷达信号处理技术的基本原理及其在军事应用中的应用。

二、雷达信号处理技术基本原理雷达信号处理技术主要包括三个方面:信号处理、图像处理和数据处理。

其中,信号处理是最基础的部分,它主要涉及信号的判定和分析。

1. 信号处理信号处理是指对雷达接收到的信号进行分析和处理,以提取出需要的信息。

信号处理包含了以下几个方面:(1)滤波。

雷达接收到的信号中,包含了大量的噪声和杂波。

滤波的作用是将这些干扰信号滤掉,只保留下需要的信号。

滤波可以分为数字滤波和模拟滤波两种。

(2)增益控制。

雷达信号是由发送端的信号在其传播途中被反射回来形成的。

由于传播距离的不同,接收的信号强度也存在差别。

因此,需要对接收到的信号进行增益控制,以保证信号质量。

(3)自适应滤波。

自适应滤波是一种用于抑制噪声干扰的有效方法。

它可以针对不同类型的噪声干扰进行优化,提高分析的准确性。

(4)脉冲压缩。

脉冲压缩是一种信号处理方法,主要用于提高雷达信号的分辨率。

脉冲压缩可以使信号的带宽变窄,从而提高信号分辨率。

2. 图像处理图像处理是指对雷达返回的数据进行处理,生成对应的图像。

雷达图像处理主要包含以下几个方面:(1)目标检测。

目标检测是指对雷达图像中的目标进行识别和检测。

目标检测可以分为单目标检测和多目标检测两种。

(2)目标跟踪。

目标跟踪是指对雷达图像中的目标进行跟踪和预测。

目标跟踪可以分为单目标跟踪和多目标跟踪两种。

(3)目标识别。

目标识别是指对雷达图像中的目标进行分类识别。

目标识别可以分为有监督学习和无监督学习两种。

3. 数据处理数据处理是指对雷达返回的原始数据进行处理,以得到需要的信息。

在雷达数据处理中,采用的主要技术有以下几个:(1)多普勒处理。

多普勒处理是一种用于处理由目标运动引起的频移的方法。

它可以将雷达接收到的信号分解成多个频率分量,从而提取出目标的运动状态。

雷达信号处理的理论与应用研究一、引言雷达信号处理是一项重要的技术,广泛应用于军事、民用、科研等领域。

其基本工作原理是通过发射电磁波,并接收回波,从而确定目标的距离、速度、方向等参数。

本文将以雷达信号处理为主题,阐述其理论与应用研究。

二、理论基础1. 信号处理在雷达信号处理中,信号处理是一个重要的环节。

它主要包括信噪比的提高、多普勒速度的测定、目标跟踪、图像重建等方法。

其中,信噪比是影响雷达信号处理最主要的因素。

通过选择合适的信号处理算法,可以有效提高信噪比,从而提高雷达系统的性能。

2. 多普勒效应多普勒效应是雷达信号处理中一个很重要的现象,它指的是物体相对于雷达运动时信号频率的变化。

对于静止物体,其频率不变。

但是当物体运动时,其引入的相对速度就会使回波信号的频率产生偏移。

通过利用多普勒效应,可以有效地测定目标的速度,从而实现对目标的追踪。

3. 目标识别算法目标识别算法是雷达信号处理中的一个关键问题,其主要目的是通过信号特征提取对目标进行识别。

目标特征通常表现为目标散射截面、目标尺寸、目标速度等特征。

常用的目标识别算法包括模式识别、神经网络等。

三、应用研究1. 军事应用雷达信号处理在军事领域有着广泛的应用,如导弹制导、目标探测与追踪等。

在导弹制导中,雷达信号处理可以有效控制导弹的飞行轨迹,实现精确打击。

在目标探测与追踪中,雷达信号处理可以识别目标特征,从而确定目标的位置、速度等参数。

2. 民用应用雷达信号处理在民用领域的应用也日趋广泛,如气象雷达、空管雷达等。

在气象雷达中,雷达信号处理可以有效探测大气中降雨的情况,从而提供准确的气象预报。

在空管雷达中,雷达信号处理可以跟踪空中飞行器的位置、速度等参数,从而保障航空安全。

3. 科研应用雷达信号处理在科研领域的应用也很广泛,如航天科学、地球物理学等。

在航天科学中,雷达信号处理可以实现对行星、卫星等天体的探测与跟踪。

在地球物理学中,雷达信号处理可以实现对地表物体的探测与识别,从而揭示地球内部结构及物理参数。

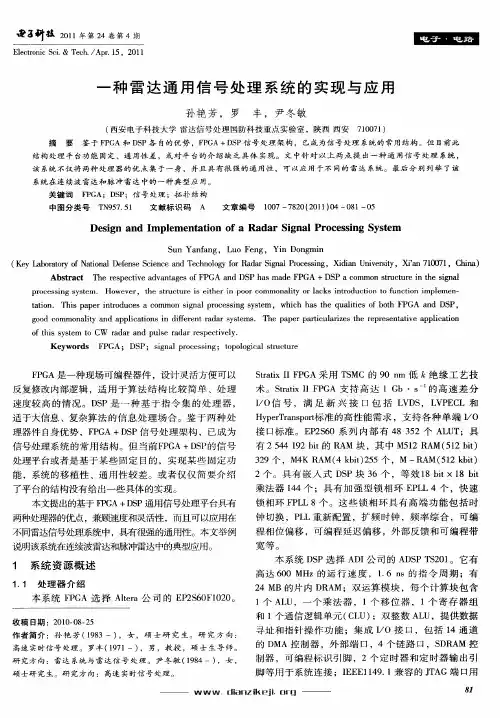

一种雷达通用信号处理系统的实现与应用一种雷达通用信号处理系统的实现与应用FPGA是一种现场可编程器件,设计灵活方便可以反复修改内部逻辑,适用于算法结构比较简单、处理速度较高的情况。

DSP是一种基于指令集的处理器,适于大信息、复杂算法的信息处理场合。

鉴于两种处理器件自身优势,FPGA+DSP信号处理架构,已成为信号处理系统的常用结构。

但当前FPGA+DSP的信号处理平台或者是基于某些固定目的,实现某些固定功能,系统的移植性、通用性较差。

或者仅仅简要介绍了平台的结构没有给出一些具体的实现。

本文提出的基于FPGA+DSP通用信号处理平台具有两种处理器的优点,兼颐速度和灵活性,而且可以应用在不同雷达信号处理系统中,具有很强的通用性。

本文举例说明该系统在连续波雷达和脉冲雷达中的典型应用。

1系统资源概述1.1处理器介绍本系统FPGA选择Altera公司的EP2S60F1020。

Stratix II FPGA采用TSMC的90nm 低k绝缘工艺技术。

Stratix II FPGA支持高达1Gb·s-1的高速差分I/O信号,满足新兴接口包括LVDS,LNPECL和HyperTransport标准的高性能需求,支持各种单端I/O接口标准。

EP2S60系列内部有48352个ALUT;具有2544192bit的RAM 块,其中M512RAM(512bit)329个,M4K RAM(4kbit)255个,M-RAM(512kbit)2个。

具有嵌入式DSP块36个,等效18bit×18bit乘法器144个;具有加强型锁相环EPLL4个,快速锁相环FPLL8个。

这些锁相环具有高端功能包括时钟切换,PLL 重新配置,扩频时钟,频率综合,可编程相位偏移,可编程延迟偏移,外部反馈和可编程带宽等。

本系统DSP选择ADI公司的ADSP TS201。

它有高达600MHz的运行速度,1.6ns的指令周期;有24MB的片内DRAM;双运算模块,每个计算块包含1个ALU,一个乘法器,1个移位器,1个寄存器组和1个通信逻辑单元(CLU);双整数ALU,提供数据寻址和指针操作功能;集成I/O接口,包括14通道的DMA控制器,外部端口,4个链路口,SDRAM控制器,可编程标识引脚,2个定时器和定时器输出引脚等用于系统连接;IEEE1149.1兼容的JTAG端口用于在线仿真;通过共享总线可以无缝连接多达8个TigerSHARC DSP。

1.2FPGA+DSP结构由于FPGA和DSP各自的自身优势,FPGA+DSP信号处理架构已成为信号处理系统的常用结构。

一般情况下FPGA+DSP的拓扑结构会根据需要进行不同的连接,这就导致这种结构的专用性,缺乏灵活性。

对于一个通用处理平台要考虑到各种不同的信号通路,因此大部分通用FPGA+DSP平台都采取各个处理器间均有通路的方式。

这种拓扑结构灵活方便,可以满足各种不同的通路需求,这种结构的缺点就是硬件设计的复杂以及可能会有资源浪费。

对于这种通用FPGA+DSP 结构,FPGA与各个DSP之间均有连接,不同之处便是DSP之间的拓扑结构。

一般分两种,一是高速外部总线口耦合结构组成多DSP 系统,这种结构可以实现多DSP共享系统内的资源,系统内的个处理器可以共享RAM,SDRAM和主机等资源,还可共享其他处理器核内资源。

这种结构的长处就在资源共享上,但这种结构的PCB设计十分困难,而且当总线负载较重时速度很难提高,要达到50~60 MHz的数据速率都很难。

另外一种结构就是高速链路口耦合结构。

ADSP TS201有4个高速链路口内核时钟600MHz时,单向数据传输率最高可达600MHz。

高速链路口通信是点对点的,这是它的局限,但也带来的一个优点就是较高的传输可靠性。

在本信号处理系统中采用第2种结构。

1.3本信号处理系统的硬件结构在充分考虑系统的通用性能上,本系统在硬件结构上采用1片FPGA与4片DSP的拓扑结构。

每片DSP与FPGA分别有一路链路口相连,4片DSP之间由链路口相连,同时,DSPA与DSPD分别有64位的数据总线与FPGA相连。

这种拓扑结构使得任意两片DSP之间都可以连通,对角的DSP可以通过连到FPGA内部的链路口相互通信。

此外,本系统采用一片FLASG存储DSP程序,对所有DSP进行加载。

DSPB,DSPC分别连有32×64Mbit的SDRAM,对DSP的内存空间进行了扩展,便于大量数据处理,。

2具体应用2.1在连续波雷达中的应用其主要功能是完成对接收的全相参体制的双波束原始视频信号的数字采样信号进行相关处理,其中包括时/频转换、MTI、MTD处理、双波束估高处理等,最终能够对动目标进行检测。

拓扑结构:待处理数据通过接插件传送到FPGA内部,通过FPGA的初步处理,经由FPGA与DSPA、DSPD相连的64位数据总线传送到两片DSP内进行进一步的处理。

DSPA将处理完的数据经过链路口直接传送到DSPB,而DSPD将处理完的数据通过DSPD到FPGA,FPGA到DSPB的链路口也传送到DSPB。

DSPC接收DSPB处理完的数据并将数据进行进一步的处理后通过链路口传送到FPGA输出。

为应用所使用的硬件拓扑结构。

处理流程:FPGA将接收到的两路信号分别进行4096点FFT,并对FFT的结果进行MTI,MTI可以是根据命令选做。

DSP中完成两路信号的二维FFT也就是MTD,CFAR,估高,杂波图等,最后将整理后的结果输出到FPGA,由FPGA输出给雷达的其它模块,。

资源的使用:在FPGA需要完成的功能为两路复信号的FFT,MTI,以及与DSP的数据通信。

FFT的实现采用Altera公司的FFT IP Core实现,它是一个高性能、高度参数化的快速傅里叶变换(FFT)处理器,实时正序输出变换结果。

采用缓冲突发模式4输出引擎结构完成一路4096点FFT。

MTI采用3次相消器即4脉冲对消法,在FPGA中采用FIFO实现。

与DSP的总线数据通信的实现为FPGA将待传输数据写到FIFO中同时向DSP发送中断,DSP响应中断后从FIFO中将数据读出。

与DSP的链路口数据通信,无论是接收链路口还是发送链路口均由一个数据缓冲模块和一个数据拆包/打包模块组成。

表1为FPGA中资源时间的具体使用,由此看出EP2S60F1020的资源丰富。

在DSPA,DSPD中接收数据采用乒乓操作,在接收一组数据的同时对已接收的数据进行操作,完成数据的定浮转换和MTD。

应用中用N点傅立叶变换实现N个窄带多普勒滤波器实现MTD。

在DSPB 中实现恒虚警检测(CFAR),采用的是两侧单元平均选大CFAR处理(GO—CFAR),也就是从被检测电路单元前后各取一段距离范围的回波信号,分别计算前后两部分的平均值,选取平均值较大的一个乘以门限因子C作为检测门限,与被检测单元作比较,如果被检测距离单元的回波幅度高于检测门限,就可认为被检测距离单元有目标存在。

被检测单元前后各空出几个参考单元避免目标本身对门限值的影响。

速度维聚心是指,对同一距离单元的各个通道道进行幅度峰选,取出其中的最大值作为目标所在的速度通道号。

杂波图的实现,首先建立杂波图,然后选取零通道数据并根据已知的方位信息及递归公式更新杂波图中数据。

假设DSPA和DSPD接收到的数据位每周期1024点的数据,DSP需要每8周期一滑窗做32脉冲的MTD,CFAR 取8个单元平均选大,则DSP中各功能所占资源如表2所示。

2.2在脉冲雷达中的应用功能:完成对接收的全相参体制的回波信号的中频采样信号进行相关处理,其中包括DDC、脉冲压缩、MTI、MTD处理、CFAR、测角等,最终能够对动目标进行检测。

所用到的拓扑结构:待处理数据通过接插件传送到FPGA内部,通过FPGA的初步处理,经由FPGA与DSPA、DSPD相连的64位数据总线传送到两片DSP内进行进一步的处理。

DSPA将处理完的数据经过链路口直接传送到DSPB,DSPD将处理完的数据直接传送到DSPC。

DSPC处理完自身数据并接收DSPB的数据并将数据进行进一步的处理后通过链路口传送到FPGA输出。

为应用所使用的硬件拓扑结构。

处理流程:FPGA将接收到的和差两路信号分别进行DDC以及低通滤波,并对结果进行整理,和路信号发送给DSPA,差路信号发送给DSPD。

在DSPA和DSPD中分别进行和路以及差路信号的脉压、MTI,其中MTI可以是根据命令选做的。

DSPA将处理完的信号传送给DSPB,DSPD将处理后的数据传送给DSPC,在DSPB和DSPC 中进行和路以及差路信号的MTD、MOD、CFAR,同时DSPC接收DSPB处理后的信号,在DSPC中进行和差比商测角,最后将整理后的结果输出到FPGA,由FPGA输出给雷达的其它模块,。

资源使用:在FPGA需要完成的功能为两路信号的DDC、低通滤波,以及与DSP的数据通信。

其中在做DDC时为了便于测试在FPGA内部有Mat-lab产生的两组数据分别作和差两路数据的内部源数据。

与DSP交互部分无论是总线传输还是链路口传输均与连续波雷达信号处理实现方法一致,在此不再赘述(假设FPGA到DSP传输数据为1024个复数)。

则在FPGA中占用的主要资源如表3所示。

在DSPA和DSPD中以乒乓方式接收FPGA的数据完成数据的定浮转换,脉冲压缩和MTI。

其中脉冲压缩采用频域脉压的方式,然后对脉压结果作MTI,采用四脉冲对消。

在DSPB和DSPC中要完成数据的MTD,MOD,CFAR,最后在DSPC中实现测角,最终将目标数据结果传输给FPGA。

这些功能的实现与连续波雷达实现这些功能方法相同,在此不再赘述。

则在DSP中所占用的资源如表4所示。

2.3几个重要模块的速度在实时信号处理系统中,系统的速度至关重要,本文所介绍的平台在各个接口及模块上均能达到不错的速率。

(1)FPGA与DSP总线传输速率。

在本系统中总线传输可以采取流水协议,零等待周期的配置,这样总线速度可以达到DSP SCLK的速度,在本系统中为50MHz×64bit的速率。

(2)FPGA与DSP链路口传输速率。

在本系统中链路口采取四位模式,则链路口可以配置成150MHz,300MHz,400MHz,600 MHz。

经过测试,FPGA与DSP之间的链路口速度可以达到400 MHz×4bit的完美无错传输。

(3)DSP与DSP链路口传输速率。

经过测试,DSP与DSP之间的链路口速度可以达到600 MHz×4bit的无错传输。

以上几个速率为数据传输十分重要的几个接口的速度,通过测试数据可知,系统可以达到较高的,完全可以满足信号实时性的要求。