UART串口通信实验报告

- 格式:doc

- 大小:41.05 KB

- 文档页数:21

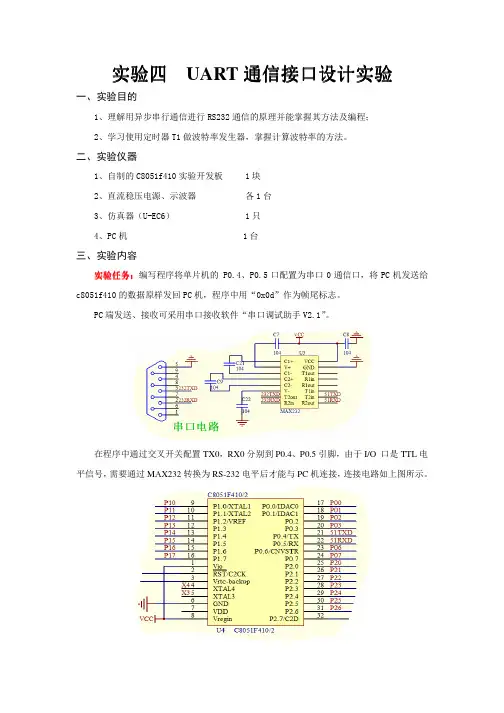

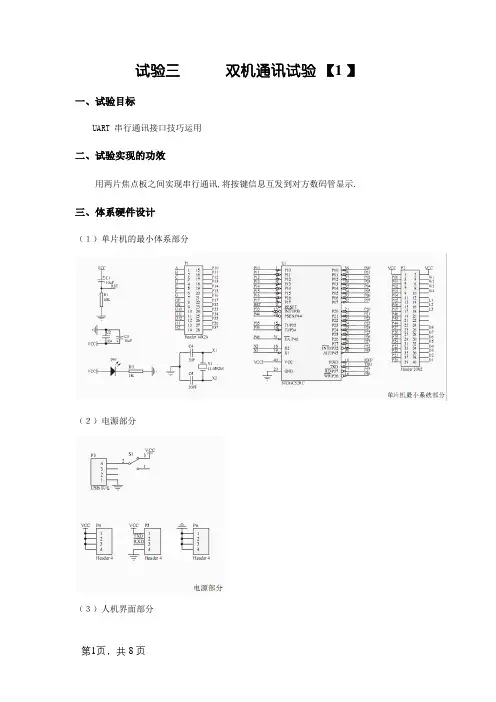

试验三双机通讯试验【1 】一、试验目标UART 串行通讯接口技巧运用二、试验实现的功效用两片焦点板之间实现串行通讯,将按键信息互发到对方数码管显示.三、体系硬件设计(1)单片机的最小体系部分(2)电源部分(3)人机界面部分数码管部分按键部分(4)串口通讯部分四、体系软件设计#include <STC.H>#define uchar unsigned char#define uint unsigned intvoid send();uchar code0[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f};//0-9的数码管显示sbit H1=P3^6;sbit H2=P3^7;sbit L1=P0^5;sbit L2=P0^6;sbit L3=P0^7;uint m=0,i=0,j;uchar temp,prt;/***y延时函数***/void delay(uint k){uint i,j; //界说局部变量ijfor(i=0;i<k;i++) //外层轮回{for(j=0;j<121;j++); //内层轮回}}/***键盘扫描***/char scan_key(){ H1=0;H2=0;L1=1;L2=1;L3=1;if(L1==0){ delay(5);if (L1==0){ L1=0;H1=1;H2=1;if(H1==0){ m=1; //KEY1键按下return(m);}if(H2==0){ m=4; //KEY4键按下return(m);}}}if(L2==0){ delay(5);if (L2==0){ L2=0;H1=1;H2=1;if(H1==0){ m=2; //KEY2键按下return(m);}if(H2==0){ m=5; //KEY5键按下return(m);}}}if(L3==0){ delay(5);if (L3==0){ L3=0;H1=1;H2=1;if(H1==0){ m=3; //KEY3键按下return(m);}if(H2==0){ m=6; // KEY6键按下return(m);}}}return(0);}/***主函数***/main(){P1M1=0x00;P1M0=0xff;SCON=0x50;//设定串行口工作方法1TMOD=0x20;//准时器1,主动重载,产生数据传输速度 TH1=0xfd;//数据传输率为9600TR1=1;//启动准时器1P0&=0xf0;while(1){if(scan_key()) //假如有按键按下{SBUF=scan_key(); //发送数据while(!TI); // 等待数据传送TI=0; // 消除数据传送标记}if(RI) //是否稀有据到来{RI=0; // 消除数据传送标记temp=SBUF; // 将吸收到的数据暂消失temp中}P1=code0[temp]; // 数据传送到P1口输出delay(500); //延时500ms}}五、试验中碰到的问题及解决办法(1)串行口和准时器的工作方法设定是症结,本次是按需传输的是两位十六进制数,串行口为工作方法1,准时器为8位主动重载;(2)采取P0&=0xf0语句使4个数码管静态点亮;(3)在发送和接收进程中,用标识位TI和RI来检测发送和接收是否完成;(4)在用电脑和单片机进行串口通讯测试时,电脑的传世速度必定要和单片机的传输速度相等,不然显示会消失错误.指点先生签字:日期:。

uart实验报告

《UART实验报告》

实验目的:通过实验学习串行通信的基本原理,掌握UART通信协议的工作原理和使用方法。

实验设备:单片机开发板、串口调试助手、电脑。

实验原理:UART(Universal Asynchronous Receiver/Transmitter)是一种通用的异步串行通信协议,用于在计算机和外部设备之间进行数据传输。

UART通信协议包括数据位、停止位、奇偶校验位等参数,通过这些参数的设置可以实现不同的通信速率和数据传输方式。

实验步骤:

1. 连接单片机开发板和电脑,打开串口调试助手。

2. 在单片机开发板上编写UART通信程序,设置通信参数。

3. 将单片机开发板通过串口连接到电脑,打开串口调试助手。

4. 在串口调试助手上发送数据,观察单片机开发板接收到的数据。

5. 在单片机开发板上发送数据,观察串口调试助手接收到的数据。

实验结果:

经过实验,我们成功地实现了通过UART通信协议在单片机开发板和电脑之间进行数据传输。

在串口调试助手上发送的数据能够被单片机开发板正确接收,并且在单片机开发板上发送的数据也能够被串口调试助手正确接收。

通过调整通信参数,我们还验证了不同通信速率和数据传输方式对通信效果的影响。

实验总结:

通过本次实验,我们深入了解了UART通信协议的工作原理和使用方法,掌握

了串行通信的基本原理。

在今后的学习和工作中,我们将能够更加熟练地应用UART通信协议进行数据传输,为实际工程应用打下了坚实的基础。

计算机与外部设备之间的通信一般采用两种方式:并行方式和串行方式。

所谓的并行方式就是各个位同时进行传输的通信方式,这种方式通信主要特点是通信的速度快,但当距离远且位数多的时候并行通信的成本就会高很多。

串行通信分为异步与同步串行通信。

UART(通用异步收发器)就是所谓的异步串行通信协议。

只要通信的双方采用相同的数据帧格式(数据位,开始位,校验位,停止位)和波特率就能在未共享同步时钟信号的情况下通过两根据数据线(RX和TX)进行数据通信。

采用这种方式,当数据传输结束后可以通过置位中断位通知处理器进行相应的处理。

STELLARIS系列ARM芯片的UART具有完全可编程,16C550型串口接口的特性(但并不兼容)。

独立发送FIFO(16B)和接收的FIFO(16B)(first in first out),可以将两个FIFO配置成不同程序的触发中断,可供选择的触发深底见下图中。

如:接收FIFO配置成1/4触发深度,则当UART收到4个数据时,产生接收中断。

UART模块的特性如下:下面是PC机的COM接口与ARM芯片的UART接口的典型电路。

注意:图中的电阻不能省略,否则会影响数据的传输。

U1是Exar(原sipex)公司出产的UART 转RS232C的接口芯片SP3232E。

可在3.3V下工作。

UART的功能概述:发送:发送逻辑从发送FIFO读取的数据执行并->串转换。

控制逻辑执行输出起始位在前的串行流,根据控制寄存器中已编程的配置,后面紧跟数据位(注:LSB最低位先输出),奇偶校验位,停止位。

接收:在检测到一个有效的起始脉冲时,接收逻辑对收到以的位流执行串->并转换,此外还会对溢出错误,奇偶校验错误,帧错误和线中止(line-break)错误进行检测。

并将检测到的状态一起写入到接收FIFO中。

波特率的产生:baud-rate divisor(波特率除数)是一个22位数,16位整数和6位小数。

串行通讯实验报告实验目的:1.了解串行通讯的基本概念和原理。

2.学习串行通讯的常用协议和流程。

3.实现串行通讯的发送和接收功能。

4.掌握使用串行通讯进行数据传输的方法。

实验器材:1.PC机一台。

2.串行通讯扩展板一块。

3.经典串行通讯工具软件。

实验原理:串行通讯是指信息逐位地按顺序进行传输的通讯方式。

串行通讯需要通过物理通道将数据逐位地传输给接收方。

常用的串行通讯协议有UART (通用异步收发传输)协议、SPI(串行外设接口)协议和I2C(串行外设接口)协议等。

实验步骤:1.将串行通讯扩展板连接到PC机上的串行通讯端口。

2.在PC机上安装串行通讯工具软件,并打开软件。

3.配置串行通讯参数,包括波特率、数据位、停止位和校验位等。

4.在串行通讯工具软件中编写发送数据的程序,并发送数据。

5.在串行通讯工具软件中接收数据,并验证接收的数据是否正确。

实验结果与分析:在实验中,我们使用串行通讯扩展板和串行通讯工具软件实现了串行通讯的发送和接收功能。

我们先配置了串行通讯的参数,在发送数据之前,我们选择了合适的波特率、数据位、停止位和校验位等。

然后,在发送数据之后,我们使用串行通讯工具软件接收数据,并验证接收的数据是否正确。

实验中我们可以观察到发送和接收的数据都是逐位地传输的,并且发送和接收的数据需要保持一致。

如果发送和接收的数据不一致,可能是由于串行通讯参数配置错误或者数据传输过程中产生了错误。

实验总结:通过本次实验,我们了解了串行通讯的基本概念和原理,学习了串行通讯的常用协议和流程,掌握了使用串行通讯进行数据传输的方法。

在实验中,我们成功完成了串行通讯的发送和接收功能,并验证了接收的数据是否正确。

实验中还存在一些问题,比如串行通讯的参数配置可能会影响数据的传输效果,我们需要根据具体情况选择合适的参数。

另外,数据传输中可能会产生噪声和错误,我们需要采取一些纠错措施来提高数据的传输可靠性。

总的来说,本次实验对我们了解串行通讯的原理和应用有很大帮助,为今后的学习和实践打下了良好的基础。

串口通信实验报告基本实验:16位的乘法器设计思想:乘法器根据以往学过数电的设计经验,应该是移位相加的方法,设被乘数为[15:0]a,乘数为[15:0]b,则从b的最高位开始算起,c初值为0,为b最高位为1,则c就等于c+a;接下来,若b的次高位为1,则c左移一位加a,若为0则c左移一位就可以了,这样的步骤做到b的最低位那么c的值就是a*b,当然最好c是中间寄存器,这样结果才不会出现中间值。

实验的源码:module muti(clk,rst,ready,a,b,c);input clk;input rst;input [15:0]a;input [15:0]b;output [31:0]c;output ready;reg [31:0]c;reg ready;reg [31:0]temp;reg [5:0]n;always @(posedge clk or posedge rst)beginif(rst)beginc<=0;ready<=1;temp<=0;n<=32;endelseif(ready)begintemp<=0;n<=32;ready<=0;endelseif(n)beginif(b[n-1])begintemp<=(temp<<1)+a;n<=n-1;endbegintemp<=temp<<1;n<=n-1;endendelsebeginc<=temp;n<=32;ready<=1;endendendmodul测试代码:`timescale 1ns/1ns module tb;reg clk;reg [15:0]a;reg [15:0]b;reg rst;wire ready;wire [31:0]c;always #10 clk=~clk; initialbeginrst<=1;clk<=0;a=0;b=0;#10 rst=0;#21 a=21;b=32;#650 a=3;b=4;#700 $stop;endmuti muti_unit(.a(a),.b(b),.rst(rst),.clk(clk),.ready(ready),.c(c));endmodule这边a被乘数,b是乘数,当rst为高时,则将c置0,ready置一,ready信号为高表示此时空闲可以计算,rst为低时则开始计算,21*32为672,3*4为12,在乘法操作时,ready信号为低电平表示在工作中不能再输入进行计算,当计算结束则变为高电平。

串口传输实验总结引言串口通信是一种常见的数据传输方式,特别适用于嵌入式系统和电子设备之间的通信。

在本次实验中,我们通过使用串口通信来实现数据的传输和接收。

本文档将总结我们在这个实验中的经验和教训,并提供一些关于串口传输的相关知识。

实验背景串口,也被称为通用异步收发传输器(UART),是一种用于在电子设备之间传输数据的常见接口。

串口通信使用两根线来传输数据,一根用于发送数据(Tx)而另一根用于接收数据(Rx)。

串口通信的一个重要特点是它是异步的,即发送端和接收端可以根据各自的节奏进行数据传输。

实验过程我们在本次实验中使用了一块嵌入式开发板和计算机之间的串口通信来实现数据传输。

以下是我们完成实验的步骤:1.配置串口通信参数:我们首先需要确定串口通信的参数,例如波特率、数据位、停止位和校验位等。

这些参数需要在发送端和接收端进行一致配置,以确保正常的数据传输。

2.编写发送端代码:我们使用编程语言编写了一个简单的程序,通过串口发送数据给接收端。

在这个程序中,我们首先初始化串口,然后将要发送的数据写入串口缓冲区,最后启动数据传输。

3.编写接收端代码:我们同样使用编程语言编写了一个程序,用于接收来自发送端的数据。

在这个程序中,我们首先初始化串口,然后开启中断监听串口接收事件,当接收到数据时,触发相应的中断处理函数来处理接收到的数据。

4.运行程序并进行测试:我们将发送端和接收端的代码分别烧录到嵌入式开发板和计算机上,并运行程序进行测试。

我们发送了不同类型的数据,例如字节、字符串和数字等,并检查接收端是否成功接收到并正确处理这些数据。

实验结果在我们的实验中,我们成功地实现了串口数据的传输和接收。

我们发送的各种类型的数据都能够被接收端正确地接收到并进行处理。

通过对输出结果的检查,我们确认了数据的准确性和完整性。

实验总结通过这个实验,我们深入了解了串口通信的原理和应用。

以下是我们在实验中的一些总结和教训:1.注意配置参数的一致性:在串口通信中,发送端和接收端的串口配置参数必须一致,包括波特率、数据位、停止位和校验位。

实验七UART串口通信一、实验目的1.能够理解UART串口通信的基本原理和通信过程。

2.学会通过配置寄存器,实现串口通信的基本操作过程。

二、实验内容通过对单片机编程来实现UART串口通信的基本过程,通过串口调试助手发送数据到单片机,并在数码管上显示出来。

三、实验参考原理3.1 串行通信的初步认识通信按照基本类型可以分为并行通信和串行通信。

并行通信时数据的各个位同时传送,可以实现字节为单位通信,但是因为通信线多占用资源多,成本高。

比如我们前边用到的P0 = 0xfe;一次给P0的8个IO口分别赋值,同时进行信号输出,类似于有8个车道同时可以过去8辆车一样,这种形式就是并行的,我们习惯上还称P0、P1、P2和P3为51单片机的4组并行总线。

而串行通信,就如同一条车道,一次只能一辆车过去,如果一个0xfe这样一个字节的数据要传输过去的话,假如低位在前高位在后,那发送方式就是0-1-1-1-1-1-1-1-1,一位一位的发送出去的,要发送8次才能发送完一个字节。

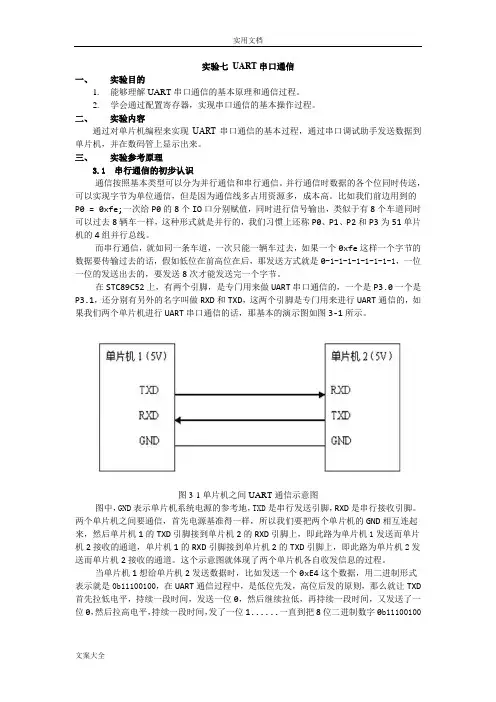

在STC89C52上,有两个引脚,是专门用来做UART串口通信的,一个是P3.0一个是P3.1,还分别有另外的名字叫做RXD和TXD,这两个引脚是专门用来进行UART通信的,如果我们两个单片机进行UART串口通信的话,那基本的演示图如图3-1所示。

图3-1 单片机之间UART通信示意图图中,GND表示单片机系统电源的参考地,TXD是串行发送引脚,RXD是串行接收引脚。

两个单片机之间要通信,首先电源基准得一样,所以我们要把两个单片机的GND相互连起来,然后单片机1的TXD引脚接到单片机2的RXD引脚上,即此路为单片机1发送而单片机2接收的通道,单片机1的RXD引脚接到单片机2的TXD引脚上,即此路为单片机2发送而单片机2接收的通道。

这个示意图就体现了两个单片机各自收发信息的过程。

当单片机1想给单片机2发送数据时,比如发送一个0xE4这个数据,用二进制形式表示就是0b11100100,在UART通信过程中,是低位先发,高位后发的原则,那么就让TXD 首先拉低电平,持续一段时间,发送一位0,然后继续拉低,再持续一段时间,又发送了一位0,然后拉高电平,持续一段时间,发了一位1......一直到把8位二进制数字0b11100100全部发送完毕。

一、实验目的1. 了解串口通信的基本原理和作用。

2. 掌握单片机串口通信的编程方法。

3. 通过实验验证串口通信的可靠性和稳定性。

二、实验原理串口通信是指通过串行通信接口进行的数据传输方式。

串口通信具有传输速率较低、通信距离较近等特点,但具有简单、可靠、易于实现等优点。

在单片机应用中,串口通信广泛应用于数据采集、设备控制、远程通信等领域。

单片机串口通信的基本原理是:通过单片机的串行通信接口(如UART、USART等)发送和接收数据。

串口通信的数据格式通常包括起始位、数据位、奇偶校验位和停止位。

三、实验设备1. 单片机开发板(如STC89C52、STM32等)2. 串口调试助手(如PuTTY、串口调试助手等)3. 仿真软件(如Proteus、Keil等)四、实验内容1. 串口通信硬件连接2. 串口通信软件编程3. 串口通信调试与验证五、实验步骤1. 硬件连接(1)将单片机的TXD、RXD、GND等引脚与计算机的串口通信线相连。

(2)将计算机的串口通信线与串口调试助手相连。

2. 软件编程(1)在仿真软件中编写单片机程序,实现数据的发送和接收。

(2)在串口调试助手中编写程序,实现数据的发送和接收。

3. 调试与验证(1)在仿真软件中运行单片机程序,观察串口调试助手中的数据是否正确接收。

(2)修改单片机程序,改变发送和接收的数据,验证串口通信的可靠性。

六、实验结果与分析1. 实验结果通过实验,成功实现了单片机与计算机之间的串口通信。

在串口调试助手中,可以观察到单片机发送的数据被正确接收,同时也可以向单片机发送数据。

2. 实验分析(1)实验验证了单片机串口通信的可靠性和稳定性。

(2)实验过程中,需要注意波特率、数据位、停止位等参数的设置,以保证通信的准确性。

(3)实验过程中,可以尝试不同的通信协议,如ASCII码、十六进制等,以适应不同的应用场景。

七、实验心得1. 串口通信是一种简单、可靠的数据传输方式,在单片机应用中具有广泛的应用前景。

UART串口通信一、实验目的1、学习实验系统的基本操作,了解在实验系统中进行程序设计、仿真和调试的操作方法和步骤;2、熟悉Proteus的虚拟仪器的使用;3、熟悉并灵活运用单片机的UART通信功能;4、熟悉虚拟串口在仿真中的应用;5、实现单片机点对点串口通信,即单片机与单片机间的相互通信;6、实现单片机与计算机串口通信。

二、实验原理1、如图(1),有甲、乙两个单片机,甲单片机外接一个3×3矩阵键盘和8个LED;乙单片机外接一个独立按键和一个数码管;甲乙两个单片机通过串口进行通信(即TXD和RXD引脚)。

图(1)单片机点对点串口通信电路仿真图按下甲单片机矩阵键盘的任意一个按键,将该键编号(编号自己设定)通过串口发送给乙单片机,乙单片机在数码管上显示出对应的按键号;按下乙单片机的外接独立按键控制甲单片机的8个LED(按键之前8个LED灯均点亮),具体关系为:(1)第1次按键,乙单片机向甲单片机通过串口发送命令字符A,甲收到该命令,使前4个LED灯亮,后4个不亮;(2)第2次按键,乙单片机向甲单片机通过串口发送命令字符B,甲收到该命令,使前4个LED不亮,后4个亮;(3)第3次按键,乙单片机向甲单片机通过串口发送命令字符C,甲收到该命令,使奇数个灯亮,偶数个灯不亮;(4)第4次按键,乙单片机向甲单片机通过串口发送命令字符D,甲收到该命令,使偶数个灯亮,奇数个灯不亮;(5)第5次按键,乙单片机向甲单片机通过串口发送命令字符E,甲收到该命令,使所有灯都不亮。

2、单片机与计算机串口通信,如图(2),需要一个单片机和一个COMPIM器件,连接电路时,将单片机的RXD和COMPIM的RXD相连,单片机的TXD与COMPIM的TXD 相连,即同名引脚相连,其它的引脚悬空。

图(2)单片机与与计算机串口通信电路仿真图实验内容:设置单片机的串口为工作方式1,波特率设置为9600。

计算机通过串口调试助手向单片机依次发送字符1、2、3、4,单片机收到每个字符后向计算机回复相应的内容,具体要求如表1所示:表1 单片机与计算机通信内容三、实验步骤1、硬件仿真。

实验二UART串口通信实验一、实验目的:1、了解S3C2410X处理器UART相关控制寄存器的使用;2、熟悉ARM处理器系统硬件电路中UART接口的设计方法;3、掌握ARM处理器串行通信的软件编程方法。

二、实验原理S3C2410X UART 单元提供三个独立的异步串行通信接口,皆可工作于中断和DMA模式。

使用系统时钟最高波特率达230.4Kbps,如果使用外部设备提供的时钟,可以达到更高的速率。

每一个UART单元包含一个16字节的FIFO,用于数据的接收和发送。

S3C2410X UART支持可编程波特率,红外发送/接收,一个或两个停止位,8bit数据宽度和1bit奇偶校验。

三、实验仪器设备1、EDUKIT-IV实验平台2、Mini2410 核心子板3、5V/2A电源适配器4、Emlink-w仿真器套件5、交叉串口线四、实验步骤(4)打开H-JTAG软件设置LPT线连接(5)探测芯片内核(ARM920T)(6)打开工程文件UART_TEST.UV2,选择Bulild Target或编译链接工程,如果显示0 Errors表示编译成功。

(7)选择开始->程序->附件->通讯->超级终端,设置COM1通讯,115200波特率,8位数据位,1位奇偶校验位。

(8)选择Debug->Start Debug Session或者调试工程并下载至SDRAM中。

(9)选择Debug->Run运行程序或者全速运行程序,并在超级终端中观察实验结果。

5、实验结果分析超级终端显示:UART0 Communication Test ExamplePlease input words, then press Enter:/> abcThe words that you input are: abc满足实验要求。

实验报告一.实验任务采用UART IP 核,实现Nexys4 或Nexys4 DDR 实验板UART接口之间的通信。

要求当拨动开关时,将开关对应的值通过UART1发送到UART2,同时利用LED 灯指示UART2接收到的当前开关的值;当按下按键时,将按键对应的值通过UART2发送到UART1,同时利用数码管指示UART1接收到的当前按下的按键位置码(C,U,d,L,r)。

UART 波特率为9600bps。

二.硬件电路框图三.程序源代码#include "xil_io.h"#include "stdio.h"#include "xintc_l.h"#include "xgpio_l.h"#include "xuartlite_l.h"void UART_SR();void BtnHandler();void My_ISR() __attribute__ ((interrupt_handler));int main(){Xil_Out32(XPAR_AXI_GPIO_2_BASEADDR+XGPIO_TRI_OFFSET,0x1f); //设定BUTTON为输入方式Xil_Out16(XPAR_GPIO_0_BASEADDR+XGPIO_TRI2_OFFSET,0x0); //LED灯输出Xil_Out32(XPAR_AXI_GPIO_2_BASEADDR+XGPIO_IER_OFFSET,XGPIO_IR_CH1_MASK); //通道1允许中断Xil_Out32(XPAR_AXI_GPIO_2_BASEADDR+XGPIO_GIE_OFFSET,XGPIO_GIE_GINTR_ENABLE_ MASK); //允许GPIO中断输出Xil_Out32(XPAR_AXI_UARTLITE_3_BASEADDR+XUL_CONTROL_REG_OFFSET,XUL_CR_ENABL E_INTR|XUL_CR_FIFO_RX_RESET|XUL_CR_FIFO_TX_RESET);//使能中断,清除RX,TX寄存器Xil_Out32(XPAR_AXI_INTC_0_BASEADDR+XIN_IER_OFFSET,XPAR_AXI_GPIO_2_IP2INTC_IRPT _MASK|XPAR_AXI_UARTLITE_3_INTERRUPT_MASK);//对中断控制器进行中断源使能Xil_Out32(XPAR_AXI_INTC_0_BASEADDR+XIN_MER_OFFSET,XIN_INT_MASTER_ENABLE_MA SK|XIN_INT_HARDWARE_ENABLE_MASK);microblaze_enable_interrupts();//允许处理器处理中断return 0;}void My_ISR(){int status;status=Xil_In32(XPAR_AXI_INTC_0_BASEADDR+XIN_ISR_OFFSET);//读取ISRxil_printf("0x%x\n",status);if((status&XPAR_AXI_UARTLITE_3_INTERRUPT_MASK)==XPAR_AXI_UARTLITE_3_INTERRUPT _MASK){UART_SR();}elseif((status&XPAR_AXI_GPIO_2_IP2INTC_IRPT_MASK)==XPAR_AXI_GPIO_2_IP2INTC_IRPT_MASK) BtnHandler(); //调用按键中断Xil_Out32(XPAR_AXI_INTC_0_BASEADDR+XIN_IAR_OFFSET,status);//写IAR}void UART_SR(){Xil_Out16(XPAR_GPIO_0_BASEADDR+XGPIO_DATA2_OFFSET,Xil_In32(XPAR_AXI_UARTLITE_3 _BASEADDR+XUL_RX_FIFO_OFFSET));}void BtnHandler(){unsigned short btncode;btncode=Xil_In8(XPAR_AXI_GPIO_2_BASEADDR+XGPIO_DATA_OFFSET)&0x1f;while((Xil_In32(XPAR_AXI_GPIO_2_BASEADDR+XGPIO_DATA_OFFSET)&0x1f)!=0){xil_printf("The pushed button's code is 0x%x\n",btncode);//打印输入的按键序号}switch(btncode){case 0x1:Xil_Out32(XPAR_AXI_UARTLITE_3_BASEADDR+XUL_TX_FIFO_OFFSET,btncode);break;case 0x2:Xil_Out32(XPAR_AXI_UARTLITE_3_BASEADDR+XUL_TX_FIFO_OFFSET,btncode);break;case 0x4:Xil_Out32(XPAR_AXI_UARTLITE_3_BASEADDR+XUL_TX_FIFO_OFFSET,btncode);break;case 0x8:Xil_Out32(XPAR_AXI_UARTLITE_3_BASEADDR+XUL_TX_FIFO_OFFSET,btncode);break;case 0x10:Xil_Out32(XPAR_AXI_UARTLITE_3_BASEADDR+XUL_TX_FIFO_OFFSET,btncode);break;default:break;}Xil_Out32(XPAR_AXI_GPIO_2_BASEADDR+XGPIO_ISR_OFFSET,Xil_In32(XPAR_AXI_GPIO_2_B ASEADDR+XGPIO_ISR_OFFSET)); //清除中断}四.实验结果五.实验心得在这个实验当中,主要是运用UART模块实现Nexys4 DDR 实验板UART接口之间的通信,在实验进程中,硬件平台搭设时,需要增加新的UART IP核作为标准输入输出接口,另外在管脚约束时,需要自己重新定义。

uart实验报告

1. 实验目的

本次实验的目的是验证串口通信协议UART的功能,通过USB-UART转换器控制开发板的板载LED的状态,以及通过调试软件UART通信观察调试台的信息输出。

2. 实验内容

本次实验环境是Espruino开发板,首先通过USB线将开发板连接至PC,使用一款USB-UART转换器将开发板连接至调试软件 PuTTY上,去UART连接口设置为9200,然后打开Espruino IDE软件,在终端上编写代码,不断编译及执行代码,以实现LED灯的转换状态。

具体实现步骤如下:

(1)安装Espruino IDE软件,建立编程环境,编写具体编程代码。

(3)将编写好的代码上传到Espruino,在调试软件 PuTTY 上可以看到板载 LED有明暗转换的视觉效果,从而验证Uart功能正常。

实验七、UART串行数据通信实验1(查询与中断方式)一、实验目的通过实验,掌握UART查询与中断方式的程序的设计。

二、实验设备●硬件:PC 机一台●LPC2131教学实验开发平台一套●软件:Windows98/XP/2000 系统,ADS 1.2 集成开发环境。

●EasyARM工具软件。

三、实验原理EasyARM2131 开发板上,UART0 的电路图如图8.1 所示,当跳线JP6 分别选择TxD0和RxD0 端时方可进行UART0 通讯实验。

图8.1 UART0 电路原理图四、实验内容实验内容1使用查询方式,通过串口0 接收上位机发送的字符串如“Hello EasyARM2131!”,然后送回上位机显示,主程序以及各子程序流程如图8.2 所示。

(改写发送内容,字符个数不同)。

说明:需要上位机(PC机)串口终端如EasyARM.exe 软件。

使用串口延长线把LPC2131教学实验开发平台的CZ2(UART0)与PC机的COM1 连接。

PC 机运行EasyARM 软件,设置串口为COM1,波特率为115200,然后选择【设置】->【发送数据】,在弹出的发送数据窗口中点击“高级”即可打开接收窗口。

图8.2 串口实验相关程序流程图1.实验预习要求①研读LPC2000 UART工作原理与控制章节,注意FIFO 接收情况的特性。

②了解LPC2131教学实验开发平台的硬件结构,注意串口部分的电路。

2.实验步骤①启动ADS 1.2,使用ARM Executable Image for lpc2131工程模板建立一个工程DataRet_C。

②在user 组中的main.c 中编写主程序代码,在项目中的config.h 文件中加入#include <stdio.h>。

③选用DebugInFlash生成目标,然后编译连接工程。

④将EasyARM2131开发板上的JP6跳线分别选择TxD0和RxD0端时,方可进行UART0通信实验。

实验四UART串口通信学院:研究生院学号:1400030034姓名:张秋明一、实验目得及要求设计一个UART串口通信协议,实现“串<-->并”转换功能得电路,也就就是“通用异步收发器”。

二、实验原理UART就是一种通用串行数据总线,用于异步通信。

该总线双向通信,可以实现全双工传输与接收。

在嵌入式设计中,UART用来主机与辅助设备通信,如汽车音响与外接AP之间得通信,与PC机通信包括与监控调试器与其它器件,如EEPROM通信。

UART作为异步串口通信协议得一种,工作原理就是将传输数据得每个字符一位接一位地传输。

其中各位得意义如下:起始位:先发出一个逻辑”0”得信号,表示传输字符得开始。

资料位:紧接着起始位之后。

资料位得个数可以就是4.5.6.7、8等,构成一个字符。

通常采用ASCII码。

从最低位开始传送,靠时钟定位。

奇偶校验位:资料位加上这一位后,使得“1”得位数应为偶数(偶校验)或奇数(奇校验),以此来校验资料传送得正确性。

停止位:它就是一个字符数据得结束标志。

可以就是1位、1.5位、2位得高电平。

由于数据就是在传输线上定时得,并且每一个设备有其自己得时钟,很可能在通信中两台设备间出现了小小得不同步。

因此停止位不仅仅就是表示传输得结束,并且提供计算机校正时钟同步得机会。

适用于停止位得位数越多,不同时钟同步得容忍程度越大,但就是数据传输率同时也越慢。

空闲位:处于逻辑“1”状态,表示当前线路上没有资料传送。

波特率:就是衡量资料传送速率得指标。

表示每秒钟传送得符号数(symbol)。

一个符号代表得信息量(比特数)与符号得阶数有关。

例如资料传送速率为120字符/秒,传输使用256阶符号,每个符号代表8bit,则波特率就就是120baud,比特率就是120*8=960bit/s。

这两者得概念很容易搞错。

三、实现程序library ieee;use ieee、std_logic_1164.all;use ieee、std_logic_arith、all;use ieee、std_logic_unsigned、all;entity uart isport(clk : in std_logic; --系统时钟rst_n: in std_logic; --复位信号rs232_rx: in std_logic; --RS232接收数据信号;rs232_tx: out std_logic --RS232发送数据信号;); end uart;architecture behav of uart isponent uart_rx port(clk : in std_logic; --系统时钟rst_n: in std_logic; --复位信号rs232_rx: in std_logic; --RS232接收数据信号clk_bps: in std_logic; --此时clk_bps得高电平为接收数据得采样点bps_start:out std_logic; --接收到数据后,波特率时钟启动置位rx_data: out std_logic_vector(7 downto 0); --接收数据寄存器,保存直至下一个数据来到rx_int: out std_logic --接收数据中断信号,接收数据期间时钟为高电平,传送给串口发送);end ponent;ponent speed_select port(clk : in std_logic; --系统时钟rst_n: in std_logic; --复位信号clk_bps: out std_logic; --此时clk_bps 得高电平为接收或者发送数据位得中间采样点bps_start:in std_logic --接收数据后,波特率时钟启动信号置位);end ponent;ponent uart_tx port(clk : in std_logic; --系统时钟rst_n: in std_logic; --复位信号rs232_tx: out std_logic; --RS232接收数据信号clk_bps: in std_logic; --此时clk_bps 得高电平为接收数据得采样点bps_start:out std_logic; --接收到数据后,波特率时钟启动置位rx_data: in std_logic_vector(7 downto 0); --接收数据寄存器,保存直至下一个数据来到rx_int: in std_logic --接收数据中断信号,接收数据期间时钟为高电平,传送给串口发送模块,使得串口正在进行接收数据得时候,发送模块不工作,避免了一个完整得数据(1位起始位、8位数据位、1位停止位)还没有接收完全时,发送模块就已经将不正确得数据传输出去);end ponent;signal bps_start_1:std_logic;signal bps_start_2:std_logic;signal clk_bps_1:std_logic;signal clk_bps_2:std_logic;signal rx_data:std_logic_vector(7 downto 0);signal rx_int:std_logic;beginRX_TOP: uart_rx port map(clk=>clk,rst_n=>rst_n,rs232_rx=>rs232_rx,clk_bps=>clk_bps_1,bps_start=>bps_start_1,rx_data=>rx_data,rx_int=>rx_int);SPEED_TOP_RX: speed_select port map(clk=>clk,rst_n=>rst_n,clk_bps=>clk_bps_1,bps_start=>bps_start_1);TX_TOP:uart_tx port map(clk=>clk, --系统时钟rst_n=>rst_n, --复位信号rs232_tx=>rs232_tx, --RS232发送数据信号clk_bps=>clk_bps_2, --此时clk_bps 得高电平为发送数据得采样点bps_start=>bps_start_2, --接收到数据后,波特率时钟启动置位rx_data=>rx_data, --接收数据寄存器,保存直至下一个数据来到rx_int=>rx_int --接收数据中断信号,接收数据期间时钟为高电平,传送给串口发送模块,使得串口正在进行接收数据得时候,发送模块不工作,避免了一个完整得数据(1位起始位、8位数据位、1位停止位)还没有接收完全时,发送模块就已经将不正确得数据传输出去);SPEED_TOP_TX: speed_select port map(clk=>clk,rst_n=>rst_n,clk_bps=>clk_bps_2,bps_start=>bps_start_2);end behav;-----------------------------------------------------------------------------------------------------------------------3个子模块------------------------------------------------------------------------------异步接收模块-------------------------------------------library ieee;use ieee、std_logic_1164.all;use ieee、std_logic_unsigned、all;entity uart_rx isport(clk : in std_logic; --系统时钟rst_n: in std_logic; --复位信号rs232_rx: in std_logic; --RS232接收数据信号clk_bps: in std_logic; --此时clk_bps得高电平为接收数据得采样点bps_start:out std_logic; --接收到数据后,波特率时钟启动置位rx_data: out std_logic_vector(7 downto 0); --接收数据寄存器,保存直至下一个数据来到rx_int: out std_logic --接收数据中断信号,接收数据期间时钟为高电平,传送给串口发送模块,使得串口正在进行接收数据得时候,发送模块不工作,避免了一个完整得数据(1位起始位、8位数据位、1位停止位)还没有接收完全时,发送模块就已经将不正确得数据传输出去);end uart_rx;architecture behav of uart_rx issignal rs232_rx0: std_logic;signal rs232_rx1: std_logic;signal rs232_rx2: std_logic;signal rs232_rx3: std_logic;signal neg_rs232_rx:std_logic;signal bps_start_r:std_logic;signal num:integer;signal rx_data_r:std_logic_vector(7 downto 0); --串口接收数据寄存器,保存直至下一个数据到来beginprocess(clk,rst_n)beginif (rst_n='0')thenrs232_rx0<='0';rs232_rx1<='0';rs232_rx2<='0';rs232_rx3<='0';elseif (rising_edge(clk)) thenrs232_rx0<=rs232_rx;rs232_rx1<=rs232_rx0;rs232_rx2<=rs232_rx1;rs232_rx3<=rs232_rx2;end if;end if;neg_rs232_rx <=rs232_rx3 and rs232_rx2 and not(rs232_rx1)and not(rs232_rx0);end process;process(clk,rst_n)beginif (rst_n='0')thenbps_start_r<='0';rx_int<='0';elseif (rising_edge(clk)) thenif(neg_rs232_rx='1') then --接收到串口数据线rs232_rx 得下降沿标志信号bps_start_r<='1'; --启动串口准备数据接收rx_int<='1'; --接收数据中断信号使能else if((num= 15) and (clk_bps='1')) then --接收完有用数据信息bps_start_r<='0'; --数据接收完毕,释放波特率启动信号rx_int<='0'; --接收数据中断信号关闭end if;end if;end if;end if;bps_start<=bps_start_r;end process;process(clk,rst_n)beginif (rst_n='0')thenrx_data_r<="00000000";rx_data<="00000000";num<=0;elseif (rising_edge(clk)) thenif(clk_bps='1')thennum<=num+1;case num iswhen 1=>rx_data_r(0)<=rs232_rx;--锁存第0bitwhen 2=>rx_data_r(1)<=rs232_rx;--锁存第0bitwhen 3=>rx_data_r(2)<=rs232_rx;--锁存第0bitwhen 4=>rx_data_r(3)<=rs232_rx;--锁存第0bitwhen 5=>rx_data_r(4)<=rs232_rx;--锁存第0bitwhen 6=>rx_data_r(5)<=rs232_rx;--锁存第0bitwhen 7=>rx_data_r(6)<=rs232_rx;--锁存第0bitwhen 8=>rx_data_r(7)<=rs232_rx;--锁存第0bitwhen 10=>rx_data<=rx_data_r;when 11=>num<=15;when others=>null;end case;if(num=15) thennum<=0;end if;end if;end if;end if;end process;end behav;---------------------------------波特率控制模块-----------------------------------------library ieee;use ieee、std_logic_1164.all;use ieee、std_logic_arith、all;use ieee、std_logic_unsigned、all;entity speed_select isport(clk : in std_logic; --系统时钟rst_n: in std_logic; --复位信号clk_bps: out std_logic; --此时clk_bps得高电平为接收或者发送数据位得中间采样点bps_start:in std_logic --接收数据后,波特率时钟启动信号置位或者开始发送数据时,波特率时钟启动信号置位);end speed_select;architecture behav of speed_select issignal cnt:std_logic_vector(12 downto 0);signal clk_bps_r:std_logic;constant BPS_PARA:integer:=5207;constant BPS_PARA_2:integer:=2603;beginprocess(clk,rst_n)beginif (rst_n='0')thencnt<="00";elseif (rising_edge(clk)) thenif((cnt=BPS_PARA)or(bps_start='0')) thencnt<="00"; --波特率计数器清零elsecnt<=cnt+'1'; --波特率时钟计数启动end if;end if;end if;end process;process(clk,rst_n)beginif (rst_n='0')thenclk_bps_r<='0';elseif (rising_edge(clk)) thenif(cnt=BPS_PARA_2) thenclk_bps_r<='1'; --clk_bps_r高电平为接收数据位得中间采样点,同时也作为发送数据得数据改变点elseclk_bps_r<='0'; --波特率计数器清零end if;end if;end if;clk_bps<=clk_bps_r;end process;end behav;---------------------------------异步发送模块------------------------------------------- library ieee;use ieee、std_logic_1164.all;use ieee、std_logic_unsigned、all;entity uart_tx isport(clk : in std_logic; --系统时钟rst_n: in std_logic; --复位信号rs232_tx: out std_logic; --RS232接收数据信号clk_bps: in std_logic; --此时clk_bps得高电平为接收数据得采样点bps_start:out std_logic; --接收到数据后,波特率时钟启动置位rx_data: in std_logic_vector(7 downto 0); --接收数据寄存器,保存直至下一个数据来到rx_int: in std_logic --接收数据中断信号,接收数据期间时钟为高电平,传送给串口发送模块,使得串口正在进行接收数据得时候,发送模块不工作,避免了一个完整得数据(1位起始位、8位数据位、1位停止位)还没有接收完全时,发送模块就已经将不正确得数据传输出去);end uart_tx;architecture behav of uart_tx issignal rx_int0: std_logic;signal rx_int1: std_logic;signal rx_int2: std_logic;signal neg_rx_int:std_logic;signal bps_start_r:std_logic;signal num:integer;signal tx_data:std_logic_vector(7 downto 0); --串口接收数据寄存器,保存直至下一个数据到来beginprocess(clk,rst_n)beginif (rst_n='0')thenrx_int0<='0';rx_int1<='0';rx_int2<='0';elseif (rising_edge(clk)) thenrx_int0<=rx_int;rx_int1<=rx_int0;rx_int2<=rx_int1;end if;end if;neg_rx_int <=not(rx_int1)and (rx_int2);end process;process(clk,rst_n)beginif (rst_n='0')thenbps_start_r<='0';tx_data<="00000000";elseif (rising_edge(clk)) thenif(neg_rx_int='1') then --接收到串口数据线rs232_rx得下降沿标志信号bps_start_r<='1'; --启动串口准备数据接收tx_data<=rx_data; --接收数据中断信号使能else if((num= 15) and (clk_bps='1')) then --接收完有用数据信息bps_start_r<='0'; --数据接收完毕,释放波特率启动信号end if;end if;end if;end if;bps_start<=bps_start_r;end process;process(clk,rst_n)beginif (rst_n='0')thenrs232_tx<='1';num<=0;elseif (rising_edge(clk)) thenif(clk_bps='1')thennum<=num+1;case num iswhen 1=>rs232_tx<='0';when 2=>rs232_tx<=tx_data(0);--发送第1bitwhen 3=>rs232_tx<=tx_data(1);--发送第2bitwhen 4=>rs232_tx<=tx_data(2);--发送第3bitwhen 5=>rs232_tx<=tx_data(3);--发送第4bitwhen 6=>rs232_tx<=tx_data(4);--发送第5bitwhen 7=>rs232_tx<=tx_data(5);--发送第6bitwhen 8=>rs232_tx<=tx_data(6);--发送第7bitwhen 9=>rs232_tx<=tx_data(7);--发送第8bitwhen 10=>rs232_tx<='1';when 11=>num<=15;when others=>null;end case;if(num=15) thennum<=0;end if;end if;end if;end if;end process;end behav;四、实验步骤1.建立新工程UART,选择芯片,型号为cyclone ii EP2C35F484C8。

实验四UART串口通信学院:研究生院学号:1400030034 姓名:张秋明一、实验目的及要求设计一个UART串口通信协议,实现“串<-->并”转换功能的电路,也就是“通用异步收发器”。

二、实验原理UART是一种通用串行数据总线,用于异步通信。

该总线双向通信,可以实现全双工传输和接收。

在嵌入式设计中,UART用来主机与辅助设备通信,如汽车音响与外接AP之间的通信,与PC机通信包括与监控调试器和其它器件,如EEPROM通信。

UART作为异步串口通信协议的一种,工作原理是将传输数据的每个字符一位接一位地传输。

其中各位的意义如下:起始位:先发出一个逻辑”0”的信号,表示传输字符的开始。

资料位:紧接着起始位之后。

资料位的个数可以是4、5、6、7、8等,构成一个字符。

通常采用ASCII码。

从最低位开始传送,靠时钟定位。

奇偶校验位:资料位加上这一位后,使得“1”的位数应为偶数(偶校验)或奇数(奇校验),以此来校验资料传送的正确性。

停止位:它是一个字符数据的结束标志。

可以是1位、1.5位、2位的高电平。

由于数据是在传输线上定时的,并且每一个设备有其自己的时钟,很可能在通信中两台设备间出现了小小的不同步。

因此停止位不仅仅是表示传输的结束,并且提供计算机校正时钟同步的机会。

适用于停止位的位数越多,不同时钟同步的容忍程度越大,但是数据传输率同时也越慢。

空闲位:处于逻辑“1”状态,表示当前线路上没有资料传送。

波特率:是衡量资料传送速率的指标。

表示每秒钟传送的符号数(symbol)。

一个符号代表的信息量(比特数)与符号的阶数有关。

例如资料传送速率为120字符/秒,传输使用256阶符号,每个符号代表8bit,则波特率就是120baud,比特率是120*8=960bit/s。

这两者的概念很容易搞错。

三、实现程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity uart isport(clk : in std_logic; --系统时钟rst_n: in std_logic; --复位信号rs232_rx: in std_logic; --RS232接收数据信号;rs232_tx: out std_logic --RS232发送数据信号;);end uart;architecture behav of uart iscomponent uart_rx port(clk : in std_logic; --系统时钟rst_n: in std_logic; --复位信号rs232_rx: in std_logic; --RS232接收数据信号clk_bps: in std_logic; --此时clk_bps 的高电平为接收数据的采样点bps_start:out std_logic; --接收到数据后,波特率时钟启动置位rx_data: out std_logic_vector(7 downto 0); --接收数据寄存器,保存直至下一个数据来到rx_int: out std_logic --接收数据中断信号,接收数据期间时钟为高电平,传送给串口发送);end component;component speed_select port(clk : in std_logic; --系统时钟rst_n: in std_logic; --复位信号clk_bps: out std_logic; --此时clk_bps的高电平为接收或者发送数据位的中间采样点bps_start:in std_logic --接收数据后,波特率时钟启动信号置位);end component;component uart_tx port(clk : in std_logic; --系统时钟rst_n: in std_logic; --复位信号rs232_tx: out std_logic; --RS232接收数据信号clk_bps: in std_logic; --此时clk_bps的高电平为接收数据的采样点bps_start:out std_logic; --接收到数据后,波特率时钟启动置位rx_data: in std_logic_vector(7 downto 0); --接收数据寄存器,保存直至下一个数据来到rx_int: in std_logic --接收数据中断信号,接收数据期间时钟为高电平,传送给串口发送模块,使得串口正在进行接收数据的时候,发送模块不工作,避免了一个完整的数据(1位起始位、8位数据位、1位停止位)还没有接收完全时,发送模块就已经将不正确的数据传输出去);end component;signal bps_start_1:std_logic;signal bps_start_2:std_logic;signal clk_bps_1:std_logic;signal clk_bps_2:std_logic;* * signal rx_data:std_logic_vector(7 downto 0);signal rx_int:std_logic;beginRX_TOP: uart_rx port map(clk=>clk,rst_n=>rst_n,rs232_rx=>rs232_rx,clk_bps=>clk_bps_1,bps_start=>bps_start_1,rx_data=>rx_data,rx_int=>rx_int);SPEED_TOP_RX: speed_select port map(clk=>clk,rst_n=>rst_n,clk_bps=>clk_bps_1,bps_start=>bps_start_1);TX_TOP:uart_tx port map(clk=>clk, --系统时钟rst_n=>rst_n, --复位信rs232_tx=>rs232_tx, --RS232发送数据信号clk_bps=>clk_bps_2, --此时clk_bps的高电平为发送数据的采样点bps_start=>bps_start_2, --接收到数据后,波特率时钟启动置位rx_data=>rx_data, --接收数据寄存器,保存直至下一个数据来到rx_int=>rx_int --接收数据中断信号,接收数据期间时钟为高电平,传送给串口发送模块,使得串口正在进行接收数据的时候,发送模块不工作,避免了一个完整的数据(1位起始位、8位数据位、1位停止位)还没有接收完全时,发送模块就已经将不正确的数据传输出去);SPEED_TOP_TX: speed_select port map(clk=>clk,rst_n=>rst_n,clk_bps=>clk_bps_2,bps_start=>bps_start_2);end behav;-----------------------------------------------------------------------------------------------------------------------3个子模块------------------------------------------------------------------------------异步接收模块-------------------------------------------library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity uart_rx isport(clk : in std_logic; --系统时钟rst_n: in std_logic; --复位信号rs232_rx: in std_logic; --RS232接收数据信号clk_bps: in std_logic; --此时clk_bps的高电平为接收数据的采样点bps_start:out std_logic; --接收到数据后,波特率时钟启动置位rx_data: out std_logic_vector(7 downto 0); --接收数据寄存器,保存直至下一个数据来到rx_int: out std_logic --接收数据中断信号,接收数据期间时钟为高电平,传送给串口发送模块,使得串口正在进行接收数据的时候,发送模块不工作,避免了一个完整的数据(1位起始位、8位数据位、1位停止位)还没有接收完全时,发送模块就已经将不正确的数据传输出去); end uart_rx;architecture behav of uart_rx issignal rs232_rx0: std_logic;signal rs232_rx1: std_logic;signal rs232_rx2: std_logic;signal rs232_rx3: std_logic;signal neg_rs232_rx:std_logic;signal bps_start_r:std_logic;signal num:integer;signal rx_data_r:std_logic_vector(7 downto 0); --串口接收数据寄存器,保存直至下一个数据到来begin* *process(clk,rst_n)beginif (rst_n='0')thenrs232_rx0<='0';rs232_rx1<='0';rs232_rx2<='0';rs232_rx3<='0';elseif (rising_edge(clk)) thenrs232_rx0<=rs232_rx;rs232_rx1<=rs232_rx0;rs232_rx2<=rs232_rx1;rs232_rx3<=rs232_rx2;end if;end if;neg_rs232_rx <=rs232_rx3 and rs232_rx2 and not(rs232_rx1)and not(rs232_rx0);end process;process(clk,rst_n)begin* * if (rst_n='0')thenbps_start_r<='0';rx_int<='0';elseif (rising_edge(clk)) thenif(neg_rs232_rx='1') then --接收到串口数据线rs232_rx的下降沿标志信号bps_start_r<='1'; --启动串口准备数据接收rx_int<='1'; --接收数据中断信号使能else if((num= 15) and (clk_bps='1')) then --接收完有用数据信息bps_start_r<='0'; --数据接收完毕,释放波特率启动信号rx_int<='0'; --接收数据中断信号关闭end if;end if;end if;end if;bps_start<=bps_start_r;end process;process(clk,rst_n)beginif (rst_n='0')thenrx_data_r<="00000000";rx_data<="00000000";num<=0;elseif (rising_edge(clk)) thenif(clk_bps='1')thennum<=num+1;case num iswhen 1=>rx_data_r(0)<=rs232_rx;--锁存第0bitwhen 2=>rx_data_r(1)<=rs232_rx;--锁存第0bitwhen 3=>rx_data_r(2)<=rs232_rx;--锁存第0bitwhen 4=>rx_data_r(3)<=rs232_rx;--锁存第0bitwhen 5=>rx_data_r(4)<=rs232_rx;--锁存第0bitwhen 6=>rx_data_r(5)<=rs232_rx;--锁存第0bitwhen 7=>rx_data_r(6)<=rs232_rx;--锁存第0bitwhen 8=>rx_data_r(7)<=rs232_rx;--锁存第0bitwhen 10=>rx_data<=rx_data_r;when 11=>num<=15;when others=>null;end case;if(num=15) thennum<=0;end if;end if;end if;end if;end process;end behav;---------------------------------波特率控制模块-----------------------------------------library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity speed_select isport(clk : in std_logic; --系统时钟rst_n: in std_logic; --复位信号clk_bps: out std_logic; --此时clk_bps的高电平为接收或者发送数据位的中间采样点bps_start:in std_logic --接收数据后,波特率时钟启动信号置位或者开始发送数据时,波特率时钟启动信号置位);end speed_select;architecture behav of speed_select issignal cnt:std_logic_vector(12 downto 0);signal clk_bps_r:std_logic;constant BPS_PARA:integer:=5207;constant BPS_PARA_2:integer:=2603;beginprocess(clk,rst_n)beginif (rst_n='0')thencnt<="0000000000000";elseif (rising_edge(clk)) thenif((cnt=BPS_PARA)or(bps_start='0')) thencnt<="0000000000000"; --波特率计数器清零elsecnt<=cnt+'1'; --波特率时钟计数启动end if;end if;end if;end process;process(clk,rst_n)beginif (rst_n='0')thenclk_bps_r<='0';elseif (rising_edge(clk)) thenif(cnt=BPS_PARA_2) thenclk_bps_r<='1'; --clk_bps_r高电平为接收数据位的中间采样点,同时也作为发送数据的数据改变点elseclk_bps_r<='0'; --波特率计数器清零end if;end if;end if;clk_bps<=clk_bps_r;end process;end behav;---------------------------------异步发送模块-------------------------------------------library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity uart_tx isport(clk : in std_logic; --系统时钟rst_n: in std_logic; --复位信号rs232_tx: out std_logic; --RS232接收数据信号clk_bps: in std_logic; --此时clk_bps的高电平为接收数据的采样点bps_start:out std_logic; --接收到数据后,波特率时钟启动置位rx_data: in std_logic_vector(7 downto 0); --接收数据寄存器,保存直至下一个数据来到rx_int: in std_logic --接收数据中断信号,接收数据期间时钟为高电平,传送给串口发送模块,使得串口正在进行接收数据的时候,发送模块不工作,避免了一个完整的数据(1位起始位、8位数据位、1位停止位)还没有接收完全时,发送模块就已经将不正确的数据传输出去); end uart_tx;architecture behav of uart_tx issignal rx_int0: std_logic;signal rx_int1: std_logic;signal rx_int2: std_logic;signal neg_rx_int:std_logic;signal bps_start_r:std_logic;signal num:integer;signal tx_data:std_logic_vector(7 downto 0); --串口接收数据寄存器,保存直至下一个数据到来beginprocess(clk,rst_n)beginif (rst_n='0')thenrx_int0<='0';rx_int1<='0';rx_int2<='0';elseif (rising_edge(clk)) thenrx_int0<=rx_int;rx_int1<=rx_int0;rx_int2<=rx_int1;end if;end if;neg_rx_int <=not(rx_int1)and (rx_int2);end process;process(clk,rst_n)beginif (rst_n='0')thenbps_start_r<='0';tx_data<="00000000";elseif (rising_edge(clk)) thenif(neg_rx_int='1') then --接收到串口数据线rs232_rx 的下降沿标志信号bps_start_r<='1'; --启动串口准备数据接收tx_data<=rx_data; --接收数据中断信号使能else if((num= 15) and (clk_bps='1')) then --接收完有用数据信息bps_start_r<='0'; --数据接收完毕,释放波特率启动信号end if;end if;end if;end if;bps_start<=bps_start_r;end process;process(clk,rst_n)beginif (rst_n='0')thenrs232_tx<='1';num<=0;elseif (rising_edge(clk)) thenif(clk_bps='1')thennum<=num+1;case num iswhen 1=>rs232_tx<='0';when 2=>rs232_tx<=tx_data(0);--发送第1bitwhen 3=>rs232_tx<=tx_data(1);--发送第2bitwhen 4=>rs232_tx<=tx_data(2);--发送第3bitwhen 5=>rs232_tx<=tx_data(3);--发送第4bitwhen 6=>rs232_tx<=tx_data(4);--发送第5bitwhen 7=>rs232_tx<=tx_data(5);--发送第6bitwhen 8=>rs232_tx<=tx_data(6);--发送第7bitwhen 9=>rs232_tx<=tx_data(7);--发送第8bitwhen 10=>rs232_tx<='1';when 11=>num<=15;when others=>null;end case;if(num=15) thennum<=0;end if;end if;end if;end if;end process;end behav;四、实验步骤1、建立新工程UART,选择芯片,型号为cyclone ii EP2C35F484C8。