单片机实用技术讲座(6)第四讲 I/O口的特点及操作

- 格式:pdf

- 大小:164.54 KB

- 文档页数:3

第四章 I/O接口及应用4.1 并行接口概述当单片机用来控制一个设备时,首先要知道设备的状态,其次是要能控制设备运行。

例如用单片机控制自动门。

首先单片机要检测(输入)自动门的开启或关闭命令,当收到开启或关闭命令时,发出(输出)开启或关闭控制指令,在开启或关闭自动门的过程中,要检测门是否开启或关闭到位(输入),到位后要发出停止信号(输出)。

所以单片机必定要有输入与输出引脚。

几乎所有单片机都设计有并行输入、输出接口。

并行输入、输出接口一般为8位。

通过一条输入指令可以一次读取8个引脚的状态,组成一个字节的数据,称为并行输入;通过一条输出指令可以将一个字节的数据送到8个引脚上,称为并行输出。

并行输入接口一般用来采集外部数据;并行输出接口用来输出控制信息。

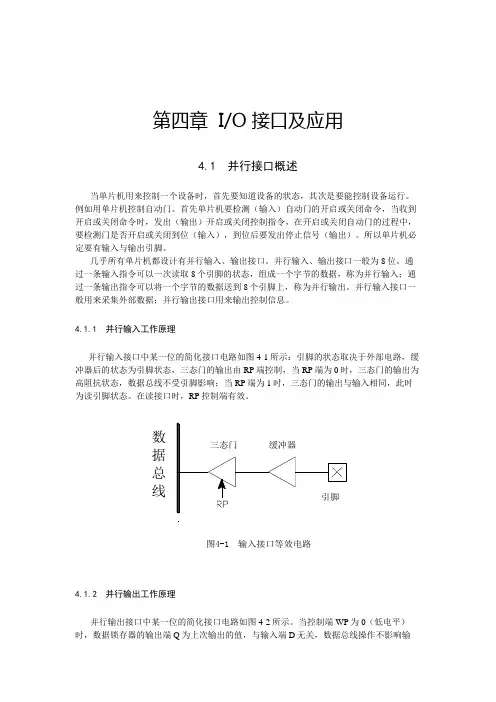

4.1.1 并行输入工作原理并行输入接口中某一位的简化接口电路如图4-1所示:引脚的状态取决于外部电路,缓ATmega16有四个8位的并行输入/输出接口,分别为PA、PB、PC和PD,对应的引脚是PA0~PA7 、PB0~PB7、PC0~PC7和PD0~PD7。

每一个引脚的简化接口电路如图4-3所示:由输入电路、输出电路及方向选择控制电路组成。

输出锁存器、三态驱动器、三态门1、上拉管组成输出电路(等效为图4-2所示的输出电路);缓冲器、三态门2组成输入电路(等效为图4-1所示的输入电路);方向锁存器、三态门3、与非门组成方向控制电路。

当方向锁存器Q端为低电平时,三态驱动器控制为高阻抗状态,输出无效,引脚状态由外部电路及上拉管控制。

输出锁存器Q端为0时,上拉管截止;输出锁存器Q端为1时,上拉管作上拉电阻用。

可通过RP端控制读取引脚信号。

当方向锁存器Q端为高电平时,三态驱动器控制为导通状态,输出引脚状态与输出锁存器的Q端状态相同,电路等效为图4-2所示的输出电路,工作原理同并行输出。

C语言编程时,在头文件<mega16.h>中定义了一些与I/O接口有关的特定变量,每一个特定变量对应单片机内部的一个特殊功能寄存器,用大写字母书写。

80C51的I/O端口结构及应用特性一,I/O端口的结构1,锁存器加引脚的典型结构80C51的I/O端口都有内部总线实现操作控制。

P0-P3四个I/O 口都可以做普通I/O口,因此,要求具有输出锁存功能。

内部总线有事分时操作,因此每个I/O端口都有相应的锁存器。

然而I/O端口又是外部的输入/输出通道,必须有相应的引脚,故形成了I/O端口的锁存器加引脚的典型结构。

2,I/O口的复用功能(1)I/O口的总线复用。

80C51在使用并行总线扩展时,P0口可作为数据总线口和低8位地址总线口,这是,P0为三态双向口。

P0口输出总线的地址数据信号,P2口输出高8位地址信号。

(2)I/O口的功能复用。

I/O口的P3为功能复用的I/O端口。

端口有复用输出的控制端;引脚也有复用输入的控制端。

3,准双向结构P0,P1,P2,P3口做普通I/O口使用时,都是准双向口结构。

准双向口的典型结构见P1口位结构图。

准双向口的输入操作和输出操作本质不同,输入操作时读引脚状态;输出操作时对口锁存器的写入操作。

有口锁存器和引脚电路可知:当有内部总线对只1或只0时,锁存器的0、1状态立即反应到引脚上。

但是输入操作(读引脚)时,如果口锁存器的状态为0,引脚被嵌位在0状态,导致无法读出引脚的高电平输入。

二,I/O端口的应用特性1,引脚的自动识别。

无论P0,P2口的总线复用,还是P3口的功能复用,内部资源会自动选择,不需要通过指令的状态选择。

2,口锁存器的读、该、写操作。

许多涉及到I/O端口的操作,只是涉及口锁存器的读出、修改、写入的操作。

这些指令都是一些逻辑运算指令、置位/清除指令、条件转移指令以及将I/O口作为目的地址的操作指令。

3,读引脚的操作指令。

如果某个I/O口被指定为源操作数,则为读引脚的操作指令。

例如,执行MOV A,P1时,P1口的引脚状态传送到累加器中,执行MOV P1,A是,指令则将累加器的内容传送到P1口锁存器中。

4,准双向口的使用。

IO口详解AVR单片机IO结构全攻略为搞清IO结构,首先看看上拉和下拉电阻的作用。

一、上拉电阻上拉就是将不确定的信号通过一个电阻钳位在高电平!电阻同时起限流作用!下拉同理!上拉电阻是用来解决总线驱动能力不足时提供电流的。

一般说法是拉电流,下拉电阻是用来吸收电流。

1、在用TTL电路驱动CMOS电路时,若TTL的高电平低于CMOS要求的高电平的门限值(1,TTL电平:输出高电平>2.4V,输出低电平<0.4V。

在室温下,一般输出高电平是3.5V,输出低电平是0.2V。

最小输入高电平和低电平:输入高电平>=2.0V,输入低电平<=0.8V,噪声容限是0.4V。

2,CMOS电平:1逻辑电平电压接近于电源电压,0逻辑电平接近于0V。

而且具有很宽的噪声容限。

),此时需用上拉电阻来提升输出高电平的电压值。

2、OC门必须外加上拉电阻,才能使用。

(OC门:三极管的叫集电极开路,场效应管的叫漏极开路,简称开漏输出。

具备"线与"能力,有0得0。

)3、为加大输出管脚的驱动能力,单片机的引脚常接入上拉电阻,(AVR单片机可配置是否接上拉,51单片机P1 P2 P3均带上拉,P0口不带,所以用P0口做按键,液晶等应用时要自己加上上拉电阻,否则无法使用切记)4、CMOS芯片上为防止静电破坏,不用的管脚不能悬空,需要接上拉电阻降低输入阻抗,提供泄荷通路。

5、提高总线的搞电磁干扰能力,悬空就容易就电磁干扰。

二、上拉电阻阻值的选择1、为节约功耗或使灌电流足够大,阻值要大,电流小。

2、为确保足够的驱动电流,阻值要小,电流大。

3、对于高速电路,过大的上拉电阻可能导致边沿变得平缓。

基于以上三点,一般选取上拉阻值为1K-10K。

三、上拉阻值的计算OC门输出高电平时是一个高阻态,其上拉电流要由上拉电阻来提供,设输入端每端口不大于100uA,设输出口驱动电流约500uA,标准工作电压是5V,输入口的高低电平门限为0.8V(低于此值为低电平);2V(高电平门限值)。

单片机IO口介绍单片机(Microcontroller)是一种集成了微处理器、存储器和各种I/O接口的芯片。

其中,I/O口是单片机与外部设备进行数据交换的通道,它是单片机最重要的功能之一、本文将详细介绍单片机的I/O口。

一、I/O口的基本概念在单片机中,I/O口是单片机与外部设备进行数据交换的接口。

它通过I/O线与外部设备相连接,可以实现数据的输入和输出。

单片机的I/O口可以分为通用I/O口和特殊功能I/O口两种类型。

通用I/O口是单片机常用的一种I/O口,它可以通过软件编程实现不同的功能,包括数字输入、数字输出和模拟输入输出等。

通用I/O口可以根据实际需求进行设置,提供灵活的数据交换方式。

特殊功能I/O口是单片机固定的一些特殊功能接口,通常用于特定的应用,如定时器、比较器、串行通信等。

特殊功能I/O口具有特殊的功能和特殊的操作要求,需要根据具体的应用进行设置。

二、通用I/O口的工作原理通用I/O口是单片机最常用的一种I/O口,它可以通过软件编程实现不同的功能。

通用I/O口的工作原理如下:1.输入模式:通用I/O口可以设置为输入模式,接收来自外部设备的输入信号。

在输入模式下,通用I/O口通常通过上拉或下拉电阻来实现输入的稳定性,并通过软件读取输入信号的状态。

2.输出模式:通用I/O口可以设置为输出模式,向外部设备输出信号。

在输出模式下,通用I/O口可以输出高电平或低电平信号,并通过软件控制输出的状态。

通用I/O口的状态可以通过软件进行设置和读取,可以实现灵活的数据交换。

通用I/O口的应用非常广泛,可以用于控制开关、驱动显示、读取按键等。

三、特殊功能I/O口的工作原理特殊功能I/O口是单片机固定的一些特殊功能接口,通常用于特定的应用。

特殊功能I/O口具有特殊的功能和特殊的操作要求,需要根据具体的应用进行设置。

下面介绍一些常见的特殊功能I/O口。

1.定时器/计数器:定时器/计数器是特殊功能I/O口中最常用的一个。

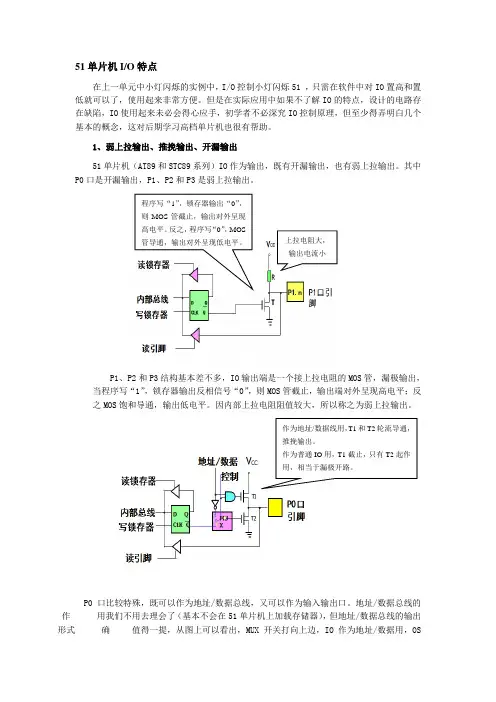

51单⽚机IO特点51单⽚机I/O 特点在上⼀单元中⼩灯闪烁的实例中,I/O 控制⼩灯闪烁51 ,只需在软件中对IO 置⾼和置低就可以了,使⽤起来⾮常⽅便。

但是在实际应⽤中如果不了解IO 的特点,设计的电路存在缺陷,IO 使⽤起来未必会得⼼应⼿,初学者不必深究IO 控制原理,但⾄少得弄明⽩⼏个基本的概念,这对后期学习⾼档单⽚机也很有帮助。

1、弱上拉输出、推挽输出、开漏输出51单⽚机(AT89和STC89系列)IO 作为输出,既有开漏输出,也有弱上拉输出。

其中P0⼝是开漏输出,P1、P2和P3是弱上拉输出。

P1、P2和P3结构基本差不多,IO 输出端是⼀个接上拉电阻的MOS 管,漏极输出,当程序写“1”,锁存器输出反相信号“0”,则MOS 管截⽌,输出端对外呈现⾼电平;反之MOS 饱和导通,输出低电平。

因内部上拉电阻阻值较⼤,所以称之为弱上拉输出。

P0⼝⽐较特殊,既可以作为地址/数据总线,⼜可以作为输⼊输出⼝。

地址/数据总线的作⽤我们不⽤去理会了(基本不会在51单⽚机上加载存储器),但地址/数据总线的输出形式确值得⼀提,从图上可以看出,MUX 开关打向上边,IO 作为地址/数据⽤,OS上拉电阻,阻值很⼤上拉电阻⼤,输出电流⼩程序写“1”,锁存器输出“0”,则MOS 管截⽌,输出对外呈现⾼电平。

反之,程序写“0”,MOS 管导通,输出对外呈现低电平。

作为地址/数据线⽤,T1和T2轮流导通,推挽输出。

作为普通IO ⽤,T1截⽌,只有T2起作⽤,相当于漏极开路。

管T1和T2轮流导通,这种形式成为推挽输出。

尽管我们不⽤地址数据总线,但这种双管轮流导通的形式是AVR/PIC 等单⽚机IO 输出的主要形式,输出和输⼊具有同样⼤的电流。

P0⼝⽤作普通IO 时,MUX 开关打向锁存器端,锁存器输出只与MOS 管T2连接,MOS 管T1不起作⽤,MOS 管T2漏极开路,称之为开漏输出。

所以P0⼝作为普通IO 使⽤,需在外部接上拉电阻。