VerilogHDL数字系统设计及实践第章Verilog行为描述

- 格式:ppt

- 大小:195.00 KB

- 文档页数:20

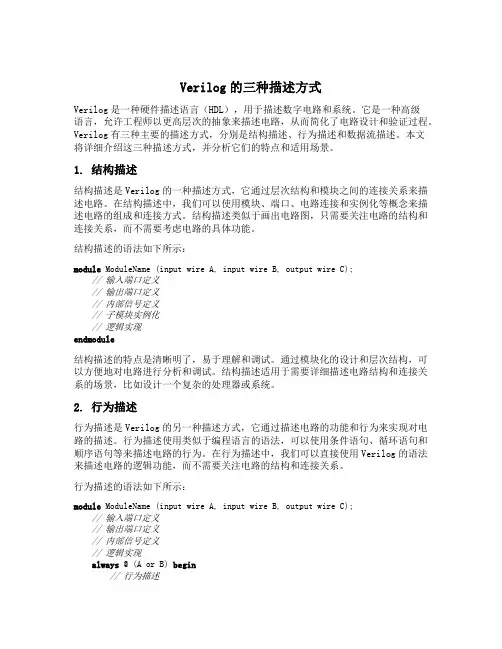

Verilog的三种描述方式Verilog是一种硬件描述语言(HDL),用于描述数字电路和系统。

它是一种高级语言,允许工程师以更高层次的抽象来描述电路,从而简化了电路设计和验证过程。

Verilog有三种主要的描述方式,分别是结构描述、行为描述和数据流描述。

本文将详细介绍这三种描述方式,并分析它们的特点和适用场景。

1. 结构描述结构描述是Verilog的一种描述方式,它通过层次结构和模块之间的连接关系来描述电路。

在结构描述中,我们可以使用模块、端口、电路连接和实例化等概念来描述电路的组成和连接方式。

结构描述类似于画出电路图,只需要关注电路的结构和连接关系,而不需要考虑电路的具体功能。

结构描述的语法如下所示:module ModuleName (input wire A, input wire B, output wire C);// 输入端口定义// 输出端口定义// 内部信号定义// 子模块实例化// 逻辑实现endmodule结构描述的特点是清晰明了,易于理解和调试。

通过模块化的设计和层次结构,可以方便地对电路进行分析和调试。

结构描述适用于需要详细描述电路结构和连接关系的场景,比如设计一个复杂的处理器或系统。

2. 行为描述行为描述是Verilog的另一种描述方式,它通过描述电路的功能和行为来实现对电路的描述。

行为描述使用类似于编程语言的语法,可以使用条件语句、循环语句和顺序语句等来描述电路的行为。

在行为描述中,我们可以直接使用Verilog的语法来描述电路的逻辑功能,而不需要关注电路的结构和连接关系。

行为描述的语法如下所示:module ModuleName (input wire A, input wire B, output wire C);// 输入端口定义// 输出端口定义// 内部信号定义// 逻辑实现always @ (A or B) begin// 行为描述endendmodule行为描述的特点是灵活性高,可以方便地实现复杂的逻辑功能。

《数字系统设计与Verilog HDL》实验报告(二)班级:自动1003班姓名:**学号:********实验二、四位并串转换电路一、实验目的1、了解及掌握时序电路的基本结构常用数字电路;2、通过ModelSim软件编写时序电路的程序进行仿真和调试。

二、实验内容1、熟悉时序电路中时钟的同步与异步用法;2、编写一个四位并串转换设计程序以及测试该模块的测试程序,要求如下:(1)输入一个四位二进制数pin;(2)每个时钟周期按从左往右的顺序输出一位pin的二进制位的数。

三、实验步骤及源程序新建工程及文件,分别添加设计程序及测试程序,进行编译及纠错,编译通过后运行程序仿真进行调试得出结果。

设计模块:module para_to_serial4(pin,clk,reset,sout);input [3:0] pin;input clk,reset;output sout;reg sout;reg [3:0] data;always @(posedge clk or negedge reset)beginif(~reset)beginsout<=1'b0;data<=pin;endelsebegindata<={data[2:0],data[3]};sout<=data[3];endendendmodule测试模块:`timescale 1ns/1nsmodule test_para_to_ser;wire sout;reg [3:0] pin;reg clk,reset;para_to_serial4 test1(pin,clk,reset,sout);initialbeginclk=1'b0;reset=1'b0;#5 reset=1'b1;#300 $stop;endinitialpin=4'b1001;always#5 clk=~clk;endmodule四、实验结果五、实验心得体会这次试验相对于上次有了一定的难度,由于这门课程刚开始学习,我还不能很好地从宏观把握这门课程,对这门课程的认识和理解还不够深刻,所以做实验时遇到了一些困难,虽然找了一些参考资料,有一定的帮助,但最后还是有点纠结,最终在和同学的交流中才比较深刻的对实验有了了解。

verilog-hdl答案第1章简介1.Verilog HDL是在哪一年首次被IEEE标准化的?Verilog HDL是在1995年首次被IEEE标准化的。

2.Verilog HDL支持哪三种基本描述方式Verilog HDL可采用三种不同方式或混合方式对设计建模。

这些方式包括:行为描述方式—使用过程化结构建模;数据流方式—使用连续赋值语句方式建模;结构化方式—使用门和模块实例语句描述建模3.可以使用Verilog HDL描述一个设计的时序吗?Verilog HDL可以清晰的建立时序模型,故可以使用Verilog HDL描述一个设计的时序。

4.语言中的什么特性能够用于描述参数化设计?在行为级描述中, Verilog HDL不仅能够在RT L级上进行设计描述,而且能够在体系结构级描述及其算法级行为上进行设计描述,而且能够使用门和模块实例化语句在结构级进行结构描述,这种特性可用于描述参数化设计。

5.能够使用Verilog HDL编写测试验证程序吗?能,可以编写testbench来对编写的程序进行验证。

6.Verilog HDL是由哪个公司最先开发的?Verilog HDL是由Gateway Design Automation公司最先开发的7.Verilog HDL中的两类主要数据类型是什么?线网数据类型和寄存器数据类型。

线网类型表示构件间的物理连线,而寄存器类型表示抽象的数据存储元件。

8.UDP代表什么?UDP代表用户定义原语9.写出两个开关级基本门的名称。

pmos nmos10.写出两个基本逻辑门的名称。

and or第2章 HDL指南1. 在数据流描述方式中使用什么语句描述一个设计?设计的数据流行为使用连续赋值语句进行描述2. 使用` t i m e s c a l e 编译器指令的目的是什么?举出一个实例。

使用编译指令将时间单位与物理时间相关联。

例如` timescale 1ns /100ps 此语句说明时延时间单位为1ns并且时间精度为100ps (时间精度是指所有的时延必须被限定在0.1ns内)3. 在过程赋值语句中可以定义哪两种时延?请举例详细说明。

第4节Verilog HDL语言的描述语句Verilog HDL 描述语句2.4.1 结构描述形式通过实例进行描述的方法,将Verilog HDL预先定义的基本单元实例嵌入到代码中,监控实例的输入。

Verilog HDL中定义了26个有关门级的关键字,比较常用的有8个。

在实际工程中,简单的逻辑电路由逻辑门和开关组成,通过门元语可以直观地描述其结构。

基本的门类型关键字如下所述:•and•nand•nor•or•xor•xnor•buf•notVerilog HDL支持的基本逻辑部件是由该基本逻辑器件的原语提供的。

其调用格式为:门类型<实例名> (输出,输入1,输入2,……,输入N)例如,nand na01(na_out, a, b, c );表示一个名字为na01的与非门,输出为na_out,输入为a, b, c。

例2-5 一个简单的全加器例子:module ADD(A, B, Cin, Sum, Cout);input A, B, Cin;output Sum, Cout;// 声明变量wire S1, T1, T2, T3;xor X1 (S1, A, B),X2 (Sum, S1, Cin);and A1 (T3, A, B),A2 (T2, B, Cin),A3 (T1, A, Cin);or O1 (Cout, T1, T2, T3);endmodule在这一实例中,模块包含门的实例语句,也就是包含内置门xor、and和or的实例语句。

门实例由线网型变量S1、T1、T2和T3互连。

由于未指定顺序,门实例语句可以以任何顺序出现。

门级描述本质上也是一种结构网表。

在实际中的使用方式为:先使用门逻辑构成常用的触发器、选择器、加法器等模块,再利用已经设计的模块构成更高一层的模块,依次重复几次,便可以构成一些结构复杂的电路。

其缺点是:不易管理,难度较大且需要一定的资源积累。

2.4.2 数据流描述形式数据流型描述一般都采用assign连续赋值语句来实现,主要用于实现组合功能。