ncverilog入门教程1

- 格式:pdf

- 大小:4.55 MB

- 文档页数:20

verilog教程Verilog是一种硬件描述语言(HDL),用于描述数字系统的行为和结构。

它是一种流行的HDL,广泛用于硬件设计和验证领域。

本教程将介绍Verilog的基本概念和语法,以帮助初学者入门。

一、Verilog的基本概念1.1 什么是VerilogVerilog是一种描述数字系统的语言,它可以用来描述硬件电路、验证设计的正确性以及进行电路仿真。

1.2 Verilog的应用领域Verilog广泛应用于硬件设计和验证领域,包括用于开发ASIC(应用特定集成电路)、FPGA(现场可编程门阵列)以及其他数字系统的设计。

1.3 Verilog的版本Verilog有多个版本,包括Verilog-1995、Verilog-2001以及最新的Verilog-2005、这些版本之间有一些语法和功能上的差异。

二、Verilog的语法结构2.1模块和端口在Verilog中,所有的电路描述都是由模块(module)组成的。

模块是电路的基本组成单元,可以看作是一个黑盒子,它接受一些输入,产生一些输出。

2.2信号声明在Verilog中,我们需要声明所有的输入和输出信号。

可以使用`input`和`output`关键字来声明这些信号。

2.3电路实现Verilog允许使用多种语句和结构来描述电路的行为和结构。

这些语句包括顺序语句、条件语句、循环语句以及层次结构。

2.4实例化模块在一个模块中,我们可以实例化其他的模块。

这样可以将一个大的电路拆分成多个小的模块,方便编写和测试。

三、Verilog的仿真和验证3.1静态验证Verilog语言本身提供了很多语法和语义层面的验证功能,对于语法和类型错误会有相应的提示。

3.2激励设计在进行电路验证时,我们需要为输入信号提供激励。

Verilog提供了一种称为`testbench`的特殊模块,用于生成输入信号并将其应用到待验证的电路中。

3.3波形仿真在Verilog中,我们可以使用仿真器来模拟电路的行为,并生成波形图来验证电路是否按预期工作。

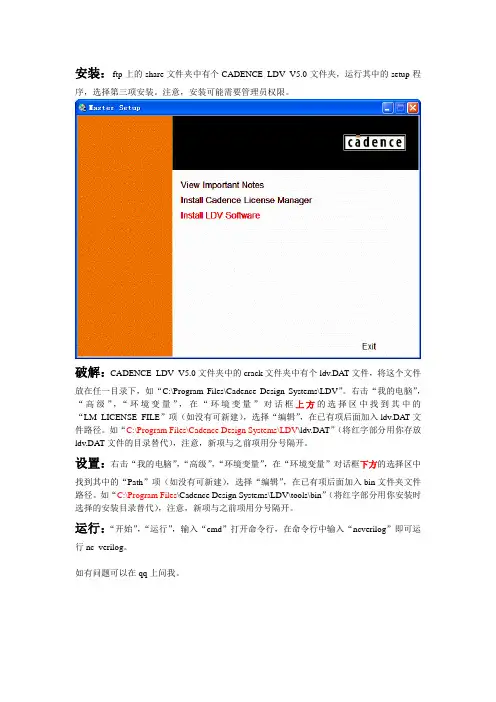

安装:ftp上的share文件夹中有个CADENCE_LDV_V5.0文件夹,运行其中的setup程

序,选择第三项安装。

注意,安装可能需要管理员权限。

破解:CADENCE_LDV_V5.0文件夹中的crack文件夹中有个ldv.DAT文件,将这个文件

放在任一目录下,如“C:\Program Files\Cadence Design Systems\LDV”。

右击“我的电脑”,“高级”,“环境变量”,在“环境变量”对话框上方的选择区中找到其中的“LM_LICENSE_FILE”项(如没有可新建),选择“编辑”,在已有项后面加入ldv.DA T文件路径。

如“C:\Program Files\Cadence Design Systems\LDV\ldv.DAT”(将红字部分用你存放ldv.DAT文件的目录替代),注意,新项与之前项用分号隔开。

设置:右击“我的电脑”,“高级”,“环境变量”,在“环境变量”对话框下方的选择区中

找到其中的“Path”项(如没有可新建),选择“编辑”,在已有项后面加入bin文件夹文件路径。

如“C:\Program Files\Cadence Design Systems\LDV\tools\bin”(将红字部分用你安装时选择的安装目录替代),注意,新项与之前项用分号隔开。

运行:“开始”,“运行”,输入“cmd”打开命令行,在命令行中输入“ncverilog”即可运行nc_verilog。

如有问题可以在qq上问我。

Ncverilog命令使用详解NCVerilog是一种用于模拟、调试和分析Verilog和SystemVerilog 代码的命令行工具。

以下是对NCVerilog命令使用的详细解释。

1. `ncverilog`命令:启动NCVerilog编译器。

语法如下:```ncverilog [options] <file_list>```- `options`:附加的编译选项,例如`-sv`表示编译SystemVerilog 代码。

- `file_list`:包含要编译的源文件的列表。

2. `+access+r`选项:允许模拟工具读取源代码中的注释。

这对于调试和分析时非常有用。

3. `+define+<macro>`选项:定义一个宏。

这可以用于在模拟期间改变代码的行为。

例如:```+define+DEBUG```4. `+incdir+<dir>`选项:指定包含库文件的目录。

这对于使用外部库或模块时非常有用。

5. `+define+<macro>={value}`选项:为宏指定一个值。

例如:```+define+WIDTH=8```6. `+libext+<ext>`选项:指定库文件的扩展名。

可以用于指定Verilog或SystemVerilog库文件的不同扩展名。

``````8. `+vcs`选项:指定使用VCS编译器的系统Verilog代码。

这对于一些特定的系统Verilog代码可能是必需的。

9. `-y <dir>`选项:指定一个目录,其中包含其他用户定义的Verilog或SystemVerilog库文件。

10. `-v <file>`选项:指定一个要编译的单独的库文件。

11. `-f <file>`选项:指定一个包含文件列表的文件。

这可以用于指定要编译的多个源文件。

12. `-fsmdebug`选项:在编译期间为FSM(有限状态机)创建调试信息。

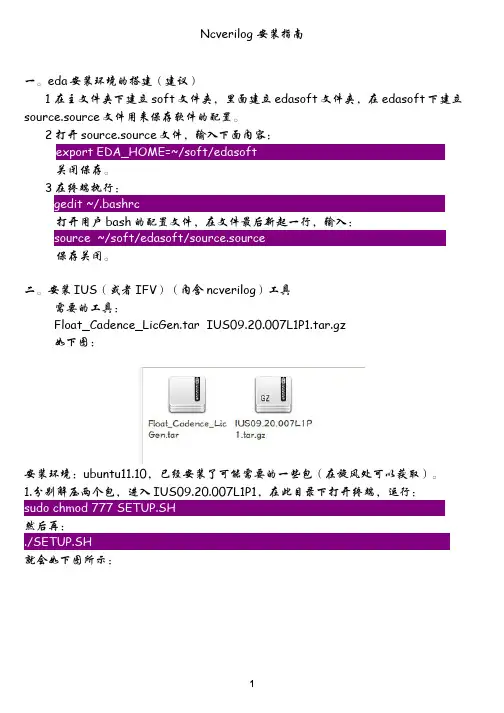

Ncverilog 安装指南一。

eda安装环境的搭建(建议)1 在主文件夹下建立soft文件夹,里面建立edasoft文件夹,在edasoft下建立source.source文件用来保存软件的配置。

2打开source.source文件,输入下面内容:关闭保存。

3在终端执行:打开用户bash的配置文件,在文件最后新起一行,输入:保存关闭。

二。

安装IUS(或者IFV)(内含ncverilog)工具需要的工具:Float_Cadence_LicGen.tar IUS09.20.007L1P1.tar.gz如下图:安装环境:ubuntu11.10,已经安装了可能需要的一些包(在旋风处可以获取)。

1.分别解压两个包,进入IUS09.20.007L1P1,在此目录下打开终端,运行:然后再:就会如下图所示:点击enter键直到出现:在后面输入你要安装的目录,如:~/soft/edasoft/IUS回车继续:下来惠询问安装路径:然后会跳出图形界面安装InstallScape:点击next直到下图,选上所有安装项(除去含64bit字样的,那个是64bit的):下一步安装:安装完会提示是否配置,选yes:选上所有进行配置。

在询问是否配置lisence时选否:之后完毕,close。

2、现在配置lisence。

进入刚解压出来的Float_Cadence_LicGen文件夹:修改all.dat的内容,只修改第二行,注意和你的IUS安装目录对应:回到Float_Cadence_LicGen文件夹,在该文件夹下打开终端,输入如下指令:如下:执行后会产生key.cadence文件。

重命名为cadencelisence.dat,放到你的安装目录下:编辑source.source文件,加入如下内容:注意上面有两个license,使用了冒号进行分隔。

如果你只有一个lisence,写一个就好。

创建缓存空间,在终端执行:保存关闭所有终端。

下载ius9.2解压后一共六个文件打开超级终端,进入到此六个文件目录下第一步:./SETUP.SH第二步:设定安装目录(即安装到哪里)第三步:输入y第四步:设定安装源文件的目录(即,一开始解压的六个文件的那个目录)第五步:【与第三步一样】输入y第六步:【与第四步一样】设定安装源文件的目录(即,一开始解压的六个文件的那个目录)第七步:第六步后会弹出窗口,路径就是刚才第四步与第六步设定的路径,不要改,点NEXT>第八步:点NEXT>第九步:路径就是刚才第二步设定的路径,不要改,点NEXT>第十步:全部勾选,点NEXT>第十一步:点install第十二步:等待(直到100%安完),点close第十三步:弹出窗口,点NO第十四步:关掉下面界面,就会回到终端第十五步,进入安装目录,即第二步的目录,在安装目录下给tools.lnx86建一个快捷方式叫tools(使用命令ln -s tools.lnx86 tools)第十六步:复制sfk和patch_cadence(这两个文件是破解文件,到下面网址能下载到,同时也能下载到IUS软件,感谢该网友的无私奉献,/viewthread.php?tid=304428&from=favorites)到IUS安装目录下,执行./patch_cadence第十七步:在windows上面制作license首先打开LicGen.exe软件,点击open,打开Cadence.lpd然后按下图填写,注意Custom后面的那一串是机器的MAC地址,如果是用虚拟机的话,在终端中运行/sbin/ifconfig -a Hwaddr 后面就是虚拟机的MAC!,点击Generate,然后Save成license.dat。

之后用记事本打开license.dat,第一行的SERVER 后面要改成虚拟机的主机名,虚拟机主机名一般默认是localhost.localdomain 。

verilog数字系统设计教程Verilog数字系统设计教程作者:XXX引言:数字系统设计是现代电子工程中非常重要的一部分。

Verilog作为一种硬件描述语言,提供了一种方便且专业的方法来设计和描述数字系统。

本教程旨在为初学者提供关于Verilog数字系统设计的详细介绍和指导。

1. Verilog简介Verilog作为一种硬件描述语言,用于描述数字系统的功能、结构和时序行为。

它类似于C语言,但更专注于硬件级别。

Verilog可以用于设计各种数字系统,例如处理器、嵌入式系统、通信设备等。

2. Verilog基本语法2.1 模块定义Verilog的基本单位是模块。

模块是数字系统的基本组成部分,可以看作是一个独立的功能单元。

模块可以包含输入、输出、内部信号以及其它子模块等。

2.2 信号声明在Verilog中,可以声明各种类型的信号,包括输入信号、输出信号和内部信号等。

信号声明定义了信号的类型、宽度和方向。

3. Verilog建模3.1 组合逻辑建模组合逻辑是数字系统中最基本的部分。

Verilog提供了各种组合逻辑建模的方法,包括逻辑运算、选择结构和多路复用器等。

3.2 时序逻辑建模时序逻辑是数字系统中需要考虑时序关系的部分。

Verilog提供了时序逻辑建模的方法,包括触发器、计数器和时序控制等。

4. Verilog仿真4.1 仿真器介绍仿真器是用于验证数字系统设计的工具。

Verilog可以与各种仿真器配合使用,用于验证设计的正确性和性能。

4.2 仿真流程仿真流程包括编写测试平台和测试用例、编译和仿真等步骤。

本节将介绍基本的仿真流程和相关技巧。

5. Verilog综合5.1 综合概述综合是将Verilog代码转换为逻辑门级描述的过程。

综合器通过将Verilog代码映射到实际的硬件库中,生成能够实现指定功能的逻辑电路。

5.2 综合流程综合流程包括综合前的优化和综合本身两个阶段。

本节将介绍综合的基本流程和主要考虑因素。

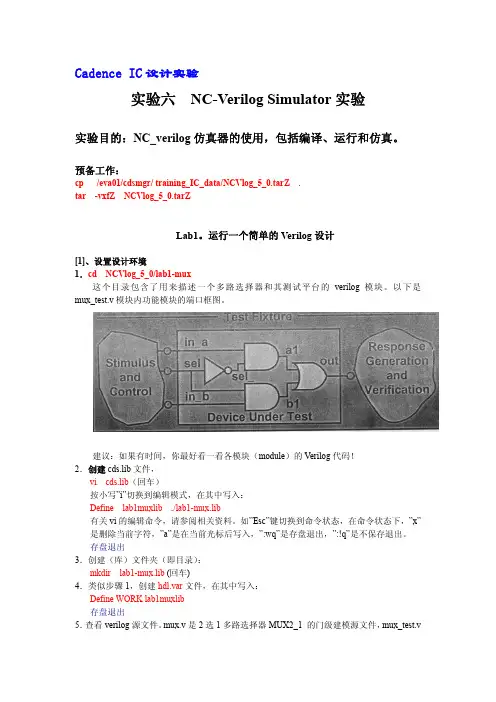

Cadence IC设计实验实验六 NC-Verilog Simulator实验实验目的:NC_verilog仿真器的使用,包括编译、运行和仿真。

预备工作:cp /eva01/cdsmgr/ training_IC_data/NCVlog_5_0.tarZ .tar -vxfZ NCVlog_5_0.tarZLab1。

运行一个简单的Verilog设计[1]、设置设计环境1.cd NCVlog_5_0/lab1-mux这个目录包含了用来描述一个多路选择器和其测试平台的verilog 模块。

以下是mux_test.v模块内功能模块的端口框图。

建议:如果有时间,你最好看一看各模块(module)的Verilog代码!2.创建cds.lib文件,vi cds.lib(回车)按小写”i”切换到编辑模式,在其中写入:Define lab1muxlib ./lab1-mux.lib有关vi的编辑命令,请参阅相关资料。

如”Esc”键切换到命令状态,在命令状态下,”x”是删除当前字符,”a”是在当前光标后写入,”:wq”是存盘退出,”:!q”是不保存退出。

存盘退出3.创建(库)文件夹(即目录):mkdir lab1-mux.lib (回车)4.类似步骤1,创建hdl.var文件,在其中写入:Define WORK lab1muxlib存盘退出5.查看verilog源文件。

mux.v是2选1多路选择器MUX2_1 的门级建模源文件,mux_test.v是mux.v的测试台,包含了输入激励信号和监控程序运行的任务语句。

[2]、编译源文件(ncvlog命令):当前目录应为。

/你的学号/NCVlog_5_0/lab1-mux。

1.ncvlog mux.v –messages ,这条指令是编译mux.v。

2.vi hdl.var打开hdl.var文件,在其中添加:Define NCVLOGOPTS –messages 存盘退出注:用NCVLOGOPTS变量定义常用的ncvlog命令行操作,从而避免每次都敲入同样的命令行。

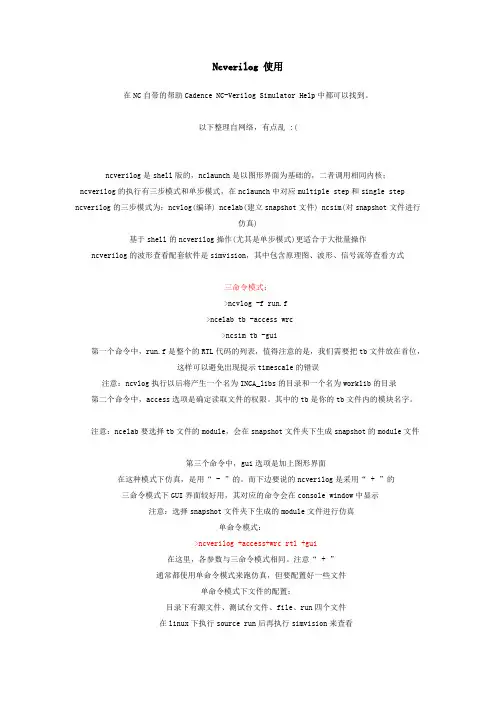

Ncverilog 使用在NC自带的帮助Cadence NC-Verilog Simulator Help中都可以找到。

以下整理自网络,有点乱 :(ncverilog是shell版的,nclaunch是以图形界面为基础的,二者调用相同内核;ncverilog的执行有三步模式和单步模式,在nclaunch中对应multiple step和single step ncverilog的三步模式为:ncvlog(编译) ncelab(建立snapshot文件) ncsim(对snapshot文件进行仿真)基于shell的ncverilog操作(尤其是单步模式)更适合于大批量操作ncverilog的波形查看配套软件是simvision,其中包含原理图、波形、信号流等查看方式三命令模式:>ncvlog -f run.f>ncelab tb -access wrc>ncsim tb -gui第一个命令中,run.f是整个的RTL代码的列表,值得注意的是,我们需要把tb文件放在首位,这样可以避免出现提示timescale的错误注意:ncvlog执行以后将产生一个名为INCA_libs的目录和一个名为worklib的目录第二个命令中,access选项是确定读取文件的权限。

其中的tb是你的tb文件内的模块名字。

注意:ncelab要选择tb文件的module,会在snapshot文件夹下生成snapshot的module文件第三个命令中,gui选项是加上图形界面在这种模式下仿真,是用“ - ”的。

而下边要说的ncverilog是采用“ +”的三命令模式下GUI界面较好用,其对应的命令会在console window中显示注意:选择snapshot文件夹下生成的module文件进行仿真单命令模式:>ncverilog +access+wrc rtl +gui在这里,各参数与三命令模式相同。

注意“ + ”通常都使用单命令模式来跑仿真,但要配置好一些文件单命令模式下文件的配置:目录下有源文件、测试台文件、file、run四个文件在linux下执行source run后再执行simvision来查看run文件内容: ncverilog +access+rw -f filefile文件内容: cnt_tb.v(注意把tb文件放在前)cnt.vtb文件中应该包含:initialbegin$shm_open("wave.shm"); //打开波形保存文件wave.shm$shm_probe(cnt_tb,"AS"); //设置探针endA -- signals of the specific scope 为当前层信号设置探针S -- Ports of the specified scope and below, excluding library cellsC -- Ports of the specified scope and below, including library cellsAS -- Signals of the specified scope and below, excluding library cells 为当前层以以下层信号都设置探针,这是最常用的设置方法AC -- Signals of the specified scope and below, including library cells还有一个 M ,表示当前scope的memories, 可以跟上面的结合使用, "AM" "AMS" "AMC"什么都不加表示当前scope的ports;$shm_close //关闭数据库查看结果时可以在source schemic wave register四个窗口同时查看保存波形信号的方法:1.SHM数据库可以记录在设计仿真过程中信号的变化. 它只在probes有效的时间内记录你setprobe on的信号的变化.2.VCD数据库也可以记录在设计仿真过程中信号的变化. 它只记录你选择的信号的变化.$dumpfile("filename"); //打开数据库$dumpvars; //depth = all scope = all$dumpvars(0); //depth = all scope = current$dumpvars(1, top.u1); //depth = 1 scope = top.u1$dumpoff //暂停记录数据改变,信号变化不写入库文件中$dumpon //重新恢复记录3.Debussy fsdb数据库也可以记录信号的变化,它的优势是可以跟debussy结合,方便调试.如果要在ncverilog仿真时,记录信号, 首先要设置debussy:a. setenv LD_LIBRARY_PATH :$LD_LIBRARY_PATH(path for debpli.so file(/share/PLI/nc_xl//nc_loadpli1))b. while invoking ncverilog use the +ncloadpli1 option. ncverilog -f run.f +debug+ncloadpli1=debpli:deb_PLIPtrfsdb数据库文件的记录方法,是使用$fsdbDumpfile和$fsdbDumpvars系统函数,使用方法参见VCD注意: 在用ncverilog的时候,为了正确地记录波形,要使用参数: "+access+rw", 否则没有读写权限产生FSDB波形文件的若干技巧:/bbs/viewthread.php?tid=2539&;extra=page%3D1下载:/bbs/viewthread.php?tid=3357&;extra=page%3D1ncverilog编译的顺序: ncverilog file1 file2 ....有时候这些文件存在依存关系,如在file2中要用到在file1中定义的变量,这时候就要注意其编译的顺序是从后到前,就先编译file2然后才是file2.,信号的强制赋值force:首先, force语句只能在过程语句中出现,即要在initial 或者 always 中间. 去除force 用release 语句.;initial begin force sig1 = 1'b1; ... ; release sig1; end, force可以对wire赋值,这时整个net都被赋值; 也可以对reg赋值.Verilog和Ncverilog命令使用库文件或库目录ex). ncverilog -f run.f -v lib/lib.v -y lib2 +libext+.v //一般编译文件在run.f中, 库文件在lib.v中,lib2目录中的.v文件系统自动搜索,使用库文件或库目录,只编译需要的模块而不必全部编译Q:我的files里面只有一个help文件夹,里面是一个叫ncprotect文件,没有你所说的hdl.var文件啊A:1、NC-VERILOG在创建工程时会生成两个文件:cds.lib和hdl.var。

Verilog语法简易教程Verilog是硬件描述语言(HDL)之一,主要用于硬件设计和仿真。

它于1984年由一家名为Gateway Design Automation的公司开发,并于1985年推出。

Verilog以其简单易学的语法和强大的功能而闻名于世。

本简易教程将向您介绍Verilog的基本语法和常用结构。

它包括模块化设计,数据类型,运算符,条件语句,循环语句和时序建模等内容。

首先,让我们先来了解Verilog中的模块化设计。

在Verilog中,设计是通过定义和连接模块来完成的。

每个模块由输入输出端口和内部逻辑组成。

以下是一个简单的Verilog模块的例子:```module adder(input [3:0] A, B, output [3:0] sum);assign sum = A + B;endmodule```上述代码定义了一个名为adder的模块,它具有两个输入端口A和B,以及一个输出端口sum。

内部逻辑通过assign语句实现,将输入端口A和B相加,并将结果赋值给输出端口sum。

接下来,让我们了解Verilog中的数据类型和运算符。

Verilog支持多种数据类型,包括位向量(bit vector)、整数(integer)、浮点数(real)等。

其中,位向量是最常用的数据类型。

以下是两个位向量相加的例子:```module adder(input [3:0] A, B, output [3:0] sum);assign sum = A + B;endmodule```在这个例子中,输入端口A和B都是4位的位向量,输出端口sum也是4位的位向量。

通过使用+运算符,我们可以对这两个位向量进行相加操作,并将结果赋值给输出端口sum。

除了基本的数据类型和运算符,Verilog还提供了丰富的条件和循环语句。

条件语句允许您在程序中根据一些条件执行不同的操作。

以下是一个简单的条件语句的例子:```beginif (A == B)equal = 1;elseequal = 0;endendmodule```在这个例子中,我们使用了always块来定义一个连续的行为。

Ncverilog 命令使用详解我们知道,由于NC-Verilog使用了Native Compile Code 的技术来加强电路模拟的效率,因此在进行模拟时必须经过compile(ncvlog 命令)以及elaborate(n celab命令)的步骤。

编译之后,针对每一个HDL设计单元会产生中间表达。

接着elaborate命令会建立整个电路的结构,产生可以用来模拟的资料。

最后使用ncsim命令来进行模拟。

三命令模式命令如下:ncvlog -f run.fncealb tb -access wrcncsim tb -gui第一个命令中,run.f是整个的RTL代码的列表,值得注意的是,我们需要把tb 文件放在首位,这样可以避免出现提示timescale的错误。

第二个命令中,access选项是确定读取文件的权限。

其中的tb是你的tb文件内的模块名字。

第三个命令中,gui选项是加上图形界面值得注意的是,在这种模式下仿真,是用“ - ”的。

而下边要说的ncverilog是采用“ + ”的。

单命令模式ncverilog +access+wrc rtl +gui在这里,各参数与三命令模式相同。

注意“ + ”。

在本文里将详细讲述ncverilog 的各种常用的参数,对于三命令模式,请读者自己查看资料。

+cdslib+... 设定你所仿真的库所在+define+macro ... 预编译宏的设定+errormax+整数当错误大于设定时退出仿真+incdir+path 设定include的路径+linedebug 允许在代码中设定line breakpoint+log+logfile 输出到名为logfile的文件中+status 显示内存和CPU的使用情况+work 工作库+access+w/r/c 读取对象的权限,缺省为无读(-w)无写(-r)无连接(-c)+gui 显示图形交互界面+input script_file 输入脚本文件+licqueque 如无licence等待licence+run 如果在GUI交互界面下, 启动后将自动开始仿真+loadpli1=... 动态加入PLI+timescale 设定仿真单位和精度+nocopyright 不显示版权信息。

verilogHDL培训教程华为(多场景)VerilogHDL培训教程——华为第一章:引言随着电子设计自动化(EDA)技术的不断发展,硬件描述语言(HDL)在数字电路设计领域扮演着越来越重要的角色。

VerilogHDL 作为一种主流的硬件描述语言,因其强大的功能、灵活的语法和广泛的应用范围,已成为数字集成电路设计工程师必备的技能之一。

本教程旨在帮助读者掌握VerilogHDL的基本概念、语法和设计方法,为华为等企业培养合格的数字电路设计人才。

第二章:VerilogHDL基础2.1VerilogHDL简介VerilogHDL是一种用于数字电路设计的硬件描述语言,它可以在多个层次上对数字系统进行描述,包括算法级、寄存器传输级(RTL)、门级和开关级。

VerilogHDL的设计初衷是为了提高数字电路设计的可重用性、可移植性和可维护性。

2.2VerilogHDL编程环境(1)文本编辑器:Notepad++、SublimeText等;(2)仿真工具:ModelSim、IcarusVerilog等;(3)综合工具:XilinxISE、AlteraQuartus等。

2.3VerilogHDL语法基础(1)关键字:VerilogHDL中的关键字具有特定含义,如module、endmodule、input、output等;(2)数据类型:包括线网类型(wire)、寄存器类型(reg)、整数类型(integer)等;(3)运算符:包括算术运算符、关系运算符、逻辑运算符等;(4)模块与端口:模块是VerilogHDL设计的基本单元,端口用于模块之间的信号传递;(5)行为描述与结构描述:行为描述用于描述电路的功能,结构描述用于描述电路的结构。

第三章:VerilogHDL设计流程3.1设计流程概述(1)需求分析:明确设计任务和功能要求;(2)模块划分:根据需求分析,将设计任务划分为若干个模块;(3)编写代码:使用VerilogHDL编写各个模块的代码;(4)仿真验证:对设计进行功能仿真和时序仿真,确保设计正确;(5)综合与布局布线:将VerilogHDL代码转换为实际电路,并进行布局布线;(6)硬件测试:在FPGA或ASIC上进行实际硬件测试。

?Verilog-A 30分钟快速入门教程进入正题,学了几天的Verilog-A,平台是Agilent ADS,主要参考“ Verilog- AMS Language Reference Manual”和ADS的帮助文档。

现在的状态算是入门了,写了个简单的PLL。

总结这几天的学习,觉得效率太低,我以前有一定 Verilog 基础,研一时学过一点 VHDL-AMS ,学到现在这个状态应该半天就够了;入门的话, 30 分钟足矣;跟着这个教程走,你会很快了解和熟悉Verilog-A 。

(前提是有一定的 Verilog 基础和电路基础)1、基尔霍夫定律撑起了整个电路学的大厦(当然也可以认为基尔霍夫定律只是麦克斯韦方程的简化版),作为模拟电路描述语言 Verilog-A ,同样将基尔霍夫定律作为其基本,最重要的两个概念便是流量 (Flow) 和位 (Potential) ,在电学里是电流和电压,在力学里可以是力和距离,在热学里可以是功率和温差,等等。

在 Verilog-A中,你可以将电阻电容电感等器件用一个方程式来表述,比如I(out) <+ V(out)/R ,这样就产生了一个电阻,最后 Verilog-A 仿真器会用某种算法( 迭代是最常见的 ) 将 I(out) 和 V(out) 求解出来,然后根据这个解去算下一个时刻的 I 、V 等,当然这仅仅是指时域仿真。

2 、下面讲Verilog-A的语法:begin end //相当于C语言的一对大括号,与Verilog同if ( expression ) true_statement ;[ else false_statement ; ] //与Verilog同case ( expression ) case_item { case_item } endcasefor ( procedural_assignment ; expression;procedural_assignment ) statement//case与for语句都跟Verilog、C语言类似cross( expr [, dir [, time_tol [, expr_tol ]]] );//cross 用来产生一个 event ,如:@(cross(V(sample) -2.0, +1.0))//指 sample 的电压超过 2.0 时触发该事件,将会执行后面的语句, +1.0 表示正向越过, -1.0 则相反ddt( expr )// 求导,如:I(n1,n2) <+ C * ddt(V(n1, n2)); //表示了一个电容idt( expr ,[ ic [, assert [, abstol ]]] ) //积分,如:V(out) <+ gain * idt(V(in) ,0) + gain * V(in);// 比例积分,式中的 0 表示积分的初值transition( expr [, time_delay [, rise_time [, fall_time [, time_tol ]]]] )// 将 expr 的值 delay一下并指定上升下降沿时间,相当于一个传输门laplace_zp( expr ,ζ ,ρ)将 expr 进行拉普拉斯变换,具体表达式参看相关文献,还有laplace_zd()等数据类型:integer 、real ,另外就是 discipline ,不知道怎么翻译比较好,比如说它将电压电流这两个 nature 类型作为一个 discipline ,这些都在 disciplines.vams这个头文件里建好了,编程时要`include "disciplines.vams"。