移相正弦信号发生器设计

- 格式:ppt

- 大小:149.50 KB

- 文档页数:11

基于FPGA的DDS移相变频正弦信号发生器设计杨春红;李石【期刊名称】《数字通信世界》【年(卷),期】2014(000)010【摘要】The direct digital frequency synthesis (DDS) technology has high frequency resolution, fast frequency switching, low phase noise and higher frequency stability, so it is widely used in communications, aerospace, instrumentation and other fields. In this paper, phase shift frequency variable sine signal generator with DDS as its core was designed based on Field Programmable Gate Array (FPGA) and hardware description language (VHDL). The experimental and simulation results show that the system has stable output frequency, high frequency accuracy, adjustable frequency and phase.%直接数字频率合成技术(DDS)由于具有频率分辨率高、频率切换速度快、相位噪声低和频率稳定度高等优点,广泛应用于通信、航空航天、仪器仪表等领域。

本文以FPGA为核心,以硬件设计语言VHDL为系统逻辑描述手段,设计了基于DDS原理的可移相、变频的正弦信号发生器。

仿真及实验结果表明:该系统具有输出频率稳定、频率精度高,频率和相位可调等特点。

第30卷 第1期华侨大学学报(自然科学版)Vol.30 No.1 2009年1月Journal of Huaqiao University (Natural Science ) J an.2009 文章编号: 100025013(2009)0120034204DDS 数字移相正弦信号发生器的设计高 银,林其伟(华侨大学信息科学与工程学院,福建泉州362021)摘要: 在直接数字频率合成器(DDS )的基础上,利用现场可编程门阵列(FP GA )设计一款数字移相正弦信号发生器,并通过Altera 公司的DE2开发板来验证1在输入环节加入一个数据锁存器,用“软设置”替代“硬设置”,同时在ROM 的验证中只采样正弦波的正上半周,来代替整个周期的采样,以降低系统的设计规模,减少系统对逻辑资源的需求1最后,绘制数字移相正弦信号发生器的顶层电路图,在QUAR TUS 6.0软件中进行仿真和硬件验证结果1关键词: 直接数字频率合成器;现场可编程门阵列;信号发生器;正弦信号;数字移相中图分类号: TN 742.1文献标识码: A生成正弦波比较常用的方法是,用一片只读存储器(ROM )和一片数模转换器(DAC ),加上地址发生计数器和寄存器[122].由于直接数字频率合成器(DDS )具有频率分辨率高、频率变换速度快、相位可连续变化等特点[3],可以实现快速的频率切换,在频率改变时能够保持相位的连续性,很容易实现频率、相位和幅度的数控调制.因此,本文采用了DDS 的设计思路,通过现场可编程门阵列(FP GA )实现DDS 数字移相正弦信号发生器.1 设计方案1.1 DDS 数字移相原理DDS 技术的核心是相位累加器,它类似一个计数器.每来一个时钟信号,相位累加器的输出就增加一个步长的相位增量,相位增量的大小由频率控制字确定.经DDS 输出的信号可描述为S out =A sin (ωt )=A sin (2πf out t ),(1)其中,S out 为经DDS 输出的信号,f out 为对应的输出频率1时间t 是连续的.为便于数字逻辑描述该表达式,需进行离散化处理,用基准时钟信号clk 进行抽样1设正弦信号的相位φ=2πf out t ,而在一个时钟周期T clk 相位φ变化量为Δφ=2πf out T clk =2πf out f clk.(2)式(2)中,f clk 是clk 的频率,对于2π可以看成是满相位的1为了对输出的相位进行控制,通过一个常数P 来实现,而每个clk 周期的相位增量Δθ用P 来表示,即Δθ=P ・Δφ1与式(2)联立可得Δθ=P ・2πf out f clk.(3)显然,信号发生器的输出可描述为S out =A sin (φ+P ・Δφ)=A sin (φ+Δθ)1(4)上式中,φ代表正弦信号发生器原始相位值1由上述推导可看出,对相位值进行简单的累加运算,就可以得到正弦信号当前相位值,也就得到了DDS 输出的正弦信号.收稿日期: 2007212210 通信作者: 林其伟(19572),男,副教授,主要从事智能仪器仪表的研究.E 2mail :qwlin @. 基金项目: 国务院侨办科研基金资助项目(06QZR03)1.2 DDS 数字移相正弦信号发生器设计由式(3)得出相位累加器的输入又可以称为相位字输入,实际上系统的基准时钟频率为f clk =2N f out 1那么,由式(3)得DDS 数字移相正弦信号发生器相移为图1 信号发生器原理框图Fig.1 Block diagram of the signal generator Δθ=P ・2π2N . (5) 频率字输入要经过一组同步寄存器,使得频率字改变时不会干扰相位累加器正常工作.相移信号发生器就是在DDS 基础上多了一个波形数据SIN ROM 表1它的地址线没有经过移相用的N 位加法器,而直接与相位累加器相连,用此链路作为基准正弦信号输出,整个框架[4]原理如图1所示.为便于设计复杂性的控制,将频率控制字设置为10位宽(二进制).频率控制字通过相位累加器来控制相位地址的变化.相位累加器的地址累加到半个周期的地址(即地址值为512)时就会溢出,则从0开始重新再次累加.相位累加器输出的数据通过寄存器锁存,防止累加器输出的数据不稳定.在加法器的模块中加入相移控制字P ,用来直接控制着输出端相移大小.在加法器模块的输出数据也对应着SINROM 数值的地址,经寄存器出来的地址数据,在SINROM 表中查找对应地址的量化值,然后经寄存器输出,即得到经数字移相后的数字正弦信号.此SINROM 表就是采用半个周期的正弦幅值数据.通过对半周期正弦幅值数据复用,来代替整个周期正弦幅值数据,以达到简化逻辑资源的目的.对比经数字移相前后的数字正弦信号的相位可知,相移后的正弦信号相差Δθ可用示波器测出.再与式(5)计算的理论相比较,即可验证设计方案是否成功.对于图1中虚线所示部分的DAC 数模转换器及低通滤波(L PF ),在仿真中暂时不考虑1因为L PF 主要用于平滑由实际生产中外界的干扰、噪声,以及直接接入通信信道(DACC )出来的噪声及毛刺现象,可以在实现硬件生产时再加入这两个部分.2 仿真与硬件验证2.1 系统仿真对于数字移相正弦信号发生器构建的顶层电路图,在QUAR TU S 6.0软件中进行仿真,得到仿真波形图如图2所示.输出的P out 是基准没有经过移相的正弦信号数据,而P 作为相移控制字,它直接控图2 信号发生器数据仿真图Fig.2 Data imitating curve of the signal generator制相移的步长,从而控制DDS 数字移相正弦信号发生器相移的大小,q 是相移后的正弦波形数据.采用频率控制字为1,以便相位累加器出来的地址数据能遍历每一个采样地址.从图2中可以知道,控制端en 和清零重置端reset 对此正弦移相信号发生器具有控制作用.在P out 为2.26μs 时,q 是530;而在P out 为2.28μs 时,q 是530,均能准确地反映P =4时正弦相移的情况.2.2 硬件验证为了能够更清晰地分析DDS 正弦相移信号发生器,采用D E2开发板进行硬件验证,并选用QU 2AR TU S 6.0里面的Signal Tap Ⅱ型嵌入式逻辑分析仪对设计中的重要层次模块信号接点进行测试[5].53第1期 高 银,等:DDS 数字移相正弦信号发生器的设计对顶层电路图略作修改,把两路正弦信号通过七段译码转换接口连接到七段译码器中,如图3所示.选用Altera 公司定制好的IP 核,完成七段译码转换连接的工作.它的一个最大优点是,该IP 核自带了引脚锁定功能,不需要再进行烦琐的引脚锁定.这个已经被Altera 公司优化过的模块,内部结构很简单,对提高系统的性能也有很大的帮助.图3 硬件验证的原理框Fig.3 Block diagram for hardware validating将修改后的系统电路在综合仿真后,下载到D E2开发板上.下载完成后,理论上是可以通过七段译码器显示正弦幅度数据,但是要通过七段译码显示的数据1这是在几十微秒数量级的时间内来回变化的,七段译码器不能分辨出来.因此,只能通过Signal Tap Ⅱ型嵌入式逻辑分析仪来观察七段译码器所显示的数据,如图4所示.从图4(a ),(b )可以看到,在DE2开发板上8个七段译码器,显示数据的频率(a)(b )图4 硬件反馈波形Fig.4 The feed backing curve of hardware63华侨大学学报(自然科学版) 2009年都很高,只有扩大时间的分辨率才能观察到七段译码器的数据.通过Signal Tap Ⅱ型嵌入式逻辑分析仪来观察下载到硬件里的正弦移相信息,在P 移动时,所对应的相移也跟着发生变化.图4(a )是截取相位控制字为32时所得1当坐标对准410时,经相移后的正弦波数据对应的幅值为10,原始正弦信号的幅值为0;当坐标向前移动到440时,第1次遇到原始正弦信号对应的幅值为10,如图4(b )所示.由图4的示波形图得到输出的相移值Δθ=(440-410)・2π210=15π256;而由式(5)可得Δθ=P ・2π2N =32・2π210=16π256,其相对误差为6.25%.如果实际应用的是32位数字移相正弦信号发生器,则误差将非常小甚至可以忽略掉1这反映整个数字移相正弦信号发生器设计的精确性,有实际应用价值.3 结束语利用可编程逻辑芯片,设计基于DDS 的数字相移频率发生器1在输入环节加入了一个数据锁存器,利用“软设置”替代“硬设置”,并在ROM 的验证中,只采样正弦波的上半周来代替整个周期的采样,降低了系统的设计规模,减少了系统对逻辑资源的需求.实验结果也证明,在这方面能够提高硬件资源的利用率,提高运行速度.这在对真正的流片成产品时是非常重要的,它大大地降低成本,提高了芯片的整体性能.参考文献:[1] 潘 松,黄继业1EDA 技术与V HDL [M ].北京:清华大学出版社,2005:3882396.[2] 潘 松,黄继业1EDA 技术实用教程[M ].北京:科学出版社,2002:3412346.[3] 黄 飞,鲁迎春,何晓雄.基于DDS 的L FM 信号发生器的FP GA 设计[J ].合肥工业大学学报:自然科学版,2006,29(5):6172619.[4] 章小梅,姜茂仁,费元春.DDS 杂散的抑制与研究[J ].信息技术,2004,6(4):124.[5] 邓 成,张亚妮,白 璘,等.嵌入式逻辑分析仪在FP GA 设计中的应用[J ].现代电子技术,2006(2):76284.The Design of DDS Digital Phase 2Shift Sine Signal G eneratorGAO Yin ,L IN Qi 2wei(College of Information Science and Engineering ,Huaqiao University ,Quanzhou 362021,China )Abstract : Based on direct digital synthesizer (DDS )and using field programmable gate array (FP GA ),a digital phase 2shift sine signal generator had been designed.This signal generator was verified through Altera Corporation ′s DE2devel 2op board.In this design ,a data flip 2latch was added at the input side ,the “soft setting ”was employed instead of “hard setting ”.At the same time ,and the positive half period sampling was used instead of the f ull period sampling of sine wave in the ROM verification ,,the scale of system and the demand to the systemic logic resources were reduced.At the end ,the top layer circuit diagram of digital phase 2shift sine signal generator was drawn ,and the hardware circuit was simulated on the Quareus 6.0.K eyw ords : direct digital synthesizer ;field programmable gate array ;signal generator ;sine signal ;digital phase 2shift(责任编辑:鲁 斌 英文审校:吴逢铁)73第1期 高 银,等:DDS 数字移相正弦信号发生器的设计。

摘要: 文章介绍了基于FPGA和数字频率合成技术,利用VHDL 编制程序并下载至Xilinx公司的SpartanⅡ系列XC2S100E-6PQ208 FPAG芯片上,加以简单的外围电路,构成了高精度数字式移相正弦波信号发生器。

该装置能够产生频率、相位、幅度均可数字式预置并可调节的两路正弦波信号,相位差范围为0~359°,步进为1°。

关键词:数字移相;FPGA;VHDL;直接数字频率合成1.引言在一些试验、研究中,有时需要存在相位差的两同频信号。

通常采用移相网络来实现,如阻容移相,变压器移相等。

采用这些方法有许多不足之处,比如:输出波形受输入波形的影响,移相操作不方便,移相角度随信号频率和所接负载等因素的影响等。

若采用直接数字频率合成及数字移相技术,能得到频率及相位差高度稳定精确的信号且实现方便。

2.波形及移相波形发生器的系统组成原理如图1所示为波形及移相波形发生器的系统组成方框图。

500)this.style.width=500;" border=0>图1 波形及移相波形发生器的系统组成原理框图标准时钟(由晶振电路产生)加于进制可编程的n进制计数器,其溢出脉冲加于可预置初值的地址计数器,生成波形存储器所需的地址信号,地址信号的产生频率正比于时钟频率,且周而复始地变化,从而使波形数据存储器输出周期的正弦序列,D/A转换器则输出连续的模拟正弦电压(或电流)波形,如图2所示。

500)this.style.width=500;" border=0>为移相方便,设一周期的正弦波共采样360个点,即波形数据存储器共存储360个正弦波形的数据。

由于移相波形的地址计数器的第一次运行初值为m,故两正弦波存在相位差为m°。

相邻采样点有n 个标准时钟脉冲间隔,即500)this.style.width=500;" border=0> 。

图1中波形数据存储器的全部数据被读出一次的频率为:500)this.style.width=500;" border=0> 。

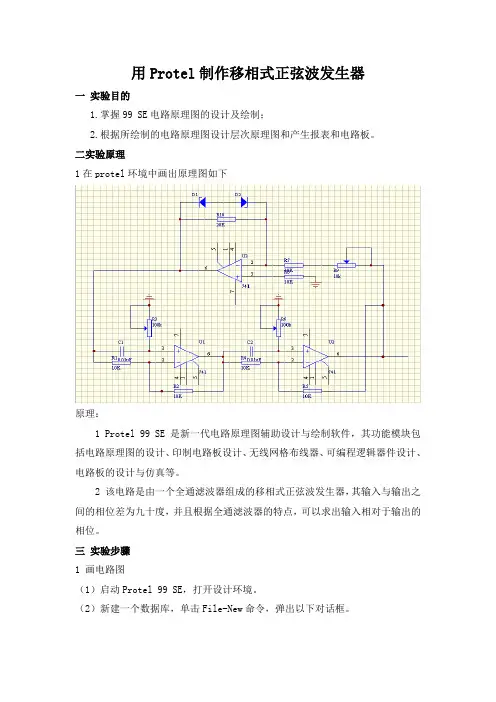

用Protel制作移相式正弦波发生器一实验目的1.掌握99 SE电路原理图的设计及绘制;2.根据所绘制的电路原理图设计层次原理图和产生报表和电路板。

二实验原理1在protel环境中画出原理图如下原理:1 Protel 99 SE 是新一代电路原理图辅助设计与绘制软件,其功能模块包括电路原理图的设计、印制电路板设计、无线网格布线器、可编程逻辑器件设计、电路板的设计与仿真等。

2 该电路是由一个全通滤波器组成的移相式正弦波发生器,其输入与输出之间的相位差为九十度,并且根据全通滤波器的特点,可以求出输入相对于输出的相位。

三实验步骤1 画电路图(1)启动Protel 99 SE,打开设计环境。

(2)新建一个数据库,单击File-New命令,弹出以下对话框。

点击OK后,生成一个叫“李婷.ddb”的文件夹。

(3)新建一个空白的Sch文件,再次点击File-New命令,弹出以下对话框。

选择Sch后点击OK,就生成了一个空白的名叫“李婷. Sch”Sch文件,(4)根据实际电路需要,加载元件库。

(5)找到所需元件,根据原理图连接电路,Sch文件正式生成。

生成的电路如原理图所示。

2生成ERC结果(1)打开原理图文件,执行菜单命令Tools-ERC.(2)执行该命令后,会出现一对话框,用户可以设置有关电气规则检查的选项。

(3)设置完电气规则检查选项后,程序自动进入文本编辑器并生成相应的检查错误报告。

(4)系统在发生错误的位置放置红色的符号,提示错误的位置3产生网络表(1)执行Design→Creat Netlist菜单命令(2)执行该命令后,会出现一对话框,用户可以进行对话框设置。

(3)对话框设置完成后,将进入Protel 99 SE的记事本程序,将结果保存为.net文件,产生如下图所示的网络表4产生材料清单(1)打开原理图文件,执行Report-→Bill of Material菜单命令。

(2)执行该命令后,系统会弹出一对话框,可以选择是产生整个项目(Project)的元件列表,还是产生当前原理图(Sheet)的元件列表。

DDS数字移相正弦信号发生器的设计

高银;林其伟

【期刊名称】《华侨大学学报(自然科学版)》

【年(卷),期】2009(030)001

【摘要】在直接数字频率合成器(DDS)的基础上,利用现场可编程门阵列(FPGA)设计一款数字移相正弦信号发生器,并通过Altera 公司的DE2开发板来验证.在输入环节加入一个数据锁存器,用"软设置"替代"硬设置",同时在ROM的验证中只采样正弦波的正上半周,来代替整个周期的采样,以降低系统的设计规模,减少系统对逻辑资源的需求.最后,绘制数字移相正弦信号发生器的顶层电路图,在QUARTUS 6.0软件中进行仿真和硬件验证结果.

【总页数】4页(P34-37)

【作者】高银;林其伟

【作者单位】华侨大学,信息科学与工程学院,福建,泉州,362021;华侨大学,信息科学与工程学院,福建,泉州,362021

【正文语种】中文

【中图分类】TN742.1

【相关文献】

1.基于DDS与数字电位器的正弦信号发生器设计 [J], 孙莹莹;卢京阳;刘思久;贲洪奇

2.基于DDS的数字移相正弦信号发生器的设计 [J], 肖炎根

3.基于FPGA的DDS移相变频正弦信号发生器设计 [J], 杨春红;李石

4.基于单片机的数字式可移相正弦信号发生器设计 [J], 刘晓艳;杨宁

5.基于DDS技术的数字移相正弦信号发生器的CPLD设计与仿真 [J], 雷能芳;苏变玲

因版权原因,仅展示原文概要,查看原文内容请购买。

正弦信号发生器设计方案一、方案比较论证所有方案可按模拟式和数字式分为两大类模拟式:①利用电阻、电容、运放等传统器件搭建LC或RC正弦信号发生器。

通过改变电路中的元件的参数值来调节输出频率。

这种方式成本低廉,但由于采用大量分立器件,受其工作原理的限制频率稳定度较低(只有10-3量级)。

另外实现扩展功能中的各种调制等也比较麻烦,电路复杂,调试困难,精度差。

②采用专用信号发生芯片MAX038来实现正弦信号波形的输出。

是美信公司的低失真单片信号发生集成电路,内部电路完善,使用该器件能够产生精确的高频三角、锯齿、正弦及方波。

使用该芯片设计简单,但扩展功能电路部分实现起来和采用分立器件同样复杂,而且频率精度和稳度均难以达到要求。

③采用基于锁相环(PLL)技术或者非线性器件频率变换技术的频率合成器。

由晶体振荡器和锁相环组成的系统中,前者保证工作频率稳定度,后者完成输出频率的调整,但是这时输出频率只能是晶体谐振频率的整数倍。

故虽然频率稳定能达到要求却很难做到频率输出范围1KHZ—10MHZ和100HZ步进的要求。

数字式:①采用AD公司专用的DDS芯片AD9851合成FM和AM的载波,采用传统的模拟调制方式来实现AM调制和FM调制。

但该方案需要额外的模拟调制FM和AM的调制电路,且制作和调制电路都比较麻烦,还难免引入一定的干扰,而且此方案中的PSK调制也不容易实现。

②采用AD公司的AD9856作为调制芯片,是内含DDS的正交调制芯片,可以实现多进制的数字幅度调制,多进制的数字相位调制和多进制的数字幅度相位联合调制。

故AM 调制,PSK调、ASK调制都可以通过它实现但是AD9856不便于调频且控制复杂。

③利用微处理器和DAC实现DDS信号产生器。

微处理器能够实现DDS的电路结构,即实现相位累加器、波形的数据表、同时实现数字/模拟转换器的控制时序。

利用微处理器完成加法运算需要读取的数据进行运算,再把运算结果送到目标单元。

基于DDS的数字移相信号发生器一、课程设计目的1、进一步熟悉QuartusⅡ的软件使用方法;2、熟悉利用VHDL设计数字系统并学习LPM ROM的使用方法;3、学习FPGA硬件资源的使用和控制方法;4、掌握DDS基本原理,学习利用此原理进行信号发生器的设计。

二、设计任务1、完成8位输出数据宽度的频率可调的移相正弦信号发生器。

2、完成8位输出数据宽度的频率可调的移相三角波、方波信号发生器。

3、以上三种波形使用一个按键依次切换。

4、波形发生器实现幅度可调。

5、信号发生器的原始数据存储在外部存储器里,由FPGA进行读取,经过D/A转换输出,由示波器观察最终结果。

6、完成两路相位相差90度的频率幅度可调的移相信号发生器。

结果通过嵌入式分析仪观察两路正交信号。

(包括正弦波、方波、三角波)注意:以上前5点为基本要求,第6点为提高要求。

三、基本原理直接数字频率合成器(DDS)是通信系统中常用到的部件,利用DDS可以制成很有用的信号源。

与模拟式的频率锁相环PLL相比,它有许多优点,突出为(1)频率的切换迅速;(2)频率稳定度高。

一个直接数字频率合成器由相位累加器、波形ROM、D/A转换器和低通滤波器构成。

DDS的原理框图如下所示:图1 直接数字频率合成器原理图其中K为频率控制字,f c为时钟频率,N为相位累加器的字长,D为ROM 数据位及D/A转换器的字长。

相位累加器在时钟f c的控制下以步长K作为累加,输出N位二进制码作为波形ROM的地址,对波形ROM进行寻址,波形ROM 输出的幅码S(n)经D/A转换器变成梯形波S(t),再经低通滤波器平滑后就可以得到合成的信号波形了。

合成的信号波形形状取决于波形ROM中存放的幅码,因此用DDS可以产生任意波形。

本设计中直接利用D/A转换器得到输出波形,省略了低通滤波器这一环节。

1、频率预置与调节电路不变量K被称为相位增量,也叫频率控制字。

DDS方程为:f0= f c K/2n,f0为输出频率,f c为时钟频率。

制作一个正弦信号发生器的设计

一、正弦信号发生器的概念

正弦信号发生器是一种可以产生所需频率的正弦波信号的设备,可以

帮助开发者测量和分析频率特性,也可以用于相关系统的诊断。

正弦信号

发生器可以产生指定频率的正弦波形,以满足不同系统的需求。

它也可以

通过波形对比法进行精确的波形测量,用于分析电子系统特性。

(1)电路设计

正弦信号发生器的电路设计主要有两种:一种是基于模拟电路的设计,另一种是基于数字电路的设计。

(1)模拟电路

模拟电路设计采用的是电路模块,主要有振荡器、滤波器、缓冲器和

调制电路。

(a)振荡器

振荡器主要由振荡电路和调整元件组成,振荡器的作用是形成振荡的

正弦波,以满足信号发生器产生不同频率的要求。

(b)滤波器

滤波器的作用是滤除振荡器产生的额外噪声,以得到纯净的正弦信号。

(c)缓冲器

缓冲器的主要作用是将振荡器的正弦波输出,缓冲器的作用是减少信

号失真,使正弦波更加完美。

(d)调制电路

调制电路的作用是对信号发生器产生的正弦波进行调制,使其能够输出更加稳定的信号频率。

(2)数字电路

采用数字电路设计的正弦信号发生器。

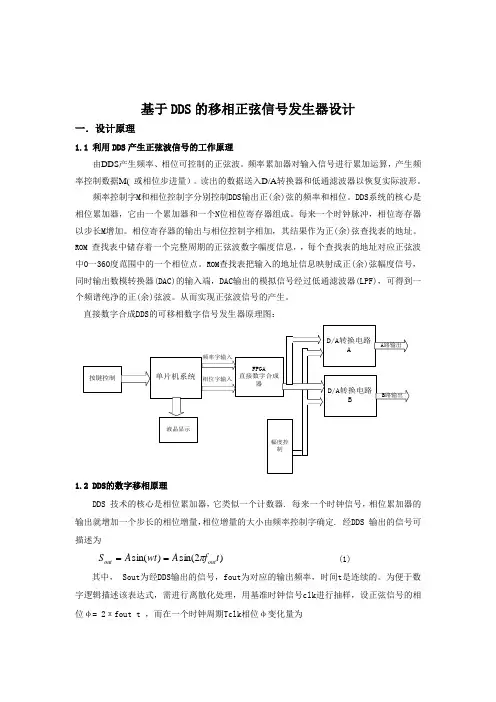

基于DDS 的移相正弦信号发生器设计一.设计原理1.1 利用DDS 产生正弦波信号的工作原理由DDS 产生频率、相位可控制的正弦波。

频率累加器对输入信号进行累加运算,产生频率控制数据M( 或相位步进量)。

读出的数据送入D/A 转换器和低通滤波器以恢复实际波形。

频率控制字M 和相位控制字分别控制DDS 输出正(余)弦的频率和相位。

DDS 系统的核心是相位累加器,它由一个累加器和一个N 位相位寄存器组成。

每来一个时钟脉冲,相位寄存器以步长M 增加。

相位寄存器的输出与相位控制字相加,其结果作为正(余)弦查找表的地址。

ROM 查找表中储存着一个完整周期的正弦波数字幅度信息,,每个查找表的地址对应正弦波中O 一360度范围中的一个相位点。

ROM 查找表把输入的地址信息映射成正(余)弦幅度信号,同时输出数模转换器(DAC)的输入端,DAC 输出的模拟信号经过低通滤波器(LPF),可得到一个频谱纯净的正(余)弦波。

从而实现正弦波信号的产生。

直接数字合成DDS 的可移相数字信号发生器原理图:1.2 DDS 的数字移相原理DDS 技术的核心是相位累加器,它类似一个计数器. 每来一个时钟信号,相位累加器的输出就增加一个步长的相位增量,相位增量的大小由频率控制字确定. 经DDS 输出的信号可描述为)2sin()sin(t f A wt A S out out π== (1)其中, Sout 为经DDS 输出的信号,fout 为对应的输出频率,时间t 是连续的。

为便于数字逻辑描述该表达式,需进行离散化处理,用基准时钟信号clk 进行抽样,设正弦信号的相位φ= 2πfout t ,而在一个时钟周期Tclk 相位φ变化量为clk out clk out f f T f ππφ22==∆ (2) 式(2)中, fclk 是clk 的频率,对于2π可以看成是满相位的1为了对输出的相位进行控制,通过一个常数P 来实现,而每个clk 周期的相位增量Δθ用P 来表示,即Δθ= P ·Δφ式1 与式(2) 联立可得clkout f f P πθ2⋅=∆ (3) 显然,信号发生器的输出可描述为)sin().sin(θφφφ∆+=∆+=A p A S out上式中,φ代表正弦信号发生器原始相位值,可看出,对相位值进行简单的累加运算,就可以得到正弦信号当前相位值,也就得到了DDS 输出的正弦信号。

正弦信号发生器摘要本系统以单片机和FPGA为控制和处理核心,基于直接数字频率合成原理,利用DDS集成芯片AD9851实现了300Hz~13MHz、步进为0.1Hz的正弦信号发生器和高频偏的DDS调频(FM)信号发生器;通过模拟乘法器MC1496实现调幅功能,其低频调制信号由FPGA和DAC0800构成DDS低频发生器产生;利用可变增益宽带放大器AD600实现幅度程控,通过检波和ADC反馈给单片机,检测和调整输出电压,实现精确的幅度控制。

使用了多种抗干扰措施以减少噪声并抑制高频自激;后级功放采用两片宽带运放AD811组成桥式功率放大器来实现。

本系统硬件设计应用了EDA工具,软件采用模块化的编程思想。

关键字:正弦信号发生器 DDS 调幅幅度控制桥式功率放大器AbstractBased on the principle of DDS, the system uses the A T89C51 and FPGA as the control and processing unit ,and uses the DDS chip AD9851 to realize the Sine and FM signal generator .The signal generator can output Sine signal of 300 Hz ~13M Hz with 0. 1 Hz frequency step, the MC 1496 is used to realize AM performance, the Amplitude control of signals are realized by using chip AD600,the low frequency modulation signal is produced by DDS made of FPGA and DAC 0800..Many methods are employed to diminish noises and restrain high frequency self-excitation. The test results show that the system achieves the requirements of design.正弦信号发生器一、方案论证与选择本系统难点有:1.产生稳定性高、频率步进较低、频带范围较广且具有一定带负载能力的正弦信号源;2.以1kHz为调制信号,在较大动态范围(100kHz~10MHz)内产生频偏为10kHz的调频信号;3.产生AM、ASK、PSK等调制信号。

1 概述正弦信号发生器作为电子技术领域里最基本的电子仪.器,应用及其广泛。

随着电子信息技术的发展,其性能的要求也越来越高,如高频率稳定度和高转换速度、具有调幅调相等功能[1]。

在实际的测量中,不仅需要正弦信号发生器还经常需要移相正弦信号发生器,及存在相位差的两路同频信号。

移相信号发生器目前已经广泛用于船舶、航空、检测等各行各业[2]。

2 系统的整体设计方案2.1 系统设计思想利用MATLAB/Simulink 中完成原理图的设计,模型仿真并通过SignalCompilder 转换成为VHDL 语言,最后验证VHDL 代码,并将正确的代码下载到硬件现实系统功能。

整个设计结构思路如图1所示。

2.2 系统设计框图DDS 以数控的方式产生频率、相位可以控制的正弦波,DDS 的基本结构主要由相位累加器、正弦ROM 查找表和D/A构成,相位累加器是整个DDS 核心。

每来1个时钟脉冲,加法器将频率控制字与相位寄存器输出的数据相加,把相加后的结果送至相位寄存器的输入端。

当下一个时钟脉冲时,累加器又将频率控制字与相位寄存器的输出数据相加,这样相.位累加器在参考时钟的作用下,进行线性相位累加,当相位累加器累积满量程(2π)时就会产生1次溢出,完成1个周期性的动作,这个周期就是DDS 合成信号的1个频率周期,累加器的溢出频率就是DDS 输出的信号频率如图3所示。

图1 设计结构图based technology, according to the principle of phase sinusoidal signal using matlab / simlink / DSP Builder build phase sinusoidal signal model, using direct digital frequency synthesis (DDS), designed to achieve a frequency, phase controllable sinusoidal signal generator. This method is designed using CNC phase sinusoidal signal generator capable of generating frequency, phase can be preset and adjustable digital sine wave signal, the digital phase shifting generator frequency, phase, amplitude can be preset to distinguish rate, precisely adjustable, and can be used separately two independent signal generator. This approach designed to facilitate generator controlled phase shifting fast, improve development efficiency and shorten the development cycle, and easy to debug the system, easy to modify.Keywords: FPGA;DSP Builder;Direct Digital Frequency Synthesis;Digital Phase Shifting图3 DDS 输出波形图图4 整个系统电路原理图直接数字频率合成(DDS)移相原理是:数字移相信号发生器的核心是DDS,在计数器的控制下相位累加器输出与相位增量相加,相加后的结果形成正弦查询表地址,取出表中与该相位对应的单元中的幅度量化正弦函数值,经高速D/A 转换器输出模拟信号。

课程设计(论文)题目简易正弦信号发生器设计学院名称电气工程学院指导教师职称班级学号学生姓名2016年10 月10 日南华大学课程设计(论文)任务书学院:电气工程学院题目:简易正弦信号发生器设计起止时间:2016年9月10日至2016年10月10日学生姓名:专业班级:指导教师:教研室主任:院长:2016 年10 月10 日摘要:移相式正弦波发生器电路,其频率稳定度通过实际测试为0.002%。

该电路性价比高,用很便宜的几个元件在很宽的频段内,实现频率连续可调。

移相式正弦波发生器是由RC超前或滞后移相反馈网络和反向放大器组成,常用于产生低频正弦信号。

RC 与运放构成的反馈网络包含180°相移,与负反馈放大器正好在该频率上构成正反馈,满足振荡的相位平衡条件,同时使放大器闭环增益大于1,即满足振荡的振幅平衡条件,就能在输出端得到正弦波振荡信号。

关键词:移相式正弦波发生器;频率可调;正反馈Abstract:Phase-shifted sine wave generator circuit, the frequency stability through the actual test of 0.002%. The circuit cost-effective, very cheap with a few components in a very wide frequency band, to achieve continuous adjustable frequency. Phase-shifted sine wave generator is composed of RC lead or lag phase-shifted feedback network and reverse amplifier, commonly used to generate low-frequency sinusoidal signal. The feedback network composed of RC and op amp consists of 180 °phase shift, and the negative feedback amplifier forms the positive feedback exactly at the frequency, which satisfies the phase balance condition of oscillation, and makes the amplifier closed-loop gain greater than 1, which satisfies the oscillation amplitude balance condition. A sine wave oscillation signal can be obtained at the output terminal.Key words: Phase - shifted sine wave generator; Frequency adjustable; Positive feedback目录任务书 (I)中文摘要 (IV)英文摘要 (V)1. 绪论 (1)2. MULTISIM软件介绍 (1)3. 设计要求 (2)3.1设计要求 (2)3.2技术指标 (2)4. 方案设计与论证 (2)4.1设计思想 (2)4.2总体方案 (3)5. 设计原理及电路图 (3)5.1设计原理 (3)5.2仿真电路图 (5)6. 软件仿真与硬件调试 (5)6.1软件仿真 (5)6.2硬件调试 (7)7. 收获与体会 (8)8. 参考文献 (9)9. 附录:实物图 (10)1 绪论正弦信号源在实验室和电子工程设计中有着十分重要的作用,正弦信号主要用于测量电路和系统的频率特性、非线性失真、增益及灵敏度等。

基于FPGA的数控移相正弦信号发生器设计数控移相正弦信号发生器是一种可以生成可编程幅度、频率和相位的正弦信号的设备。

其设计基于现场可编程门阵列(FPGA)技术,可以实现高度灵活性和精确性。

要设计一个基于FPGA的数控移相正弦信号发生器,我们需要考虑以下几个方面:1. FPGA选择:选择适合设计的FPGA芯片,这需要根据信号发生器的要求(幅度、频率、相位精度等)和设计成本来确定。

常用的FPGA芯片有Xilinx的系列和Altera(现在是英特尔)的系列。

根据具体需求选择合适的FPGA芯片。

2.数模转换:在FPGA内部需要使用数模转换器将数字数据转换成模拟信号。

这可以使用数字到模拟转换器(DAC)来实现。

DAC负责将数字信号转换成连续的模拟信号,以便于输出。

3.正弦信号生成:在FPGA中使用数学计算和相位累加器的方法生成正弦波形信号。

首先,使用数学计算生成包含一个周期(360度或2π)中所有可能相位的正弦波表。

然后,通过一个相位累加器按照要求的频率和相位来选择波形。

4.频率控制:频率控制可以使用一个可编程的计数器来实现。

使用计数器来计算每个时钟周期的累加次数,从而确定正弦波的输出频率。

可以通过修改计数器的计数初始值来调整输出频率。

5.相位控制:相位控制可以通过一个可编程的累加器来实现。

累加器的值将用作正弦波表的索引,以选择正确的相位值。

通过调整累加器的初始值和累加步长,可以实现需要的相位偏移。

6.幅度控制:幅度控制可以使用一个可编程的增益控制器来实现。

增益控制器通过改变DAC的输入电压来控制输出信号的幅度。

可以通过修改增益控制器的增益值来调整输出信号的幅度。

7.控制接口:为了方便用户对信号发生器的控制,可以添加一个控制接口,如按钮、开关、旋钮或者串行通信接口(如UART、SPI)。

通过这些接口,用户可以编程设置信号发生器的参数,如频率、相位、幅度等。

设计完毕后,我们可以通过FPGA的开发工具将设计烧录到FPGA芯片中,并通过相应的接口连接到外部电路中,实现数控移相正弦信号的发生。