CMOS比较器(6)解读

- 格式:ppt

- 大小:2.07 MB

- 文档页数:34

cmos电压迟滞比较器电路标题:CMOS电压迟滞比较器电路的原理与应用导语:本文将深入探讨CMOS电压迟滞比较器电路的原理与应用。

通过分析其工作原理、特点和优势,我们可以更好地理解它在现代电路设计中的重要性和应用价值。

摘要:CMOS电压迟滞比较器电路是一种关键的电子元件,其通过比较输入电压与参考电压,产生高或低电平输出。

本文将从基本原理的介绍开始,详细讨论CMOS电压迟滞比较器电路的结构、工作方式和性能特点,并介绍其在数模转换、振荡器等领域的应用。

目录:1. 引言2. CMOS电压迟滞比较器电路的基本原理3. CMOS电压迟滞比较器电路的结构和工作方式4. CMOS电压迟滞比较器电路的性能特点4.1 高输入阻抗和低功率消耗4.2 快速响应和高精度4.3 低噪声和抗干扰能力强5. CMOS电压迟滞比较器电路的应用5.1 数模转换5.2 振荡器5.3 其他应用领域6. 我对CMOS电压迟滞比较器电路的个人观点和理解7. 总结1. 引言CMOS电压迟滞比较器电路是一种用于比较输入电压和参考电压的重要元件。

它在现代集成电路设计中发挥着关键作用,广泛应用于数模转换、振荡器以及其他各种电路设计中。

在本文中,我们将对CMOS 电压迟滞比较器电路进行深入研究,以更好地了解其原理、结构、性能特点和应用。

2. CMOS电压迟滞比较器电路的基本原理CMOS电压迟滞比较器电路通过将输入电压与参考电压进行比较,输出高或低电平。

其基本原理基于MOS管的开关特性。

当输入电压大于参考电压时,输出结果为高电平;当输入电压小于参考电压时,输出结果为低电平。

这种电路可以通过调整参考电压的阈值、电流源和电压迟滞等参数,实现不同的比较功能。

3. CMOS电压迟滞比较器电路的结构和工作方式CMOS电压迟滞比较器电路一般由输入级、差分放大器和输出级等部分组成。

输入级主要负责将输入电压进行增益放大,差分放大器用于进行输入电压和参考电压的比较,并输出差分信号,输出级将差分信号转化为高或低电平输出。

cmos电压比较器工作原理CMOS电压比较器作为一种常见的电子电路元件,广泛应用于模拟电路和数字电路中。

它主要用于比较两个电压信号的大小,并根据比较结果产生输出。

本文将详细介绍CMOS电压比较器的工作原理,从输入端、比较器电路、输出以及工作过程等方面加以说明,以帮助读者更好地理解和应用CMOS电压比较器。

一、输入端:CMOS电压比较器的输入端主要包括正向输入端(+IN)和反向输入端(-IN)。

+IN和-IN分别接收待比较的两个电压信号。

在比较器工作过程中,电压信号较大的输入端通常被连接为正向输入端,而电压信号较小的输入端则连接为反向输入端。

比较器根据这两个输入端的电压差异来判断两个输入信号的大小。

二、比较器电路:CMOS电压比较器的核心是比较器电路,它根据输入信号的电压差异来产生输出结果。

比较器电路一般由多个晶体管和电阻器组成。

例如,一个常见的CMOS电压比较器电路是由两个互补MOS(CMOS)晶体管构成,分别是P型MOS晶体管和N型MOS晶体管。

这两个晶体管通过控制电压的变化来实现电压比较和输出的切换。

CMOS电压比较器的输出主要有两种状态,即高电平和低电平。

输出根据输入信号的电压差异来切换状态。

当+IN电压大于-IN电压时,输出为高电平;当+IN电压小于-IN电压时,输出为低电平。

输出信号可被进一步使用于数字电路中的逻辑电路或模拟电路中的信号处理。

假设我们有一个CMOS电压比较器,输入端的+IN接收一个电压信号Vin=3V,而-IN接收一个电压信号Vin'=2V。

在这种情况下,比较器电路将根据这两个输入信号的差异来产生输出。

由于Vin大于Vin',所以比较器的输出为高电平。

如果Vin=2V,Vin'=3V,那么比较器的输出将会是低电平。

四、工作过程:CMOS电压比较器的工作过程可以分为下述几个步骤:1.输入阶段:输入信号通过正向和反向输入端输入到比较器电路中。

2.比较阶段:比较器电路根据输入信号的电压差异进行比较,并判断电压的大小关系。

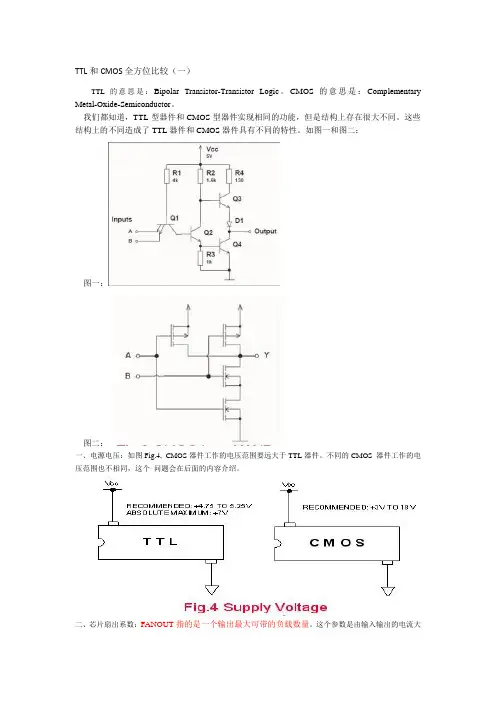

TTL和CMOS全方位比较(一)TTL的意思是:Bipolar Transistor-Transistor Logic。

CMOS的意思是:Complementary Metal-Oxide-Semiconductor。

我们都知道,TTL型器件和CMOS型器件实现相同的功能,但是结构上存在很大不同。

这些结构上的不同造成了TTL器件和CMOS器件具有不同的特性。

如图一和图二:图一:图二:一、电源电压:如图Fig.4, CMOS器件工作的电压范围要远大于TTL器件。

不同的CMOS 器件工作的电压范围也不相同,这个问题会在后面的内容介绍。

二、芯片扇出系数:FANOUT指的是一个输出最大可带的负载数量。

这个参数是由输入输出的电流大小来决定的。

在使用TTL器件时,需要特别注意这个参数。

CMOS器件,由于电流小,FANOUT值很大。

如图Fig.5所示,该器件的FANOUT = 5TTL和CMOS全方位比较(二)四、传输延时:Tphl指由高电平变为低电平的延时,Tplh指由低电平变为高电平的延时。

通常情况下,Tphl 不等于Tplh。

这个传输延时将决定芯片可工作的最高频率。

五、消耗功率:功率使用瓦特(watts)来计量。

它代表着芯片在单位时间内消耗的电能。

这是一个很重要的参数。

不同种类的芯片所消耗的功率有很大的不同。

从上面表格中,可以得到以下结论:Ø TTL 器件的工作电压基本相同Ø 各种TTL器件的VOH ,VOL, VIH ,VIL 基本相同Ø 低功耗型器件(ALS,LS)的电流要小于非低功耗型器件(AS,F)Ø 改良型器件的传输延时要小于非改良型器件Ø F型器件的各项参数都处在一个中等水平,是目前广泛采用的一种从上面表格中,可以得到以下结论:Ø CMOS器件可以工作在很大的电压范围Ø 名称中包含T的CMOS器件的VOH ,VOL, VIH ,VIL 和TTL器件相同Ø CMOS器件的功耗要远小于TTL器件。

cmos电压迟滞比较器电路摘要:一、引言二、CMOS 电压迟滞比较器电路的工作原理1.电路结构2.工作原理三、CMOS 电压迟滞比较器的特性1.输入电压范围2.输出电压3.迟滞特性四、CMOS 电压迟滞比较器的应用1.波形发生器2.电压监控器3.逻辑电路五、CMOS 电压迟滞比较器的优缺点1.优点2.缺点六、结论正文:一、引言CMOS 电压迟滞比较器电路是一种广泛应用于电子领域的电压比较器,其具有较高的性能和稳定性,被广泛应用于各种电子设备中。

本文将详细介绍CMOS 电压迟滞比较器电路的工作原理、特性以及应用。

二、CMOS 电压迟滞比较器电路的工作原理1.电路结构:CMOS 电压迟滞比较器电路主要由NMOS 和PMOS 晶体管组成,具有输入端、输出端和电源端。

其核心部分是电压比较器,具有两个输入端和一个输出端。

2.工作原理:当输入电压达到一定值时,比较器将根据输入电压的差异产生不同的输出电压。

具体而言,当输入电压差大于预设阈值时,输出电压为高电平;当输入电压差小于预设阈值时,输出电压为低电平。

三、CMOS 电压迟滞比较器的特性1.输入电压范围:CMOS 电压迟滞比较器具有较宽的输入电压范围,可以满足不同应用场景的需求。

2.输出电压:CMOS 电压迟滞比较器的输出电压具有较大的驱动能力,可以驱动多种负载。

3.迟滞特性:CMOS 电压迟滞比较器具有较好的迟滞特性,能够在一定范围内保持稳定的输出电压。

四、CMOS 电压迟滞比较器的应用1.波形发生器:CMOS 电压迟滞比较器可以产生不同频率和幅度的波形信号,被广泛应用于通信领域。

2.电压监控器:CMOS 电压迟滞比较器可以用于监测电源电压、模拟信号等,具有较高的精度和稳定性。

3.逻辑电路:CMOS 电压迟滞比较器可以与其他逻辑电路器件组合,实现复杂的逻辑功能。

五、CMOS 电压迟滞比较器的优缺点1.优点:CMOS 电压迟滞比较器具有较高的性能、稳定性和可靠性,输入电压范围宽,输出电压驱动能力强,迟滞特性好。

cmos比较器原理

CMOS比较器是一种电路器件,用于比较两个电压的大小,

并输出其比较结果。

其原理是基于CMOS技术,使用MOSFET(金属-氧化物半导体场效应晶体管)作为开关。

CMOS比较器通常由一个或多个差分对和输出级组成。

在一个典型的CMOS比较器中,差分对由两个高阻抗输入的MOSFET组成,一个作为正输入,一个作为负输入。

当输入

电压中的一个大于另一个时,相应的MOSFET导通,将电荷

传递到输出级。

输出级由两个CMOS反向驱动的晶体管组成,一个在正电压上驱动,另一个在负电压上驱动。

这些反向驱动的晶体管将电荷从输入级传递到电路输出,产生一个高电平或低电平的输出电压。

当两个输入电压相等时,差分对中的两个MOSFET都处于相

反的导通状态,输出级中没有电荷传递,输出电压保持不变。

而当一个输入电压大于另一个电压时,差分对中相应的MOSFET会导通,将电荷传递到输出级,输出电压发生变化。

输出电压的变化可以通过反馈电路来增强,并改善比较器的性能。

CMOS比较器具有低功耗、高转换速度和较大的输入电阻等

优点,使其在数字电路中得到广泛应用。

它常用于模数转换、电压级移位和逻辑控制等领域。

由于CMOS比较器不需要额

外的功耗,它在电池供电等低电源电压条件下的应用非常适合。

cmos电压比较器工作原理CMOS电压比较器是一种常用的电子器件,它可以将两个输入电压进行比较,并输出相应的逻辑信号。

本文将简要介绍CMOS电压比较器的工作原理。

CMOS电压比较器由两个互补的MOS管组成,通常为n型和p型MOS管。

其中n型MOS管通常被称为NMOS管,p型MOS管则被称为PMOS管。

这两个MOS管的控制端一般用一个差分输入电路来形成,分别对应输入电压的正和负端。

CMOS电压比较器通常由以下三个部分组成:差分输入电路、比较器和输出电路。

首先是差分输入电路。

它由两个输入晶体管和一个负反馈电路组成。

输入电压通过差分输入电路被分成正、负两支,正输入端和负输入端分别与输入电压的正负端相连。

正负两支输入电压的大小决定了输入电压的大小和极性。

接下来是比较器。

比较器是用来将输入电压转换为输出电压的核心部分。

通常情况下,比较器由两个互补MOS管构成。

输入电压经过差分输入电路后,相应的信号被传递到互补MOS 管。

当输入电压的正支大于负支时,NMOS管将被打开,PMOS管将被关闭;反之,当输入电压的负支大于正支时,NMOS管将被关闭,PMOS管将被打开。

因此,比较器将输入电压的大小和极性转换为了不同的管路状态。

最后是输出电路。

输出电路用于提取和输出比较器的输出信号。

输出电路通常由一个或多个电晶体管组成,它们的工作状态与比较器的输出信号相关联。

比如,当开关管为导通状态时,输出电压为高电平;相反,当开关管为截止状态时,输出电压为低电平。

总的来说,CMOS电压比较器利用差分输入电路将输入电压的大小和极性转换为互补MOS管的不同状态。

这样,它可以非常快速地将输入电压的信息转换为输出电压信号,并输出给后续电路进行处理。

CMOS电压比较器在数字电路和模拟电路中广泛应用,比如在模数转换器、自适应滤波器和通信系统中。

需要注意的是,本文所列出的是CMOS电压比较器的基本工作原理,实际的电路中可能还会包含其他的电路元件或功能模块,以实现更精确的比较和输出。

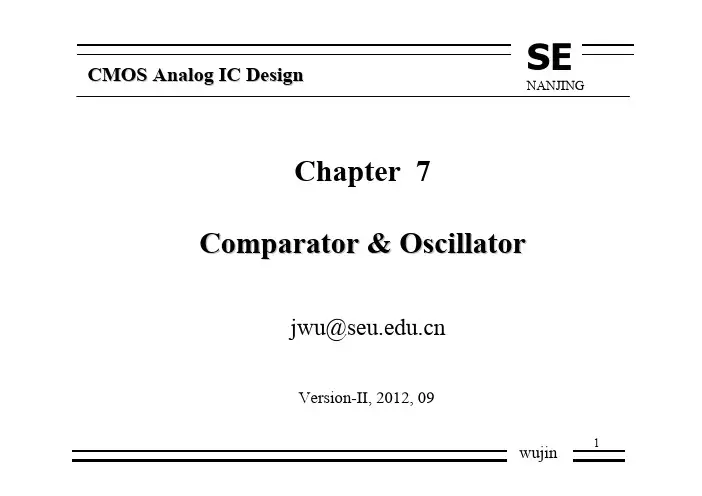

refV ⎪⎩⎪⎨⎧<>=in in V V ,0 ,1预放大判决驱动One stage buffer Two or more stage buffers The polarity of comparator is changed when one more INV used.wujinCross pair: M5/M8, Positive Feedback induced in DP load;Mainly to boost gain and small signal Speed.Fully symmetric & Differential OTA,N/P complimentary DPwujin-i gIf W/L of CP (M21,M23) large than that of MOS diode (M20,M22), Hysteric comparator is formed.wujinTo shift or switch reference based on comparator statutefor positive scanning, V applied first, when V+, switch to V for negative scanning, V applied first, when V, switch to VReference switch methodsexternal feedback control, analog mode & digital mode;internal feedback control, positive FB to introduce unsymmetrical.14wujin+V refNMOS switchPMOS switchBetterOutput as digital controlin configuring actual V refV DD /V ref ?; *i SPH V V +=+Modified CMOSHysterics comp should be firstly scaled down VDDwujin26302×=26302×==V B when V CC in to make I 2CC , V in and thus V A low, V B , V o , keep in CC , V A high, V , toggle.V A ?23wujinϕFor output upper level limitRecharge: initial staterecharge & evaluation mode.in +1ref −ΔωΔϕUnsymmetrical of each stage, C1/C2 charging-discharging carrier out alternately [separated by (N-1)/2=3 stage for each other], for setting frequency & duty cycle , VN-CS?RS Latch needed to hole the statue33wujinINV3ClkClkBis under constant current, a small35。

cmos电压迟滞比较器电路摘要:1.CMOS 电压迟滞比较器电路概述2.CMOS 电压迟滞比较器的工作原理3.CMOS 电压迟滞比较器的特点与应用正文:CMOS 电压迟滞比较器电路概述CMOS 电压迟滞比较器电路是一种基于互补金属氧化物半导体(CMOS)技术的电压比较器电路。

在数字电路和模拟电路设计中,电压比较器扮演着十分重要的角色,它能够将输入电压信号转换为二进制信号,即高电平或低电平,从而实现对电压信号的判断和处理。

CMOS 电压迟滞比较器电路因其低功耗、高噪声抑制能力和稳定性等优点,在现代电子系统中得到了广泛应用。

CMOS 电压迟滞比较器的工作原理CMOS 电压迟滞比较器电路主要由输入端、输出端和比较器核心部分组成。

输入端连接待比较的电压信号,输出端输出高电平或低电平信号。

比较器核心部分是电路的关键部分,通常由一对共源放大器和一对共射放大器组成,其中共源放大器用于正向电压信号的放大,共射放大器用于负向电压信号的放大。

CMOS 电压迟滞比较器的工作原理主要基于电压迟滞现象。

当输入电压信号的正值部分与负值部分相等时,输出端输出低电平信号;当输入电压信号的正值部分大于负值部分时,输出端输出高电平信号。

这种比较方式能有效降低电路的功耗,并提高电路的噪声抑制能力。

CMOS 电压迟滞比较器的特点与应用CMOS 电压迟滞比较器电路具有以下特点:1.低功耗:CMOS 技术本身具有较低的功耗特性,因此CMOS 电压迟滞比较器电路在低功耗应用场合具有优势。

2.高噪声抑制能力:CMOS 电压迟滞比较器电路具有较高的噪声抑制能力,能有效抑制电路中的噪声,提高电路的稳定性。

3.宽工作电压范围:CMOS 电压迟滞比较器电路具有较宽的工作电压范围,能够适应不同电压系统的应用需求。

4.响应速度快:CMOS 电压迟滞比较器电路具有较快的响应速度,能够满足高速信号处理的需求。

CMOS 电压迟滞比较器电路在实际应用中具有广泛的应用领域,如模拟信号处理、数字信号处理、通信系统、自动控制等领域。

cmos运算放大器和比较器的设计及应用CMOS运算放大器和比较器是集成电路中常见的两种功能模块,它们在电子设备中的应用非常广泛。

本文将介绍CMOS运算放大器和比较器的设计原理和应用。

我们先来了解一下CMOS运算放大器。

CMOS运算放大器是一种基于互补金属氧化物半导体(CMOS)技术的放大器,它采用了互补对称的MOS管结构,具有低功耗、高增益、高输入阻抗和良好的共模抑制能力等优点。

CMOS运算放大器通常由差分放大电路和输出级组成。

差分放大电路是CMOS运算放大器的核心部分,它由两个互补对称的差分对(Differential Pair)和负反馈电路组成。

差分放大电路的输入信号通过差分对进行放大,然后经过负反馈电路进行稳定和控制。

通过调整差分对的工作电流和电压偏置,可以实现不同的放大倍数和频率响应。

CMOS运算放大器的应用非常广泛,主要包括模拟信号放大、滤波器设计、电压比较器、ADC/DAC等。

在模拟信号放大方面,CMOS运算放大器可以用于音频放大器、视频放大器、传感器信号放大等。

在滤波器设计方面,CMOS运算放大器可以用于实现低通滤波器、高通滤波器、带通滤波器等。

在电压比较器方面,CMOS 运算放大器可以用于比较两个电压大小并输出高低电平信号。

在ADC/DAC方面,CMOS运算放大器可以用于模拟信号的采样和转换。

接下来,我们来了解一下CMOS比较器。

CMOS比较器是一种用于比较两个电压大小的电路,它的输出是一个数字信号,表示两个输入信号的大小关系。

CMOS比较器通常由差分放大电路和输出级组成。

差分放大电路是CMOS比较器的核心部分,它由两个互补对和负反馈电路组成。

差分放大电路的输入信号通过差分对进行放大,然后经过负反馈电路进行稳定和控制。

通过调整差分对的工作电流和电压偏置,可以实现不同的比较阈值和响应时间。

CMOS比较器的应用非常广泛,主要包括电压比较、模拟信号判别、开关控制等。

在电压比较方面,CMOS比较器可以用于比较两个电压的大小并输出高低电平信号。

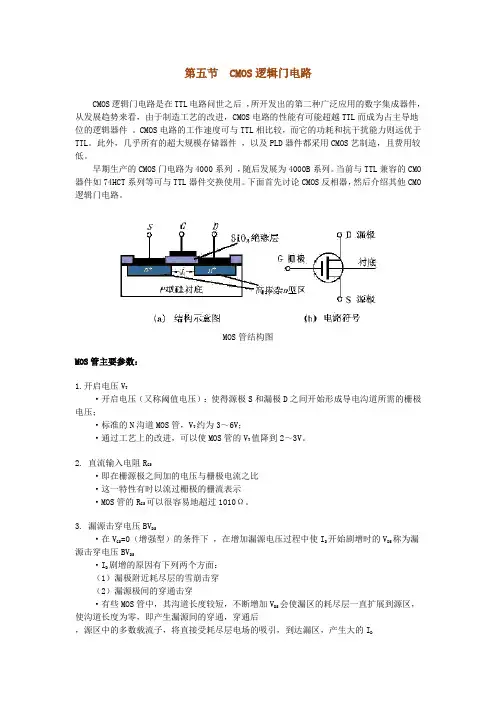

第五节CMOS逻辑门电路CMOS逻辑门电路是在TTL电路问世之后,所开发出的第二种广泛应用的数字集成器件,从发展趋势来看,由于制造工艺的改进,CMOS电路的性能有可能超越TTL而成为占主导地位的逻辑器件。

CMOS电路的工作速度可与TTL相比较,而它的功耗和抗干扰能力则远优于TTL。

此外,几乎所有的超大规模存储器件,以及PLD器件都采用CMOS艺制造,且费用较低。

早期生产的CMOS门电路为4000系列,随后发展为4000B系列。

当前与TTL兼容的CMO 器件如74HCT系列等可与TTL器件交换使用。

下面首先讨论CMOS反相器,然后介绍其他CMO 逻辑门电路。

MOS管结构图MOS管主要参数:1.开启电压V T·开启电压(又称阈值电压):使得源极S和漏极D之间开始形成导电沟道所需的栅极电压;·标准的N沟道MOS管,V T约为3~6V;·通过工艺上的改进,可以使MOS管的V T值降到2~3V。

2. 直流输入电阻R GS·即在栅源极之间加的电压与栅极电流之比·这一特性有时以流过栅极的栅流表示·MOS管的R GS可以很容易地超过1010Ω。

3. 漏源击穿电压BV DS·在V GS=0(增强型)的条件下,在增加漏源电压过程中使I D开始剧增时的V DS称为漏源击穿电压BV DS·I D剧增的原因有下列两个方面:(1)漏极附近耗尽层的雪崩击穿(2)漏源极间的穿通击穿·有些MOS管中,其沟道长度较短,不断增加V DS会使漏区的耗尽层一直扩展到源区,使沟道长度为零,即产生漏源间的穿通,穿通后,源区中的多数载流子,将直接受耗尽层电场的吸引,到达漏区,产生大的I D4. 栅源击穿电压BV GS·在增加栅源电压过程中,使栅极电流I G由零开始剧增时的V GS,称为栅源击穿电压BV GS。

5. 低频跨导g m·在V DS为某一固定数值的条件下,漏极电流的微变量和引起这个变化的栅源电压微变量之比称为跨导·g m反映了栅源电压对漏极电流的控制能力·是表征MOS管放大能力的一个重要参数·一般在十分之几至几mA/V的范围内6. 导通电阻R ON·导通电阻R ON说明了V DS对I D的影响,是漏极特性某一点切线的斜率的倒数·在饱和区,I D几乎不随V DS改变,R ON的数值很大,一般在几十千欧到几百千欧之间·由于在数字电路中,MOS管导通时经常工作在V DS=0的状态下,所以这时的导通电阻R ON可用原点的R ON来近似·对一般的MOS管而言,R ON的数值在几百欧以内7. 极间电容·三个电极之间都存在着极间电容:栅源电容C GS 、栅漏电容C GD和漏源电容CDS·C GS和C GD约为1~3pF·C DS约在0.1~1pF之间8. 低频噪声系数NF·噪声是由管子内部载流子运动的不规则性所引起的·由于它的存在,就使一个放大器即便在没有信号输人时,在输出端也出现不规则的电压或电流变化·噪声性能的大小通常用噪声系数NF来表示,它的单位为分贝(dB)·这个数值越小,代表管子所产生的噪声越小·低频噪声系数是在低频范围内测出的噪声系数·场效应管的噪声系数约为几个分贝,它比双极性三极管的要小一、CMOS反相器由本书模拟部分已知,MOSFET有P沟道和N沟道两种,每种中又有耗尽型和增强型两类。

如何看懂电路图(六)数字逻辑电路读图要点和举例数字逻辑电路的读图步骤和其它电路是相同的,只是在进行电路分析时处处要用逻辑分析的方法。

读图时要:①先大致了解电路的用途和性能。

②找出输入端、输出端和关键部件,区分开各种信号并弄清信号的流向。

③逐级分析输出与输入的逻辑关系,了解各部分的逻辑功能。

④最后统观全局得出分析结果。

例1三路抢答器图11是智力竞赛用的三路抢答器电路。

裁判按下开关SA4,触发器全部被置零,进入准备状态。

这时Q1~Q3均为1,抢答灯不亮;门1和门2输出为0,门3和门4组成的音频振荡器不振荡,扬声器无声。

竞赛开始,假定1号台抢先按下SA1,触发器C1翻转成Q1=1、Q1=0。

于是:①门2输出为1,振荡器振荡,扬声器发声;②HL1灯点亮;③门1输出为1,这时2号、3号台再按开关也不起作用。

裁判宣布竞赛结果后,再按一下SA4,电路又进入准备状态。

例2彩灯追逐电路图12是4位移位寄存器控制的彩灯电路。

开始时按下SA,触发器C1~C4被置成1000,彩灯HL1被点亮。

CP脉冲来到后,寄存器移1位,触发器C1~C4成0100,彩灯HL2点亮。

第2个CP脉冲点亮HL3,第3个点亮HL4,第4个CP又把触发器C1~C4置成1000,又点亮HL1。

如此循环往复,彩灯不停闪烁。

只要增加触发器可使灯数增加,改变CP的频率可变化速度。

555集成时基电路的特点555集成电路开始出现时是作定时器应用的,所以叫做555定时器或555时基电路。

但是后来经过开发,它除了作定时延时控制外,还可以用于调光、调温、调压、调速等多种控制以及计量检测等作用;还可以组成脉冲振荡、单稳、双稳和脉冲调制电路,作为交流信号源以及完成电源变换、频率变换、脉冲调制等用途。

由于它工作可靠、使用方便、价格低廉,因此目前被广泛用于各种小家电中。

555集成电路内部有几十个元器件,有分压器、比较器、触发器、输出管和放电管等,电路比较复杂,是模拟电路和数字电路的混合体。

refV ⎪⎩⎪⎨⎧<>=in in V V ,0 ,1预放大判决驱动One stage buffer Two or more stage buffers The polarity of comparator is changed when one more INV used.wujinCross pair: M5/M8, Positive Feedback induced in DP load;Mainly to boost gain and small signal Speed.Fully symmetric & Differential OTA,N/P complimentary DPwujin-i gIf W/L of CP (M21,M23) large than that of MOS diode (M20,M22), Hysteric comparator is formed.wujinTo shift or switch reference based on comparator statutefor positive scanning, V applied first, when V+, switch to V for negative scanning, V applied first, when V, switch to VReference switch methodsexternal feedback control, analog mode & digital mode;internal feedback control, positive FB to introduce unsymmetrical.14wujin+V refNMOS switchPMOS switchBetterOutput as digital controlin configuring actual V refV DD /V ref ?; *i SPH V V +=+Modified CMOSHysterics comp should be firstly scaled down VDDwujin26302×=26302×==V B when V CC in to make I 2CC , V in and thus V A low, V B , V o , keep in CC , V A high, V , toggle.V A ?23wujinϕFor output upper level limitRecharge: initial staterecharge & evaluation mode.in +1ref −ΔωΔϕUnsymmetrical of each stage, C1/C2 charging-discharging carrier out alternately [separated by (N-1)/2=3 stage for each other], for setting frequency & duty cycle , VN-CS?RS Latch needed to hole the statue33wujinINV3ClkClkBis under constant current, a small35。

cmos电压比较器工作原理# cmos电压比较器工作原理CMOS电压比较器是一种电子器件,用于比较两个输入电压,并将比较结果以高或低电平输出。

它在许多电路中都扮演着重要的角色,例如模拟电路中的开关、电源管理电路中的电压检测等。

## 工作原理CMOS电压比较器的核心是一个差分放大器,由一对PMOS和NMOS晶体管组成。

它们分别连接到一个共享的源极,并与两个输入电压相连。

一个输入电压通过一个电阻分压网络进入PMOS管,另一个输入电压经过一个反相器(由PMOS和NMOS管组成)并进入NMOS管。

输出电压则取决于输入电压之间的差异。

当两个输入电压相等时,差分放大器的输出电压为0V。

这是因为通过PMOS管和NMOS管流入源极的电流相等,它们的电压降也相等。

因此,在这种情况下,差分放大器的输出电压保持在低电平。

当一个输入电压高于另一个输入电压时,会产生一个差异电压。

这个差异电压将导致差分放大器的输出电压发生改变。

如果将高电平输出定义为逻辑“1”,那么输出将变为高电平。

类似地,如果一个输入电压低于另一个输入电压,差分放大器的输出电压将保持低电平。

因此,如果将低电平输出定义为逻辑“0”,那么输出将变为低电平。

## 电路结构CMOS电压比较器主要由差分放大器和输出电路组成。

除了差分对之外,输出电路通常也包含一个反相器,用于产生逻辑反向的输出信号。

差分对是CMOS电压比较器的关键部分,它由两个PMOS晶体管和两个NMOS晶体管组成。

这些晶体管按照特定的连接方式配置,以实现基本的比较功能。

输出电路通常由一个反相器组成,该反相器由一个PMOS晶体管和一个NMOS晶体管组成。

这个反相器将差分放大器的输出信号反向,产生与输入信号相反的逻辑电平。

## 总结CMOS电压比较器是一种常见的电子器件,用于比较两个输入电压并输出相应的电平。

它主要由差分放大器和输出电路组成,其中差分放大器负责比较输入电压的差异,并产生输出信号。

输出电路通常使用反相器来反向输出信号。

cmos电压比较器工作原理CMOS电压比较器是一种常用的集成电路,主要用于比较输入电压与参考电压的大小关系,并输出相应的比较结果。

其工作原理基于CMOS技术,具有低功耗、高速度和稳定性等优势,广泛应用于模拟信号处理、电源管理和数据转换等领域。

CMOS电压比较器通常由差动放大器、比较器和输出级组成。

差动放大器是CMOS电压比较器的核心部分,负责放大输入信号并将其转换为差分信号。

比较器则利用差分信号进行比较,判断输入电压与参考电压的大小关系。

输出级负责将比较结果转换为输出电压,以供后续电路使用。

在CMOS电压比较器中,差动放大器采用了差分对结构,由两个输入端和一个输出端组成。

输入端分别连接输入电压和参考电压,通过差动对的放大作用,将输入电压和参考电压进行放大。

差分对结构由两个晶体管组成,一个为p型晶体管,一个为n型晶体管。

p 型晶体管的栅极连接输入电压,n型晶体管的栅极连接参考电压。

当输入电压大于参考电压时,p型晶体管导通,n型晶体管截止,输出电压为高电平;当输入电压小于参考电压时,p型晶体管截止,n型晶体管导通,输出电压为低电平。

比较器部分采用了两个互补的MOS管作为开关,通过控制这两个开关的导通与截止,实现对输入电压和参考电压的比较。

当输入电压大于参考电压时,上管导通,下管截止,输出电压为高电平;当输入电压小于参考电压时,上管截止,下管导通,输出电压为低电平。

输出级通常由电平转换电路和输出缓冲器组成。

电平转换电路负责将比较器输出的高低电平转换为标准的数字信号,以供后续电路处理。

输出缓冲器则增强了输出电流的驱动能力,保证了比较结果的准确性和稳定性。

总结起来,CMOS电压比较器的工作原理是基于差动放大器和比较器的组合,通过对输入电压和参考电压进行差分放大和比较,实现对信号大小关系的判断,并输出相应的比较结果。

其优点在于低功耗、高速度和稳定性,使其成为广泛应用于模拟信号处理和数据转换等领域的重要集成电路。