430学习笔记

- 格式:doc

- 大小:187.50 KB

- 文档页数:52

IMX283学习笔记-10⽉更新我的EasyARM-i.MX283学习笔记1、前记 .......................................................................................................................... - 1 -初学第⼀阶段计划 (1)2、关于IMX283A开发板 ............................................................................................... - 3 -3、EASYARM-I.MX283学习-----5个⽉我学了什么? ....................................................... - 5 -关于接下来该学习什么,怎么学习做⼀个规划: (6)4、EASYARM-I.MX283学习之点亮LED灯....................................................................... - 6 -1、按照教程安装好ECLIPSE:参照10.4节的做法 (6)2、操作步骤 (6)1、前记对于ARM9没有什么基础,硬要说对ARM了解的话,我会STM32,也算对ARM半个⼊门了。

去年看到ZLG的IMX283开发套件时,那时很想买,但终究没买。

究其原因,当时正在学习STM32。

其实我作为硬件⼯程师(⾃诩),学习过很多单⽚机,例如51、MSP430、STM32,当然还有专业课上的FPGA当然,已有⼀年多没接触了。

这些芯⽚,可要说会也不是特别精通,可要说不会但毕竟也学过⼀段时间。

这⼀路过来,反正也是懵懵懂懂,图个新鲜感。

很多东西学过后就忘记了,现在呢就养成了写⼀些⾃学笔记的习惯。

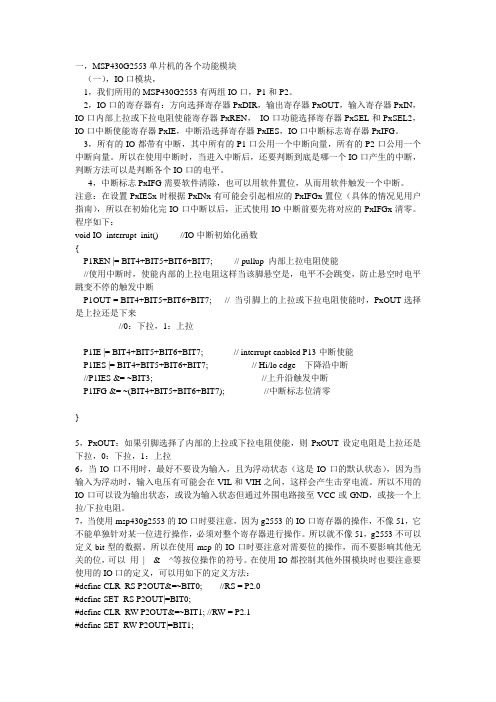

一,MSP430G2553单片机的各个功能模块(一),IO口模块,1,我们所用的MSP430G2553有两组IO口,P1和P2。

2,IO口的寄存器有:方向选择寄存器PxDIR,输出寄存器PxOUT,输入寄存器PxIN,IO口内部上拉或下拉电阻使能寄存器PxREN,IO口功能选择寄存器PxSEL和PxSEL2,IO口中断使能寄存器PxIE,中断沿选择寄存器PxIES,IO口中断标志寄存器PxIFG。

3,所有的IO都带有中断,其中所有的P1口公用一个中断向量,所有的P2口公用一个中断向量。

所以在使用中断时,当进入中断后,还要判断到底是哪一个IO口产生的中断,判断方法可以是判断各个IO口的电平。

4,中断标志PxIFG需要软件清除,也可以用软件置位,从而用软件触发一个中断。

注意:在设置PxIESx时根据PxINx有可能会引起相应的PxIFGx置位(具体的情况见用户指南),所以在初始化完IO口中断以后,正式使用IO中断前要先将对应的PxIFGx清零。

程序如下:void IO_interrupt_init() //IO中断初始化函数{P1REN |= BIT4+BIT5+BIT6+BIT7; // pullup 内部上拉电阻使能//使用中断时,使能内部的上拉电阻这样当该脚悬空是,电平不会跳变,防止悬空时电平跳变不停的触发中断P1OUT = BIT4+BIT5+BIT6+BIT7; // 当引脚上的上拉或下拉电阻使能时,PxOUT选择是上拉还是下来//0:下拉,1:上拉P1IE |= BIT4+BIT5+BIT6+BIT7; // interrupt enabled P13中断使能P1IES |= BIT4+BIT5+BIT6+BIT7; // Hi/lo edge 下降沿中断//P1IES &= ~BIT3; //上升沿触发中断P1IFG &= ~(BIT4+BIT5+BIT6+BIT7); //中断标志位清零}5,PxOUT:如果引脚选择了内部的上拉或下拉电阻使能,则PxOUT设定电阻是上拉还是下拉,0:下拉,1:上拉6,当IO口不用时,最好不要设为输入,且为浮动状态(这是IO口的默认状态),因为当输入为浮动时,输入电压有可能会在VIL和VIH之间,这样会产生击穿电流。

MSP430G2553学习笔记(数据手册)MSP430G2553性能参数(DIP-20) 工作电压范围:1.8~3.6V。

5种低功耗模式。

16位的RISC结构,62.5ns指令周期。

超低功耗:运行模式-230µA;待机模式-0.5µA;关闭模式-0.1µA;可以在不到1µs的时间里超快速地从待机模式唤醒。

基本时钟模块配置:具有四种校准频率并高达16MHz的内部频率;内部超低功耗LF振荡器;32.768KHz晶体;外部数字时钟源。

两个16 位Timer_A,分别具有三个捕获/比较寄存器。

用于模拟信号比较功能或者斜率模数(A/D)转换的片载比较器。

带内部基准、采样与保持以及自动扫描功能的10位200-ksps 模数(A/D)转换器。

16KB闪存,512B的RAM。

16个I/O口。

注意:MSP430G2553无P3口!MSP430G2553的时钟基本时钟系统的寄存器DCOCTL-DCO控制寄存器DCOxDCO频率选择控制1MODxDCO频率校正选择,通常令MODx=0注意:在MSP430G2553上电复位后,默认RSEL=7,DCO=3,通过数据手册查得DCO频率大概在0.8~1.5MHz之间。

BCSCTL1-基本时钟控制寄存器1XT2OFF不用管,因为MSP430G2553内部没有XT2提供的HF时钟XTS不用管,默认复位后的0值即可DIV Ax设置ACLK的分频数00 /101 /210 /411 /8RSELxDCO频率选择控制2BCSCTL2-基本时钟控制寄存器2SELMxMCLK的选择控制位00 DCOCLK01 DCOCLK10 LFXT1CLK或者VLOCLK11 LFXT1CLK或者VLOCLK DIVMx设置MCLK的分频数00 /101 /210 /411 /8SELSSMCLK的选择控制位0 DCOCLK1 LFXT1CLK或者VLOCLK DIVSx设置SMCLK的分频数00 /101 /210 /411 /8DCORDCO直流发生电阻选择,此位一般设00 内部电阻1 外部电阻BCSCTL3-基本时钟控制寄存器3XT2Sx不用管LFXT1Sx00 LFXT1选为32.768KHz晶振01 保留10 VLOCLK11 外部数字时钟源XCAPxLFXT1晶振谐振电容选择00 1pF01 6pF10 10pF11 12.5pFmsp430g2553.h中基本时钟系统的内容/************************************************************* Basic Clock Module************************************************************/#define __MSP430_HAS_BC2__ /* Definition to show that Module is available */SFR_8BIT(DCOCTL); /* DCO Clock Frequency Control */SFR_8BIT(BCSCTL1); /* Basic Clock System Control 1 */SFR_8BIT(BCSCTL2); /* Basic Clock System Control 2 */SFR_8BIT(BCSCTL3); /* Basic Clock System Control 3 */#define MOD0 (0x01) /* Modulation Bit 0 */#define MOD1 (0x02) /* Modulation Bit 1 */#define MOD2 (0x04) /* Modulation Bit 2 */#define MOD3 (0x08) /* Modulation Bit 3 */#define MOD4 (0x10) /* Modulation Bit 4 */#define DCO0 (0x20) /* DCO Select Bit 0 */#define DCO1 (0x40) /* DCO Select Bit 1 */#define DCO2 (0x80) /* DCO Select Bit 2 */#define RSEL0 (0x01) /* Range Select Bit 0 */#define RSEL1 (0x02) /* Range Select Bit 1 */#define RSEL2 (0x04) /* Range Select Bit 2 */#define RSEL3 (0x08) /* Range Select Bit 3 */#define DIVA0 (0x10) /* ACLK Divider 0 */#define DIVA1 (0x20) /* ACLK Divider 1 */#define XTS (0x40) /* LFXTCLK 0:Low Freq. / 1: High Freq. */ #define XT2OFF (0x80) /* Enable XT2CLK */#define DIVA_0 (0x00) /* ACLK Divider 0: /1 */#define DIVA_1 (0x10) /* ACLK Divider 1: /2 */#define DIVA_2 (0x20) /* ACLK Divider 2: /4 */#define DIVA_3 (0x30) /* ACLK Divider 3: /8 */#define DIVS0 (0x02) /* SMCLK Divider 0 */#define DIVS1 (0x04) /* SMCLK Divider 1 */#define SELS (0x08) /* SMCLK Source Select 0:DCOCLK /1:XT2CLK/LFXTCLK */#define DIVM0 (0x10) /* MCLK Divider 0 */#define DIVM1 (0x20) /* MCLK Divider 1 */#define SELM0 (0x40) /* MCLK Source Select 0 */#define SELM1 (0x80) /* MCLK Source Select 1 */#define DIVS_0 (0x00) /* SMCLK Divider 0: /1 */#define DIVS_1 (0x02) /* SMCLK Divider 1: /2 */#define DIVS_2 (0x04) /* SMCLK Divider 2: /4 */#define DIVS_3 (0x06) /* SMCLK Divider 3: /8 */#define DIVM_0 (0x00) /* MCLK Divider 0: /1 */#define DIVM_1 (0x10) /* MCLK Divider 1: /2 */#define DIVM_2 (0x20) /* MCLK Divider 2: /4 */#define DIVM_3 (0x30) /* MCLK Divider 3: /8 */#define SELM_0 (0x00) /* MCLK Source Select 0: DCOCLK */#define SELM_1 (0x40) /* MCLK Source Select 1: DCOCLK */#define SELM_2 (0x80) /* MCLK Source Select 2: XT2CLK/LFXTCLK */#define SELM_3 (0xC0) /* MCLK Source Select 3: LFXTCLK */#define LFXT1OF (0x01) /* Low/high Frequency Oscillator Fault Flag */#define XT2OF (0x02) /* High frequency oscillator 2 fault flag */#define XCAP0 (0x04) /* XIN/XOUT Cap 0 */#define XCAP1 (0x08) /* XIN/XOUT Cap 1 */#define LFXT1S0 (0x10) /* Mode 0 for LFXT1 (XTS = 0) */#define LFXT1S1 (0x20) /* Mode 1 for LFXT1 (XTS = 0) */#define XT2S0 (0x40) /* Mode 0 for XT2 */#define XT2S1 (0x80) /* Mode 1 for XT2 */#define XCAP_0 (0x00) /* XIN/XOUT Cap : 0 pF */#define XCAP_1 (0x04) /* XIN/XOUT Cap : 6 pF */#define XCAP_2 (0x08) /* XIN/XOUT Cap : 10 pF */#define XCAP_3 (0x0C) /* XIN/XOUT Cap : 12.5 pF */#define LFXT1S_0 (0x00) /* Mode 0 for LFXT1 : Normal operation */ #define LFXT1S_1 (0x10) /* Mode 1 for LFXT1 : Reserved */#define LFXT1S_2 (0x20) /* Mode 2 for LFXT1 : VLO */#define LFXT1S_3 (0x30) /* Mode 3 for LFXT1 : Digital input signal */#define XT2S_0 (0x00) /* Mode 0 for XT2 : 0.4 - 1 MHz */#define XT2S_1 (0x40) /* Mode 1 for XT2 : 1 - 4 MHz */#define XT2S_2 (0x80) /* Mode 2 for XT2 : 2 - 16 MHz */#define XT2S_3 (0xC0) /* Mode 3 for XT2 : Digital input signal */基本时钟系统例程(DCO)MSP430G2553在上电之后默认CPU执行程序的时钟MCLK来自于DCO时钟。

高中的月考反思随笔(经典版)编制人:__________________审核人:__________________审批人:__________________编制单位:__________________编制时间:____年____月____日序言下载提示:该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!并且,本店铺为大家提供各种类型的经典范文,如工作报告、工作计划、方案大全、教学教案、随笔大全、总结范文、短美文、诗词歌赋、教学资料、其他范文等等,想了解不同范文格式和写法,敬请关注!Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you!Moreover, our store provides various types of classic sample essays for everyone, such as work reports, work plans, comprehensive plans, teaching plans, essays, summary essays, short and beautiful essays, poetry and poetry, teaching materials, and other sample essays. If you want to learn about different formats and writing methods of sample essays, please stay tuned!高中的月考反思随笔高中的月考是对一个月以来学习的情况及学习方法、学习状态的总结,目地并不在于比较、排名,更重要在于总结这一个多月的学习情况。

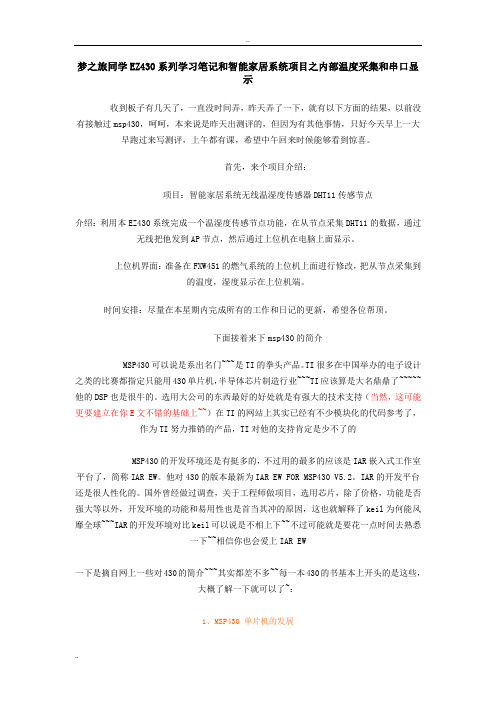

梦之旅同学EZ430系列学习笔记和智能家居系统项目之内部温度采集和串口显示收到板子有几天了,一直没时间弄,昨天弄了一下,就有以下方面的结果,以前没有接触过msp430,呵呵,本来说是昨天出测评的,但因为有其他事情,只好今天早上一大早跑过来写测评,上午都有课,希望中午回来时候能够看到惊喜。

首先,来个项目介绍:项目:智能家居系统无线温湿度传感器DHT11传感节点介绍:利用本EZ430系统完成一个温湿度传感节点功能,在从节点采集DHT11的数据,通过无线把他发到AP节点,然后通过上位机在电脑上面显示。

上位机界面:准备在FXW451的燃气系统的上位机上面进行修改,把从节点采集到的温度,湿度显示在上位机端。

时间安排:尽量在本星期内完成所有的工作和日记的更新,希望各位帮顶。

下面接着来下msp430的简介MSP430可以说是系出名门~~~是TI的拳头产品。

TI很多在中国举办的电子设计之类的比赛都指定只能用430单片机,半导体芯片制造行业~~~TI应该算是大名鼎鼎了~~~~~他的DSP也是很牛的。

选用大公司的东西最好的好处就是有强大的技术支持(当然,这可能更要建立在你E文不错的基础上~~)在TI的网站上其实已经有不少模块化的代码参考了,作为TI努力推销的产品,TI对他的支持肯定是少不了的MSP430的开发环境还是有挺多的,不过用的最多的应该是IAR嵌入式工作室平台了,简称IAR EW。

他对430的版本最新为IAR EW FOR MSP430 V5.2。

IAR的开发平台还是很人性化的。

国外曾经做过调查,关于工程师做项目,选用芯片,除了价格,功能是否强大等以外,开发环境的功能和易用性也是首当其冲的原因,这也就解释了keil为何能风靡全球~~~IAR的开发环境对比keil可以说是不相上下~~不过可能就是要花一点时间去熟悉一下~~相信你也会爱上IAR EW一下是摘自网上一些对430的简介~~~其实都差不多~~每一本430的书基本上开头的是这些,大概了解一下就可以了~:1、MSP430 单片机的发展MSP430 系列是一个 16 位的、具有精简指令集的、超低功耗的混合型单片机,在 1996 年问世,由于它具有极低的功耗、丰富的片内外设和方便灵活的开发手段,已成为众多单片机系列中一颗耀眼的新星。

会计工作读书笔记纸上得来终觉浅,绝知此事要躬行。

下面是小编精心为您整理的会计工作,希望您喜欢!会计工作读书笔记篇一很庆幸能有一个机会到实习,我清楚地知道能有这次实习是非常不容易的。

虽然只有三天,但我也会充分利用好。

对会计有点了解的人就会想三天这么短能学到什么啊,但我却觉得可以的,这三天里能让你学到对基本业务的处理,对会计的核算过程有个总体的概念框架,大概了解做全盘帐时所包括的环节。

以下是我三天里具体的实习情况:第一天,主要是练习写数字金额和中文大写和看公司以前的凭证和账簿。

书本上对会计的金额数字作了严格的要求,单单写得清晰是不够的,还必须书写规范,做到不容易被更改。

写数字和中文大写虽然看似简单,但也要细心认真,不要小看。

练习好数字后就开始看看别人是怎样填写会计凭证、粘贴原始凭证和登记账簿的。

这些虽然在学校的模拟课上都有做过,但跟真实的记账是有不同之处的,有些科目和处理程序是不同的,这些是可以灵活处理,体现会计原则的相关性。

看懂了那些记账凭证后就自己尝试对账,因为发生的费用比较多,所以我认真地算了几遍,算出来心里就踏实了,明白到原来是这回事。

第二天,主要对账——记账凭证和科目汇总表之间的核对、科目汇总表和各种账簿之间的核对。

一开始核对时觉得有点懵,不太懂数据的来龙去脉。

后来静下心来,耐心地看了几遍,不懂的就请教会计、或,用心地把账都对上了。

为了保证准确性,我细心地核对了几遍,才把它真正弄懂了。

第三天,主要是学习一些会计的知识点和如何编制报表。

跟会计的聊天中认识到把书本上了理论知识真正地灵活地运用到实际工作中是很重要的,学好会计需要漫长的时间,且要“三心(耐心、细心、专心)一意”。

而且更正了一直的错误认识:做会计的不是有经验就不用什么职称了。

正如郑会计所说:没有理论知识,如何能指导实践!最后学习如何编制报表,本来以为会很复杂,听了平姐简单的解说,再慢慢地认真看了几遍那些报表,发觉不是很难,知道了那些数据是如何得出。

优秀的数学家在定理或理论之间看到了类似,卓越的数学家则从类似中间看到了类似——Banach(巴拿赫)毋庸置疑,Lefschetz(莱夫谢茨)和Wiener(维纳)都是这种可以从相似之间看到相似的数学家。

不过他们的讲课技巧实在是不能让人恭维。

Rota(罗塔)曾讲了一个Lefschetz的故事,关于他的课是如何难懂,因为他经常语无伦次。

这是几何课的开场白:“一个Riemann(黎曼)曲面是一定形式的Hausdroff(豪斯多夫)空间。

你们知道Hausdroff空间是什么吧?它也是紧的,好了。

我猜想它也是一个流形。

你们当然知道流形是什么。

现在让我给你们讲一个不那么平凡的定理——Riemann-Roch(罗赫)定理。

”要知道第一节Riemann 曲面的课如果这样进行的话,恐怕Riemann复生也未必可以听懂。

Wiener尽管是个天才,却是那种不善于讲课的那种,总是以为把真正深刻的数学讲出来一定要写一大堆积分符号。

有一个关于他和中文的事情,Wiener 天真的认为自己懂一种汉语,一次在中国餐馆,他终于有了施展的机会,但是服务员却根本不知道他讲的是汉语。

最后,Wiener不得不评论:“他必须离开这里,他不会说北京话。

”……百思论坛数学与物理/forum-430-1.html数学分支的细化与深入:本科阶段:连续与离散的关系?无穷与有限的关系?一个闭形式何时才是恰当形式?在同伦于点的区域(单连通区域)有Poicare引理之逆告诉我们这个自动成立。

在非单连通区域有著名的deRham定理告诉我们如何成立,那就是微分形式在所有闭链上的积分为零。

代数拓扑学中研究与连续映射的连续形变有关的各种课题是同伦论(homotopy theory),庞加莱已经提出了基本群的概念,后来切赫和胡雷维奇先后提出同伦群的观念。

空间X的n维同伦群是n维球面Sn到空间X的连续映射按同伦关系进行分类而得的同伦类集合(?用到了连续映射同伦的概念)20世纪20年代德国数学家霍普夫(Huopufu,1894.11.19-1971.6.3)探讨了球面同伦理论。

业余无线电操作证题库部分试题及学习笔记(v170418)【本文以中国无线电协会无线电分会发布的业余无线电台操作证书B类考试题库(电子版文本v170418)为蓝本,结合自己的体会,对于较难的题目,加入了一些题目中涉及到的相关概念、公式、计算方法、理解和助记方式等,希望对参加A、B考试的朋友有所帮助。

】卷面题数:50涉及题数:694[I]LK0116【Q】业余电台的无线电发射设备应符国家规定的下列主要技术指标:【A】符合频率容限、符合杂散发射最大允许功率电平[B]杂散发射不低于最大允许功率电平、电源电压及频率符合国家电网标准、采用标准天线阻抗[C]杂散发射不低于最大允许功率电平、频率漂移不低于频率容限、电源利用效率满足节能要求[D]工作频率范围足够宽、杂散发射不低于最大允许功率电平、带宽大于允许最低值[I]LK0117【Q】频率容限是发射设备的重要指标,通常用下述单位来表示:【A】百万分之几(或者赫兹)[B]dB[C]瓦[D]百分之几(或者兆赫)[I]LK0118【Q】杂散域发射功率是发射设备的重要指标,通常用下述单位来表示:【A】绝对功率dBm、低于载波发射功率的分贝值dBc、低于PEP发射功率的相对值dB[B]绝对功率(瓦)[C]百分之几[D]千赫(或者赫芝)[I]LK0137【Q】杂散发射是指必要带宽之外的一个或多个频率的发射,其发射电平可降低而不致影响相应信息的传输。

一台发射机,工作频率为145.000MHz,但在435.000MHz的频率上也有发射。

这种发射属于:【A】杂散发射[B]带外发射[C]谐波发射[D]带内发射【杂散发射是在必要带宽外某个或某些频率上的发射,其发射电平可降低但不影响相应信息传递。

包括:谐波发射、寄生发射、互调产物、以及变频产物,但带外发射除外。

一般来说,落在中心频率两侧,必要带宽±250%倍处或以外的发射都认为是杂散发射。

】[I]LK0113【Q】在无线电管理中,由国家将某个特定的频带列入频率划分表,规定该频带可在指定的条件下供业余业余业务或者卫星业余业务使用,这个过程称为:【A】划分[I]LK0114【Q】在无线电管理中,将无线电频率或频道规定由一个或多个部门,在指定的区域内供地面或空间无线电通信业务在指定条件下使用,这个过程称为:【A】分配 [I]LK0115【Q】在无线电管理中,将无线电频率或频道批准给具体的业余无线电台在规定条件下使用,这个过程称为:【A】指配[I]LK0140【Q】在频率划分表中,一个频带被标明划分给多种业务时,这些业务被分为下述类别:【A】主要业务和次要业务[I]LK0141【Q】在频率划分表中,当一个频段划分给业余业务或卫星业余业务和多个其他业务,并且业余业务和卫星业余业务作为次要业务时,业余无线电台应该遵循的规则是:【A】不得对主要业务电台产生有害干扰有害干扰[I]LK0142【Q】在频率划分表中,当一个频段划分给业余业务或卫星业余业务和多个其他业务,并且业余业务和卫星业余业务作为次要业务时,业余无线电台遵循的规则是:【A】不得对来自主要业务电台的有害干扰提出保护要求[I]LK0143【Q】在频率划分表中,当一个频段划分给业余业务或卫星业余业务和多个其他业务,并且业余业务和卫星业余业务作为次要业务时,业余无线电台遵循的规则是:【A】可要求保护不受来自同一业务或其他次要业务电台的有害干扰[I]LK0119【Q】必要带宽(necessary bandwidth)是指:对给定的发射类别而言,其恰好足以保证在相应速率及在指定条件下具有所要求质量的信息传输的所需带宽。

第一集中华道路主要讲述中国古代思想发展历程及中华民族走向统一的过程,中心思想是探索中华道路中儒家思想的引领作用及各民族集大统的客观规律。

知识点:1. 百家争鸣:法家墨子兼爱非攻,儒家孔子亚圣荀子王阳明阳明,心法、仁爱、尊卑有序,道家老子庄子无为;2. 儒学完善历程:儒学、刘邦建立汉王朝孔子祭祀标志儒学登入上流,汉武帝儒学,罢黜百家,独尊儒学,阳明心法,新旧儒学,明朝反腐;3. 民族统一历程:北魏改汉、大唐长安文化自信、海陆丝绸之路、吉尔吉斯斯坦乡愁。

第二集中华起源:主要讲述中华民族祖先进化过程,中心思想是中华民族是自中华大地产生并延绵不断发展起来的民族。

知识点:1. 猿人至古人至智人至现代人,主要变化为脑容量的增大、下颚的凸起、眉骨的凸起等。

第三集农业起源主要讲述中华民族如何开始种植及生产粮食的过程,纯叙述无思想。

知识点:1. 南方稻谷驯化为野生稻至生产稻,北方狗尾巴草与谷子驯化为谷子,直至明朝一直为第一大生产作物。

狗尾巴草为莠,良莠不齐的典故来源。

第四集文明起源主要讲述各个文化作用圈的形成及互通过程,为讲述邦国的形成奠定基础,纯叙述无思想。

知识点:1. 红山文化、牛河梁文化等(史前五千年左右)第五集邦城时代主要讲述各邦国即初始国家的兴衰过程,为讲述第一个广域王权国家夏朝奠定基础,纯叙述无思想。

知识点:1. 史前四千年左右三大集团有华夏、三苗、武夷,发现的遗址有陶寺(文尧的遗址)、陶寺因外族入侵与内斗而衰。

万邦万国呈繁星点点直至夏朝出现而向月明星稀转变;中国一词源于陶寺,表示中城之都、中土之国;上古时代的龙山时代,又称三皇五帝时代,五帝一般认为黄帝、颛顼、帝喾、尧、舜。

第六集夏朝觅踪主要讲述考古学界寻找夏朝存在的过程,中心思想夏朝客观存在而非神话。

知识点:1. 夏朝第一个奴隶制国家,大约在公元前2020年至1600年,存续约四百八十年,十七名帝皇更替;2. 大禹是夏朝第一位帝王,大禹之子启取代益成王,改尧舜禹的禅让制变世袭制,太康失国,后羿代夏,寒浞代后羿,少康中兴复兴夏朝,暴君夏桀是最后一位夏朝帝皇,商汤取代夏桀建立商;3. 河南洛阳二里头遗址(夏朝中晚期),河南嵩山新砦遗址(启至太康),河南郑州王城岗遗址(疑是大禹阳都待证);4. 商朝甲骨文是最早文字,夏出土的陶器上刻符疑是文字待证,可能是更古老的文字,最古老的文献资料商朝《尚书》、司马迁《史记.夏本纪》均有夏朝记载,证实夏朝存在,但因当时未出现文字,夏朝史料少之又少,考古是探源的主要途径。

一,MSP430G2553单片机的各个功能模块(一),IO口模块,1,我们所用的MSP430G2553有两组IO口,P1和P2。

2,IO口的寄存器有:方向选择寄存器PxDIR,输出寄存器PxOUT,输入寄存器PxIN,IO口内部上拉或下拉电阻使能寄存器PxREN,IO口功能选择寄存器PxSEL和PxSEL2,IO口中断使能寄存器PxIE,中断沿选择寄存器PxIES,IO口中断标志寄存器PxIFG。

3,所有的IO都带有中断,其中所有的P1口公用一个中断向量,所有的P2口公用一个中断向量。

所以在使用中断时,当进入中断后,还要判断到底是哪一个IO口产生的中断,判断方法可以是判断各个IO口的电平。

4,中断标志PxIFG需要软件清除,也可以用软件置位,从而用软件触发一个中断。

注意:在设置PxIESx时根据PxINx有可能会引起相应的PxIFGx置位(具体的情况见用户指南),所以在初始化完IO口中断以后,正式使用IO中断前要先将对应的PxIFGx清零。

程序如下:void IO_interrupt_init() //IO中断初始化函数{P1REN |= BIT4+BIT5+BIT6+BIT7; // pullup 内部上拉电阻使能//使用中断时,使能内部的上拉电阻这样当该脚悬空是,电平不会跳变,防止悬空时电平跳变不停的触发中断P1OUT = BIT4+BIT5+BIT6+BIT7; // 当引脚上的上拉或下拉电阻使能时,PxOUT选择是上拉还是下来//0:下拉,1:上拉P1IE |= BIT4+BIT5+BIT6+BIT7; // interrupt enabled P13中断使能P1IES |= BIT4+BIT5+BIT6+BIT7; // Hi/lo edge 下降沿中断//P1IES &= ~BIT3; //上升沿触发中断P1IFG &= ~(BIT4+BIT5+BIT6+BIT7); //中断标志位清零}5,PxOUT:如果引脚选择了内部的上拉或下拉电阻使能,则PxOUT设定电阻是上拉还是下拉,0:下拉,1:上拉6,当IO口不用时,最好不要设为输入,且为浮动状态(这是IO口的默认状态),因为当输入为浮动时,输入电压有可能会在VIL和VIH之间,这样会产生击穿电流。

所以不用的IO口可以设为输出状态,或设为输入状态但通过外围电路接至VCC或GND,或接一个上拉/下拉电阻。

7,当使用msp430g2553的IO口时要注意,因为g2553的IO口寄存器的操作,不像51,它不能单独针对某一位进行操作,必须对整个寄存器进行操作。

所以就不像51,g2553不可以定义bit型的数据。

所以在使用msp的IO口时要注意对需要位的操作,而不要影响其他无关的位,可以用| & ^等按位操作的符号。

在使用IO口控制其他外围模块时也要注意要使用的IO口的定义,可以用如下的定义方法:#define CLR_RS P2OUT&=~BIT0; //RS = P2.0#define SET_RS P2OUT|=BIT0;#define CLR_RW P2OUT&=~BIT1; //RW = P2.1#define SET_RW P2OUT|=BIT1;#define CLR_EN P2OUT&=~BIT2; //EN = P2.2#define SET_EN P2OUT|=BIT2;#define DataPort P1OUT8,g2553的P27和P26脚分别接外部晶体的输出和输入脚XOUT和XIN,默认是自动设为了晶振管脚功能,但是当想把它们用为普通的IO时,也可以,设置对应的SEL设为普通的IO即可,如下:P2DIR |= BIT6+BIT7; //把P26和P27配置为普通IO 并为输出脚默认为晶振的输入和输出引脚作为dac0832的P2SEL &= ~(BIT6+BIT7); //cs和wr控制端P2SEL2 &= ~(BIT6+BIT7);(二),时钟系统1,msp430能做到超低功耗,合理的时钟模块是功不可没的。

但是功能强大的时钟模块设置起来也相对复杂一些。

2,msp430的时钟源有:(1),外接低频晶振LFXT1CLK:低频模式接手表晶体32768Hz,高频模式450KHz~8MHz;(2),外接高速晶振XT2CLK:8MHz;(3),内部数字控制振荡器DCO:是一个可控的RC振荡器,频率在0~16MHz;(4),超低功耗低频振荡器VLO:不可控,4~20KHz 典型值为12KHz;3,时钟模块:430的时钟模块有MCLK SMCLK ACLK :(1),主系统时钟MCLK:提供给MSP430的CPU时钟。

可以来自LFXT1CLK XT2CLK DCO VLO可选,默认为DCO。

(2),子系统时钟SMCLK: 提供给高速外设。

可以来自LFXT1CLK XT2CLK DCO VLO 可选,默认为DCO。

(3),辅助系统时钟ACLK:提供给低速外设。

可来自LFXT1CLK VLO。

4,内部的振荡器DCO和VLO提供的时钟频率不是很精确,随外部环境变化较大。

DCO默认的频率大概为800KHz,但我用示波器观察的为1.086MHz左右,当DCO设置的过高时,用示波器可以看到波形不再是方波,而是类似于正弦波。

DCO可以用CCS提供的宏定义进行相对比较精确的设置,如下:DCOCTL = CALDCO_12MHZ; //DCO设为12MHz 这种方法设DCO频率比较精确,实际测得为12.08MHz左右正弦波BCSCTL1 = CALBC1_12MHZ;用这种方法可以设置1,8,12,16MHz宏定义如下:#ifndef __DisableCalDataSFR_8BIT(CALDCO_16MHZ);SFR_8BIT(CALBC1_16MHZ);SFR_8BIT(CALDCO_12MHZ);SFR_8BIT(CALBC1_12MHZ);SFR_8BIT(CALDCO_8MHZ);SFR_8BIT(CALBC1_8MHZ);SFR_8BIT(CALDCO_1MHZ);SFR_8BIT(CALBC1_1MHZ);#endif5,使用超低功耗低频振荡器VLO可以很大程度地降低系统功耗,下面的例子是设置ACLK 为VLO,MCLK为VLO的8分频:#include <msp430g2553.h>//1延时//#define CPU_F ((double)16000000)//cpu frequency16000000#define CPU_F ((double)1630)//cpu frequency1630 //CPU的实际MCLK大约为13.05/8=1.63KHz#define delay_us(x) __delay_cycles((long)(CPU_F*(double)x/1000000.0))#define delay_ms(x) __delay_cycles((long)(CPU_F*(double)x/1000.0))void main(void){volatile unsigned int i; // V olatile to prevent removalWDTCTL = WDTPW + WDTHOLD; // Stop watchdog timerBCSCTL3 |= LFXT1S_2; // LFXT1 = VLO 低频时钟选择为VLO ACLK选为VLOIFG1 &= ~OFIFG; // Clear OSCFault flag 清除振荡器错误中断标志__bis_SR_register(SCG1 + SCG0); // Stop DCO SCG1禁止SMCLK SCG0禁止DCOBCSCTL2 |= SELM_3 + DIVM_3; // MCLK = LFXT1/8//因为前面已经选择了LFXT1 = VLO 所以MCLK选为VLO 8分频所以CPU的MCLK 大约为1.5KHzP1DIR = 0xFF; // All P1.x outputsP1OUT = 0; // All P1.x resetP2DIR = 0xFF; // All P2.x outputsP2OUT = 0; // All P2.x resetP1SEL |= BIT0+BIT4; // P1.0 P1.4options 功能选择为外围模块//p1.0输出ACLK,来自VLO,p1.4输出SMCLK,因为禁止了SMCLK,所以P1.4脚无波形输出//VLO典型值为12KHz 实际用示波器测得为:13.05KHz 左右波动//所以CPU的实际MCLK大约为13.05/8=1.63KHzfor (;;){P1OUT ^= BIT6; // P1.6 闪烁delay_ms(1000);}}6,如上面的程序所示,其中的延迟函数用那种方法,使用系统的延迟周期函数__delay_cycles(int n); 可以达到比较精确的延迟,如下://more_//1延时//#define CPU_F ((double)16000000)//cpu frequency16000000#define CPU_F ((double)12000000)//cpu frequency12000000#define delay_us(x) __delay_cycles((long)(CPU_F*(double)x/1000000.0))#define delay_ms(x) __delay_cycles((long)(CPU_F*(double)x/1000.0))//2空函数#define nop() _NOP();7,系统上电后默认使用的是DCO时钟,DCO默认的频率大概为800KHz,但我用示波器观察的为1.086MHz左右,当DCO设置的过高时,用示波器可以看到波形不再是方波,而是类似于正弦波。

(三),定时器Timer_A1,MSP430g2553具有两个16位的定时器:Timer0_A Timer1_A。

分别具有三个捕捉/比较寄存器,具有输入捕捉,输出比较功能。

可以产生定时中断,也可以产生PWM。

2,产生PWM,例子如下:#include <msp430g2553.h>void Timer_A0_1_init() //TA0.1输出PWM{TACTL|= TASSEL_1+MC_1;//ACLK,增计数CCTL1=OUTMOD_7;//输出模式为复位/置位CCR0=328;//时钟频率为32768HZ,100HZ//CCR1=164;//时钟频率为32768HZ,占空比CCR1/CCR0=50%CCR1=109;//占空比CCR1/CCR0=1/3 TA0.1由P1.2 P1.6输出}void Timer_A1_2_init() //TA1.2输出PWM{TA1CTL|= TASSEL_1+MC_1;//ACLK,增计数TA1CCTL2=OUTMOD_7;//输出模式为复位/置位,注意CCTL2要写为TA1CCTL2TA1CCR0=164;//时钟频率为32768HZ,波形32768/CCR0=199HZTA1CCR2=41;//占空比CCR2/CCR0=1/4,注意CCR2要写成TA1CCR2 TA1.2由P2.4 P2.5输出}void Timer_A1_1_init() //TA1.1输出PWM{TA1CCTL1=OUTMOD_7;TA1CCR1=123; //占空比CCR1/CCR0=3/4,注意CCR1要写成TA1CCR1 TA1.1由P2.1 P2.2输出}void IO_init(){P1SEL|=BIT2+BIT6;P1DIR|=BIT2+BIT6;//P1.2 P1.6输出TA0.1 OUT1P2SEL|=BIT4+BIT5;P2DIR|=BIT4+BIT5;//P2.4 P2.5输出TA1.2 OUT2P2SEL|=BIT1+BIT2;P2DIR|=BIT1+BIT2; //P2.1 P2.2输出TA1.1 OUT1}void main(void) {WDTCTL=WDTPW+WDTHOLD;IO_init();Timer_A0_1_init();Timer_A1_2_init();Timer_A1_1_init();_BIS_SR(CPUOFF); // Enter LPM0 进入低功耗模式0SMCLK ON,ACLK ON}3,Timer_A的捕获/比较寄存器TAR寄存器是Timer_A的16位的计数寄存器。