第三章 地址译码技术及存储器接口

- 格式:ppt

- 大小:1.64 MB

- 文档页数:74

第3章I/O端口地址译码技术作业1、什么是I/O端口在一个接口电路中一般拥有几种端口2、I/O端口是I/O接口电路中能被CPU直接访问的寄存器。

在一个接口电路中一般拥有:命令端口、状态端口和数据端口。

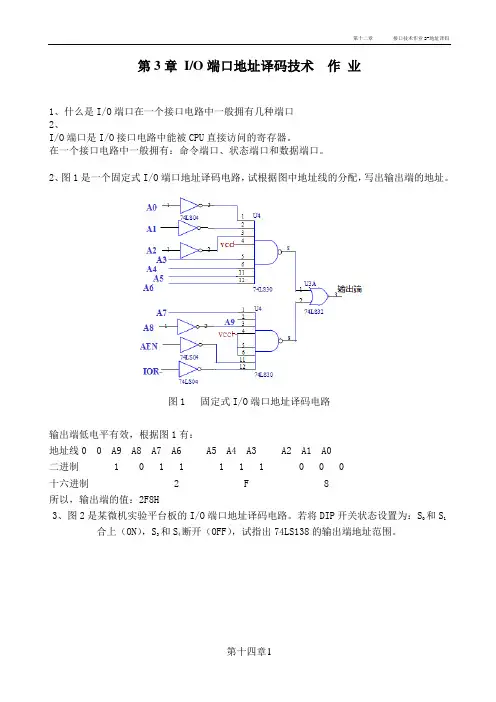

2、图1是一个固定式I/O端口地址译码电路,试根据图中地址线的分配,写出输出端的地址。

图1 固定式I/O端口地址译码电路输出端低电平有效,根据图1有:地址线0 0 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0二进制 1 0 1 1 1 1 1 0 0 0十六进制 2 F 8所以,输出端的值:2F8H3、图2是某微机实验平台板的I/O端口地址译码电路。

若将DIP开关状态设置为:S0和S1合上(ON),S3和S4断开(OFF),试指出74LS138的输出端地址范围。

图2 使用比较器的可选式译码电路从图2中可以看出,当S0断开时,其值为1(高电平),A6必须为0,对应的异或门输出才会是1,;同样,当S1合上时,其值为0(高电平),A7必须为1,对应的异或门输出才会是1;类推,S2合上,S3断开时,A8,A9必须为1,0。

即当S2和S1合上,S3和S0断开时,译码电路输入地址线的值地址线0 0 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0二进制 0 1 1 0 片选片内端口寻址十六进制 0~7H 0~7H所以,CS0地址为:180H~187H共8个端口地址。

CS1地址为:188H~18FH共8个端口地址。

CS2地址为:190H~197H共8个端口地址。

CS3地址为:198H~19FH共8个端口地址。

CS4地址为:1A0H~1A7H共8个端口地址。

CS5地址为:1A8H~1AFH共8个端口地址。

CS6地址为:1B0H~1B7H共8个端口地址。

CS7地址为:1B8H~1BFH共8个端口地址。

存储器是用来存放数据的集成电路或介质,常见的存储器有半导体存储器(ROM 、RAM )、光存储器(如CD 、VCD 、MO 、MD 、DVD )、磁介质存储器(如磁带、磁盘、硬盘)等。

存储器是计算机极为重要的组成部分,有了它计算机才具有存储信息的功能,组成部分,有了它计算机才具有存储信息的功能,使计算机可以脱离人使计算机可以脱离人的控制自动工作。

的控制自动工作。

单片机系统中主要使用的存储器是半导体存储器,从单片机系统中主要使用的存储器是半导体存储器,从使用功能上,可分为随机存取存储器(RAM )和只读存储器(ROM )两类。

RAM 主要用于存放各种现场数据、中间计算结果,以及主机与外设交换信息等,它的存储单元的内容既可读出,又可写入。

ROM 中存储的信息只能读出,不能写入,如PC 机主板上的存放BIOS 程序的芯片就是ROM 存储器。

2.3.1 RAM 存储器RAM 存储器是指断电时信息会丢失的存储器,但是这种存储器可以现场快速地修改信息,所以RAM 存储器是可读写存储器,一般都作为数据存储器使用,用来存放现场输入的数据或者存放可以更改的运行程序和数据。

根据其工作原理不同,可分为以下两类:基于触发器原理的静态读写存储器(SRAM ,Static RAM )和基于分布电容电荷存储原理的动态读写存储器(DRAM ,Dynamic RAM )。

一般SRAM 用于仅需要小于64KB 数据存储器的小系统或作为大系统中高速缓冲存储器;而DRAM 常用于需要大于64KB 的大系统,这样刷新电路的附加成本会被大容量的DRAM低功耗、低成本等利益所补偿。

SRAM的基本结构如图所示。

RAM的结构大体由三部分组成:地址译码器,存储矩阵,输入/输出电路。

SRAM的基本结构1. 地址译码方式地址译码有两种方式,一种是单译码方式,或称为字结构方式;另一种是双译码方式,或称为X-Y译码结构。

1)单译码方式16字×4位的存储器共有64个存储单元,排列成16行×4列的矩4阵,每个小方块表示一个存储单元。

存储器的地址译码方式及其适用场合是些什么?(1)一维地址译码(或称为线选法),这种方法用于小容量的存储器芯片,(2)二维地址译码(即重合法),这种方法用于大容量的存储器芯片,存储器的扩展及地址线的位数是什么意思?(1)位扩展:当存储器的容量要求与芯片的容量相同,但位数不同,就需要进行位方向上扩展。

(2)字扩展:当存储器的位数与芯片的相同,但是容量不足时,就需要在字方向上扩展。

(3)字位同时扩展:是指在内存容量和数据位长宽两个方向上同时扩展。

当需要组成的内存容量为M,字长为N时,若已有芯片为m×n,所需芯片数=(M∕m)×(N∕n)(4)地址线位数:如果存储器的容量=2N,那么N就是整个存储器地址线的位数如果芯片的容量=2n,那么n就是每个芯片地址线的位数RAS、CAS信号有什么用?请画一个原理图并说明它们是如何产生的?RAS和CAS是提供给外部RAM的行地址和列地址的选通信号。

图见课本。

8086CPU在组织系统时,为什么要把存储器分为奇和偶两个体?如何实现这种控制?由此推想,对32位CPU应该有几个控制信号,才能保证单字节,双字节和一个双字寻址都能进行的要求?8086的数据总线16位,但1个内存单元中存放的数是8位,为了一次对2个单元进行访问,要把存储器分为奇和偶两个体。

每个内存单元都一个地址,要访问2个单元时,从偶存储器开始,可用一个控制信号来选择。

那么,对32为CPU 应该有4个控制信号,才能保证单字,双字节和一个双字寻址都能进行的要求。

用存储器件组成内存时,为什么总是采用矩阵形式?请用一个具体例子说明。

简化选择内存单元的译码电路,通过行选择线和列选择线来确定一个内存单元,因而用存储器组成内存时,总是采用矩阵形式。

比如,要组成1K字节的内容,如果不用矩阵来组织这些单元,而是将它们一字排开,那么就要1024条译码线才能实现对这些单元的寻址。

如果用32*32的矩阵来实现排列,那么,就只要32条行选择线和32条列选择线就可以了。