4 之 1

基本原理

本方法只适用于采用基于总线互连结构 的系统中,由于系统中每个处理机都能觉察 到存储器系统正在进行的活动,在某个活动 破坏了Cache的一致性时, Cache控制器 将采取相应的动作使有关的拷贝无效或更新。

《Computer Architecture》V3

幻灯片 19/75

同济大学.电子与信息工程学院.计算机科学与工程系

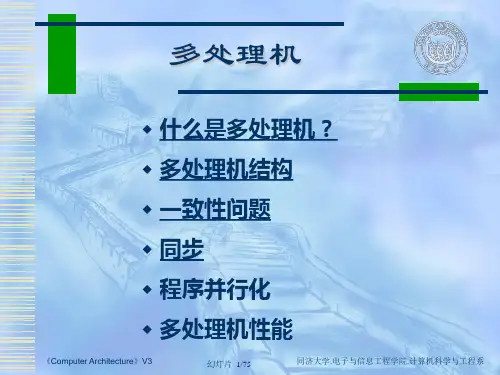

利用多任务处理可以提高处理速度,利

用系统的重组能力可以提高可靠性。

《Computer Architecture》V3 幻灯片 2/75 同济大学.电子与信息工程学院.计算机科学与工程系

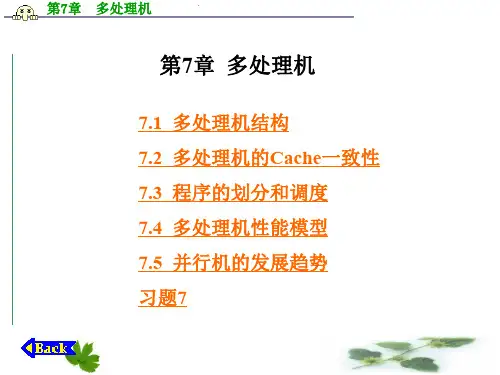

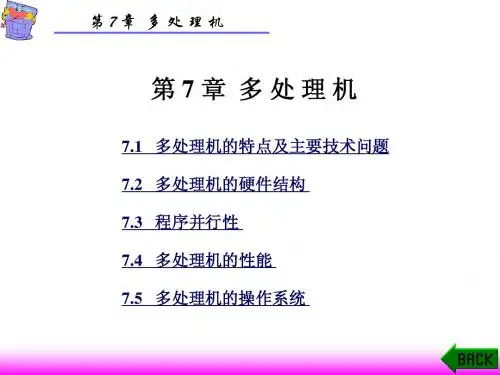

本章内容

2 之 2

提 示

因为多处理机系统结构是一个巨大而多

样的领域,其中很多领域仍处于不成熟的阶

段,所以本课程集中于多处理机设计的主流

《Computer Architecture》V3

幻灯片 13/75

同济大学.电子与信息工程学院.计算机科学与工程系

本章内容>>一致性问题>>Cache一致性>>原因分析

共享可写数据引起的 不一致性

不同处理器对相同单元在各自Cache的拷贝 的异步写操作。

处理机

Cache 共享存 储器 P1 P2 P1 P2 P1 P2

《Computer Architecture》V3 幻灯片 23/75 同济大学.电子与信息工程学院.计算机科学与工程系

本章内容>>一致性问题>>Cache一致性>>解决方法>>监听协议

2 之 1

采用写回策略的

Cache

WL RL,WL 读写 RR WL WR 无效 WR RL 只读 RL,RR