MM74HC595MTC中文资料

- 格式:pdf

- 大小:96.64 KB

- 文档页数:10

74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态.三态。

特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换 Remote control holding register。

描述 595是告诉的硅结构的CMOS器件, 兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

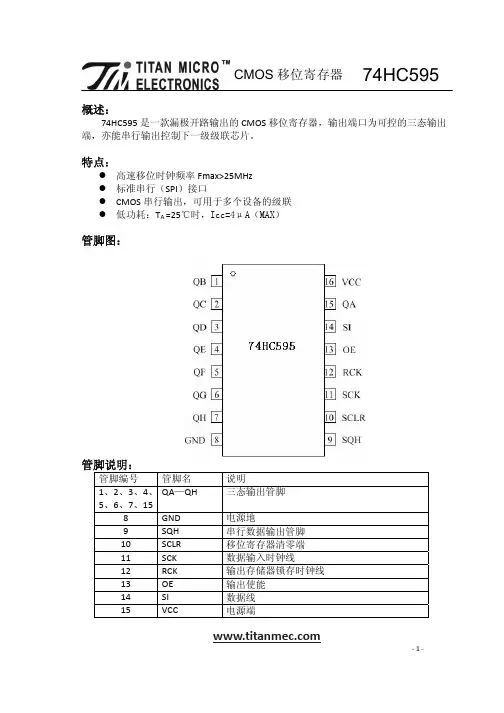

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f 0=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解 595的工作情况74HC595引脚图,管脚图________QB-—|1 16|——VccQC—-|2 15|--QAQD——|3 14|--SIQE—-|4 13|—-/GQF—-|5 12|--RCKQG--|6 11|—-SRCKQH-—|7 10|—-/SRCLRGND- |8 9|-—QH'|________|74595的数据端:QA—-QH: 八位并行输出端,可以直接控制数码管的8个段。

QH':级联输出端。

我将它接下一个595的SI端。

8位串行输入/输出或者并行输出移位寄存器,具有高阻关断状态。

三态。

特点

8位串行输入

8位串行或并行输出

存储状态寄存器,三种状态

输出寄存器可以直接清除

100MHz的移位频率

输出能力

并行输出,总线驱动

串行输出;标准

中等规模集成电路

应用

串行到并行的数据转换

Remote control holding register.

描述

595是告诉的硅结构的CMOS器件,

兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存

储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

参考数据

C PD决定动态的能耗,

P D=C PD×V CC×f1+∑(C L×V CC2×f0)

F1=输入频率,C L=输出电容f0=输出频率(MHz)Vcc=电源电压

引脚说明

功能表

H=高电平状态L=低电平状态↑=上升沿

↓=下降沿

Z=高阻

NC=无变化

×=无效

当MR为高电平,OE为低电平时,数据在SH CP上升沿进入移位寄存器,在ST CP上升沿输出到并行端口。

74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换 Remote control holding register. 描述 595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能O E时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解 595的工作情况74HC595引脚图,管脚图________QB--|1 16|--VccQC--|2 15|--QAQD--|3 14|--SIQE--|4 13|--/GQF--|5 12|--RCKQG--|6 11|--SRCKQH--|7 10|--/SRCLRGND- |8 9|--QH'|________|74595的数据端:QA--QH: 八位并行输出端,可以直接控制数码管的8个段。

QH': 级联输出端。

我将它接下一个595的SI端。

74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换 Remote contr ol holding register. 描述 595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp 的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解 595的工作情况引脚功能表:管脚编号管脚名管脚定义功能1、2、3、4、5、6、7、15QA—QH 三态输出管脚8 GND 电源地9 SQH 串行数据输出管脚10 SCLR 移位寄存器清零端11 SCK 数据输入时钟线12 RCK 输出存储器锁存时钟线13 OE 输出使能14 SI 数据线15 VCC 电源端真值表:输入管脚输出管脚SI SCK SCLR RCK OEX X X X H QA—QH 输出高阻X X X X L QA—QH 输出有效值X X L X X 移位寄存器清零L 上沿H X X 移位寄存器存储LH 上沿H X X 移位寄存器存储HX 下沿H X X 移位寄存器状态保持X X X 上沿X 输出存储器锁存移位寄存器中的状态值X X X 下沿X 输出存储器状态保持74595的数据端:QA--QH: 八位并行输出端,可以直接控制数码管的8个段。

74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换 Remote contr ol holding register. 描述 595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp 的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解 595的工作情况引脚功能表:管脚编号管脚名管脚定义功能1、2、3、4、5、6、7、15QA—QH 三态输出管脚8 GND 电源地9 SQH 串行数据输出管脚10 SCLR 移位寄存器清零端11 SCK 数据输入时钟线12 RCK 输出存储器锁存时钟线13 OE 输出使能14 SI 数据线15 VCC 电源端真值表:输入管脚输出管脚SI SCK SCLR RCK OEX X X X H QA—QH 输出高阻X X X X L QA—QH 输出有效值X X L X X 移位寄存器清零L 上沿H X X 移位寄存器存储LH 上沿H X X 移位寄存器存储HX 下沿H X X 移位寄存器状态保持X X X 上沿X 输出存储器锁存移位寄存器中的状态值X X X 下沿X 输出存储器状态保持74595的数据端:QA--QH: 八位并行输出端,可以直接控制数码管的8个段。

74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换 Remote contr ol holding register. 描述 595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp 的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解 595的工作情况引脚功能表:真值表:74595的控制端说明:/SRCLR(10脚): 低点平时将移位寄存器的数据清零。

通常我将它接Vcc。

SRCK(11脚):上升沿时数据寄存器的数据移位。

QA-->QB-->QC-->...-->QH;下降沿移位寄存器数据不变。

(脉冲宽度:5V时,大于几十纳秒就行了。

我通常都选微秒级)RCK(12脚):上升沿时移位寄存器的数据进入数据存储寄存器,下降沿时存储寄存器数据不变。

(通常我将RCK置为低电平,) 当移位结束后,在RCK端产生一个正脉冲(5V时,大于几十纳秒就行了。

![[整理]74HC595完整中文资料](https://uimg.taocdn.com/68a06277227916888486d7e2.webp)

74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换 Remote contr ol holding register. 描述 595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp 的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解 595的工作情况引脚功能表:管脚编号管脚名 管脚定义功能1、2、3、4、5、6、7、15 QA —QH三态输出管脚8GND电源地9 SQH串行数据输出管脚10SCLR移位寄存器清零端11SCK 数据输入时钟线12 RCK输出存储器锁存时钟线 13OE 输出使能14 SI 数据线 15VCC电源端真值表:输入管脚输出管脚SI SCK SCLR RCKOEX X X X H QA —QH 输出高阻 X X X X L QA —QH 输出有效值 X X L X X 移位寄存器清零 L 上沿 H X X 移位寄存器存储L H 上沿 H X X 移位寄存器存储H X 下沿 H X X 移位寄存器状态保持X X X 上沿 X 输出存储器锁存移位寄存器中的状态值XXX下沿X输出存储器状态保持74595的数据端:QA--QH: 八位并行输出端,可以直接控制数码管的8个段。

74HC595芯片中文资料

8位串行输入/输出或者并行输出移位寄存器,具有高阻关断状态。

三态。

特点

8位串行输入

8位串行或并行输出

存储状态寄存器,三种状态

输出寄存器可以直接清除

100MHz的移位频率

输出能力

并行输出,总线驱动

串行输出;标准

中等规模集成电路

应用

串行到并行的数据转换

Remote control holding register.

描述

595是告诉的硅结构的CMOS器件,

兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

参考数据

C PD决定动态的能耗,

P D=C PD×V CC×f1+∑(C L×V CC2×f0)

F1=输入频率,C L=输出电容f0=输出频率(MHz)Vcc=电源电压

引脚说明

功能表

H=高电平状态

L=低电平状态

↑=上升沿

↓=下降沿

Z=高阻

NC=无变化

×=无效

当MR为高电平,OE为低电平时,数据在SH CP上升沿进入移位寄存器,在ST CP上升沿输出到并行端口。

74HC595的中文资料

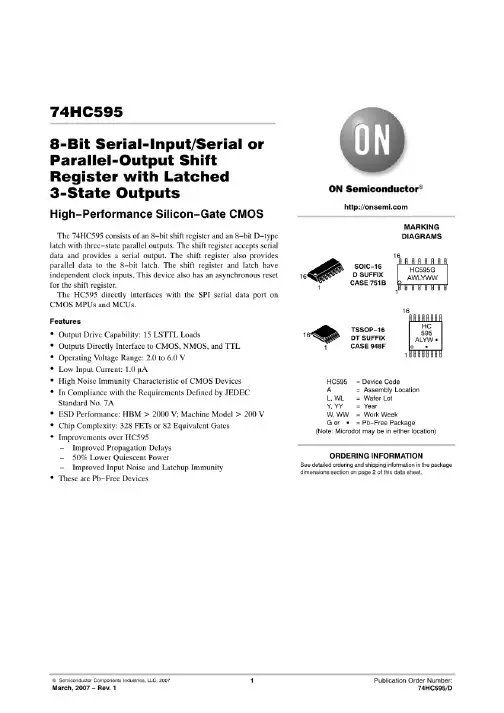

74HC595——具有三态输出锁存功能的8位串行输入、串行/并行输出移位寄存器(本文翻译自NXP的74HC595的datasheet)

74HC595和74HCT595是带有存储寄存器和三态输出的8位串行移位寄存器,移位寄存器和存储寄存器有各自的时钟。

每当移位寄存器输入时钟SHCP上升沿来临之时,数据被移出。

每当存储寄存器输入时钟STCP上升沿来临之时,数据并行的存储到存储寄存器。

如果两个时钟上升沿同时到来,移位寄存器总是要比存储寄存器的提前一个时钟。

移位寄存器有一个串行出入(DS)和一个串行标准输出(Q7S)。

同时也提供一个异步复位端(低电平有效),存储寄存器有一个8位3态总线输出。

输出使能(OE)为低电平时,存储寄存器的值就输出。

下面是一个功能框图,有利于理解:

接着是一个逻辑符号:

功能表如下:

时序图:

在SH CP上升沿进入移位寄存器,在ST CP上升沿输出到并行端口。

74HC595完整中文资料74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有咼阻、关、断状态。

三态。

特点8位串行输入8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换Remote c ontrol holding register. 描述595是告诉的硅结构的CMO器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp勺上升沿输入,在S Tcp 的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7 ),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能0E时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗,PD= CPD< VCC< f1 + 刀(CL X VCC2< f0) F 1=输入频率,。

1=输出电容f0 =输出频率(MHZ Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解595的工作情况功能表:真值表:74595的数据端:QA--QH:八位并行输出端,可以直接控制数码管的8个段。

QH':级联输出端。

我将它接下一个595的SI端。

SI:串行数据输入端。

74595的控制端说明:/SRCLR(10脚):低点平时将移位寄存器的数据清零。

通常我将它接Vcc。

SRCK(11脚):上升沿时数据寄存器的数据移位。

QA-->QB-->QC-->…-->QH ;下降沿移位寄存器数据不变。

(脉冲宽度:5V时,大于几十纳秒就行了。

74HC595芯片资料

8位串行输入/输出或者并行输出移位寄存器,具有高阻关断状态。

三态。

特点

8位串行输入

8位串行或并行输出

存储状态寄存器,三种状态

输出寄存器可以直接清除

100MHz的移位频率

输出能力

并行输出,总线驱动

串行输出;标准

中等规模集成电路

应用

串行到并行的数据转换

Remote control holding register.

描述

595是告诉的硅结构的CMOS器件,

兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q 7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

参考数据

C PD决定动态的能耗,

P D=C PD×V CC×f1+∑(C L×V CC2×f0)

F1=输入频率,C L=输出电容f0=输出频率(MHz)Vcc=电源电压

引脚说明

功能表

H=高电平状态

L=低电平状态↑=上升沿

↓=下降沿

Z=高阻

NC=无变化

×=无效。

74HC595 的中文资料

74HC595 具有三态输出锁存功能的8 位串行输入、串行/并行输出移位寄存器

本文翻译自NXP 的74HC595 的datasheet

74HC595 和74HCT595 是带有存储寄存器和三态输出的8 位串行移位寄存器,移位寄存器和存储寄存器有各自的时钟。

每当移位寄存器输入时钟SHCP 上升沿来临之时,数据被移出。

每当存储寄存器输入时钟STCP 上升沿来临之时,数据并行的存储到存储寄存器。

如果两个时钟上升沿同时到来,移位寄存器总是要比存储寄存器的提前一个时钟。

移位寄存器有一个串行出入(DS)和一个串行标准输出(Q7S)。

同时也提供一个异步复位端(低电平有效),存储寄存器有一个8 位3 态总线输出。

输出使能(OE)为低电平时,存储寄存器的值就输出。

下面是一个功能框图,有利于理解:

接着是一个逻辑符号:。

74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出;595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解 595的工作情况74HC595引脚图,管脚图________QB--|1 16|--VccQC--|2 15|--QAQD--|3 14|--SIQE--|4 13|--/GQF--|5 12|--RCKQG--|6 11|--SRCKQH--|7 10|--/SRCLRGND- |8 9|--QH'|________|74595的数据端:QA--QH: 八位并行输出端,可以直接控制数码管的8个段。

QH': 级联输出端。

我将它接下一个595的SI端。

SI: 串行数据输入端。

74595的控制端说明:/SRCLR(10脚): 低点平时将移位寄存器的数据清零。

通常我将它接Vcc。

SRCK(11脚):上升沿时数据寄存器的数据移位。

QA-->QB-->QC-->...-->QH;下降沿移位寄存器数据不变。