3.DSP的数值运算基础介绍

- 格式:pdf

- 大小:1.06 MB

- 文档页数:71

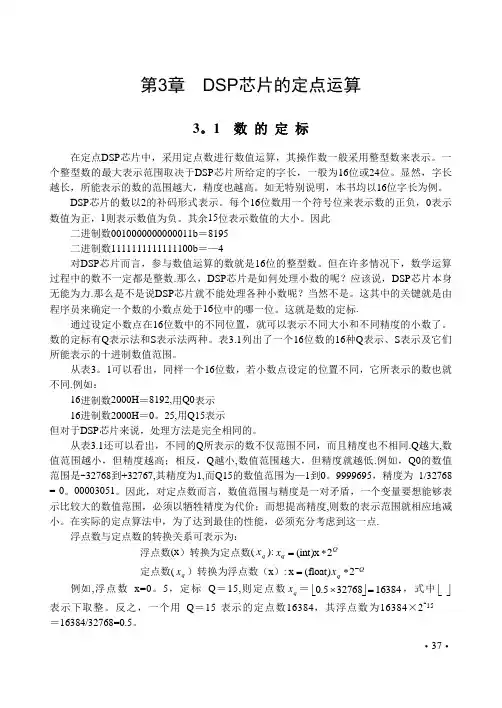

第3章 DSP 芯片的定点运算3。

1 数 的 定 标在定点DSP 芯片中,采用定点数进行数值运算,其操作数一般采用整型数来表示。

一个整型数的最大表示范围取决于DSP 芯片所给定的字长,一般为16位或24位。

显然,字长越长,所能表示的数的范围越大,精度也越高。

如无特别说明,本书均以16位字长为例。

DSP 芯片的数以2的补码形式表示。

每个16位数用一个符号位来表示数的正负,0表示数值为正,1则表示数值为负。

其余15位表示数值的大小。

因此二进制数0010000000000011b =8195 二进制数1111111111111100b =—4对DSP 芯片而言,参与数值运算的数就是16位的整型数。

但在许多情况下,数学运算过程中的数不一定都是整数.那么,DSP 芯片是如何处理小数的呢?应该说,DSP 芯片本身无能为力.那么是不是说DSP 芯片就不能处理各种小数呢?当然不是。

这其中的关键就是由程序员来确定一个数的小数点处于16位中的哪一位。

这就是数的定标.通过设定小数点在16位数中的不同位置,就可以表示不同大小和不同精度的小数了。

数的定标有Q 表示法和S 表示法两种。

表3.1列出了一个16位数的16种Q 表示、S 表示及它们所能表示的十进制数值范围。

从表3。

1可以看出,同样一个16位数,若小数点设定的位置不同,它所表示的数也就不同.例如:16进制数2000H =8192,用Q0表示 16进制数2000H =0。

25,用Q15表示但对于DSP 芯片来说,处理方法是完全相同的。

从表3.1还可以看出,不同的Q 所表示的数不仅范围不同,而且精度也不相同.Q 越大,数值范围越小,但精度越高;相反,Q 越小,数值范围越大,但精度就越低.例如,Q0的数值范围是-32768到+32767,其精度为1,而Q15的数值范围为—1到0。

9999695,精度为 1/32768 = 0。

00003051。

因此,对定点数而言,数值范围与精度是一对矛盾,一个变量要想能够表示比较大的数值范围,必须以牺牲精度为代价;而想提高精度,则数的表示范围就相应地减小。

实验一 CCS 的使用及DSP 基本数学运算一、实验目的1、熟悉CCS 集成开发环境,掌握工程的生成方法;2、熟悉SEED-DEC2407 实验环境;3、掌握CCS 集成开发环境的调试方法;4、了解数在DSP 中的基本计算过程。

二、实验原理TI 公司为TMS320系统的集成与调试所提供的工具包括:标准评估模块Evaluation Module (EVM )、扩展开发系统eXtenfed Development System (即硬仿真器,如XDS510)、集成开发环境Code Composer Stdio(CCS )。

标准评估模块(EVM )是TI 或TI 的第三方为TMS320 DSP 的使用者设计生产的一种评价DSP 的硬件平台,其外观和布局结构如图1.1。

扩展开发系统(XDS )是功能强大的全速仿真器,用以系统级的集成与调试。

PC 机与XDS 及EVM 板的连接方式如图1.2。

图1.1 标准评估模块(EVM )外观及布局图1.2 DSP 开发调试环境硬件连接示意图发布的Code Composer Studio开放型集成DSP 开发环境(IDE )功能强大、直观、易用。

具有编程、编译、链接、在线调试等功能。

CCS2.0开发调试软件的主界面如图1.3。

图1.3 CCS2.0开发调试软件的主界面DSP 的中央处理单元CPU 是内部总线上的核心模块,负责完成数据处理的任务。

即取数,逻辑运算,送回数据。

由三部分组成:输入比例部分(定标器)、中央算术逻辑部分(CALU )、乘法器。

TMS320LF240x 系列CPU 模块的内部功能结构如图1.4。

图1.4 CPU 模块的内部功能结构TMS320LF240x 系列DSP 有2个16位的状态寄存器ST0和ST1,含有状态位和控制位。

ST0和ST1可以被保存到数据存储器(SST )或从数据存储器中加载(LST ),从而可以保存和恢复子程序的机器状态(现场保护)。

第一.二章1 DSP芯片的结构特点?答:(1)改进的哈弗结构 1,哈弗结构 DSP处理器将程序代码和数据的存储空间分开,各有自己的地址总线和数据总线。

(目的是为了同时取指令和取操作数,并进行指令和数据的处理,从而大大提高运算速度) 2.,改进的哈弗结构在改进的哈弗结构的基础上,使得程序的代码和数据的存储空间之间也可以进行数据的传送。

(2)多总线结构多总线结构可以保证在一个机器周期内多次访程序和数据的空间。

TMS320C54X内有P,C,D,E4条总线。

P:传送取自ROM的指令代码和立即数;C,D:传送从RAM读出的操作数;E:传送写入到RAM中的数据。

(3)流水线技术将指令的各个部分驻重叠起来执行,而不是一条指令执行完之后,才开始执行下一条指令。

第一条指令去指后,在译码时,第二条指令就取值,第一条指令取数时,第二条指令译码,而第三条指令就考试取值。

(4)多处理单元(5)特殊的DSP指令(6)指令周期短功能强(7)运算精度高(8)丰富的外设(9)功耗低DSP最重要的特点是:特殊的内部结构,强大的信息处理能力及较高的运行速度。

2DSP分为两种:1,定点DSP,数据采用定点方式表示,正数表示是方法和小数表示方法。

2.浮点DSP,数据既可以表示成整数,也可以表示成浮点数。

3 DSP芯片可以归纳为三大系列:(1)TMS320C2000系列:适用于控制领域TMS320P2407(2)TMS320C5000 系列:应用与通信领域TMS320C54X(3)TMS320C6000系列:应用于图像处理TMS320C60X区别:三者CPU内部结构相同,片内存储器,外设电路配置不同。

4:TMS320C54X的内部结构:(1)CPU 包括算术逻辑运算单元,乘法器,累加器,移位寄存器,各种专门用途的寄存器,地址生成器及内部总线。

1,先进的总线结构(1条程序总线,3条数据总线和4条地址总线)2,位算术逻辑运算单元,包括1个40位桶形移位寄存器和2个独立的40位累加器3,17×17位并行乘法器,与40为专用加法器相连,用于非流水线是单周期乘法/ 累加运算(4)比较,选择,存储空间:用于加法/比较选择(5)指数编码器:可以在单个周期内计算40位累加器中数值的指数(6)双地址生成器:包括8位辅助寄存器和2个辅助寄存器算术运算单元(2)存储器系统包括片内的程序ROM,片内单访问的数据RAM和双访问的数据RAM,外接存储器接口。

结合信号处理算法的特点,说明DSP是一种特别适合于进行数字信号处理运算的微处理器?答:根据数字信号处理算法的特点,对芯片内部结构进行了特定的优化;它主要应用是实时地实现各种数字信号处理算法。

其中滤波运算的特点是大量的乘加运算;频繁的访问存储器;FFT运算的特点是碟形运算,码位倒置以及大量的乘加、减运算,其中样本按码位倒置的顺序排列,DSP处理器应具有对应的寻址方式,否则读取样本将花费大量的时间频繁的访问存储器,读取系数和样本,保存结果。

大多数信号处理算法都是由滤波、变换、卷积和相关等一些基本的运算构成;很多信号处理任务都要求在限定的时间内完成,即是信号处理的实时性要求。

DSP的特点:1. 高效的内部总线;2. 灵活的寻址方式;3. 单周期乘累加运算;4. 指令流水线;5. 硬件循环;6. 超标量操作等。

2)简述处理器的基本组成,并指出冯〃诺依曼结构和哈佛结构的区别。

处理器的基本组成:中央处理器(CPU)、内部总线结构、功能寄存器、数据存储器、程序存储器、I/O口、串行口、中断系统、定时器;冯.诺依曼结构:采用单存储空间,即程序指令和数据公用一个存储空间,使用单一的地址和数据总线,取指令和取操作数都是通过一条总线分时进行的;哈佛结构:采用双存储空间,程序存储器和数据存储器分开,有各自独立的程序总线和数据总线,可独立编址和独立访问,可对程序和数据进行独立传输,使取指令操作、指令执行操作、数据吞吐并行完成,大大提高了数据处理能力和指令的执行速度,非常适合与实时的数字信号处理。

3)简述TMS320F2812处理器CPU的组成及特点。

TMS320F2812处理器CPU的组成:保护流水线机制、独立的寄存器空间、算术逻辑单元ALU、地址寄存器算术单元ARAU、桶形移位器、乘法器;TMS320F2812处理器CPU的特点:16X16位和32X32位乘法累加操作、哈佛总线结构、快速中断响应和处理、统一的存储器规划、4M的线性程序地址、4M的线性数据地址、高效的代码(C/C++和汇编语言)、TMS320F24X/LF240X处理器源代码兼容。

在定点的DSP或处理器中,实现一个浮点数的运算时一个非常复杂的事情,尤其是非四则运算的函数运算,例如三角函数运算,sin,cos,tan,又比如指数运算,exp,非整数的幂运算等等。

用机器来实现这样复杂的运算,会花费很多的计算指令周期。

在某些程度下,用定点整数去代替浮点运算,会很大程度的节省运算时间,是应用程序达到实时运算的效果。

一DSP定点算数运算1数的定标在定点DSP芯片中,采用定点数进行数值运算,其操作数一般采用整型数来表示。

一个整型数的最大表示范围取决于DSP芯片所给定的字长,一般为16位或24位。

显然,字长越长,所能表示的数的范围越大,精度也越高。

如无特别说明,本书均以16位字长为例。

DSP芯片的数以2的补码形式表示。

每个16位数用一个符号位来表示数的正负,0表示数值为正, l则表示数值为负。

其余15位表示数值的大小。

因此,二进制数0010000000000011b=8195二进制数1111111111111100b=-4对DSP芯片而言,参与数值运算的数就是16位的整型数。

但在许多情况下,数学运算过程中的数不一定都是整数。

那么,DSP芯片是如何处理小数的呢?应该说,DSP芯片本身无能为力。

那么是不是说DSP芯片就不能处理各种小数呢?当然不是。

这其中的关键就是由程序员来确定一个数的小数点处于16位中的哪一位。

这就是数的定标。

通过设定小数点在16位数中的不同位置,就可以表示不同大小和不同精度的小数了。

数的定标有Q表示法和S表示法两种。

表1.1列出了一个16位数的16种Q表示、S表示及它们所能表示的十进制数值范围。

从表1.1可以看出,同样一个16位数,若小数点设定的位置不同,它所表示的数也就不同。

例如,16进制数2000H=8192,用Q0表示16进制数2000H=0.25,用Q15表示但对于DSP芯片来说,处理方法是完全相同的。

从表1.1还可以看出,不同的Q所表示的数不仅范围不同,而且精度也不相同。

DSP概述[转]默认分类2006-11-12 12:12:12 阅读44 评论1 字号:大中小订阅引言:DSP(digital singnal processor)是一种微处理器,它接收模拟信号,转换为0或1的数字信号,再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。

DSP最突出的两大特色是强大数据处理能力和高运行速度,加上具有可编程性,实时运行速度可达每秒数以千万条复杂指令程序,远远超过通用微处理器,有业内人士预言,DSP将是未来集成电路中发展最快的电子产品,并成为电子产品更新换代的决定因素。

DSP的发展历程:在DSP出现之前,MPU(微处理器)承担着数字信号处理的任务,但它的处理速度较低,无法满足高速实时的要求。

70年代时, DSP的理论和算法基础被提出。

但当时DSP仅仅局限于在教科书,即使是研制出来的DSP系统也是由分立组件组成的,其应用领域仅限于军事、航空航大部门。

到了20世纪60年代,计算机和信息技术的飞速发展为DSP提供了长足进步的机会。

1982年美国德州仪器公司(TI公司)生产出了第一代数字信号处理器(DSP)TMS320C10,这种DSP器件采用微米工艺NMOS技术制作,虽功耗和尺寸稍大,但运算速度却是MPU的几十倍,这种数字信号处理器一面世就在语音合成和编码解码器中得到了广泛应用。

接下来,随着CMOS技术的进步与发展,第二代基于CMOS工艺的DSP芯片应运而生,其存储容量和运算速度成倍提高,成为语音处理、图像硬件处理技术的基础。

80年代后期,第三代DSP芯片问世,运算速度得到进一步提高,这使其应用范围逐步扩大到了通信和计算机领域。

90年代是DSP发展的重要时期,在这段时间第四代和第五代DSP器件相继出现。

目前的DSP属于第五代产品,与第四代相比,第五代DSP系统集成度更高,它已经成功地将DSP芯核及外围组件综合集成在单一芯片上。

这种高集成度的DSP芯片在通信、计算机领域大行其道,近年来已经逐渐渗透到人们日常消费领域,前景十分看好。

dsp芯片的原理与应用概念及重点第一章:1.dsp定义:是指利用计算机,微处理器或专用处理设备,以数字形式对信号进行的采集,交换,滤波,估值,增强,压缩,识别等处理。

2.dsp同时实现的方法:1,在通用型的计算机上以软件同时实现;2,在通用型的计算机系统上加之专用的快速处理机同时实现;3,用通用型的单片机同时实现;4,用通用型的可编程dsp芯片同时实现;5,用专用的dsp芯片同时实现。

3.dsp芯片的优点:1,在一个指令周期内一般至少可以完成一次乘法和一次加法;2,程序空间和数据空间分开,可以同时访问指令和数据;3,片内具有快速ram,通常可通过独立的数据总线在两块中同时访问;4,具有低开销或无开销循环及跳转的硬件支持;5,快速的中断处理和硬件i/o支持;6,具有在单调周期内操作的多个硬件地址生产器;7,可以并行执行多个操作;8,支持流水线操作,使取值,译码和执行等操作可以并行执行。

4.dsp芯片的特点:1,哈佛结构;2,流水线操作方式;3,专用的硬件乘法器;4,高效率的dsp指令;5,快速的指令周期。

5.dsp芯片运算速度衡量标准:1,指令周期;2,mac时间;3,fft执行时间;4,mips;5,mops;6,mflops;7,bops第二章dsp芯片的基本结构大致可以分后cpu、总线、存储器以及内置外设与专用硬件电路等部分。

tms320系列dsp芯片的cpu主要组成:指令解码部分、运算与逻辑部分、寻址部分;运算与逻辑部分通常包含:算术逻辑单元、累加器acc、桶形移位寄存器、乘坐递增单元(mac)哈佛结构:主要特点是将程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个相互独立的存储器,每个存储器独立编址,独立访问。

与两个存储器相对应的是系统中设置了程序总线和数据总线两条总线,从而使数据得吞吐率提高了一倍。

(加图)哈佛结构的改良:1.容许数据存放在程序存储器中,并被算数运算指令轻易采用进一步增强了芯片的灵活性;2.指令存储在高速缓冲器中,当继续执行此指令时,不须要再从存储器中读取指令,节约了一个指令周期的时间。

一DSP定点算数运算1 数的定标在定点DSP芯片中,采用定点数进行数值运算,其操作数一般采用整型数来表示。

一个整型数的最大表示范围取决于DSP芯片所给定的字长,一般为16位或24位。

显然,字长越长,所能表示的数的范围越大,精度也越高。

如无特别说明,本书均以16位字长为例。

DSP芯片的数以2的补码形式表示。

每个16位数用一个符号位来表示数的正负,0表示数值为正,l则表示数值为负。

其余15位表示数值的大小。

因此,二进制数0010000000000011b=8195二进制数1111111111111100b= -4对DSP芯片而言,参与数值运算的数就是16位的整型数。

但在许多情况下,数学运算过程中的数不一定都是整数。

那么,DSP芯片是如何处理小数的呢?应该说,DSP芯片本身无能为力。

那么是不是说DSP芯片就不能处理各种小数呢?当然不是。

这其中的关键就是由程序员来确定一个数的小数点处于16位中的哪一位。

这就是数的定标。

通过设定小数点在16位数中的不同位置,就可以表示不同大小和不同精度的小数了。

数的定标有Q表示法和S表示法两种。

表1.1列出了一个16位数的16种Q 表示、S表示及它们所能表示的十进制数值范围。

从表1.1可以看出,同样一个16位数,若小数点设定的位置不同,它所表示的数也就不同。

例如,16进制数2000H=8192,用Q0表示16进制数2000H=0.25,用Q15表示但对于DSP芯片来说,处理方法是完全相同的。

从表1.1还可以看出,不同的Q所表示的数不仅范围不同,而且精度也不相同。

Q越大,数值范围越小,但精度越高;相反,Q越小,数值范围越大,但精度就越低。

例如,Q0 的数值范围是-32768到+32767,其精度为1,而Q15的数值范围为-1到0.9999695,精度为1/32768=0.00003051。

因此,对定点数而言,数值范围与精度是一对矛盾,一个变量要想能够表示比较大的数值范围,必须以牺牲精度为代价;而想精度提高,则数的表示范围就相应地减小。

dsp基础学习总结笔记1、cj431电压基准芯⽚,2.5v2、电平标准3、驱动器74HC245(为增强PWM的驱动负载能⼒)4、增加输⼊端的抗⼲扰能⼒:在芯⽚的输⼊端加上拉电阻加电源或者下拉电阻接地,没有⽤到的采样端⼝尽量不要悬空。

5、D/A电路⽅案通⽤扩展语⾔GEL和c相似,但是有所不同。

GEL语⾔是C语⾔的⼀个⼦集。

与c语⾔不同的是gel不需要指定函数返回值的类型。

Gel中的while语句和c中的while语句相同,gel不⽀持标准c的break和continue语句6、⼀个完整的dsp⼯程包括头⽂件(.h),库⽂件(.lib),源⽂件(.c),以及配置⽂件.Cmd使⽤关键字MENUITEM可以在gel菜单下选择⽤户⾃定义的菜单项,然后⽤hotmenu、dialog或slider等关键字,在这个新的下拉菜单中添加新的菜单项。

7、关于添加⽂件遇到的问题8、变量查找:edit→find:Ctrl+f9、调试时,添加断点的快捷⽅法如下点击图上的⼩⼿即可10、单步调试第⼀个的意思是单击⼀步⾛⼀步,第⼆个的意思是指在单步运⾏时遇到⼦函数不进⼊⼦函数内部进⾏⽽是把它当成⼀步来执⾏,第三个的意思是当执⾏到⼦函数内部时使⽤这个按钮就可以执⾏完剩下的部分返回上⼀层函数。

如果想在⼀个窗⼝内同时看到c和汇编,则有操作View→mixed source/asm 11、观察变量右击变量→add to watch window 可以得到变量的值、类型、地址等。

12、位域定义、结构体以及共同体的知识结构体先定义再声明Union SCIFFCT_REG {Uint16 all;Struct SCIFFCT_BITS bit;};//---------------------------------------------------------------------------// SCI Register File://Struct SCI_REGS {Union SCICCR_REG SCICCR; // Communications control register Union SCICTL1_REG SCICTL1; // Control register 1Uint16 SCIHBAUD; // Baud rate (high) registerUint16 SCILBAUD; // Baud rate (low) registerUnion SCICTL2_REG SCICTL2; // Control register 2Union SCIRXST_REG SCIRXST; // Receive status registerUint16 SCIRXEMU; // Receive emulation buffer registerUnion SCIRXBUF_REG SCIRXBUF; // Receive data bufferUint16 rsvd1; // reservedUint16 SCITXBUF; // Transmit data bufferUnion SCIFFTX_REG SCIFFTX; // FIFO transmit registerUnion SCIFFRX_REG SCIFFRX; // FIFO receive registerUnion SCIFFCT_REG SCIFFCT; // FIFO control registerUint16 rsvd2; // reservedUint16 rsvd3; // reservedUnion SCIPRI_REG SCIPRI; // FIFO Priority control};//---------------------------------------------------------------------------// SCI External References & Function Declarations://Extern volatile struct SCI_REGS SciaRegs;Extern volatile struct SCI_REGS ScibRegs;由于scihbaud和scilbaud定义时为unit16型的,所以不能⽤.all或者.bit 的⽅式来访问,只能直接给寄存器整体进⾏赋值。

DSP入门(献给初学者)DSP的特点对于没有使用过DSP的初学者来说,第一个困惑就是DSP其他的嵌入式处理器究竟有什么不同,它和单片机,ARM有什么区别。

事实上,DSP也是一种嵌入式处理器,它完全可以完成单片机的功能。

唯一的重要的区别在于DSP支持单时钟周期的“乘-加”运算。

这几乎是所有厂家的DSP芯片的一个共有特征。

几乎所有的DSP处理器的指令集中都会有一条MAC指令,这条指令可以把两个操作数从RAM 中取出相乘,然后加到一个累加器中,所有这些操作都在一个时钟周期内完成。

拥有这样一条指令的处理器就具备了DSP功能具有这条指令就称之为数字信号处理器的原因在于,所有的数字信号处理算法中最为常见的算术操作就是“乘-加”。

这是因为数字信号处理中大量使用了内积,或称“点积”的运算。

无论是FIR滤波,FFT,信号相关,数字混频,下变频。

所有这些数字信号处理的运算经常是将输入信号与一个系数表或者与一个本地参考信号相乘然后积分(累加),这就表现为将两个向量(或称序列)进行点积,在编程上就变成将输入的采样放在一个循环buffer里,本地的系数表或参考信号也放在一个buffer里,然后使用两个指针指向这两个buffer。

这样就可以在一个loop里面使用一个MAC指令将二者进行点积运算。

这样的点积运算对与处理器来说是最快的,因为仅需一个始终周期就可以完成一次乘加。

了解DSP的这一特点后,当我们设计一个嵌入式系统时,首先要考虑处理器所实现的算法中是否有点积运算,即是否要经常进行两个数组的乘加,(记住数字滤波,相关等都表现为两个数组的点积)如果有的话,每秒要做多少次,这样就能够决定是否采用DSP,采用多高性能的DSP了。

浮点与定点浮点与定点也是经常是初学者困惑的问题,在选择DSP器件的时候,是采用浮点还是采用定点,如果用定点是16位还是32位?其实这个问题和你的算法所要求的信号的动态范围有关。

定点的计算不过是把一个数据当作整数来处理,通常AD采样来的都是整数,这个数相对于真实的模拟信号有一个刻度因子,大家都知道用一个16位的AD去采样一个0到5V的信号,那么AD输出的整数除以2^16再乘以5V就是对应的电压。

数字信号处理器(DSP)主要针对代表连续信号的数字进行数学运算,以得到相应的处理结果。

这种数学运算是以快速叶变换(FFT)为基础,对数字信号进行实时处理。

近二十年来,由于集成电路技术的高速发展,使得用硬件来实现各种数字滤波和快速傅立叶变换成为可能,从而使DSP得到了极其迅速的发展和广泛的应用。

在数字化的世界和互联网的时代,DSP变得越来越重要,可以说是无处不在。

DSP最基本的特征是:1)能够在一个指令周期内实现一次或多次乘法累加(MAC)运算。

所以,在DSP中集成了多个乘法累加运算单元,可以进行并行乘法累加运算。

2)能够在一个指令周期内完成对存储器的多次读取。

所以,在DSP中集成了多个片内总线和多端口片内存储器。

3)为了加快处理器中的运算,在DSP中集成了多个地址产生单元,以支持循环寻址和位翻转寻址。

4)处理器中的运算大多是重复的运算,为了方便使用,大部分DSP都支持这种重复运算,而不用额外编写重复运算的指令。

5)大部分DSP都提供多个串行或并行I/O接口,以及特别I/O接口来处理特殊的数据,以降低成本和提高输出/输入性能。

虽然应用于不同领域的DSP有不同的型号,但其内部结构大同小异,都具有哈佛(Harvard)结构的特征。

它包括处理器内核,指令缓冲器,数据存储器和程序存储器,I/O 接口控制器,程序地址总线和程序数据总线,直接读取的地址总线和数据总线等单元,其中最核心的是处理器内核。

它的性能好坏直接决定了DSP的性能和使用范围。

Analog Device 公司的TigerSHARC处理器内核就具有典型的哈佛结构特征。

它于1998年10月问世,具有特大指令字组(VLIW)的结构,一个周期可执行四条32位指令,可以工作于多种数据宽度,支持定点和浮点两种格式, 支持两种单指令多重数据(SIMD)运算,一个周期可执行四条16x16位定点乘法,支持六种不同的数据:(8位,16位,32位,64位)定点、32位IEEE-754浮点和40位扩展精度浮点。

DSP重点知识点1.数字信号处理的实现方法(P1)1)在通用计算机上用软件实现(速度较慢,一般用于DSP算法模拟)2)在通用计算机系统中加上专用的加速处理机实现(专用性强,应用受限,不便于系统的独立运行)3)用通用的单片机实现——用于不太复杂的数字信号处理(简单的DSP算法)4)用专用的DSP芯片实现——具有更加爱适合DSP的软硬件资源,可用于复杂的数字信号处理算法5)用专用的DSP芯片实现——特殊场合,要求信号处理速度极高(专用性强,应用受限)2.DSP两种含义(P2)1)数字信号处理技术(Digital Signal Processing)2)数字信号处理器(Digital Signal Processor)3.DSP芯片的结构(P2)1)哈佛结构片内程序空间和数据空间是合在一起的,取指令和取操作数都是通过一条总线分时进行的2)改进的哈佛结构程序空间和数据空间分开,1组程序存储器总线,3组数据存储器总线,3组地址总线,允许同时取指令和取操作数,还允许在程序空间和数据空间之间相互传送数据3)多总线结构一个机器周期内可以多次访问程序空间和数据空间,如TMS320C51x内部有P、C、D、E共4条总线,每条总线又包括地址总线和数据总线4)流水线结构4.DSP芯片的分类(P4)1)按照基础特性分类:静态DSP芯片一致性DSP芯片2)按照数据格式分类:定点DSP芯片浮点DSP芯片3)按照用途分类:通用型DSP芯片专用型DSP芯片5.TMS320C54x硬件结构(P8)1)TMS320系列同一代芯片具有相同的CPU结构,但是片内存储器和片内外围设备的配置是不同的2)TMS320C54x是16位定点DSP,采用改进的哈佛结构,有一组程序总线和三组数据总线6.TMS320C54x总线结构(P10)片内有8条16位主总线:4条程序/数据总线和4条地址总线7.累加器A 可以用来累加器寻址。

8.1) IPTR :中断向量指针,9位字段中断向量驻留的128字程序存储区地址。