74HC165D

- 格式:pdf

- 大小:77.02 KB

- 文档页数:10

74HC165 概述74HC165是一款高速CMOS器件,74HC165遵循JEDEC标准no.7A。

74HC165引脚兼容低功耗肖特基TTL(LSTTL)系列。

74HC165是8位并行读取或串行输入移位寄存器,可在末级得到互斥的串行输出(Q7和Q7),当并行读取(PL)输入为低时,从D0到D7口输入的并行数据将被异步地读取进寄存器内。

而当PL为高时,数据将从DS输入端串行进入寄存器,在每个时钟脉冲的上升沿向右移动一位(Q0 → Q1 → Q2,等等)。

利用这种特性,只要把Q7输出绑定到下一级的DS输入,即可实现并转串扩展。

74HC165的时钟输入是一个“门控或”结构,允许其中一个输入端作为低有效时钟使能(CE)输入。

CP和CE的引脚分配是独立的并且在必要时,为了布线的方便可以互换。

只有在CP为高时,才允许CE由低转高。

在PL上升沿来临之前,不论是CP还是CE,都应当置高,以防止数据在PL的活动状态发生位移。

74HC165 特性异步8位并行读取同步串行输入兼容JEDEC标准no.7AESD保护HBM EIA/JESD22-A114E超过2000 VMM EIA/JESD22-A115-A超过200 V温度范围-40~+85 ℃-40~+125 ℃74HC165 参数74HC165 基本参数电压 2.0~6.0V驱动电流+/-5.2 mA传输延迟16 ns@5V74HC165 其他特性最高频率56 MHz逻辑电平CMOS功耗考量低功耗或电池供电应用74HC165 封装与引脚SO16, SSOP16, DIP16, TSSOP168 位移位寄存器(并行输入,互补串行输出)简要说明当移位/置入控制端(SH/LD)为低电平时,并行数据(A-H)被置入寄存器,而时钟(CLK,CLK INH)及串行数据(SER)均无关。

当SH/LD为高电平时,并行置数功能被禁止。

CLK和CLK INK在功能上是等价的,可以交换使用。

74HCT165D中文资料DATA SHEETProduct speci?cationFile under Integrated Circuits, IC06December 1990INTEGRATED CIRCUITS74HC/HCT1658-bit parallel-in/serial-out shift registerFor a complete data sheet, please also download:The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications ?The IC06 74HC/HCT/HCU/HCMOS Logic Package Information ?The IC06 74HC/HCT/HCU/HCMOS Logic Package OutlinesFEATURESAsynchronous 8-bit parallel load ?Synchronous serial input ?Output capability: standard ?I CC category: MSI GENERAL DESCRIPTIONThe 74HC/HCT165 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A.The 74HC/HCT165 are 8-bit parallel-load or serial-in shift registers with complementary serial outputs (Q 7and Q 7)available from the last stage. When the parallel load (PL)input is LOW, parallel data from the D 0toD 7inputs are loaded into the register asynchronously.When PL is HIGH, data enters the register serially at the D s input and shifts one place to the right(Q 0→Q 1→Q 2,etc.) with each positive-going clock transition. This feature allows parallel-to-serial converterexpansion by tying the Q 7output to the D S input of the succeeding stage.The clock input is a gated-OR structure which allows one input to be used as an active LOW clock enable (CE)input.The pin assignment for the CP and CE inputs is arbitrary and can be reversed for layout convenience. The LOW-to-HIGH transition of input CE should only take place while CP HIGH for predictable operation. Either the CP or the CE should be HIGH before the LOW-to-HIGH transition of PL to prevent shifting the data when PL is activated.APPLICATIONSParallel-to-serial data conversionQUICK REFERENCE DATAGND = 0 V; T amb = 25°C; t r = t f = 6 ns Notes1.C PD is used to determine the dynamic power dissipation (P D in μW):P D = C PD ×V CC 2×f i +∑(C L ×V CC 2×f o )where:f i = input frequency in MHz f o = output frequency in MHz ∑(C L ×V CC 2×f o )= sum of outputs C L =output load capacitance in pF V CC =supply voltage in V2.For HC the condition is V I = GND to V CCFor HCT the condition is V I = GND to V CC ?1.5 V ORDERING INFORMATIONSee “74HC/HCT/HCU/HCMOS Logic Package Information”.SYMBOL PARAMETERCONDITIONS TYPICAL UNITHCHCTt PHL / t PLHpropagation delay CP to Q 7,Q 7PL to Q 7,Q 7D 7 to Q 7,Q 7C L = 15 pF; V CC = 5 V161511141711ns ns ns f max maximum clock frequency 5648MHz C I input capacitance3.5 3.5pF C PD power dissipation capacitance per packagenotes 1 and 23535pFPIN DESCRIPTIONPIN NO.SYMBOL NAME AND FUNCTION1PL asynchronous parallel load input (active LOW)7Q7complementary output from the last stage9Q7serial output from the last stage2CP clock input (LOW-to-HIGH edge-triggered)8GND ground (0 V)10D s serial data input11, 12, 13, 14, 3, 4, 5, 6D0to D7parallel data inputs15CE clock enable input (active LOW)16V CC positive supply voltageFig.1 Pin configuration.Fig.2 Logic symbol.Fig.3 IEC logic symbol.FUNCTION TABLE Note1.H = HIGH voltage levelh = HIGH voltage level one set-up time prior to the LOW-to-HIGH clock transition L = LOW voltage levelI =LOW voltage level one set-up time prior to the LOW-to-HIGH clock transitionq =lower case letters indicate the state of the referenced output one set-up time prior to theLOW-to-HIGH clock transition X = don’t care↑=LOW-to-HIGH clock transitionOPERATING MODESINPUTS Q n REGISTERS OUTPUTS PLCECPD SD 0-D 7Q 0Q 1-Q 6Q 7Q 7parallel load L L X X X X X X L H L H L - L H - H L H H L serial shift H H L L ↑↑l h X X L H q 0-q 5q 0-q 5q 6q 6q 6q 6hold “do nothing”HH X X X q 0q 1-q 6q 7q 7Fig.4 Functional diagram.Fig.5 Logic diagram.DC CHARACTERISTICS FOR 74HCFor the DC characteristics see“74HC/HCT/HCU/HCMOS Logic Family Specifications”. Output capability: standardI CC category: MSIAC CHARACTERISTICS FOR HCGND = 0 V; t r= t f= 6 ns; C L= 50 pFSYMBOL PARAMETERT amb(°C)UNITTEST CONDITIONS74HCV CC(V)WAVEFORMS +25?40to+85?40to+125 min.typ.max.min.max.min.max.t PHL/ t PLH propagation delay CE,CP to Q7,Q7521915165332820541352505043ns 2.04.56.0Fig.6t PHL/ t PLH propagation delayPL to Q7,Q75018141653328205413525043ns 2.04.56.0Fig.6t PHL/ t PLH propagation delay D7to Q7,Q7361310120242015030261803631ns 2.04.56.0Fig.6t THL/ t TLH output transition time 197675151319161102219ns 2.04.56.0Fig.6t W clock pulse width HIGH or LOW 801614176510020171202420ns 2.04.56.0Fig.6t W parallel load pulse width; LOW 8016145410020171202420ns 2.04.56.0Fig.6t rem removal time PL to CP,CE 100 2017228612525211503026ns 2.04.56.0t su set-up timeD s to CP,CE 801614114310020171202420ns 2.04.56.0Fig.6t su set-up time CE to CP;CP to CE 801614176510020172420ns 2.04.56.0Fig.6t su set-up timeD n to PL 801614228610020171202420ns 2.04.56.0Fig.6t h hold timeD s to CP,CED n to PL 555622555555ns 2.04.56.0Fig.6t h hold time CE to CP CP to CE 5 551765555555ns 2.04.56.0Fig.6f max maximum clockpulse frequency 630351751615242842024MHz 2.04.56.0Fig.6SYMBOL PARAMETERT amb(°C)UNITTEST CONDITIONS74HCV CC(V)WAVEFORMS +25?40to+85?40to+125min.typ.max.min.max.min.max.DC CHARACTERISTICS FOR 74HCTFor the DC characteristics see“74HC/HCT/HCU/HCMOS Logic Family Specifications”.Output capability: standardI CC category: MSINote to HCT typesThe value of additional quiescent supply current (?I CC)for a unit load of 1 is given in the family specifications. To determine?I CC per input, multiply this value by the unit load coefficient shown in the table below.INPUT UNIT LOAD COEFFICIENTD n D s CP CE PL 0.35 0.35 0.65 0.65 0.65AC CHARACTERISTICS FOR 74HCT GND = 0 V; t r= t f= 6 ns;C L= 50 pFSYMBOL PARAMETERT amb(°C)UNITTEST CONDITIONS74HCTV CC(V)WAVEFORMS +25?40to+85?40to+125min.typ.max.min.max.min.max.t PHL/ t PLH propagation delayCE,CP to Q7,Q717344351ns 4.5Fig.6t PHL/ t PLH propagation delayPL to Q7,Q720405060ns 4.5Fig.6t PHL/ t PLH propagation delayD7to Q7,Q714283542ns 4.5Fig.6 t THL/ t TLH output transition time7151922ns 4.5Fig.6t W clock pulse widthHIGH or LOW1662024ns 4.5Fig.6t W parallel load pulsewidth; LOW2092530ns 4.5Fig.6t rem removal timePL to CP,CE2082530ns 4.5Fig.6t su set-up timeD s to CP,CE2022530ns 4.5Fig.6t su set-up timeCE to CP; CP to CE2072530ns 4.5Fig.6t su set-up timeD n to PL20102530ns 4.5Fig.6t h hold timeD s to CP,CE;D n to PL7?1911ns 4.5Fig.6t h hold timeCE to CP, CP to CE0?700ns 4.5Fig.6f max maximum clock pulsefrequency26442117MHz 4.5Fig.6AC WAVEFORMSThe changing to output assumes internal Q6 opposite state from Q7.(1)HC: V M= 50%; V I= GND to V CC.HCT:V M= 1.3 V; V I=GND to 3 V.Fig.6Waveforms showing the clock (CP) to output (Q7or Q7) propagation delays, the clock pulse width, the output transition times and the maximum clock frequency.The changing to output assumes internal Q6opposite state from Q7.(1)HC: V M= 50%; V I= GND to V CC.HCT:V M= 1.3 V; V I =GND to 3 V.Fig.7Waveforms showing the parallel load (PL) pulse width, the parallel load to output (Q7or Q7)propagation delays, the parallel load to clock (CP) and clock enable (CE) removal time.(1)HC: V M= 50%; V I= GND to V CC.HCT:V M= 1.3 V; V I=GND to 3 V.Fig.8 Waveforms showing the data input (D n)to output (Q7or Q7)propagation delays when PL is LOW.CE may change only from HIGH-to-LOW while CPis LOW.The shaded areas indicate when the input ispermitted to change for predictable outputperformance.(1)HC: V M= 50%; V I= GND to V CC.HCT:V M= 1.3 V; V I=GND to 3 V.Fig.9Waveforms showing the set-up and hold times from the serial data input (D s)to the clock (CP)and clock enable (CE)inputs, from the clock enable input (CE)to the clock input (CP)and from the clock input (CP) to the clock enable input (CE).(1)HC: V M= 50%; V I= GND to V CC.HCT:V M= 1.3 V; V I=GND to 3 V.Fig.10 Waveforms showing the set-up and hold times fromthe data inputs (D n)to the parallel load input (PL).PACKAGE OUTLINESSee“74HC/HCT/HCU/HCMOS Logic Package Outlines”.。

74HC165的联级编程实例三篇篇一:74HC165的联级编程实例#include<reg51.h>#include<intrins.h>sbitCLK=P2^5;//时钟sbitLD=P2^6;//移位,置位sbitSO=P2^7;//输出#defineLED1P0#defineLED2P1inthc165(){inti=0;chardat1=0,dat2=0;intdat=0;LD=0;//允许数据数据进入165 _nop_();LD=1;//for(i=0;i<8;i++){dat1<<=1;CLK=0;if(SO==1)dat1|=0x01; CLK=1;}for(i=0;i<8;i++){dat2<<=1;CLK=0;if(SO==1)dat2|=0x01; CLK=1;}LD=0;dat=dat1;dat<<=8;dat|=dat2;returndat;}voidmain(){while(1){LED1=(hc165()&0XFF);LED2=((hc165()>>8)&0XFF); }}篇二:74HC165联级编程实例#include<AT89X51.h>#define uchar unsigned char#define uint unsigned intsbit DS=P1^0 ; //595sbit SH=P1^1 ;sbit ST=P1^2 ;//sbit MR=P1^3;sbit CLK=P1^4;//165sbit INH=P1^5;sbit LD=P1^6;sbit SO=P1^7;//msec(511);0.5s//msec(2);2ms//msec(1021);//1svoid msec(unsigned long x) //延时 {unsigned char j;while(x!=0){x--;for(j=0;j<116;j++) {;}}}void hc595(uchar *p,n) {uchar i,j;for(;n>0;n--){i=*p;for(j=0;j<8;j++){DS=i&0x80;i=i<<1;SH=0;SH=1;}ST=0;ST=1;ST=0;p++;}}void hc165(uchar *d,n) {uchar i=0,j,c=0;LD=1;LD=0;LD=1;INH=0;for(j=0;j<(n*8);j++) {CLK=1;i=i<<1;i=i|SO;CLK=0;c++;if(c==8){*d=i;c=0;d++;}}}main(){uchar *P,*D;uchari,a[5]={0x00,0x00,0x00,0x00,0x01},b[5]={0x0ff,0x0ff,0x0ff,0x0ff,0x0f f}; P=a;D=b;hc595(P,5);hc165(D,5);P3=b[4];while(1);for(i=0;i<34;i++){if(i==8){a[3]=0x01; a[4]=0x00;}if(i==16){a[2]=0x01;a[3]=0x00;}if(i==24){a[1]=0x01;a[2]=0x00;}if(i==32){a[0]=0x01;a[1]=0x00;}P=a;hc595(P,5);a[0]<<=1;a[1]<<=1; a[2]<<=1; a[3]<<=1; a[4]<<=1; msec(511); }}篇三:74HC165联级编程实例74HC595 74HC165程序例子(AVR)硬件说明:ATmega48/88/168的PB5是SPI时钟输出,接74HC595/74HC165的移位时钟输入端;PB4是SPI的MISO数据输人,接74HC165的数据输出;PB3是SPI的MOSI数据输出,接74HC595的串行数据输入端SER;PB2接74HC595/74HC165的锁存时钟输入端。

74hc165 电平标准740HC165是一种8位移位寄存器,它常用于电子设备中的数据输入和输出。

在设计和使用电子电路中,了解和理解其电平标准是非常重要的。

首先,让我们来了解一下何为电平标准。

在电子领域中,电平标准用来定义不同电压值所代表的逻辑状态,例如高电平表示1,低电平表示0。

电平标准是为了保证不同设备和电路之间的互操作性以及通信的可靠性。

740HC165的电平标准和逻辑电平定义如下:1.电源电压:740HC165的工作电压范围通常为2V至6V。

这意味着电路在这个电压范围内工作时,可以正常执行其功能。

2.逻辑高电平:对于输入信号而言,当输入电压高于特定阈值电压(通常称为ViH)时,电路将识别为逻辑高电平。

在740HC165中,典型的ViH电平为0.7VCC,其中VCC是电路的电源电压。

也就是说,如果输入电压高于0.7VCC,电路将被视为处于逻辑高电平。

3.逻辑低电平:对于输入信号而言,当输入电压低于特定阈值电压(通常称为ViL)时,电路将识别为逻辑低电平。

在740HC165中,典型的ViL电平为0.3VCC,其中VCC是电路的电源电压。

也就是说,如果输入电压低于0.3VCC,电路将被视为处于逻辑低电平。

4.输出电平:对于输出信号而言,当输出电压高于特定阈值电压(通常称为VOH)时,电路将输出逻辑高电平。

在740HC165中,典型的VOH电平为0.9VCC,其中VCC是电路的电源电压。

相反,当输出电压低于特定阈值电压(通常称为VOL)时,电路将输出逻辑低电平。

在740HC165中,典型的VOL电平为0.1VCC,其中VCC是电路的电源电压。

总结一下,740HC165的电平标准意味着输入电压高于0.7倍的电源电压将被视为逻辑高电平,低于0.3倍的电源电压将被视为逻辑低电平。

对于输出电平而言,高于0.9倍的电源电压将输出逻辑高电平,低于0.1倍的电源电压将输出逻辑低电平。

了解电平标准对于正确设计和使用电子电路至关重要。

(31条消息)74HC165级联电路篇(三)

74HC165其实和74HC595一样,也有级联功能,74HC595级联在前面已经整理过,这里说下74hc165的级联。

前面基础篇也讲到74HC165是个并行输入转串行输出的逻辑芯片,该芯片除了串行输出外还有一个串行输入引脚,74HC165的级联功能就使用到这个串行输入引脚,也就是引脚10(DS):

下面就讲下74HC165级联的原理:

从前面的两篇74HC165文章知道,74HC165并行转串行是通过移位寄存器实现的,当PL为低电平时,并行数据(8bit)进入移位寄存器,当PL为高时,进入移位寄存器的数据就从DS引脚进入寄存器,然后在每个时钟的上升沿往输出引脚Q7移一位。

根据这个原理,只要把输出Q7(引脚9)连到下一级74HC165的DS引脚(引脚10)即可实现级联功能,如下图:

最后再以图文并茂的方式总结下74HC165级联后的工作过程,如下图:

74HC165的级联电路就整理到这里,下一篇是级联的编程,总结下如何读取74HC165级联的数据。

74hc165接收函数支持联级/**************************************************** 74hc165intn();//初始化74hc165satin();//开始输入接收单级数据:dat=inpute();//接收返回值到dat使用数组保存多级:hc165pinsav(d)//d为接收个数,联级个数。

******************************************************/ #ifndef __74hc165_H__#define __74hc165_H__#include "A T89X52.h"#include <intrins.h>#include<stdio.h>unsigned char hc165insav[4];//保存接收数据联极sbit ck=P1^1;//时钟2引脚。

sbit sd=P1^0;//数据9引脚。

sbit sh=P1^2;//开始输入1引脚。

//SI联级10引脚,连接下级的9引脚。

/****************************************************五个机器周期******************************************************/ void nop(){_nop_();_nop_();_nop_();_nop_();_nop_();_nop_();_nop_();}/****************************************************74hc165初始化******************************************************/void hc165intn() //初始化{sh=1;sd=1;ck=1;}/****************************************************74hc165开始输人******************************************************/ void hc165satin(){sh=0; //起始接收脉冲开始接收。

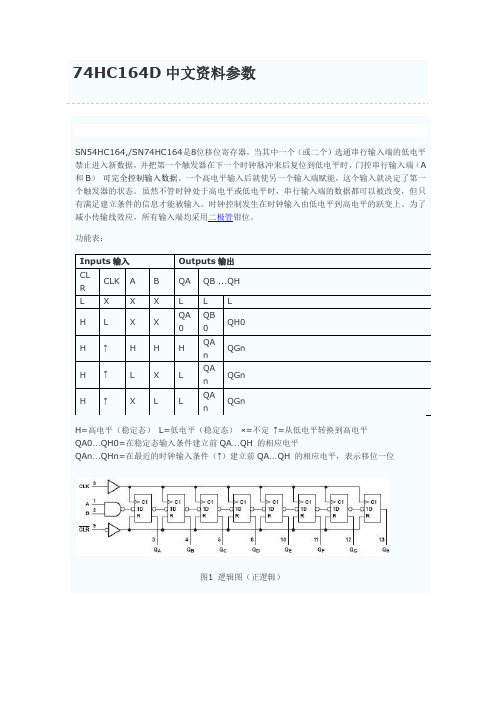

74HC164D中文资料参数SN54HC164,/SN74HC164是8位移位寄存器,当其中一个(或二个)选通串行输入端的低电平禁止进入新数据,并把第一个触发器在下一个时钟脉冲来后复位到低电平时,门控串行输入端(A 和B)可完全控制输入数据。

一个高电平输入后就使另一个输入端赋能,这个输入就决定了第一个触发器的状态。

虽然不管时钟处于高电平或低电平时,串行输入端的数据都可以被改变,但只有满足建立条件的信息才能被输入。

时钟控制发生在时钟输入由低电平到高电平的跃变上。

为了减小传输线效应,所有输入端均采用二极管钳位。

功能表:Inputs输入Outputs输出CLRCLK A B QA QB ...QHL X X X L L LH L X X QAQBQH0H↑H H H QAnQGnH↑L X L QAnQGnH↑X L L QAnQGnH=高电平(稳定态)L=低电平(稳定态)×=不定↑=从低电平转换到高电平QA0…QH0=在稳定态输入条件建立前QA…QH 的相应电平QAn…QHn=在最近的时钟输入条件(↑)建立前QA…QH 的相应电平,表示移位一位图1 逻辑图(正逻辑)图2 引脚图Absolute Maximum Ratings绝对最大额定值Supply voltage range, 电源电压范围VCC–0.5 V to 7V Input clamp current, 输入钳位电流IIK (VI < 0 or VI > VCC) (seeNote 1)±20 mA Output clamp current,输出钳位电流IOK (VO < 0 or VO > VCC) (seeNote 1)±20 mA Continuous output current,连续输出电流IO (VO = 0 to VCC)±25 mA Continuous current through 连续通过电流VCC or GND±50 mA封装热阻thermal impedance, θJA (see Note 2):D 封装86℃/W N 封装80℃/W NS 封装76℃/W PW 封装113℃/WStorage temperature range, Tstg储存温度范围–65℃ to 150℃DC SPECIFICATIONS直流电气规格表:符号Parameter 参数SN54HC164SN74HC164最小典型最大最小典型最大VCCSupply Voltage 电源电压256256图3 参数测量信息图4 typical clear, shift, and clear sequence典型清除、移位和清除时序应用电路:图5 LCD驱动电路图6 LED驱动电路74HC164中文资料参数时间:2016-06-15 来源:资料室作者:编号:颖展电子SN54HC164,/SN74HC164是8位移位寄存器,当其中一个(或二个)选通串行输入端的低电平禁止进入新数据,并把第一个触发器在下一个时钟脉冲来后复位到低电平时,门控串行输入端(A 和B)可完全控制输入数据。

![74HC165功能说明[技巧]](https://img.taocdn.com/s1/m/680d699703d276a20029bd64783e0912a2167c05.png)

74hc165编程说明接触单片机,嵌入式有好长一段时间了,一直想找个机会把自己总结的东西拿出来晒晒太阳(其实没有什么,高手可能早已经了解),在这里我只想分享给和我一样奋斗在单片机一线的广大童鞋么一点小小的甚至卑微的经验。

我们都知道通信从大的方面有两种:串行和并行。

串行的最大优点是占用总线少,但是传输速率低;并行恰恰相反,占用总线多,传输速率高。

市面上有很多这样的芯片,有串入并出的(通俗讲就是一个一个进,最后一块出来),有并入串出的(相对前者而言)。

具体用哪种类型要根据我们得实际情况。

比如利用单片机显示数码管单纯的显示一个数码管如果仅仅是为了显示那么动用单片机一个端口(如P0或P1/P2/P3)那没有什么,当然这里我说的数码管是8段的(如果利用BCD类型16进制数码管那么只需四个即可)就拿51类型的单片机来说,总共32个I/O口,一般如果不是做太大的工程是完全够用的,但有些时候你会恨单片机怎么不多长几条“腿”,怎么省还是不够用。

别急集成串行芯片来帮忙哈哈客套话就不多说了言归正传,今天我介绍一下几个在数码管显示或键盘处理中经常用到的移位寄存器芯片,首先登场的是74HC165:74HC165/74LS165是典型并入串出芯片,用它来读取外界键盘信息再好不过了,前提我们得了解它,我们先了解其引脚:引出端符号CLK,CLK INH 时钟输入端(上升沿有效)A-H 并行数据输入端SER 串行数据输入端QH 输出端QHn 互补输出端SH/LD 移位控制/置入控制(低电平有效)真值表时序图其实看一个芯片是如何使用的,不只是看引脚功能,更重要的是要看时序图和真值表,从其中我们可以详细的了解到它是如何使用的,然后转化成程序代码即可。

从上面我们的真值表和时序图中我们要特别注意几个端口的变化,真值表中SH/LD只有在高电平的时候方才有效;CLK,CLK INH只有当其中一个为低电平的时候,另一个时钟才能正确的输入,这是非常重要的(一般的我们在使用时,可以将其中的一个直接接地,另一个做时钟输入端口使用)。

74HC165、75HC595芯片引脚及原理框图 -电子技术图 74HC165、75HC595芯片引脚及原理框图有了图引脚资料,也许还须再加上时序波形图,再加上内部功能电路图,才能有分析工作原理的条件。

也许仍然不够,还须深究对信号的处理细节。

移位寄存器芯片属于中规模集成电路,其电路结构较为复杂,这么一通搞下来,费时费力。

有简单的办法吗?可由应用电路的构成,倒推芯片所完成的功能。

也许换一个路子走,更有效率。

先看图,弄明白IC芯片在电路中起到的作用。

其中用于处理显示的相关电路部分:①5组反相器(BU5)为通讯信号传输芯片,其中9、8脚传输的为显示同步时钟(串行脉冲);1、2、3、4脚两组反相器传输的显示数据(串行脉冲),以上是数码管显示所需的两路输入信号。

②BU1、BU3用于串行脉冲的再处理,将串行输入转换为8路并行输出(专门处理数码管显示信息)。

配合后续电路分析,BU1输出信号经三极管BQ1~BQ8放大,用于数码管的8段显示驱动;BU3输出信号再经BU2进行功率放大,用于6位(7只发光二极管也算作一位,再加上5位数码显示)数码管驱动。

据此,本电路是根据由MCU主板来(主板MCU发送)的串行脉冲,被动显示的,若显示88888或-----,或无显示,仅有两个可能:①MCU主板未有串行脉冲(显示数据)送至面板,此故障概率较大;②BU5、BU1、BU2、BU3等电路异常,此故障概率较小。

先不管芯片好坏,测量BU5相关输入、输出引脚的串行脉冲信号,此处推荐采用示波器测量较为准确,若有一路是存在的,则说明主板MCU已经工作(该两路脉冲是主板MCU已经正常工作的标志)。

若两路俱无,则故障检修方向已经明确指向排线端子及主板MCU基本工作条件电路。

若脉冲正常,而显示异常,检修方向即指向面板电路。

例如针对74HC595芯片,①只要测知输入11脚串行脉冲(显示时钟)和输入14脚串行脉冲(显示数据)正常,②则其余8个“段驱动”信号输出脚,至少有数个脚应有脉冲电压(如2.5V左右)输出。

74HC165用法

----CanolaFlower2014.1.23

74HC165级联,如下图

SH/LD为低,并口数据存入8个位寄存器中。

8个位寄存器分别为Q0、Q1、Q2、Q3、Q4、Q5、Q6、Q7。

此时Q7里已经有值,可以直接读取了

所以,逻辑可以是这样

读取Q7的数据,然后

IN_CLK_LOW;IN_CLK_HIGH; 制造一次上升沿,执行移位操作,使Q6的值移位到Q7中。

SH/LD为高,允许移位。

一个时钟脉冲,QH向外输出一位数据,同时,从SER 采集一位数据补充8位寄存器。

如上级联情况,右边74HC165的SER悬空,采集数据为0.

左边74HC165,一个脉冲,QH输出一位数据,同时,从SER采集一位数据补充低位。

相当于如下:

开始前

H1-G1-F1-E1-D1-C1-B1-A1 H2-G2-F2-E2-D2-C2-B2-A2

开始传输

1,1G-1F-1E-1D-1C-1B-1A-2H 2G-2F-2E-2D-2C-2B-2A-0

2,1F-1E-1D-1C-1B-1A-2H-2G 2F-2E-2D-2C-2B-2A-0-0

3,1E-1D-1C-1B-1A-2H-2G-2F 2E-2D-2C-2B-2A-0-0-0。

14,B2-A2-0-0-0-0-0-0 0-0-0-0-0-0-0-0

15,A2-0-0-0-0-0-0-0 0-0-0-0-0-0-0-0

16,0-0-0-0-0-0-0-0 0-0-0-0-0-0-0-0

这样,就把2个级联的74HC165的并口数据,全部以串口形式传输给了MCU。

74HC165串口驱动程序//-------------------------------------库函数声明,管脚定义-------------#include <reg52.h>sbit LOAD=P1^7; //用P1^7控制SH/LD管脚//----------------------------------------------------------------------// 函数名称:UART_init()// 功能说明:串口初始化,设定串口工作在方式0//----------------------------------------------------------------------void UART_init(void){SCON =0x10; //没串行口方式0,允许接收,启动接收过程ES=0; // 禁止串口中断}//----------------------------------------------------------------------// 函数名称:PA()// 输入参数:无// 输出参数:返回由并口输入的数据// 功能说明:接收八位串行数据//----------------------------------------------------------------------unsigned char PA(void){unsigned char PA_data;LOAD=0; //当P1.7输出低电平,74LS165将并行数据置入寄存器中LOAD=1; //当P1.7输出高电平,74LS165将并行数据置入寄存器中UART_init(); //74LS165工作在时钟控制下的串行移位状态While(RI==0); //循环等待RI=0;PA_data=SBUF;return PA_data; //返回并行输入的数据}74HC164串口驱动程序//-----------------------------------库函数声明,管脚定义--------------#include <reg52.h>sbit CLR=P1^7; //用P1^7控制CLR//-----------------------------------------------------------------------// 函数名称:UART_init()// 功能说明:串口初始化,设定串口工作在方式0//-----------------------------------------------------------------------void UART_init(void) {SCON =0x00;//没串行口方式0,允许发送,启动发送过程ES=0;// 禁止串口中断}//-----------------------------------------------------------------------// 函数名称:PA_out() // 输入参数:PA_data,需要从74LS164并行口输出的数据// 输出参数:无// 功能说明:发送八位串行数据至并口//-----------------------------------------------------------------------void PA_out(unsigned char){CLR =0; //并口输出清零CLR =1; //开始串行移位UART_init(); //74LS165工作在时钟控制下的串行移位状态While(TI==0); //循环等待TI=0;SBUF=PA_data;}74HC165驱动程序/-------------------------------------库函数声明,管脚定义---------------#include <reg52.h>sbit a7=ACC^7;sbit simuseri_CLK=P1^6; //用P1^6模拟串口时钟sbit simuseri_DATA=P1^5; //用P1^5模拟串口数据//-----------------------------------------------------------------------// 函数名称:in_simuseri// 输入参数:无// 输出参数:data_buf// 功能说明:8位同步移位寄存器,将simuseri_DATA串行输入的数据按从低位到高位// 保存到data_buf//-----------------------------------------------------------------------char in_simuseri(void){char i;char data_buf;i=8;do{ACC=ACC>>1;for(;simuseri_CLK==0;) ;a7=simuseri_DATA;for(;simuseri_CLK==1;) ;}while(--i!=0);simuseri_CLK=0;data_buf=ACC;return(data_buf);}//-------------------------------------库函数声明,管脚定义--------------sbit drive74165_LD=P1^7;//用P1^7控制SH/LD管脚//-----------------------------------------------------------------------// 函数名称:PAs// 输入参数:无// 输出参数:PAs_buf,返回并行输入74LS165的数据// 功能说明:直接调用,即可读取并行输入74LS165的数据,不需要考虑74LS165的// 工作原理//-----------------------------------------------------------------------char PAs(void){char PAs_buf;drive74165_LD =0; 并行置入数据drive74165_LD =1; 开始串行移位PAs_buf= in_simuseri();Return(PAs_buf);}74HC164驱动程序//-------------------------------------库函数声明,管脚定义--------------#include <reg52.h>sbit simuseri_CLK=P1^6; //用P1^6模拟串口时钟sbit simuseri_DATA=P1^5; //用P1^5模拟串口数据sbit drive74164_CLR=P1^7; //用P1^7控制CLRsbit a0=ACC^0;//-----------------------------------------------------------------------// 函数名称:out_simuseri// 输入参数:data_buf// 输出参数:无// 功能说明:8位同步移位寄存器,将data_buf的数据逐位输出到simuseri_DATA //-----------------------------------------------------------------------void out_simuseri(char data_buf){char i;i=8;ACC=data_buf;do{simuseri_CLK=0;simuseri_DATA=a0;simuseri_CLK=1;ACC=ACC>>1;}while(--i!=0);simuseri_CLK=0;}//-----------------------------------------------------------------------// 函数名称:PA_out// 输入参数:Pseri_out,需要输出的8位数据// 输出参数:无// 功能说明:将Pseri_out中的数据送到74165并行口A-G输出//-----------------------------------------------------------------------void PA_out (char Pseri_out ){drive74165_CLR =0; //并口输出清零drive74165_CLR =1; //开始串行移位out_simuseri(Pseri_out);}。

DATA SHEETProduct specificationFile under Integrated Circuits, IC06December 199074HC/HCT1658-bit parallel-in/serial-out shift registerFor a complete data sheet, please also download:•The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications •The IC06 74HC/HCT/HCU/HCMOS Logic Package Information •The IC06 74HC/HCT/HCU/HCMOS Logic Package OutlinesFEATURES•Asynchronous 8-bit parallel load •Synchronous serial input •Output capability: standard •I CC category: MSI GENERAL DESCRIPTIONThe 74HC/HCT165 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A.The 74HC/HCT165 are 8-bit parallel-load or serial-in shift registers with complementary serial outputs (Q 7and Q 7)available from the last stage. When the parallel load (PL)input is LOW, parallel data from the D 0toD 7inputs are loaded into the register asynchronously.When PL is HIGH, data enters the register serially at the D s input and shifts one place to the right(Q 0→Q 1→Q 2,etc.) with each positive-going clock transition. This feature allows parallel-to-serial converter expansion by tying the Q 7output to the D S input of the succeeding stage.The clock input is a gated-OR structure which allows one input to be used as an active LOW clock enable (CE)input.The pin assignment for the CP and CE inputs is arbitrary and can be reversed for layout convenience. The LOW-to-HIGH transition of input CE should only take place while CP HIGH for predictable operation. Either the CP or the CE should be HIGH before theLOW-to-HIGH transition of PL to prevent shifting the data when PL is activated.APPLICATIONS•Parallel-to-serial data conversionQUICK REFERENCE DATAGND = 0 V; T amb = 25°C; t r = t f = 6 ns Notes1.C PD is used to determine the dynamic power dissipation (P D in µW):P D = C PD ×V CC 2×f i +∑(C L ×V CC 2×f o )where:f i = input frequency in MHz f o = output frequency in MHz ∑(C L ×V CC 2×f o )= sum of outputs C L =output load capacitance in pF V CC =supply voltage in V2.For HC the condition is V I = GND to V CCFor HCT the condition is V I = GND to V CC −1.5 V ORDERING INFORMATIONSee “74HC/HCT/HCU/HCMOS Logic Package Information”.SYMBOL PARAMETERCONDITIONS TYPICAL UNITHCHCTt PHL / t PLHpropagation delay CP to Q 7,Q 7PL to Q 7,Q 7D 7 to Q 7,Q 7C L = 15 pF; V CC = 5 V161511141711ns ns ns f max maximum clock frequency 5648MHz C I input capacitance3.5 3.5pF C PD power dissipation capacitance per packagenotes 1 and 23535pFPIN DESCRIPTIONPIN NO.SYMBOL NAME AND FUNCTION1PL asynchronous parallel load input (active LOW)7Q7complementary output from the last stage9Q7serial output from the last stage2CP clock input (LOW-to-HIGH edge-triggered)8GND ground (0 V)10D s serial data input11, 12, 13, 14, 3, 4, 5, 6D0to D7parallel data inputs15CE clock enable input (active LOW)16V CC positive supply voltageFig.1 Pin configuration.Fig.2 Logic symbol.Fig.3 IEC logic symbol.FUNCTION TABLE Note1.H = HIGH voltage levelh = HIGH voltage level one set-up time prior to the LOW-to-HIGH clock transition L = LOW voltage levelI =LOW voltage level one set-up time prior to the LOW-to-HIGH clock transitionq =lower case letters indicate the state of the referenced output one set-up time prior to theLOW-to-HIGH clock transition X = don’t care↑=LOW-to-HIGH clock transitionOPERATING MODESINPUTS Q n REGISTERS OUTPUTS PLCECPD SD 0-D 7Q 0Q 1-Q 6Q 7Q 7parallel load L L X X X X X X L H L H L - L H - H L H H L serial shift H H L L ↑↑l h X X L H q 0-q 5q 0-q 5q 6q 6q 6q 6hold “do nothing”HH X X X q 0q 1-q 6q 7q 7Fig.4 Functional diagram.Fig.5 Logic diagram.DC CHARACTERISTICS FOR 74HCFor the DC characteristics see“74HC/HCT/HCU/HCMOS Logic Family Specifications”. Output capability: standardI CC category: MSIAC CHARACTERISTICS FOR HCGND = 0 V; t r= t f= 6 ns; C L= 50 pFSYMBOL PARAMETERT amb(°C)UNITTEST CONDITIONS74HCV CC(V)WAVEFORMS +25−40to+85−40to+125min.typ.max.min.max.min.max.t PHL/ t PLH propagation delayCE,CP to Q7,Q7521915165332820541352505043ns 2.04.56.0Fig.6t PHL/ t PLH propagation delayPL to Q7,Q7501814165332820541352505043ns 2.04.56.0Fig.6t PHL/ t PLH propagation delayD7to Q7,Q7361310120242015030261803631ns 2.04.56.0Fig.6t THL/ t TLH output transitiontime 19767515139519161102219ns 2.04.56.0Fig.6t W clock pulse widthHIGH or LOW 801614176510020171202420ns 2.04.56.0Fig.6t W parallel load pulsewidth; LOW 801614145410020171202420ns 2.04.56.0Fig.6t rem removal timePL to CP,CE 1002017228612525211503026ns 2.04.56.0Fig.6t su set-up timeD s to CP,CE 801614114310020171202420ns 2.04.56.0Fig.6t su set-up timeCE to CP;CP to CE 801614176510020171202420ns 2.04.56.0Fig.6t su set-up timeD n to PL 801614228610020171202420ns 2.04.56.0Fig.6t h hold timeD s to CP,CED n to PL 555622555555ns 2.04.56.0Fig.6t h hold timeCE to CPCP to CE 555−17−6−5555555ns 2.04.56.0Fig.6f max maximum clockpulse frequency 630351751615242842024MHz 2.04.56.0Fig.6SYMBOL PARAMETERT amb(°C)UNITTEST CONDITIONS74HCV CC(V)WAVEFORMS +25−40to+85−40to+125min.typ.max.min.max.min.max.DC CHARACTERISTICS FOR 74HCTFor the DC characteristics see“74HC/HCT/HCU/HCMOS Logic Family Specifications”.Output capability: standardI CC category: MSINote to HCT typesThe value of additional quiescent supply current (∆I CC)for a unit load of 1 is given in the family specifications. To determine∆I CC per input, multiply this value by the unit load coefficient shown in the table below.INPUT UNIT LOAD COEFFICIENTD n D s CP CE PL 0.35 0.35 0.65 0.65 0.65AC CHARACTERISTICS FOR 74HCT GND = 0 V; t r= t f= 6 ns; C L= 50 pFSYMBOL PARAMETERT amb(°C)UNITTEST CONDITIONS74HCTV CC(V)WAVEFORMS +25−40to+85−40to+125min.typ.max.min.max.min.max.t PHL/ t PLH propagation delayCE,CP to Q7,Q717344351ns 4.5Fig.6t PHL/ t PLH propagation delayPL to Q7,Q720405060ns 4.5Fig.6t PHL/ t PLH propagation delayD7to Q7,Q714283542ns 4.5Fig.6 t THL/ t TLH output transition time7151922ns 4.5Fig.6t W clock pulse widthHIGH or LOW1662024ns 4.5Fig.6t W parallel load pulsewidth; LOW2092530ns 4.5Fig.6t rem removal timePL to CP,CE2082530ns 4.5Fig.6t su set-up timeD s to CP,CE2022530ns 4.5Fig.6t su set-up timeCE to CP; CP to CE2072530ns 4.5Fig.6t su set-up timeD n to PL20102530ns 4.5Fig.6t h hold timeD s to CP,CE;D n to PL7−1911ns 4.5Fig.6t h hold timeCE to CP, CP to CE0−700ns 4.5Fig.6f max maximum clock pulsefrequency26442117MHz 4.5Fig.6AC WAVEFORMSThe changing to output assumes internal Q6opposite state from Q7.(1)HC: V M= 50%; V I= GND to V CC.HCT:V M= 1.3 V; V I=GND to 3 V.Fig.6Waveforms showing the clock (CP) to output (Q7or Q7) propagation delays, the clock pulse width, the output transition times and the maximum clock frequency.The changing to output assumes internal Q6opposite state from Q7.(1)HC: V M= 50%; V I= GND to V CC.HCT:V M= 1.3 V; V I =GND to 3 V.Fig.7Waveforms showing the parallel load (PL) pulse width, the parallel load to output (Q7or Q7)propagation delays, the parallel load to clock (CP) and clock enable (CE) removal time.(1)HC: V M= 50%; V I= GND to V CC.HCT:V M= 1.3 V; V I=GND to 3 V.Fig.8 Waveforms showing the data input (D n)to output (Q7or Q7)propagation delays when PL is LOW.CE may change only from HIGH-to-LOW while CPis LOW.The shaded areas indicate when the input ispermitted to change for predictable outputperformance.(1)HC: V M= 50%; V I= GND to V CC.HCT:V M= 1.3 V; V I=GND to 3 V.Fig.9Waveforms showing the set-up and hold times from the serial data input (D s)to the clock (CP)and clock enable (CE)inputs, from the clock enable input (CE)to the clock input (CP)and from the clock input (CP) to the clock enable input (CE).(1)HC: V M= 50%; V I= GND to V CC.HCT:V M= 1.3 V; V I=GND to 3 V.Fig.10 Waveforms showing the set-up and hold times from the data inputs (D n)to the parallel load input (PL).PACKAGE OUTLINESSee“74HC/HCT/HCU/HCMOS Logic Package Outlines”.。