《微机原理总线》PPT课件

- 格式:ppt

- 大小:383.00 KB

- 文档页数:14

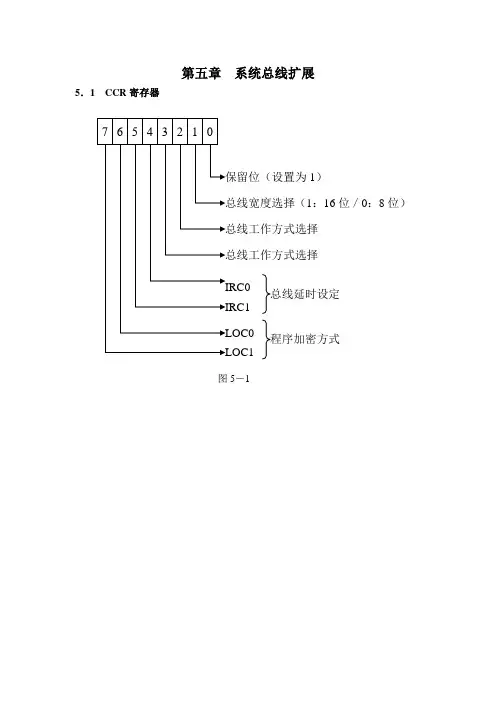

第五章系统总线扩展5.1 CCR寄存器1)1:16位/0:8位)图5-1CCR寄存器的装载过程:当CPU上电或CPU复位后,在10个状态周期的复位序列中,CPU从外部存储器地址为2018H(CCB 芯片配置字节)处,读取内容,然后将此内容装入CCR寄存器。

所以设置CCR寄存器的方法:在外部存储器地址为2018H处,写入CCR寄存器的内容,在CPU上电运行时,CPU自动将此内容装入CCR寄存器中。

CCR.1是总线宽度选择位,选择外部数据总线是8位还是16位(80C196),因为8098只有八条数据线,所以此位因设成0。

CCR.2和CCR.3用来确定总线的工作方式,共有四种总线工作方式只讲述标准总线工作方式。

IRO0,IRO1(CCR.4,CCR.5)用来确定总线等待周期的数量,调整总线的工作速度。

LOC0,IOC1(CCR.6,CCR.7)针对CPU内部有程序存储器的96系列单片机的。

这两位可以对CPU内部程序存储器的内容进行读写保护,防止非法得到程序内容。

对于8098、80C196这种内部无程序存储器的芯片,这两位可以是任意值。

5.2总线的标准工作方式A、地址/数据总线CPU的外部地址/数据总线由P3、P4口构成。

地址线有16条,数据线有八条。

低八位地址线和数据线分时复用。

P3.0~P3.7对应AD0~AD7,P4.0~P4.7对应A8~A15。

分时复用:CPU操作外部地址/数据总线时,先送出相应的16位地址(P3.0~P3.7为低八位,P4.0~P4.7为高八位),然后P3.0~P3.7变成数据总线,送出数据或接收数据,此时P4.0~P4.7仍为高八位地址。

所以分时复用的概念:P3.0~P3.7作为既作为低八位的地址线也作为数据总线,P4.0~P4.7只作为高八位的地址总线。

时序图:P3.0~P3.7地址数据P4.0~P4.7 地址图5-2问题:当CPU的低八位地址/数据总线作为数据总线时,低八位的地址信号就消失了,但对于存储器来说,在整个读写过程中在存储器的地址线上,地址信号必须有效,如何在外部存储器的地址线保存CPU送出的地址信号?解决方法:利用锁存器和ALE信号(地址锁存信号)。