中南大学数字电路知识题与答案解析

- 格式:ppt

- 大小:1.85 MB

- 文档页数:67

中南大学数字电子技术基础期末考试试卷四套附答案Prepared on 21 November 2021中南大学信息院《数字电子技术基础》期终考试试题(110分钟)(第一套)一、填空题:(每空1分,共15分)=+的两种标准形式分别为()、()。

1.逻辑函数Y AB C2.将2004个“1”异或起来得到的结果是()。

3.半导体存储器的结构主要包含三个部分,分别是()、()、()。

4.8位D/A转换器当输入数字量为5v。

若只有最低位为高电平,则输出电压为()v;当输入为,则输出电压为()v。

5.就逐次逼近型和双积分型两种A/D转换器而言,()的抗干扰能力强,()的转换速度快。

6.由555定时器构成的三种电路中,()和()是脉冲的整形电路。

7.与PAL相比,GAL器件有可编程的输出结构,它是通过对()进行编程设定其()的工作模式来实现的,而且由于采用了()的工艺结构,可以重复编程,使它的通用性很好,使用更为方便灵活。

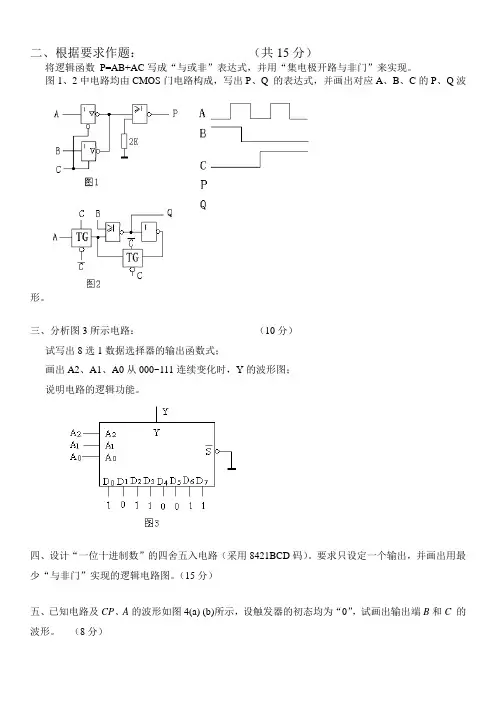

二、根据要求作题:(共15分)1.将逻辑函数P=AB+AC写成“与或非”表达式,并用“集电极开路与非门”来实现。

2.图1、2中电路均由CMOS门电路构成,写出P、Q的表达式,并画出对应A、B、C的P、Q波形。

三、分析图3所示电路:(10分)1)试写出8选1数据选择器的输出函数式;2)画出A2、A1、A0从000~111连续变化时,Y的波形图;3)说明电路的逻辑功能。

四、设计“一位十进制数”的四舍五入电路(采用8421BCD码)。

要求只设定一个输出,并画出用最少“与非门”实现的逻辑电路图。

(15分)五、已知电路及CP、A的波形如图4(a)(b)所示,设触发器的初态均为“0”,试画出输出端B和C的波形。

(8分)BC六、用T触发器和异或门构成的某种电路如图5(a)所示,在示波器上观察到波形如图5(b)所示。

试问该电路是如何连接的?请在原图上画出正确的连接图,并标明T的取值。

(6分)七、图6所示是16*4位ROM和同步十六进制加法计数器74LS161组成的脉冲分频电路。

中南大学数电2试题答案一、选择题1. 在数字逻辑中,一个D触发器可以实现以下哪种功能?A. 边沿触发B. 水平触发C. 电平触发D. 脉冲触发答案:A2. 以下哪个选项是正确的二进制加法规则?A. 0+0=1B. 1+1=10C. 1+0=10D. 0+1=10答案:B3. 在数字电路中,什么是“同步电路”?A. 由组合逻辑电路构成的电路B. 由时序逻辑电路构成的电路C. 由异步触发器构成的电路D. 由同步触发器构成的电路答案:D4. 以下哪个是四变量逻辑函数的标准形式?A. 卡诺图B. 真值表C. 布尔表达式D. 逻辑状态图答案:C5. 一个4位二进制计数器在计数到“1111”时,下一个状态是什么?A. 0000B. 1000C. 1001D. 1100答案:A二、填空题1. 在数字电路中,__________逻辑门可以实现两个输入的逻辑与功能。

答案:AND2. 一个3线到8线译码器的输入端有__________个输入。

答案:33. 触发器的主要特性之一是具有__________功能。

答案:记忆4. 在数字电路设计中,__________是一种用于简化复杂逻辑函数的图形工具。

答案:卡诺图5. 一个计数器的输出在特定时钟周期内的变化序列称为__________。

答案:计数序列三、简答题1. 请简述数字电路与模拟电路的区别。

答:数字电路处理的是离散的信号,通常是二进制形式,它们在特定的逻辑电平上工作,如高电平或低电平。

模拟电路处理的是连续变化的信号,可以在任何电压或电流值之间变化。

数字电路的主要优点是抗干扰能力强,易于实现复杂的逻辑功能,而模拟电路则在处理连续信号,如音频和视频信号方面更为有效。

2. 什么是组合逻辑电路?答:组合逻辑电路是一种数字电路,其输出仅取决于当前的输入值,不依赖于电路之前的状态或输入历史。

这些电路不包含存储元件,如触发器,因此它们没有记忆功能。

组合逻辑电路的示例包括加法器、编码器、解码器和多路选择器。

中南大学信息院《数字电子技术基础》期终考试试题(110分钟)(第一套)一、填空题:(每空1分,共15分)1.逻辑函数Y=AB+C的两种标准形式分别为()、()。

2.将2004个“1”异或起来得到的结果是()。

3.半导体存储器的结构主要包含三个部分,分别是()、()、()。

4.8位D/A转换器当输入数字量10000000为5v。

若只有最低位为高电平,则输出电压为()v;当输入为10001000,则输出电压为()v。

5.就逐次逼近型和双积分型两种A/D转换器而言,()的抗干扰能力强,()的转换速度快。

6.由555定时器构成的三种电路中,()和()是脉冲的整形电路。

7.与PAL相比,GAL器件有可编程的输出结构,它是通过对()进行编程设定其()的工作模式来实现的,而且由于采用了()的工艺结构,可以重复编程,使它的通用性很好,使用更为方便灵活。

二、根据要求作题:(共15分)1.1.将逻辑函数P=AB+AC写成与或非型表达式,并用集电极开路门来实现。

2.2.图1、2中电路均由CMOS门电路构成,写出P、Q的表达式,并画出对应A、B、C的P、Q波形。

三、分析图3所示电路,写出F1、F2的逻辑表达式,说明电路的逻辑功能。

图中所用器件是8选1数据选择器74LS151。

(10分)四、设计一位十进制数的四舍五入电路(采用8421BCD码)。

要求只设定一个输出,并画出用最简与非门实现的逻辑电路图。

(15分)五、已知电路及CP、A的波形如图5(a)(b)所示,设触发器的初态均为“0”,试画出输出端B和C的波形。

(8分)BC六、用T触发器和异或门构成的某种电路如图6(a)所示,在示波器上观察到波形如图6(b)所示。

试问该电路是如何连接的?请在原图上画出正确的连接图,并标明T的取值。

(6分)七、电路如图7所示,其中RA=RB=10kΩ,C=0.1μf,试问:1.在Uk为高电平期间,由555定时器构成的是什么电路,其输出U0的频率f0=? 2.分析由JK触发器FF1、FF2、FF3构成的计数器电路,要求:写出驱动方程和状态方程,列出状态转换表,画出完整的状态转换图;3.设Q3、Q2、Q1的初态为000,Uk所加正脉冲的宽度为T w=6/f0,脉冲过后Q3、Q2、Q1将保持在哪个状态?(共15分)八、图8所示是16*4位ROM和同步十六进制加法计数器74LS161组成的脉冲分频电路。

中南大学数字电子技术基础期末考试试卷四套附答案Document serial number【NL89WT-NY98YT-NC8CB-NNUUT-NUT108】中南大学信息院《数字电子技术基础》期终考试试题(110分钟)(第一套)一、填空题:(每空1分,共15分)=+的两种标准形式分别为()、()。

1.逻辑函数Y AB C2.将2004个“1”异或起来得到的结果是()。

3.半导体存储器的结构主要包含三个部分,分别是()、()、()。

4.8位D/A转换器当输入数字量为5v。

若只有最低位为高电平,则输出电压为()v;当输入为,则输出电压为()v。

5.就逐次逼近型和双积分型两种A/D转换器而言,()的抗干扰能力强,()的转换速度快。

6.由555定时器构成的三种电路中,()和()是脉冲的整形电路。

7.与PAL相比,GAL器件有可编程的输出结构,它是通过对()进行编程设定其()的工作模式来实现的,而且由于采用了()的工艺结构,可以重复编程,使它的通用性很好,使用更为方便灵活。

二、根据要求作题:(共15分)1.将逻辑函数P=AB+AC写成“与或非”表达式,并用“集电极开路与非门”来实现。

2.图1、2中电路均由CMOS门电路构成,写出P、Q的表达式,并画出对应A、B、C的P、Q波形。

三、分析图3所示电路:(10分)1)试写出8选1数据选择器的输出函数式;2)画出A2、A1、A0从000~111连续变化时,Y的波形图;3)说明电路的逻辑功能。

四、设计“一位十进制数”的四舍五入电路(采用8421BCD码)。

要求只设定一个输出,并画出用最少“与非门”实现的逻辑电路图。

(15分)五、已知电路及CP、A的波形如图4(a)(b)所示,设触发器的初态均为“0”,试画出输出端B和C的波形。

(8分)BC六、用T触发器和异或门构成的某种电路如图5(a)所示,在示波器上观察到波形如图5(b)所示。

试问该电路是如何连接的?请在原图上画出正确的连接图,并标明T的取值。

中南大学2016《数字电子技术基础》测试样卷(第一套)一、填空题:(每空1分,共15分)1.逻辑函数的两种标准形式分别为()、()。

2.将2004个“1”异或起来得到的结果是()。

3.半导体存储器的结构主要包含三个部分,分别是()、()、()。

4.8位D/A转换器当输入数字量10000000为5v。

若只有最低位为高电平,则输出电压为()v;当输入为10001000,则输出电压为()v。

5.就逐次逼近型和双积分型两种A/D转换器而言,()的抗干扰能力强,()的转换速度快。

6.由555定时器构成的三种电路中,()和()是脉冲的整形电路。

7.与PAL相比,GAL器件有可编程的输出结构,它是通过对()进行编程设定其()的工作模式来实现的,而且由于采用了()的工艺结构,可以重复编程,使它的通用性很好,使用更为方便灵活。

二、根据要求作题:(共15分)1.将逻辑函数P=AB+AC写成与或非型表达式,并用集电极开路门来实现。

2.图1、2中电路均由CMOS门电路构成,写出P、Q的表达式,并画出对应A、B、C的P、Q波形。

三、分析图3所示电路,写出F1、F2的逻辑表达式,说明电路的逻辑功能。

图中所用器件是8选1数据选择器74LS151。

(10分)四、设计一位十进制数的四舍五入电路(采用8421BCD码)。

要求只设定一个输出,并画出用最简与非门实现的逻辑电路图。

(15分)五、已知电路及CP、A的波形如图5(a)(b)所示,设触发器的初态均为“0”,试画出输出端B和C的波形。

(8分)BC六、用T触发器和异或门构成的某种电路如图6(a)所示,在示波器上观察到波形如图6(b)所示。

试问该电路是如何连接的?请在原图上画出正确的连接图,并标明T的取值。

(6分)七、电路如图7所示,其中RA=RB=10kΩ,C=0.1μf,试问:1.在Uk为高电平期间,由555定时器构成的是什么电路,其输出U0的频率f0=? 2.分析由JK触发器FF1、FF2、FF3构成的计数器电路,要求:写出驱动方程和状态方程,列出状态转换表,画出完整的状态转换图;3.设Q3、Q2、Q1的初态为000,Uk所加正脉冲的宽度为Tw=6/f0,脉冲过后Q3、Q2、Q1将保持在哪个状态?(共15分)八、图8所示是16*4位ROM和同步十六进制加法计数器74LS161组成的脉冲分频电路。

中南大学数字电子技术基础期末考试试卷(四套附答案)中南大学信息院《数字电子技术基础》期终考试试题(110分钟)(第一套)一、填空题:(每空1分,共15分)=+的两种标准形式分别为()、1.逻辑函数Y AB C()。

2.将2004个“1”异或起来得到的结果是()。

3.半导体存储器的结构主要包含三个部分,分别是()、()、()。

4.8位D/A转换器当输入数字量10000000为5v。

若只有最低位为高电平,则输出电压为()v;当输入为10001000,则输出电压为()v。

5.就逐次逼近型和双积分型两种A/D转换器而言,()的抗干扰能力强,()的转换速度快。

6.由555定时器构成的三种电路中,()和()是脉冲的整形电路。

7.与PAL相比,GAL器件有可编程的输出结构,它是通过对()进行编程设定其()的工作模式来实现的,而且由于采用了()的工艺结构,可以重复编程,使它的通用性很好,使用更为方便灵活。

二、根据要求作题:(共15分)1.将逻辑函数 P=AB+AC写成“与或非”表达式,并用“集电极开路与非门”来实现。

2.图1、2中电路均由CMOS门电路构成,写出P、Q 的表达式,并画出对应A、B、C的P、Q波形。

三、分析图3所示电路:(10分)1)试写出8选1数据选择器的输出函数式;2)画出A2、A1、A0从000~111连续变化时,Y的波形图;3)说明电路的逻辑功能。

四、设计“一位十进制数”的四舍五入电路(采用8421BCD码)。

要求只设定一个输出,并画出用最少“与非门”实现的逻辑电路图。

(15分)五、已知电路及CP、A的波形如图4(a) (b)所示,设触发器的初态均为“0”,试画出输出端B和C的波形。

(8分)BC六、用T触发器和异或门构成的某种电路如图5(a)所示,在示波器上观察到波形如图5(b)所示。

试问该电路是如何连接的?请在原图上画出正确的连接图,并标明T的取值。

(6分)七、图6所示是16*4位ROM和同步十六进制加法计数器74LS161组成的脉冲分频电路。

中南大学信息院《数字电子技术基础》期终考试试题(110分钟)(第一套)一、填空题:(每空1分,共15分)=+的两种标准形式分别为1.逻辑函数Y AB C()、()。

2.将2004个“1”异或起来得到的结果是()。

3.半导体存储器的结构主要包含三个部分,分别是()、()、()。

4.8位D/A转换器当输入数字量10000000为5v。

若只有最低位为高电平,则输出电压为()v;当输入为10001000,则输出电压为()v。

5.就逐次逼近型和双积分型两种A/D转换器而言,()的抗干扰能力强,()的转换速度快。

6.由555定时器构成的三种电路中,()和()是脉冲的整形电路。

7.与PAL相比,GAL器件有可编程的输出结构,它是通过对()进行编程设定其()的工作模式来实现的,而且由于采用了()的工艺结构,可以重复编程,使它的通用性很好,使用更为方便灵活。

二、根据要求作题:(共15分)1.将逻辑函数P=AB+AC写成“与或非”表达式,并用“集电极开路与非门”来实现。

2.图1、2中电路均由CMOS门电路构成,写出P、Q 的表达式,并画出对应A、B、C的P、Q波形。

三、分析图3所示电路:(10分)1)试写出8选1数据选择器的输出函数式;2)画出A2、A1、A0从000~111连续变化时,Y的波形图;3)说明电路的逻辑功能。

四、设计“一位十进制数”的四舍五入电路(采用8421BCD码)。

要求只设定一个输出,并画出用最少“与非门”实现的逻辑电路图。

(15分)五、已知电路及CP、A的波形如图4(a) (b)所示,设触发器的初态均为“0”,试画出输出端B和C的波形。

(8分)BC六、用T触发器和异或门构成的某种电路如图5(a)所示,在示波器上观察到波形如图5(b)所示。

试问该电路是如何连接的?请在原图上画出正确的连接图,并标明T的取值。

(6分)七、图6所示是16*4位ROM和同步十六进制加法计数器74LS161组成的脉冲分频电路。

二、根据要求作题:(共15分)将逻辑函数P=AB+AC写成“与或非”表达式,并用“集电极开路与非门”来实现。

图1、2中电路均由CMOS门电路构成,写出P、Q 的表达式,并画出对应A、B、C的P、Q波形。

三、分析图3所示电路:(10分)试写出8选1数据选择器的输出函数式;画出A2、A1、A0从000~111连续变化时,Y的波形图;说明电路的逻辑功能。

四、设计“一位十进制数”的四舍五入电路(采用8421BCD码)。

要求只设定一个输出,并画出用最少“与非门”实现的逻辑电路图。

(15分)五、已知电路及CP、A的波形如图4(a) (b)所示,设触发器的初态均为“0”,试画出输出端B和C的波形。

(8分)BC七、图6所示是16*4位ROM和同步十六进制加法计数器74LS161组成的脉冲分频电路。

ROM中的数据见表1所示。

试画出在CP信号连续作用下的D3、D2、D1、D0输出的电压波形,并说明它们和CP信号频率之比。

(16分)表1:地址输入数据输出A3 A2 A1 A0 D3 D2 D1 D00 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 1 1 1 0 0 0 0 0 0 1 1 0 1 0 00 1 0 11 0 1 0 1 0 0 1 1 0 0 01 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 1 0 0 1 0 0 0 0 1 0 1 0 0 0 1 1 1 0 0 0 0CP波形如图所示:八、综合分析图7所示电路,RAM的16个地址单元中的数据在表中列出。

要求:(1)说明555定时器构成什么电路?(18分)(2)说明74LS160构成多少进制计数器?(3)说明RAM在此处于什么工作状态,起什么作用?(4)写出D\A转换器CB7520的输出表达式(U O与d9~d0之间的关系);(5)画出输出电压U o的波形图(要求画一个完整的循环)。

中南大学2016《数字电子技术基础》测试样卷(第一套)一、填空题:(每空1分,共15分)1.逻辑函数的两种标准形式分别为()、()。

2.将2004个“1”异或起来得到的结果是()。

3.半导体存储器的结构主要包含三个部分,分别是()、()、()。

4.8位D/A转换器当输入数字量10000000为5v。

若只有最低位为高电平,则输出电压为()v;当输入为10001000,则输出电压为()v。

5.就逐次逼近型和双积分型两种A/D转换器而言,()的抗干扰能力强,()的转换速度快。

6.由555定时器构成的三种电路中,()和()是脉冲的整形电路。

7.与PAL相比,GAL器件有可编程的输出结构,它是通过对()进行编程设定其()的工作模式来实现的,而且由于采用了()的工艺结构,可以重复编程,使它的通用性很好,使用更为方便灵活。

二、根据要求作题:(共15分)1.将逻辑函数P=AB+AC写成与或非型表达式,并用集电极开路门来实现。

2.图1、2中电路均由CMOS门电路构成,写出P、Q的表达式,并画出对应A、B、C的P、Q波形。

三、分析图3所示电路,写出F1、F2的逻辑表达式,说明电路的逻辑功能。

图中所用器件是8选1数据选择器74LS151。

(10分)四、设计一位十进制数的四舍五入电路(采用8421BCD码)。

要求只设定一个输出,并画出用最简与非门实现的逻辑电路图。

(15分)五、已知电路及CP、A的波形如图5(a)(b)所示,设触发器的初态均为“0”,试画出输出端B和C的波形。

(8分)BC六、用T触发器和异或门构成的某种电路如图6(a)所示,在示波器上观察到波形如图6(b)所示。

试问该电路是如何连接的?请在原图上画出正确的连接图,并标明T的取值。

(6分)七、电路如图7所示,其中RA=RB=10kΩ,C=0.1μf,试问:1.在Uk为高电平期间,由555定时器构成的是什么电路,其输出U0的频率f0=? 2.分析由JK触发器FF1、FF2、FF3构成的计数器电路,要求:写出驱动方程和状态方程,列出状态转换表,画出完整的状态转换图;3.设Q3、Q2、Q1的初态为000,Uk所加正脉冲的宽度为Tw=6/f0,脉冲过后Q3、Q2、Q1将保持在哪个状态?(共15分)八、图8所示是16*4位ROM和同步十六进制加法计数器74LS161组成的脉冲分频电路。