南京邮电大学软件设计VHDL实验报告

- 格式:doc

- 大小:1.16 MB

- 文档页数:23

湖南科技大学信息与电气工程学院《课程设计报告》题目:电子技术课程设计报告专业:通信工程班级:一班姓名:何家乐学号: 1004040126指导教师:罗朝辉任务书题目《电子技术》课程设计时间安排课程设计时间为10天(2周)。

(1)调研、查资料1天。

(2)总体方案设计2 天。

(3)电路设计2天(画原理图,参数计算)。

(4)实验室完成相应电路的验证。

3天(5)撰写设计说明书 1 天。

(6)验收1 天。

目的:训练学生综合运用学过的电子技术原理的基础知识,独立进行查找资料、选择方案、设计电路、撰写报告,进一步加深对电子电路基本理论的理解,提高运用基本技能的能力,为今后的学习和工作打下坚实的基础。

要求:(1)能正确设计电路,画出线路图,分析电路原理。

(2)按时参加课程设计指导,定期汇报课程设计进展情况。

(3)广泛收集相关技术资料。

(4)独立思考,刻苦钻研,严禁抄袭。

(5)按时完成课程设计任务,认真、正确地书写课程设计报告。

(6)培养实事求是、严谨的工作态度和认真的工作作风。

总体方案实现:(1)明确设计任务,对所要设计的任务进行具体分析,充分了解电路性能、指标内容及要求。

(2)制定设计方案。

(3)迸行具体设计:单元电路的设计;参数计算;器件选择;绘制电路原理图。

(4)撰写课程设计报告(说明书):课程设计报告是对设计全过程的系统总结,也是培养综合科研素质的一个重要环节。

指导教师评语:评分等级:()指导教师签名:课程设计报告1.课题名称:RGB LED Control 原理图及PCB设计2.设计任务及要求⑴任务:完成RGB LED control 的设计,并画出原理图及其PCB设计。

⑵要求:①能正确设计电路,画出线路图,分析电路原理。

②按时参加课程设计指导,定期汇报课程设计进展情况。

③广泛收集相关技术资料。

④独立思考,刻苦钻研,严禁抄袭。

⑤按时完成课程设计任务,认真、正确地书写课程设计报告。

⑥培养实事求是、严谨的工作态度和认真的工作作风。

实验一:3位比较器一、实验目的1、熟悉Xilinx ISE/ModelSim软件,掌握软件的VHDL程序输入、程序编译和程序仿真操作;2、学习利用VHDL语言设计三位比较器控制电路程序;3、根据三位比较器的原理设计VHDL程序,使得a,b为三位信息的输入端口,若a>b 则c=1。

否则c=0;二、VHDL源程序:●Compare3源代码:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity compare3 isport (a:in std_logic_vector(2 downto 0);b:in std_logic_vector(2 downto 0);c:out std_logic);end compare3;architecture Behavioral of compare3 isbeginprocess (a,b)beginif(a>=b)thenc<='1';elsec<='0';end if;end process;end Behavioral;●三位比较器testbench代码:LIBRARY ieee;USE ieee.std_logic_1164.ALL;-- Uncomment the following library declaration if using-- arithmetic functions with Signed or Unsigned values--USE ieee.numeric_std.ALL;ENTITY tbench1 ISEND tbench1;ARCHITECTURE behavior OF tbench1 IS-- Component Declaration for the Unit Under Test (UUT)COMPONENT compare3PORT(a : IN std_logic_vector(2 downto 0);b : IN std_logic_vector(2 downto 0);c : OUT std_logic);END COMPONENT;--Inputssignal a : std_logic_vector(2 downto 0) := "000";signal b : std_logic_vector(2 downto 0) := "000";--Outputssignal c : std_logic;-- No clocks detected in port list. Replace <clock> below with -- appropriate port nameBEGIN-- Instantiate the Unit Under Test (UUT)uut: compare3 PORT MAP (a => a,b => b,c => c);-- Clock process definitions-- Stimulus processstim_proc: processbegin-- hold reset state for 100 ns.wait for 10 ns;a <= "010";b <= "001";wait for 10 ns;a <= "110";b <= "111";wait for 10 ns;a <= "011";b <= "111";wait for 10 ns;a <= "110";b <= "101";wait for 10 ns;a <= "110";b <= "000";wait for 10 ns;a <= "100";b <= "101";wait for 1000 ns;-- insert stimulus herewait;end process;END;三、实验结果与分析●实验仿真波形图●实验结果分析由波形图观察可得该VHDLd代码实现了比较的功能,在输入a,b值大小不同的情况下,成许进行比较均能的出结果并给C赋值,当a>b,c=1, 反之c=0。

vhdl实验报告VHDL实验报告引言:VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,广泛应用于数字电路设计和仿真。

本篇实验报告将介绍我在VHDL实验中的学习和实践经验,包括实验目的、实验过程、实验结果以及对VHDL的理解和展望。

一、实验目的VHDL实验的主要目的是让我们掌握VHDL语言的基本语法和使用方法,能够利用VHDL描述数字电路,并通过仿真和综合工具进行验证和实现。

通过这些实验,我们可以深入了解数字电路的原理和设计方法,提高我们的逻辑设计能力和工程实践能力。

二、实验过程在实验过程中,我们首先学习了VHDL的基本语法,包括实体声明、端口声明、信号声明等。

然后,我们通过实例学习了VHDL的建模方法,包括组合逻辑电路的建模和时序逻辑电路的建模。

在组合逻辑电路的建模中,我们学习了使用逻辑运算符和条件语句描述电路的功能;在时序逻辑电路的建模中,我们学习了使用过程语句和时钟信号描述电路的状态转换。

在学习了VHDL的基础知识后,我们开始进行实验设计。

我们选择了一个简单的数字电路,如4位加法器,来进行实验验证。

首先,我们通过VHDL语言描述了加法器的功能和结构,包括输入端口、输出端口和中间信号。

然后,我们使用仿真工具进行了功能仿真,验证了加法器的正确性。

接着,我们使用综合工具将VHDL代码综合成门级电路,并进行了时序仿真和时序优化,验证了加法器的时序正确性和性能。

三、实验结果通过实验,我们成功地实现了4位加法器的功能,并验证了其正确性和性能。

在功能仿真中,我们输入了不同的测试数据,观察了输出结果,发现加法器能够正确地进行加法运算,并得到了正确的结果。

在时序仿真中,我们观察了电路的时序行为,包括输入信号的变化、输出信号的响应和中间信号的传播延迟等,发现加法器能够在时序上满足要求,并且具有较好的性能。

vhdl设计实验报告VHDL设计实验报告引言VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,广泛应用于数字电路设计和验证。

本实验旨在通过设计一个简单的电路来熟悉VHDL语言的基本语法和设计流程。

一、实验背景数字电路是现代电子系统的基础,而VHDL则是描述和设计数字电路的重要工具。

VHDL可以帮助工程师们以一种形式化的语言来描述电路的功能和结构,从而实现电路的模拟和验证。

二、实验目的本实验的目的是通过使用VHDL语言设计一个简单的电路,加深对VHDL语言的理解,并掌握基本的电路设计流程。

三、实验步骤1. 确定电路功能在设计电路之前,首先需要明确电路的功能。

本实验中,我们选择设计一个4位加法器电路。

2. 设计电路结构根据电路功能的要求,设计电路的结构。

在本实验中,我们需要设计一个4位加法器,因此需要使用4个输入端口和一个输出端口。

3. 编写VHDL代码使用VHDL语言编写电路的描述代码。

在代码中,需要定义输入和输出端口的类型和位宽,并实现电路的功能。

4. 进行仿真使用仿真工具对设计的电路进行仿真,以验证电路的功能是否符合预期。

通过输入不同的测试数据,观察输出是否正确。

5. 下载到FPGA开发板将设计好的电路代码下载到FPGA开发板上进行验证。

通过连接输入信号和观察输出信号,验证电路在实际硬件上的运行情况。

四、实验结果与分析经过仿真和实际验证,我们设计的4位加法器电路在功能上符合预期。

输入不同的数据进行加法运算时,输出结果都正确。

五、实验总结通过本次实验,我们深入了解了VHDL语言的基本语法和设计流程。

通过设计一个简单的电路,我们掌握了VHDL的应用方法,并通过仿真和实际验证,加深了对电路设计的理解。

六、实验心得本实验让我对VHDL语言有了更深入的认识。

通过实际操作,我更加熟悉了VHDL的编写和仿真流程。

实验四————LED数码管显示数字实验内容:在四个七段LED数码管上显示数字“1234”。

实验原理:实现LED数码管数字显示电路的输入和输出端口控制信号如图所示clkLed_bit reset led_seg输入和输出端口信号图中clk信号为50MHz时钟信号。

reset信号为复位按键输入信号,当reset按键按下时,reset信号为低电平。

输出信号led_bit为驱动LED数码管的位码信号,因为有四个LED 数码管,需要四根信号线,控制四个LED数码管中的哪一个LED数码管显示。

输出信号led_seg为驱动LED数码管的段码信号,共有八根信号线,分别是a,b,c,d,e,f,g,dp段,输出信号led_seg能够控制一个LED数码管中的哪一段显示。

四个七段LED数码管的排列如下图所示:四个LED数码管LED数码管采用共阳极发光二极管,如下图所示,需要点亮数码管中的某一段时,应该在对应段的段码信号输出低电平。

共阳极LED数码管由于每个LED数码管有八个发光二极管,八个发光二极管同时导通时需要提供比较大的电流,需要给共阳极加驱动电路,如下图所示,当需要某一LED数码管显示数字时,就给该行的控制信号led_bit(i)提供一个低电平信号。

共阳极LED数码管的阳极驱动电路原理图实验内容:本次实验采用了两个进程:1.scanclk_get:获取扫描时序控制信号2.led_selest_get:选择数码管并显示数字流程图:Clknum scan_cntr reset led_bit<3:0>源代码:library IEEE;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity EXP4_M isport(clk,rst:in std_logic;led_bit:out std_logic_vector(3 downto 0); led_seg:out std_logic_vector(7 downto 0)); end EXP4_M;进程scanclk_get 产生LED 数码管扫描时序控制电路 Led_select_d isplay 进程选择要显示的数据和对应的数码管 七段译码器architecture Behavioral of EXP4_M issignal scanclk:std_logic_vector(17 downto 0);beginscanclk_get:process(clk,rst)beginif rst='0' thenscanclk<=(others=>'0');elsif rising_edge(clk) thenscanclk<=scanclk+1;end if;end process scanclk_get;led_select_display:process(scanclk)begincase scanclk(17 downto 16) iswhen "00" =>led_bit<="1110";led_seg<="10011111" ;when "01"=>led_bit<="1101";led_seg<="00100101" ;when "10"=>led_bit<="1011";led_seg<="00001101" ;when "11"=>led_bit<="0111";led_seg<="10011001" ;when others =>null;end case;end process led_select_display;end Behavioral;UCF文件:net "clk" loc =Y11;net "rst" loc =J3;net "led_bit(0)" loc =M5;net "led_bit(1)" loc =M4;net "led_bit(2)" loc =M3;net "led_bit(3)" loc =M2;net "led_seg(0)" loc =R4;net "led_seg(1)" loc =T3;net "led_seg(2)" loc =T2;net "led_seg(3)" loc =T1;net "led_seg(4)" loc =N4;net "led_seg(5)" loc =N3;net "led_seg(6)" loc =N2;net "led_seg(7)" loc =N1;实验结果:实验箱数码管依次显示“1234”。

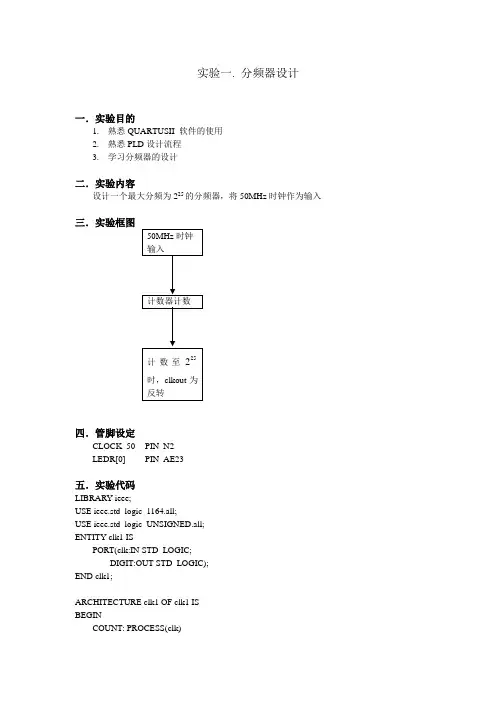

实验一. 分频器设计一.实验目的1.熟悉QUARTUSII 软件的使用2.熟悉PLD设计流程3. 学习分频器的设计二.实验内容设计一个最大分频为225的分频器,将50MHz时钟作为输入三.实验框图四.管脚设定CLOCK_50 PIN_N2LEDR[0] PIN_AE23五.实验代码LIBRARY ieee;USE ieee.std_logic_1164.all;USE ieee.std_logic_UNSIGNED.all;ENTITY clk1 ISPORT(clk:IN STD_LOGIC;DIGIT:OUT STD_LOGIC);END clk1;ARCHITECTURE clk1 OF clk1 ISBEGINCOUNT: PROCESS(clk)V ARIABLE temp:STD_LOGIC_VECTOR(25 DOWNTO 0);BEGINIF(clk'EVENT AND clk = '1')THENtemp := temp+1;IF(temp(25)='1') THENtemp:=(OTHERS=>'0');END IF;END IF;DIGIT <= temp(24);END PROCESS count;END clk1;六.心得体会通过这次实验,我初步掌握了QUARTUSII 软件的使用,为今后的实验打下基础。

实验二. VHDL描述风格比较一.实验目的1.深入体会VHDL三种描述风格的区别2. 学习3输入表决器,异或门的实现3.设计一个5输入表决器。

二.实验内容以3输入表决器,异或门,通用寄存器等代码为例,深入体会VHDL描述风格。

1.学习已给的3输入表决器代码,完成3输入表决器的三种描述方式的验证比较。

在QUARTUS II中对程序进行编译,下载,验证。

使用拔码开关SW0,SW1,SW2作为三个输入,输出在LEDR0表示,亮表示‘1’,不亮表示‘0’2.学习已给的异或门代码,完成异或门的三种描述方式的验证比较。

综合实践总结报告综合实践名称: EDA技术与实践综合实践地点、时间一.题目功能分析和设计实验的要求有如下三点:1.用16*16点阵的发光二极管显示字符;2.可显示字符为0~9的数字字符与A~F英文字母的大写;3.输入为四位二进制矢量;按照要求可知,LED点阵模块,共由16×16=256个LED发光二极管组成,如何在该点阵模块上显示数字和字母是本实验的关键。

先将要显示的每一幅图像画在一个16×16共256个小方格的矩形框中,再在有笔划下落处的小方格里填上“1”,无笔划处填上“0”,这样就形成了与这个汉字所对应的二进制数据在该矩形框上的分布以数字8为例,点阵分布为:0000000000000000000000000000000000011111111110000001111111111000000110000001100000011000000110000001100000011000000111111111100000011111111110000001100000011000000110000001100000011000000110000001111111111000000111111111100000000000000000000000000000000000考虑到实际物理实验平台上点阵发光二极管的原理,以下为16×16点阵LED外观图,只要其对应的X、Y轴顺向偏压,即可使LED 发亮。

例如如果想使左上角LED点亮,则Y0=1,X0=0即可。

所以我采用行列扫描的方法,用四位二进制数做列选信号(总共16列),如选中第一列,则扫描第一列之中哪些行是高电平(1),哪些行是低电平(0);为高电平的则点亮,为低电平的不亮。

(列信号都接地)。

如此,列选信号由“0000”变到“1111”时,16列扫描完毕,一个字也就出来了,列选信号重新由“0000”开始扫描。

注意扫描频率必须要足够快,才能保证显示一个数字或字母时所有灯在肉眼看来是同时在闪烁的。

年月日VHDL实验报告学院专业学号姓名实验1 译码器设计一、实验原理1、译码器是数字系统中常用的组合逻辑电路,常用于地址译码。

74LS138是最常用的一种小规模集成电路,它有3个二进制输入端和8个译码输出端。

表1.1是它的真值表。

表1.1 3-8 译码器真值表2、普通的LED数码管由7段和一个点组成,使用它进行显示,需要译码驱动。

本实验实现一个七段LED显示译码电路。

为了实验方便,在译码之前加入一个4位二进制加法计数器,当低频率的脉冲信号输入计数器后,由7段译码器将计数值译为对应的十进制码,并由数码管显示出来。

图1.1为此电路的原理图。

图1.1 7段LED译码显示电路二、实验内容1、设计一个4-16译码器。

2、设计轮流显示表1.2所示字符的程序。

表1.2 字母显示真值表3、通过仿真,观察设计的正确性。

4、下载、验证设计的正确性。

三、源程序1、4-16译码器。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY decode ISPORT( d0, d1, d2,d3, s1 ,s2 ,s3:IN STD_LOGIC;Y : OUT STD_LOGIC_VECTOR ( 15 DOWNTO 0 ) );END decode;ARCHITECTURE rtl OF decode ISSIGNAL indata : STD_LOGIC_VECTOR ( 3 DOWNTO 0 );BEGINIndata <= d3 & d2 & d1 & d0 ;PROCESS ( indata, s1, s2, s3 )BEGINIF (s1 ='1' AND s2='0' AND s3 = '0' ) THENCASE indata ISWHEN "0000" => Y <= "1111111111111110" ;WHEN "0001" => Y <= "1111111111111101" ;WHEN "0010" => Y <= "1111111111111011" ; WHEN "0011" => Y <= "1111111111110111" ;WHEN "0100" => Y <= "1111111111101111" ;WHEN "0101" => Y <= "1111111111011111" ;WHEN "0110" => Y <= "1111111110111111" ;WHEN "0111" => Y <= "1111111101111111" ;WHEN "1000" => Y <= "1111111011111111" ;WHEN "1001" => Y <= "1111110111111111" ;WHEN "1010" => Y <= "1111101111111111" ; WHEN "1011" => Y <= "1111011111111111" ;WHEN "1100" => Y <= "1110111111111111" ;WHEN "1101" => Y <= "1101111111111111" ;WHEN "1110" => Y <= "1011111111111111" ;WHEN "1111" => Y <= "0111111111111111" ;WHEN OTHERS=> NULL;END CASE;ELSEY <= "1111111111111111" ;END IF;END PROCESS;END rtl;2、轮流显示表1.2所示字符的程序。

VHDL实验报告5090309160 庄炜旭实验三. 4位可逆计数器,4位可逆二进制代码-格雷码转换器设计一.实验目的学习时序电路的设计,仿真和硬件测试,进一步熟悉VHDL设计技术1. 学习4位可逆计数器的设计2. 学习4位可逆二进制代码-格雷码转换器设计二.实验内容设计4位可逆计数器,及4位可逆二进制代码-格雷码转换器,并仿真,下载。

[具体要求]1.4位可逆计数器a)使用CLOCK_50作为输入时钟,其频率为50MHz(对于频率大于50Hz的闪烁,人眼会看到连续的光),因而,对其进行225的分频后,再用于时钟控制。

(可利用实验一)b)使用拨码开关SW17作为模式控制,置‘1’时为加法计数器,置‘0’时为减法计数器,同时使用LEDR17显示SW17的值。

c)使用KEY3作为异步复位开关(按下时为0,不按为1),当为加法计数器时,置“0000”,当为减法计数器时,置“1111”。

d)使用LEDR3,LEDR2,LEDR1,LEDR0作为转换后的输出结果显示,LEDR3为高位,LEDR0为低位。

2.4位可逆二进制代码――格雷码转换器a)使用拨码开关SW17作为模式控制,置‘1’时为二进制代码―>格雷码转换,置‘0’时为格雷码―>二进制代码,同时使用LEDR17显示SW17的值。

b)使用拨码开关SW3, SW2, SW1, SW0作为输入的被转换数,SW3为高位,SW0为低位。

c)使用LEDR3,LEDR2,LEDR1,LEDR0作为转换后的输出结果显示,LEDR3为高位,LEDR0为低位。

三.管脚设定SW[0]PIN_N25SW[1]PIN_N26SW[2]PIN_P25SW[3] PIN_AE14SW[17] PIN_V2LEDR[0] PIN_AE23LEDR[1] PIN_AF23LEDR[2] PIN_AB21LEDR[3] PIN_AC22LEDR[17] PIN_AD12KEY[3] PIN_W26CLOCK_50 PIN_N2四.相关知识二进制代码与格雷码相互转换格雷码(Gray Code,简称G码)是典型的循环码,它是由二进制码(Binary,简称 B 码)导出的。

VHDL数字电路课程实验报告实验一8分频器一、实验要求:分别用信号量和变量实现八分频器二、实验过程:1、代码:8分频器vhdlibrary ieee;use ieee.std_logic_1164.all;entity freq_divider isport(clk: in std_logic;out1, out2: buffer bit);end freq_divider;architecture example of freq_divider issignal count1: integer range 0 to 7;beginprocess(clk)variable count2: integer range 0 to 7;beginif(clk'event and clk='1') thencount1<=count1+1;count2:=count2+1;if(count1=3) thenout1<=not out1;count1<=0;end if;if(count2=4) thenout2<=not out2;count2:=0;end if;end if;end process;end example;八分频器tbLIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY fd_tb isEND fd_tb;architecture behavior of fd_tb iscomponent freq_dividerport(clk:IN STD_LOGIC;out1, out2: buffer bit);end component;signal clk:std_logic;signal out1,out2:bit;beginu1: freq_divider port map(clk,out1,out2);processbeginclk<='0';wait for 50 ns;loopclk<=not clk;wait for 25 ns;end loop;end process;end behavior;2、结果图:实验二实现例8.6一、实验要求:电路只有一个输入时钟信号,输出信号在适中的两个边沿都会发生变化二、实验内容:1、代码信号发生器vhdENTITY signal_gen ISPORT (clk: IN BIT;outp: OUT BIT);END signal_gen;ARCHITECTURE fsm OF signal_gen ISTYPE state IS (one, two, three);SIGNAL pr_state1, nx_state1: state;SIGNAL pr_state2, nx_state2: state;SIGNAL out1, out2: BIT;BEGINPROCESS(clk)BEGINIF (clk'EVENT AND clk = '1') THENpr_state1 <= nx_state1;END IF;END PROCESS;PROCESS (clk)BEGINIF (clk'EVENT AND clk = '0') THENpr_state2 <= nx_state2;END IF;END PROCESS;PROCESS (pr_state1)BEGINCASE pr_state1 ISWHEN one =>out1 <= '0';nx_state1 <= two;WHEN two =>out1 <= '1';nx_state1 <= three;WHEN three =>out1 <= '1';nx_state1 <= one;END CASE;END PROCESS;PROCESS (pr_state2)BEGINCASE pr_state2 ISWHEN one =>out2 <= '1';nx_state2 <= two;WHEN two =>out2 <= '0';nx_state2 <= three;WHEN three =>out2 <= '1';nx_state2 <= one;END CASE;END PROCESS;outp <= out1 AND out2;END fsm;信号发生器tbentity tb_fsm isend tb_fsm;architecture behavior of tb_fsm is component signal_gen isport( clk: in bit;outp: out bit);end component;signal clk,outp:bit;beginu1: signal_gen port map(clk,outp); processbeginclk<='0';wait for 20 ns;loopclk<=not clk;wait for 10 ns;end loop;end process;end behavior;2、结果图实验三常数比较器一、实验要求常数比较器,用于比较的变量位宽应大于等于常数二、实验内容1、代码常数比较器vhdLIBRARY ieee;USE ieee.std_logic_1164.all;entity compare isport(b: in integer range 0 to 15;x1,x2,x3: out std_logic);end compare;architecture compare of compare isconstant a: integer:=10;beginx1<='1' when a>b else '0';x2<='1' when a=b else '0';x3<='1' when a<b else '0';end compare;常数比较器tbLIBRARY ieee;USE ieee.std_logic_1164.all;entity tb_compare isend tb_compare;architecture behavior of tb_compare iscomponent compareport(b: in integer range 0 to 15;x1,x2,x3: out std_logic);end component;signal b: integer;signal x1,x2,x3: std_logic;beginu1: compare port map(b, x1,x2,x3);processbeginb<=5; wait for 10 ns;b<=8; wait for 10 ns;b<=10; wait for 10 ns;b<=13; wait for 10 ns; b<=10; wait for 10 ns; b<=3; wait for 10 ns; end process;end behavior;2、结果图实验四序列检测器一、实验要求序列检测’1001’弱检测到,输出‘1‘,否则输出’0‘二、实验内容1、状态图2、代码序列检测器vhdlibrary ieee;use ieee.std_logic_1164.all;entity string_detector isport(datain,clk: in bit;q: out bit);end string_detector;architecture sd of string_detector istype state is (zero, one, two, three, four);signal pr_state, nx_state: state;beginprocess(clk)beginif(clk'event and clk='1') thenpr_state<=nx_state;end if;end process;process(datain, pr_state)begincase pr_state iswhen zero=>q<='0';if(datain='1') then nx_state<=one;else nx_state<=zero;end if;when one=>q<='0';if(datain='0') then nx_state<=two;else nx_state<=zero;end if;when two=>q<='0';if(datain='0') then nx_state<=three;else nx_state<=zero;end if;when three=>q<='0';if(datain='1') then nx_state<=four;else nx_state<=zero;end if;when four=>q<='1';nx_state<=zero;end case;end process;end sd;序列检测器tb------------------------------------------------------------------ library ieee;use ieee.std_logic_1164.all;------------------------------------------------------------------ entity testBench isend testBench;------------------------------------------------------------------architecture test of testBench iscomponent string_detector isport(datain,clk: in bit;q: out bit);end component;signal datain,clk:bit;signal q:bit;beginSD: string_detector port map(datain,clk,q);processbeginfor i in 0 to 100 loopclk<='0';wait for 10 ns;clk<='1';wait for 10 ns;end loop;end process;processbegindin<='1';wait for 20ns;din<='0';wait for 20ns;din<='0';wait for 20ns;din<='0';wait for 20ns;din<='1';wait for 20ns;din<='0';wait for 20ns;din<='0';wait for 20ns;din<='1';wait for 20ns;din<='0';wait for 20ns;din<='1';wait for 20ns;din<='0';wait for 20ns;end process;end test;3、结果图。

实验一一、实验目的:1、掌握用VHDL 语言和EPLD 进行组合逻辑电路的设计方法。

2、加深对EPLD 设计全过程的理解。

3、掌握组合逻辑电路的静态测试方法。

二、实验设备:1、PC 机2、EDA 实验箱(主芯片是ALTERA EPM7128SLC84-15)。

三、实验内容:1.用VHDL语言设计的四舍五入判别电路,其输入为8421BCD码。

a.程序:library ieee;use ieee.std_logic_1164.all;entity judge isport(a:in std_logic_vector(0 to 3);b:out std_logic);end judge;architecture art of judge isbeginprocess(a)beginif(a<="1001"and a>="0101")thenb<='1';elsif(a<"0101")thenb<='0';elseb<='X';end if;end process;end art;b.运行结果:2.用VHDL语言设计的四个开关控制一盏灯,其中任一开关动作都会导致灯的变化。

a.程序:library ieee;use ieee.std_logic_1164.all;entity xor2 isport(a,b:in std_logic;c:out std_logic);end xor2;architecture artxor2 of xor2 isbeginc<=a xor b;end artxor2;library ieee;use ieee.std_logic_1164.all;entity switch isport(a,b,c,d:in std_logic;q:out std_logic);end switch;architecture art of switch iscomponent xor2 isport(a,b:in std_logic;c:out std_logic);end component xor2;signal tmpa,tmpb:std_logic;beginU1:xor2 port map(a,b,tmpa);U2:xor2 port map(c,d,tmpb);U3:xor2 port map(tmpa,tmpb,q);end art;b.运行结果:其中设开关闭合为1,灯亮为13.用VHDL语言设计优先排队电路,其中A优先级最高,B优先级次高,C优先级最低,并且输出端只有优先级较高的为1。

南京邮电大学课程设计报告设计类别: EDA-VHDL专业名称: 电子信息工程班级学号: b10010910学生姓名: 0基本题 : 矩阵键盘按键的数码管显示综合题 : 信号发生器设计指导教师: 梅中辉日期: 2013年9月15日—9月30日一课题内容:要求学生设计出4*4矩阵键盘对某一按键按下就在数码管显示一个数字。

按键从左上角到右下角依次为1,2, (16)二对选题的理解键盘扫描的实现过程如下:对于4×4键盘,通常连接为4行、4列,因此要识别按键,只需要知道是哪一行和哪一列即可,为了完成这一识别过程,我们的思想是,首先固定输出4行为高电平,然后输出4列为低电平,在读入输出的4行的值,通常高电平会被低电平拉低,如果读入的4行均为高电平,那么肯定没有按键按下,否则,如果读入的4行有一位为低电平,那么对应的该行肯定有一个按键按下,这样便可以获取到按键的行值。

同理,获取列值也是如此,先输出4列为高电平,然后在输出4行为低电平,再读入列值,如果其中有哪一位为低电平,那么肯定对应的那一列有按键按下。

获取到行值和列值以后,组合成一个8位的数据,根据实现不同的编码在对每个按键进行匹配,找到键值后在7段码管显示。

二、获取到行值和列值以后,组合成一个8位的数据,根据实现不同的编码在对每个按键进行匹配,找到键值后在7段码管显示。

三、实现方案系统原理图1234567890A B CDEF弹跳消除电 路键盘译码电 路键盘扫描电路键盘扫描信号键盘输入按键数据数码管显示分频电路弹跳消抖时钟信号键盘扫描时钟信号系统时钟信号3.1.1 矩阵式键盘扫描的工作原理1234567890A B CDEFKY0(00) 1110KY1(01) 1101KY2(10) 1011KY3(11) 0111键盘扫描信号经提升电阻至VCCKX3KX2KX1KX0图3.2 4*4矩阵式键盘的面板配置矩阵式键盘是一种常用的电子输入装置,在平常的生活中,矩阵式键盘在通信设备如手机,信息终端如计算机,家用电器如油烟机等各式电子产品上都具有很重要的作用。

VHDL练习一1、七段译码管设计流程:七段译码管的实现不需要什么运算,和逻辑,只需要设定对应关系就可以。

首先调用ieee库,调用std_logic_1164.all,然后定义实体dec7,包含输入端口clk、data_in,输出端口dec,其中clk是std_logic类型,data_in根据要求是一个整型,输出端口对应到译码管的7段器件,所以是std_logic_vector类型。

接着定义结构体实现功能,进程敏感表为clk,使用case语句分情况输出,默认共阴极译码管,0为亮灯,当输出不在0~9范围时输出中间横线。

备注:一开始使用三位二进制数作为输入,后验证可以使用整型作为输入数据。

验证模块:声明空实体dec7_tb进行测试,将参数定义,并赋初值。

对被测试原件映射,定义时钟周期20ns,时钟进程自循环进行。

主进程验证时随意选取3组数据进行测试结果:结果与设计一致,认为设计成功。

2、十进制计数器设计流程:实体counter10,输入信号reset,up_enable,clk,输出信号bcd(4位),count。

结构体设计,定义信号变量temp(4位),作为可读数,记录当前数字。

当reset有效(当1有效),计数清零,否则当up_enable有效并获得clk上升沿时,计数加1,当计数达到9,count输出一个脉冲并将计数器归零。

完成后将计数器数字输出给bcd。

后来发现可以定义bcd为inout类型,就不需要temp作为中间变量。

验证模块:分别验证计数正确性、count输出、reset功能、up_enable功能。

结果:符合设计目标,计数器到9输出脉冲,up_enable为零时不计数,reset重置。

3、序列检测器设计流程:采用5位移位寄存器实现序列检测,当reset有效,重置寄存器;否则时钟上升沿到来时进行寄存器内容左移并在最低位读入数据,检测当前寄存器内容是否满足要求,是的话输出匹配信号脉冲。

验证模块:验证模块中增加constant std_logic_vector类型的data作为输入码流,预设为16位。

西安电子科技大学实验报告班级:学号:姓名:地点: EⅡ-505 批次:第二批时间:星期五下午、晚上实验一3-8译码器电路设计实验(一)实验名称:3-8译码器电路设计(二)实验目的:1)掌握ISE开发工具的使用,掌握FPGA开发的基本步骤;2)掌握组合逻辑电路设计的一般方法;3)掌握程序下载方法,了解UCF文件的格式;4)初步了解开发板资源,掌握开发板使用方法。

重点了解滑动开关和LED显示灯的使用方法。

5)理解并掌握VHDL程序的结构,掌握输入输出端口的含义;(三)实验内容:(1)用VHDL实现3-8译码器模块译码器电路如图3-1所示。

其功能如表3-1所示。

试用VHDL完成该译码器的设计,并在开发图3-1 74x138 3-8译码器板上进行检验。

(2)将程序下载到FPGA并进行检验●资源使用要求:⏹用滑动开关SW0~SW4作为输入A,B,C,G1;⏹滑动开关BTN_EAST,BTN_WEST作为控制端G2A,G2B;⏹8个LED灯表示8个输出。

●检验方法:当SW0处于OFF(G1=1)或者SW1处于ON(G2A=1)或者SW2处于ON(G2B=1)位置时,所有LED灯灭;当SW0处于ON(G1=1),且BTN_EAST,BTN_WEST均处于OFF状态时,反映当前输入的译码输出在LED灯上显示,即当输入为000(滑动开关SW0-SW2处于OFF状态),LED0亮,其它灯灭,等等。

(四)实验步骤:1)启动ISE,新建工程文件,编写3-8译码器的VHDL模块;2)新建UCF文件,输入位置约束;3)完成综合、实现,生成下载文件;4)连接开发板USB下载线,开启开发板电源;5)下载到FPGA;6)拨动开关,验证结果是否正确。

(五)实验代码:entity decode38 isPort ( A : in STD_LOGIC;B : in STD_LOGIC;C : in STD_LOGIC;G1 : in STD_LOGIC;G2A : in STD_LOGIC;G2B : in STD_LOGIC;Y : out STD_LOGIC_VECTOR (7 downto 0));end decode38;architecture Behavioral of decode38 issignal din: std_logic_vector(2 downto 0);begindin <= C&B&A;PROCESS(din,G1,G2A,G2B)beginif (G1='1' AND G2A='0' AND G2B='0') THENcase din iswhen "000" => Y<="00000001";when "001" => Y<="00000010";when "010" => Y<="00000100";when "011" => Y<="00001000";when "100" => Y<="00010000";when "101" => Y<="00100000";when "110" => Y<="01000000";when "111" => Y<="10000000";when others => Y<="00000000";end case;elsif(G1='0' OR G2A='1' OR G2B='1')THENY <= "00000000";elsenull;end if;end process;end Behavioral;约束性文件NET "A" LOC = "L13" | IOSTANDARD = LVTTL | PULLUP;NET "B" LOC = "L14" | IOSTANDARD = LVTTL | PULLUP;NET "C" LOC = "H18" | IOSTANDARD = LVTTL | PULLUP;NET "G1" LOC = "N17" | IOSTANDARD = LVTTL | PULLUP;NET "Y<7>" LOC = "F9" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8; NET "Y<6>" LOC = "E9" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8; NET "Y<5>" LOC = "D11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8; NET "Y<4>" LOC = "C11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8; NET "Y<3>" LOC = "F11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8; NET "Y<2>" LOC = "E11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8; NET "Y<1>" LOC = "E12" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8; NET "Y<0>" LOC = "F12" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8;NET "G2A" LOC = "H13" | IOSTANDARD = LVTTL | PULLdown;NET "G2B" LOC = "D18" | IOSTANDARD = LVTTL | PULLdown;实验二可逆计数器设计实验(一)实验名称:八位可逆计数器电路设计(二)实验目的:1)进一步熟练ISE 开发工具,巩固FPGA 开发的基本步骤; 2)掌握设计仿真方法;3)掌握时序逻辑电路设计的一般方法,掌握时钟分频程序设计方法; 4)理解VHDL 的层次结构设计,掌握原理图输入方法; 5)巩固程序下载方法;6)了解开发板时钟资源,以及时钟分频方法。

【关键字】实验项目一数据选择器一、实验与设计要求1.熟悉MAX+PLUS II的编译环境,掌握该集成环境各个菜单项的使用;2.了解MAX+PLUSII的VHDL程序设计输入方法,初步了解该软件的仿真环境;3.初步运用VHDL编程,体会硬件描述语言的先进性;4.理解VHDL语言的并发执行的特点;5.熟悉VHDL语法6. 按照如下图示,设计一个四路的数据选择器,该电路能将四组不同的数据有选择的输出,每一组数据的宽度为4,输出那一组数据由选择开关决定,如下表:AB QCDS0S1二、实验与设计方法1.加入MAX+PLUSII软件之前,在E盘上新建一个工作目录\lyung。

2.加入MAX+PLUSII文本编辑器,编写VHDL程序,并保存文件至\lyung\mux41.vhd:3. 将工程指向当前文件并编译当前文件。

4. 建立波形仿真文件,设置输入、输出端口及输入端口的信号波形,保存波形仿真文件。

5. 加入仿真器工作环境,查看波形仿真结果。

6. 选择器件, 为电路端口分配FPGA器件引脚。

7. 进行第二次编译(包括逻辑综合和器件工艺映射),生成目标文件(*.sof等)。

8.将目标文件下载至FPGA器件。

9.在实验台上进行实际操作,验证设计的正确性。

三、实验与设计结果通过实验,初步熟悉了MAX+PLUS II的编译环境,并掌握该集成环境各个菜单项的使用。

实验过程中,了解了MAX+PLUSII的VHDL程序设计输入方法,初步运用VHDL编程,成功的按照实验要求设计了程序的VHDL源码(见附件1),熟悉了VHDL语法,理解了VHDL语言的并发执行的特点;并进行了仿真实验(仿真实验截图见图4-1),初步了解该软件的仿真环境,并成功的将文件烧入实验平台,成功通过了测试(实验平台截图见图4-2)。

四、程序源码及实验截图4-0、VHDL源码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY mux41 ISPORT (a,b,c,d: IN STD_LOGIC_VECTOR (3 DOWNTO 0);s1,s0: IN STD_LOGIC;q: OUT STD_LOGIC_VECTOR (3 DOWNTO 0));END mux41;ARCHITECTURE behave OF mux41 ISSIGNAL sel: STD_LOGIC_VECTOR(1 DOWNTO 0);BEGINsel <= s1 & s0;q<= a WHEN sel="00" ELSEb WHEN sel="01" ELSEc WHEN sel="10" ELSEd WHEN sel="11" ELSE"XXXX";END behave ;图 4-2 实验平台实验项目二三—八译码器一、实验与设计要求1.掌握组合逻辑电路的设计的一般步骤和方法;2.掌握一般电路设计要求及其设计知识;3. 设计一个3-8译码器,此电路有三个输入端(A,B,C),八个输出端D[7··0];当输入为为不同的值(0~7)时,只有对应的输出端才有输出;如下图所示:Y7二、实验与设计方法1.建立真值表2. 编写VHDL语言程序3. 将工程指向当前文件并编译当前文件。

南京邮电大学软件设计VHDL实验报告

通信与信息工程学院

/ 年第 2 学期

软件设计实验报告

模块名称VHDL 专业通信工程

学生班级

学生学号

学生姓名

指导教师梅中辉

设计题目 基本课题:04. 2对4译码器

综合课题:18. 奇偶校验器

任务要求 1.基本课题:设计一个2对4译码器(输入:A B 输出:Y3 Y2

Y1 Y0),真值表如图2。

2. 奇偶校验器系统的功能是对八位二进制数据及其奇偶校验位的

输入进行校验,输出正确的奇、偶校验位。

ODD_IN 与EVEN_IN 是控

制奇校验和偶校验功能输入,IN0到IN7是七位数据及一位校验位

数据输入,IN_READY 表示输入数据已经准备好,能够处理,当

OUT_REQ 输入表示要求输出数据,CLK 端口用于接收时钟信号,支

持系统的时钟上升沿同步。

当输出端口OUT_READY 输出信号有效

时,表示输出数据已经准备好,能够为下级电路使用,ODD_OUT 与

EVEN_OUT 用来输出正确的奇偶校验位。

上述控制端口均为高电平有

效。

A B Y3 Y2 Y1 Y0 0 0 0 1 1 0 0 1 1 1 1 0 1 1 0 1 1 0 1 1 0 1 1 1 实验设备及软件

1. 微型计算机 2. EDA-VHDL 开发软件

同组人员学号及姓

名

11001803 胡雪琪

参考文献 1. 张顺兴 《数字电路与系统设计》东南大学出版社 .8

2. 苗丽华《VHDL 数字电路设计教程》人民邮电出版社 .11 VHDL

课程设计题目及要求(自编资料)

3. VHDL 课程设计题目及要求(自编资料)

4. 杨晓慧 杨永健 《基于FPGA 的EDA/SOPC 技术与VHDL 》 国防工

业出版社 .7

5. Peter J. Ashenden 《The VHDL Cookbook 》Dept. Computer

Science University of Adelaide South Australia July,

1990

报告内容

一. 实验目的

1.掌握组合逻辑中译码器电路的设计原理。

2.能利用VHDL 语言设计一个2-4译码器。

二. 实验器件

1.微型计算机

2.EDA-VHDL 开发软件

三. 实验名称

2-4译码器

四. 题目要求概述

设计一个2对4译码器(输入:A B 输出:Y3 Y2 Y1 Y0),真值表如图

五. 系统分析

○

1.原理图:

分析:EN=1,Z[0]=Z[1]=Z[2]=Z[3]=1;

EN=0,Z[0]=!(!A!B ),Z[1]=!(!AB),Z[2]=!(A!B),Z[3]=!AB

○

2.设计算法: A B Y3 Y2 Y1 Y0 1 0 0 1 1 0 0 1 1 1 1 0 1 1 0 1 1 0 1 1 0 1 1 1

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY XiaoLi IS --定义实体名称为XiaoLi

PORT( EN:IN STD_LOGIC; --定义输入/输出端口a:IN STD_LOGIC_VECTOR(1 DOWNTO 0);

y:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END XiaoLi;

ARCHITECTURE dataxl OF XiaoLi IS

BEGIN

PROCESS(EN,a)

BEGIN

IF(EN='0')THEN

CASE a IS --用CASE语句进行译码

WHEN "00"=>y<="1110";

WHEN "01"=>y<="1101";

WHEN "10"=>y<="1011";

WHEN "11"=>y<="0111";

WHEN OTHERS=>y<="0000";

END CASE;

ELSE y<="1111";

END IF;

END PROCESS;

END dataxl;

○3设计要点:

1. 2-4译码器有一个使能端EN,低电平有效,因此要用到IF语句分情况处理,当EN=1时,输出全为逻辑1;当EN=0时,在使能下对输入进行译码输出。

2. 在2-4译码器中,要求根据相应的输入译码得到相应的输出,这需要用到CASE语句,根据满足的条件直接选择相应的顺序语句执行。

然后根据题目要求进行设置。

六.逻辑仿真图及功能分析

逻辑仿真图:

功能分析:EN=1时,y[0..3]=1111

EN=0时,a[0..1]=00,y[0..3]=1110

a[0..1]=01,y[0..3]=1101

a[0..1]=10,y[0..3]=1011

a[0..1]=11,y[0..3]=0111

七.时序仿真及分析

时序仿真:

EN=0

EN=1

分析:EN=1时,y3y2y1y0=111

EN=0时,a1a0=00,y3y2y1y0=1110; a1a0=01, y3y2y1y0=1101;

a1a0=10,y3y2y1y0=1011; a1a0=11,y3y2y1y0=0111.

五.调试过程与问题

1.创立工程:

在File/NewProjectWizard里输入工程路径作为当前的工作目录,工程名和顶层文件实体名为必须相同设为XiaoLi。

其中目标器件选取Altera公司Cyclone2的EP2C8T144C8。

2建立文本/编辑文件:

在File/New里选取VHDL File文件类型,输入相应代码后保存文件,要保存在已建立的文件夹里,存盘文件名要与实体名保持一致,即XiaoLi.vhd。

若不一致,在编译过程中会出现错误,在顶层文件中找不到要编译的文件。

3编译综合:

执行Processing/Compiler Tool,启动编译器,编译成功后显示编译报告。

选择Tool/Netlist Viewer/Technology Map Viewer观察生成后的门级电路原理图。

对于不同的目标器件,尽管逻辑功能一样,可是其门级电路的结构是不一样。

2-4译码器综合后的门级电路原理图:。