CPLD实验指导书

- 格式:pdf

- 大小:2.02 MB

- 文档页数:73

实验一基本门电路的设计[实验目的]1.学习MAX+PLUSII 软件的基本操作;2.学习使用原理图、文本文件进行设计输入;3.初步掌握器件设计、编译、仿真和编程的过程;4.学习掌握教学实验板的使用方法;4.学习掌握基本门电路的设计方法;[实验说明]基本门电路主要用来实现基本的输入/输出之间的逻辑关系,包括与门、或门、非门、与非门、或非门、异或门、同或门灯,下面为2输入端与非门的基本门电路的设计。

2输入端与非是组合逻辑电路中的基本逻辑器件,有2个输入端A、B和1个输出端Y。

其真值表如表所示。

2输入端与非门应具备的脚位:输入端:A、B;输出端:Y。

[实验要求]1用原理图方法实现2输入与非门2用VHDL语言实现2输入与非门3设计仿真文件,进行软件验证4通过下载线下载到实验板上进行验证[实验报告要求]1画出原理图2写出VHDL编程语言源文件3给出软件仿真和硬件测试结果4通过下载线下载到实验板上进行验证5写出学习总结附:1.原理图输入与非门原理图输入法的操作步骤介绍如下。

(1)建立新文件:选取窗口菜单File-New,出现对话框,选择Graphic Editor file选项,单击OK按钮,进入图形编辑画面。

(2)保存:选取窗口菜单File-Save,出现对话框,键入文件名nand2.gdf,单击OK按钮(3)指定项目名称,要求与文件名相同:选取窗口菜单File-Project-Name,键入文件名nand2,单击OK按钮。

(4)确定对象的输入位置:在图形窗口内单击鼠标左键。

(5)引入逻辑门:选取窗口菜单Symbol-Enter Symbol,在\Maxplus2\max2lib\prim处双击,在Symbol File菜单中选取NAND2逻辑门,单击OK按钮。

(6)引入输入和输出脚:按步骤(5)选出2个输入端和1个输出脚。

(7)更改输入和输出脚的脚位名称:在PIN_NAME处双击鼠标左键,进行更名,输入脚位A、B,输出脚为Y。

《可编程逻辑器件与应用专题》讲义附实验指导书清华大学电子工程系第一章绪论§1.1 可编程ASIC综述为特定的产品或应用而设计的芯片被称为专用集成电路ASIC(Application Specific Integrated Circuits),除了全定制的专用集成电路外,目前有五种半定制的元件,可实现ASIC的要求,它们是:*可编程逻辑器件(PLD)*复杂可编程逻辑器件(CPLD)*现场可编程门阵列(FPGA)*门阵列(Gate Array)*标准单元(Standard Cell)在这些器件中,尤其是前三种器件的出现,使得电子系统的设计工程师利用相应的EDA软件,在办公室或实验室里就可以设计自己的ASIC器件,其中近几年发展起来的CPLD和FPGA格外引人注目。

这三种器件都具有用户可编程性,能实现用户需要的各种专门用途,因此被称作可编程专用集成电路。

半导体制造厂家可按照通用器件的规格大批量生产这种集成电路,作为一种通用集成电路,用户可以从市场上选购,再通过设计软件编程实现ASIC的要求。

由于这种方式对厂家和用户都带来了好处而受到欢迎,因此发展特别迅速,已经成为实现ASIC的一种重要手段。

随着半导体技术的迅速发展,从八十年代开始,构造许多电子系统仅仅需要三种标准电路:微处理器,存储器和可编程ASIC。

电子系统设计的这场革命是从70年代开始的,当时存储器已经作为标准产品进入市场,而80年代的微处理器也成为一种标准产品。

值得注意的是,微处理器和存储器作为电子系统的两个主要模块,一直都是可编程的。

但是组成电子系统的各种控制逻辑仍然需要大量的中小规模通用器件。

直到近十年来,随着可编程逻辑器件的出现,才给电子系统的控制逻辑提供了可编程的灵活性。

而可编程门阵列作为一种高密度,通用的可编程逻辑器件与它的开发系统一起为更多的电子系统逻辑设计确定了一种新的工业标准。

越来越多的电子系统设计工程师用CPLD或FPGA作为电子系统设计的第三个模块来实现一个电子系统。

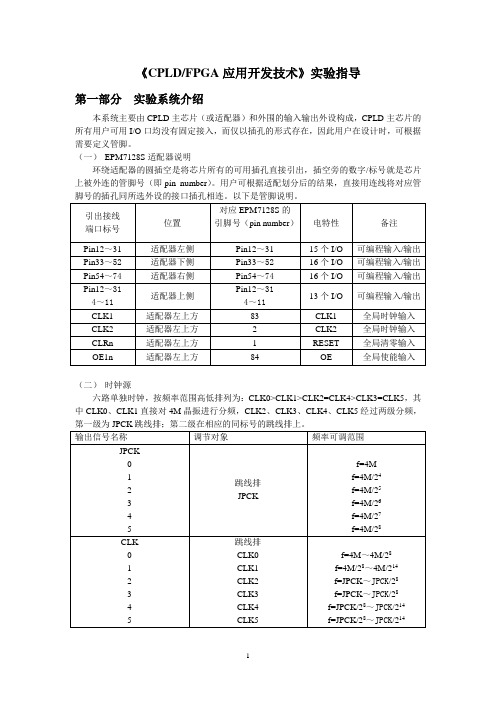

《CPLD/FPGA应用开发技术》实验指导第一部分实验系统介绍本系统主要由CPLD主芯片(或适配器)和外围的输入输出外设构成,CPLD主芯片的所有用户可用I/O口均没有固定接入,而仅以插孔的形式存在,因此用户在设计时,可根据需要定义管脚。

(一)EPM7128S适配器说明环绕适配器的圆插空是将芯片所有的可用插孔直接引出,插空旁的数字/标号就是芯片上被外连的管脚号(即pin number)。

用户可根据适配划分后的结果,直接用连线将对应管脚号的插孔同所选外设的接口插孔相连。

以下是管脚说明。

(二)时钟源六路单独时钟,按频率范围高低排列为:CLK0>CLK1>CLK2=CLK4>CLK3=CLK5,其中CLK0、CLK1直接对4M晶振进行分频,CLK2、CLK3、CLK4、CLK5经过两级分频,第一级为JPCK跳线排;第二级在相应的同标号的跳线排上。

(三)普通输入输出器件接口主要为开关、LED灯。

1、按键开关:不按为“1”,按下为“0”。

2、拨码开关:拨上为“1”,拨下为“0”。

3、LED灯:输入高电平亮、输入低电平灭。

(四)扫描类接口外设1、8位七段数码管共阴极数码管,字形输入为a、b、c、d、e、f、g、Dp。

对应标准数码管的七个段位和一个小数点,高电平有效。

[SEL2,SEL1,SEL0]译码后确定哪一位数码管被点亮;若同时显示,只需要产生[SEL2,SEL1,SEL0]信号的时钟足够快(>100Hz)。

其操作类似于向8*8bit存储器中写数据。

2、16*16LED点阵(1)[L0~L15]对应点阵的行输入、高电平有效。

(2)[SEL3,SEL2,SEL1,SEL0]译码后为点阵列选通,决定哪一列被点亮。

若同时显示,只要产生循环地址信号的时钟足够快。

其操作类似于向16*16bit存储器中写数据。

(五)EEPROM(2864)D0~D7:EEPROM数据端A0~A12: 地址输入端/WE: 写使能,“0”有效/OE: 读使能,“0”有效/CE: 片选第二部分实验内容实验一组合逻辑电路的设计一、实验目的:1、掌握用VHDL语言和EPLD进行组合逻辑电路的设计方法。

数字电子系统设计(CPLD)实验指导书中国矿业大学电工电子教学实验中心2001年11月目录第一部分CPLDEE实验开发系统及配套软件简介第一节CPLDEE实验开发系统简介第二节CPLDDN下载软件简介第二部分数字电子系统设计实验实验一简单逻辑电路设计与仿真实验二译码与寄存器电路设计与仿真实验三全加器设计、仿真与下载实验四分频程序设计与12归1电路实验五利用硬件描述语言进行数字钟设计实验六串形扫描显示电路设计实验七BCD码转换电路设计实验八数据采集与显示电路设计实验九LPM使用及8*8乘法器的设计实验十CPLD间串行通信(单工)综合实验一数字系统设计与单片机接口实验一综合实验二数字系统设计与单片机接口实验二综合实验三数字系统设计与单片机接口实验三综合实验四数字系统设计与单片机接口实验四综合实验五数字系统设计与单片机接口实验五综合实验六CPLD与计算机双工串行通信实验综合实验七CPLD与计算机并行口通信实验第一部分 CPLDEE实验开发系统及配套软件简介第一节CPLDEE实验开发系统简介目前,随着大规模可编程器件在市场上的应用越来越广泛,各高校都相继开出了这门课程,为了配合高校EDA技术的教学、实验以及科研人员的设计开发,我们推出了CP LDEE--4系列实验开发装置。

本实验装置是在世界银行贷款招标标书要求的基础上设计并有所突破,广泛适用于教学和科研,面向本科教育、研究生教育及科研开发。

1.系统基本特征●配备:本实验箱配有三家公司(altera低电压1k系列(3万门以上)、lattice的ispLS I1032E—70LJ84、xilinx的xc95108系列)芯片下载板,适用范围广泛。

●资源:芯片门数最多达到10万门(ACEX1K100),管脚可达208脚。

●编辑方式有图形编辑,文本编辑,波形编辑,混合编辑等方式,硬件描述语言有AHDL,VHDL,Verilog-HDL等语言。

●主板功能:✧配有模拟可编程器件ispPAC器件系列,突破传统的EDA实验箱一般只做数字电路实验的模式,用户可以在实验箱上通过的模拟可编程器件进行模拟电子的开发训练。

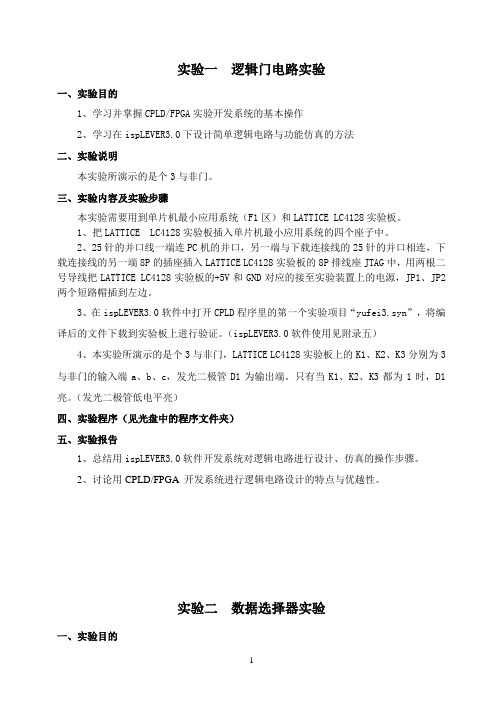

实验一逻辑门电路实验一、实验目的1、学习并掌握CPLD/FPGA实验开发系统的基本操作2、学习在ispLEVER3.0下设计简单逻辑电路与功能仿真的方法二、实验说明本实验所演示的是个3与非门。

三、实验内容及实验步骤本实验需要用到单片机最小应用系统(F1区)和LATTICE LC4128实验板。

1、把LATTICE LC4128实验板插入单片机最小应用系统的四个座子中。

2、25针的并口线一端连PC机的并口,另一端与下载连接线的25针的并口相连,下载连接线的另一端8P的插座插入LATTICE LC4128实验板的8P排线座JTAG中,用两根二号导线把LATTICE LC4128实验板的+5V和GND对应的接至实验装置上的电源,JP1、JP2两个短路帽插到左边。

3、在ispLEVER3.0软件中打开CPLD程序里的第一个实验项目“yufei3.syn”,将编译后的文件下载到实验板上进行验证。

(ispLEVER3.0软件使用见附录五)4、本实验所演示的是个3与非门,LATTICE LC4128实验板上的K1、K2、K3分别为3与非门的输入端a、b、c,发光二极管D1为输出端。

只有当K1、K2、K3都为1时,D1亮。

(发光二极管低电平亮)四、实验程序(见光盘中的程序文件夹)五、实验报告1、总结用ispLEVER3.0软件开发系统对逻辑电路进行设计、仿真的操作步骤。

2、讨论用CPLD/FPGA 开发系统进行逻辑电路设计的特点与优越性。

实验二数据选择器实验一、实验目的1、掌握CPLD/FPGA实验开发系统的操作技巧2、掌握用ISPLEVER3.0进行一般数字逻辑电路的设计方法3、学习CPLD/FPGA芯片下载与实验基本方法二、实验说明通过电平开关设置待选择的数据,由发光二极管显示。

三、实验内容及步骤本实验需要用到单片机最小应用系统(F1区)和LATTICE LC4128实验板。

1、把LATTICE LC4128实验板插入单片机最小应用系统的四个座子中。

C P L D课程设计指导手册(测控专业)编制:王宗省2012年6月20日CPLD课程设计是继随堂实验课之后的实践教学单元,是学生将所学可编程器件的理论、知识要点、技术要点、编程方法等运用于实践的第二个步骤,是可编程器件课程的重要教学环节。

为规范本课程设计的各组成部分,使学生通过本课程设计,能在意识上建立理论与实践相连接的通道,切实达到能综合运用课本所学知识并将其转换为解决实际问题的利器的目的,特此编制本课程设计指导书。

本指导手册适用于测控专业本科学生。

目录一、性质、目的与任务 (4)二、主要内容 (4)三、课程设计报告的要求及主要内容 (6)四、时间安排 (6)五、纪律 (7)六、评分标准 (7)七、参考文献与说明 (7)一、 性质、目的与任务CPLD课程设计是继随堂实验课之后的实践教学单元,是学生将所学可编程器件的理论、知识要点、技术要点、编程方法等运用于实践的第二个步骤,是可编程器件课程的重要教学环节。

二、 主要内容1、数字时钟要求:(1) 计时天、时、分、秒;(2) 用8位数码管显示时间,相互间用DP间隔;(3) 可以手动设置时间;(4) 设定定时功能(提高)。

2、交通灯控制要求:(1) 东西方向黄灯,南北方向红灯,10秒后,东西方向转换为红灯,南北方向转换为绿灯;(2) 东西方向红灯,南北方向绿灯,45秒后,南北方向转换为黄灯;(3) 南北方向黄灯,东西方向红灯,10秒后,南北方向转换为红灯,东西方向转换为绿灯;(4) 南北方向红灯,东西方向绿灯,45秒后,东西方向转换为黄灯;(5) 依次循环;(6) 计时时间用两位数码管显示;(7) 为了在紧急情况下保证通行安全,可以手动设置路口全为红灯。

3、键盘输入显示要求:(1) 设计一个20键盘的键盘,用行列扫描的方式读取按键;(2) 设定一个开关,当该开关接高电平时,将按键所对应的编码按10进制用两位数码管显示;(3) 当上述开关接低电平时,将按键所对应的编码按16进制用两位数码管显示。

可编程逻辑系统的VHDL设计技术ဣ!ዩ!ᒎ!ࡴ!ၗ!VHDLForPROGRAMMABLELOGIC启东市微机应用研究所Qidong Microcomputer Institute目 录前言 (1)第一章 CPLD可编程数字逻辑实验系统1.1 实验系统硬件配置........................................................................... (1)1.2 实验系统软件配置........................................................................... (1)第二章 PLD器件简介2.1 PLD器件概述 (2)2.1.1 数字器件的分类........................................................................ (2)2.1.2 PLD器件的基本结构和基本工作原理 .......................................... (3)2.1.3 PLD器件开发的一般过程............................................................... (4)2.2 Xilinx公司芯片XC系列器件介绍 ................................................... (4)第三章 ISE 4.1i快速入门3.1 Xilinx 的ISE集成软件环境概述 (8)3.2 Xilinx 的ISE集成软件使用 (9)3.2.1 设计输入(Design Entry Utilities) ........................... ............ (9)3.2.2 综合(Synthesize) (13)3.2.3 设计实现(Implement Design ) ... (15)3.2.4 设计文件的产生及下载(Generate Programming File) (16)第四章 VHDL语言简介4.1 设计实体 ......... (17)4.1.1 实体说明.................. ................................................... ............ (17)4.1.2 构造体 (18)4.2 标识符、数据对象、数据类型及属性... ...... .......................................... (21)4.2.1 标识符.......................................... ......... ................................. (21)4.2.2 数据对象............................................. ......... ........................... (21)4.2.3 数据类型 (23)4.2.4 属性........................................................................ ............... (25)4.3 组合和同步逻辑的设计.................................... ......... ...... (25)4.3.1 组合逻辑...................................................... ........................... (25)4.3.2 同步逻辑................................................ ................................. (27)4.3.3 FIFO缓冲器...................................................... (29)4.4 运算符............................................................... .............................. (29)4.4.1 逻辑运算符...................................................... ... ..................... (29)4.4.2 算术运算符................................. ...... ..................... .................. (29)4.4.3 关系运算符............................................. ............... .................. (30)4.4.4 移位运算符................................. ..................... ........................ (30)第五章 编程实验5.1 实验系统使用须知................................. .......................................... (31)5.2 实验......................................................... .................................... (31)5.2.1 74系列门电路.......................................... ...... (31)5.2.2 译码器及编码器................................. ............ ........................... (37)5.2.3 计数器....................................... ..................... ........................ (43)5.2.4 加法器............................................. ............ ........................... (45)5.2.5 移位寄存器................................................... ...... ........................ (47)5.2.6 通用寄存器............................................. ......... ........................ (53)5.2.7 总线缓冲驱动器....................................... ............ ..................... (55)5.2.8 点阵LED实验................................................ ............... ......... (62)前言用于传统数字系统设计的基本器件主要为标准逻辑器件,如TTL74系列、CMOS4000系列。

实验一CPLD可编程数字信号发生器实验 (1)实验十眼图实验 (6)实验七振幅键控(ASK)调制与解调实验 (9)实验八FSK移频键控调制与解调实验 (15)实验十一载波同步提取实验 (29)实验十二位同步提取实验 (35)实验十四载波传输系统实验 (53)实验十五数字基带传输系统实验 (55)实验一CPLD 可编程数字信号发生器实验一、实验目的1、熟悉各种时钟信号的特点及波形。

2、熟悉各种数字信号的特点及波形。

二、实验内容1、熟悉CPLD 可编程信号发生器各测量点波形。

2、测量并分析各测量点波形及数据。

3、学习CPLD 可编程器件的编程操作。

三、实验器材1、信号源模块一块2、连接线若干3、20M 双踪示波器一台四、实验原理CPLD 可编程模块用来产生实验系统所需要的各种时钟信号和各种数字信号。

它由CPLD可编程器件ALTERA 公司的EPM240T100C5、下载接口电路和一块晶振组成。

晶振JZ1 用来产生系统内的32.768MHz 主时钟。

1、CPLD 数字信号发生器包含以下五部分:1) 时钟信号产生电路将晶振产生的32.768MHZ 时钟送入CPLD 内计数器进行分频,生成实验所需的时钟信号。

通过拨码开关S4 和S5 来改变时钟频率。

有两组时钟输出,输出点为“CLK1”和“CLK2”,S4 控制“CLK1”输出时钟的频率,S5 控制“CLK2”输出时钟的频率。

2) 伪随机序列产生电路通常产生伪随机序列的电路为一反馈移存器。

它又可分为线性反馈移存器和非线性反馈移存器两类。

由线性反馈移存器产生出的周期最长的二进制数字序列称为最大长度线性反馈移存器序列,通常简称为m序列。

3) 帧同步信号产生电路信号源产生8K 帧同步信号,用作脉冲编码调制的帧同步输入,由“FS”输出。

4) NRZ 码复用电路以及码选信号产生电路码选信号产生电路:主要用于8 选 1 电路的码选信号;NRZ 码复用电路:将三路八位串行信号送入CPLD,进行固定速率时分复用,复用输出一路24 位NRZ 码,输出端口为“NRZ”,码速率由拨码开关S5 控制,对应关系见表1-2。

数字电子系统设计(CPLD)实验指导书中国矿业大学电工电子教学实验中心2001年11月目录第一部分CPLDEE实验开发系统及配套软件简介第一节CPLDEE实验开发系统简介第二节CPLDDN下载软件简介第二部分数字电子系统设计实验实验一简单逻辑电路设计与仿真实验二译码与寄存器电路设计与仿真实验三全加器设计、仿真与下载实验四分频程序设计与12归1电路实验五利用硬件描述语言进行数字钟设计实验六串形扫描显示电路设计实验七 BCD码转换电路设计实验八数据采集与显示电路设计实验九 LPM使用及8*8乘法器的设计实验十 CPLD间串行通信(单工)综合实验一数字系统设计与单片机接口实验一综合实验二数字系统设计与单片机接口实验二综合实验三数字系统设计与单片机接口实验三综合实验四数字系统设计与单片机接口实验四综合实验五数字系统设计与单片机接口实验五综合实验六 CPLD与计算机双工串行通信实验综合实验七 CPLD与计算机并行口通信实验第一部分 CPLDEE实验开发系统及配套软件简介第一节CPLDEE实验开发系统简介目前,随着大规模可编程器件在市场上的应用越来越广泛,各高校都相继开出了这门课程,为了配合高校EDA技术的教学、实验以及科研人员的设计开发,我们推出了CP LDEE--4系列实验开发装置。

本实验装置是在世界银行贷款招标标书要求的基础上设计并有所突破,广泛适用于教学和科研,面向本科教育、研究生教育及科研开发。

1.系统基本特征●配备:本实验箱配有三家公司(altera低电压1k系列(3万门以上)、lattice的ispLS I1032E—70LJ84、xilinx的xc95108系列)芯片下载板,适用范围广泛。

●资源:芯片门数最多达到10万门(ACEX1K100),管脚可达208脚。

●编辑方式有图形编辑,文本编辑,波形编辑,混合编辑等方式,硬件描述语言有AHDL,VHDL,Verilog-HDL等语言。

●主板功能:✧配有模拟可编程器件ispPAC器件系列,突破传统的EDA实验箱一般只做数字电路实验的模式,用户可以在实验箱上通过的模拟可编程器件进行模拟电子的开发训练。