半导体存储器及接口

- 格式:ppt

- 大小:3.39 MB

- 文档页数:108

第五章半导体存储器一.填空题1.某CPU 有20条地址总线,则寻址主存最大空间为________。

若其中128K×8存储空间全部由8K×8的EPROM 答案:1024K;162.对于SRAM,容量位16K×8的芯片共有________条地址线和________条数据线。

答案:14;83.采用局部片选译码片选法,如果有3条地址线不参加译码,将会产生________倍空间重叠。

答案:8二.选择题1.对于SRAM,容量为32KB 的芯片需()根地址线。

CA.12B.14C.15D.162.在CACHE-主存层次中的替换法是由()实现的;对虚拟存储器的控制是由()完成的。

A;CA.硬件B.软件C.软硬件D.外部设备3.主存和CPU 之间增加高速缓存的目的是()。

CA.扩大主存容量、提高速度B.解决主存和外存之间的速度匹配C.解决CPU 和主存之间的速度匹配D.解决CPU 和外存之间的速度匹配4.某计算机字长16位、存储容量64KB,若按字编址,则它的寻址范围是()。

BA.0~64KB.0~32KC.0~64KBD.0~32KB5.某一容量为512×8位的RAM 芯片,除电源端和接地端外,该芯片引出线的最小数目应为()个。

DA.9B.12C.17D.196.一EPROM 芯片的地址范围为30800H~30FFFH 无地址重叠,则该芯片的存储容量为()。

BA.1KBB.2KBC.4KBD.8KB1.一台微机具有4KB 的连续存储区,其存储空间首地址为4000H,则末地址为()。

AA.4FFFHB.5000HC.7FFFHD.8000H三.分析题1.有一2732EPROM 芯片的译码电路如图8所示,请计算该芯片的地址范围及存储容量A 11A 12A 13A 14A 15A 19地址范围:FF000H~FFFFFH存储容量:4KB第六章I/O接口技术一.填空题1.CPU通过一个外设接口同外设之间交换的信息包括数据信息、状态信息和______,这三个信息通常都是通过CPU的______总线来传送到。

第七章 半导体存储器数字信息在运算或处理过程中,需要使用专门的存储器进行较长时间的存储,正是因为有了存储器,计算机才有了对信息的记忆功能。

存储器的种类很多,本章主要讨论半导体存储器。

半导体存储器以其品种多、容量大、速度快、耗电省、体积小、操作方便、维护容易等优点,在数字设备中得到广泛应用。

目前,微型计算机的内存普遍采用了大容量的半导体存储器。

存储器——用以存储一系列二进制数码的器件。

半导体存储器的分类根据使用功能的不同,半导体存储器可分为随机存取存储器(RAM —Random Access Memory )和只读存储器(ROM —Read-Only memory )。

按照存储机理的不同,RAM 又可分为静态RAM 和动态RAM 。

存储器的容量存储器的容量=字长(n )×字数(m )7.1随机存取存储器(RAM )随机存取存储器简称RAM ,也叫做读/写存储器,既能方便地读出所存数据,又能随时写入新的数据。

RAM 的缺点是数据的易失性,即一旦掉电,所存的数据全部丢失。

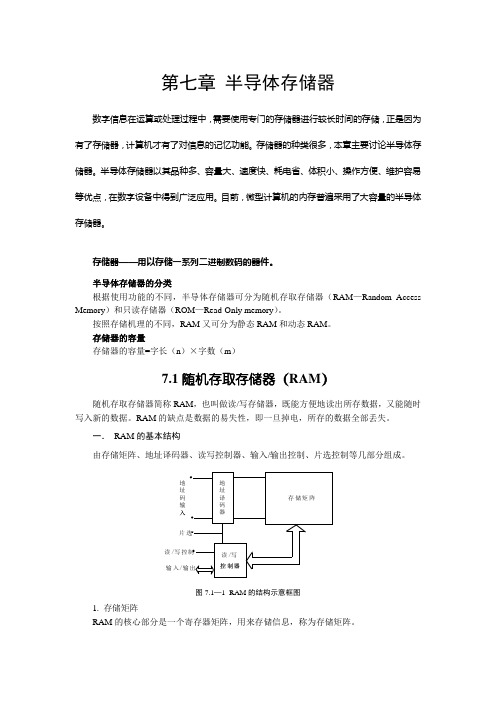

一. RAM 的基本结构由存储矩阵、地址译码器、读写控制器、输入/输出控制、片选控制等几部分组成。

存储矩阵读/写控制器地址译码器地址码输片选读/写控制输入/输出入图7.1—1 RAM 的结构示意框图1. 存储矩阵RAM 的核心部分是一个寄存器矩阵,用来存储信息,称为存储矩阵。

图7.1—5所示是1024×1位的存储矩阵和地址译码器。

属多字1位结构,1024个字排列成32×32的矩阵,中间的每一个小方块代表一个存储单元。

为了存取方便,给它们编上号,32行编号为X 0、X 1、…、X 31,32列编号为Y 0、Y 1、…、Y 31。

这样每一个存储单元都有了一个固定的编号(X i 行、Y j 列),称为地址。

11113131131********列 译 码 器行译码器...........位线位线位线位线位线位线.......X X X Y Y Y 0131131A A A A A A A A A A 地 址 输 入地址输入0123456789D D数据线....图7.1-5 1024×1位RAM 的存储矩阵2. 址译码器址译码器的作用,是将寄存器地址所对应的二进制数译成有效的行选信号和列选信号,从而选中该存储单元。

《微型计算机原理与接口技术》习题与思考答案第1章微型计算机概论1.1 A B C 1.2 B 1.3 B 1.4 C 1.5 A B C 1.6 B D1.7 00000111B=7D=07H 11010100B=212D=D4H01101010B=106D=6AH 10110.101B=22.625D=16.AH11001.011B=25.375D=19.6H1.8 127D=11111111B=FFH 12.625D=1100.101B=C.AH225.9375D=11100001.1111B=E1.FH 18.3l25D=10010.0101B=12.5H206.125=11001110.001B=CE.2H1.9 10H=10000B=16D 0.A8H=0.10101B=0.65625D28.9H=101000.1001B=40.5625D 4B.2AH=1001011.0010101B=75.6762D20E.4H=1000001110.01B=526.25D1.10 [+37]原=00100101B [+37]反=00100101B [+37]补=00100101B [+37]过余=10100101B[+94]原=01011110B [+94]反=01011110B [+94]补=01011110B [+94]过余=11011110B[-11]原=10001011B [-11]反=11110100B [-11]补=11110101B [-11]过余=01110101B[-125]原=11111101B [-125]反=10000010B [-125]补=10000011B [-125]过余=00000011B 1.11补码00010101B的真值为+21D 补码41H的真值为+65D补码9BH的真值为-101D 补码FFH的真值为-1D补码11110101B的真值为-11D1.12 A的ASCII码为41H a的ASCII码为61Hg的ASCII码为67H z的ASCII码为7AH0的ASCII码为30H 9的ASCII码为39H*的ASCII码为2AH +的ASCII码为2BHCR的ASCII码为0DH %的ASCII码为25H1.12一个16×16字形点阵占用存储空间32B一个24×24字形点阵占用存储空间72B一个32×32字形点阵占用存储空间128B1.14 (以8位补码为例)[X]补+[Y]补=[+38]补+[+100]补=0001010B,溢出[X]补+[Z]补=[+38]补+[-20]补=00010010B,未溢出[Y]补- [Z]补=[+100]补- [-20]补=01111000B,未溢出[Z]补- [X]补=[-20]补- [+38]补=11000110B,未溢出1.15 X与Y=0100B X或Z=1111B Y异或Z=1101B 非Y=1001B1.16微型计算机具有体积小、重量轻、功耗低;功能强;可靠性高;价格低廉;结构灵活、适应性强;使用方便、维护容易等特点。

微型计算机及接口技术考核学问点依据高等教育自学考试教材《微型计算机及接口技术》杨全胜2022 版和微型计算机及接口技术〔课程代码04732〕考试大纲编写。

1.考核学问点1.1.微型计算系统概述1.1.1.微型计算机系统的组成局部微型计算机系统主要由硬件系统和软件系统组成。

其中,硬件系统包括主机和外设,软件系统包含系统软件和应用软件。

硬件系统在冯·诺依曼体系构造由运算器、掌握器、存储器、输入设备、输出设备5局部组成。

系统软件包括BIOS、操作系统和支撑软件。

1.1.2.总线在微型计算机中的作用微型计算机中各部件之间及微型计算机与设备之间通过总线相连,它是微型计算机系统中各部件或设备之间传送信息的公共导线,一般由地址总线、数据总线和掌握总线 3 组组成。

地址总线:一般是单向总线,传送CPU 发出的地址信息。

数据总线:是双向总线,既可以从 CPU 传送数据信息到外设和主存,也可以从主存和外设向 CPU 传送数据。

掌握总线:每根的方向是肯定的,它们分别传送掌握信息、时序信息和状态信息,这些信息掌握数据总线、地址总线的使用。

1.1.3.微型计算机系统主要性能指标通常承受下面一些常见的性能指标来衡量一台微型计算机的好坏。

字长:是指微型计算机系统中CPU 一次能处理的二进制数。

主频:CPU 工作时的节拍由计算机主时钟掌握。

主频就是主时钟不断产生的时钟脉冲的固定频率。

速度:每秒所能执行的指令条数。

主存容量和存取时间:主存容量是指微型计算机中内部存储器能存放数据的最大字节数。

32 根地址总线,最大主存容量是2 的32 次方=4GB。

微型计算机内主存完成一次读写所需要的时间称为存取时间。

兼容性:通常是指同一个软件不加修改就可在两台机器上运行。

1.1.4.程序如何转换成最终的电子信号一个高级语言描述的程序,需要经过编译、连接、执行,才能最终变成一个个电子的数据信号、地址信号或掌握信号,完成所需的工作。

无论是高级语言的程序还是汇编程序,最终都要转换成机器能识别的机器指令,这些机器指令再在CPU 的工作下转换成各类电子信号。