专用集成电路,verilog移位乘法器,源代码及电路仿真

- 格式:pdf

- 大小:530.53 KB

- 文档页数:7

verilog的移位运算Verilog 编程语言是专门用于数字电路设计的硬件描述语言之一,它可以描述电子电路的行为。

其中,移位运算是 Verilog 中的一种重要运算,它可以让我们对数字信号进行位的移动操作,并且还可以进行逻辑移位或算术移位运算。

在 Verilog 中,移位运算符是 ">>" 和 "<<",它们可以分别实现右移和左移运算。

在移位运算中,所移动的位数可以作为操作符的参数进行定义。

移位运算符的操作数可以是以下任意一种:1. 一个位向量或一个寄存器。

2. 一个常量或一个表达式。

例如,下面的代码实现了一个移位器,将一个 8 位的输入向右移动 n 位,并在输出上输出结果:```module shift_register(input [7:0] D, input [2:0] n, output [7:0] Q);assign Q = D >> n;endmodule```上面的代码中,我们定义了一个shift_register 模块,它有三个输入和一个输出。

其中,输入D 表示要移动的数据,n 表示要移动的位数,而Q 则表示输出的结果。

移位运算还可以实现不同类型的位移动:逻辑移位 (_logic shift)逻辑移位运算将移动后的结果填充0 或者1,可以分为两种类型:左移和右移。

左移操作符: "<<",它将将一个数据左移指定位数,并用 0 填充。

右移操作符: ">>",它将将一个数据右移指定位数,并用 0 填充。

例如,下面的代码实现了一个逻辑移位器,用于将一个 8 位的输入向左移动 n 位,并在输出上输出结果:```module logic_shift_register(input [7:0] D, input [2:0] n, output [7:0] Q);assign Q = D << n;endmodule```算术移位 (arithmetic shift)算术移位运算比逻辑移位运算更为复杂,它是通过重复移动最高位的数值来完成的。

verilog简单乘法器Verilog简单乘法器Verilog是一种硬件描述语言,用于描述数字系统的行为。

在数字电路设计中,乘法器是一个常见的电路组件,它用于执行乘法运算。

本文将介绍一个简单的Verilog乘法器的设计与实现。

乘法器是一种数字电路,用于计算两个数的乘积。

它接收两个输入数,将它们相乘得到一个输出。

在本文中,我们将实现一个4位乘法器,即输入和输出都是4位的二进制数。

我们需要定义输入和输出端口。

在Verilog中,我们可以使用“input”和“output”关键字来声明端口。

对于4位乘法器,我们可以声明两个4位的输入端口A和B,以及一个8位的输出端口P。

module simple_multiplier(input [3:0] A,input [3:0] B,output [7:0] P);接下来,我们需要实现乘法器的功能。

乘法器的实现可以通过多次执行加法运算来实现。

具体地,我们可以将输入的两个4位数逐位相乘,然后将得到的部分乘积相加得到最终的乘积。

在Verilog中,我们可以使用“assign”关键字来执行赋值操作。

我们可以定义一些临时变量,用于存储部分乘积和最终乘积的结果。

然后,通过多次执行加法运算,将部分乘积相加得到最终乘积。

下面是一个实现4位乘法器的简单示例代码:reg [7:0] temp;reg [7:0] result;always @(*) begintemp = A[0] * B;result = temp;temp = A[1] * B;result = result + (temp << 1);temp = A[2] * B;result = result + (temp << 2);temp = A[3] * B;result = result + (temp << 3);endassign P = result;在上述代码中,我们使用了一个“always”块来执行乘法器的功能。

Verilog代码乘法除法1. 引言Verilog是一种硬件描述语言,用于设计和建模数字电路。

在数字电路中,乘法和除法是常见的运算操作。

本文将介绍如何使用Verilog编写乘法和除法的代码,并提供一些示例来帮助读者更好地理解。

2. 乘法2.1 基本原理乘法是一种基本的算术运算,用于计算两个数的积。

在数字电路中,我们可以使用逻辑门和触发器来实现乘法运算。

2.2 Verilog代码示例下面是一个简单的Verilog代码示例,用于实现两个8位无符号整数的乘法运算:module multiplier (input [7:0] a,input [7:0] b,output reg [15:0] result);always @(*) beginresult = a * b;endendmodule上述代码定义了一个名为multiplier的模块,该模块有两个输入端口a和b,以及一个输出端口result。

在always @(*)块中,我们使用乘法操作符将输入端口a和b相乘,并将结果存储在输出端口result中。

2.3 测试与验证为了测试上述的乘法模块,我们可以编写一个测试台,输入一些测试用例,并验证输出结果是否正确。

module multiplier_test;reg [7:0] a;reg [7:0] b;wire [15:0] result;multiplier dut(.a(a),.b(b),.result(result));initial begin// Test case 1: a = 5, b = 3a = 5;b = 3;#10; // Wait for 10 time unitsif (result !== 15)$display("Test case 1 failed");// Test case 2: a = 10, b = 0a = 10;b = 0;#10; // Wait for 10 time unitsif (result !== 0)$display("Test case 2 failed");// Add more test cases here...endendmodule上述代码定义了一个名为multiplier_test的测试台模块。

Verilog乘法运算转换一、概述Verilog是一种硬件描述语言,广泛应用于数字电路设计中。

在数字电路设计中,乘法运算是一种常见的运算操作,因为乘法运算需要消耗较多的硬件资源,设计一个高效的乘法运算电路对于数字电路设计而言至关重要。

本文将介绍Verilog乘法运算的转换方法,帮助读者更好地理解乘法运算电路的设计。

二、乘法运算原理乘法运算是一种基本的算术运算,其原理是将两个数相乘得到一个结果。

在数字电路中,乘法运算通常使用乘法器来实现。

乘法器的实现原理是将两个数分别拆分成多个部分,然后通过加法器和移位器等逻辑电路进行运算,最终得到乘法的结果。

三、乘法运算电路的转换针对Verilog中乘法运算的转换,可以采取以下几种方法来实现:1. 使用乘法器IP核现代的FPGA和ASIC芯片通常都内置了乘法器IP核,可以直接在Verilog代码中调用该IP核来进行乘法运算。

这种方法非常简单方便,但是需要注意IP核的资源占用情况。

2. 使用移位和加法如果没有乘法器IP核或者需要优化硬件资源的情况下,可以使用移位和加法来实现乘法运算。

这种方法需要将乘数和被乘数分别拆分成多个部分,然后通过移位和加法器来进行运算。

这种方法虽然相对复杂一些,但是可以更好地控制硬件资源的使用。

3. 使用查找表实现乘法器另一种常见的方法是使用查找表来实现乘法器。

通过预先计算乘法运算的结果并存储在查找表中,然后根据乘数和被乘数的值来索引查找表来获得乘法的结果。

这种方法可以大大减少乘法运算的计算量,提高运算的速度。

四、案例分析下面通过一个简单的Verilog代码示例来说明乘法运算的转换方法:```verilogmodule mul (input wire [7:0] a,input wire [7:0] b,output wire [15:0] result);// 方法一:使用乘法器IP核assign result = a * b;endmodule```上述Verilog代码中,我们定义了一个模块mul,其中包含两个输入端口a和b,一个输出端口result。

verilog乘法运算Verilog乘法运算是数字电路设计中非常基础的运算之一,其实现过程完全依赖于已有的硬件结构,通常使用乘法器实现。

下面介绍Verilog 乘法器的基本原理以及实现方法,供大家学习参考。

一、Verilog乘法器的基本原理乘法器是将两个二进制数进行乘法运算的一种专门的数字电路,可以通过硬件电路结构来实现。

具体来讲,它由一系列与门、异或门、加法器和移位器组成,因此可以将两个n位的二进制数相乘,得到一个2n位的结果。

二、Verilog乘法器的实现方法Verilog语言可以非常方便地实现乘法器,下面我们来看一下乘法器的代码实现。

假设我们要实现8位的乘法器,用于计算两个8位的二进制数的乘积,可以采用如下的Verilog代码:module multi(x, y, z);input [7:0] x, y;output [15:0] z;wire [15:0] w;assign w = x * y;assign z = w;endmodule上述代码中,module multi定义了一个名为multi的模块。

该模块有三个端口,x和y用于输入两个8位的二进制数,z用于输出它们的乘积。

在模块中,使用wire类型定义了一个16位的中间变量w,用来存储计算结果。

乘法操作是通过赋值运算符“*”完成的。

最后,把w直接赋值给z即可。

三、Verilog乘法器的测试最后,为了验证我们实现的乘法器的正确性,我们还需要编写一个测试程序。

测试程序通常采用assert语句检查乘法运算的正确性。

下面是一个测试程序的例子:module testbench;reg [7:0] x, y;wire [15:0] z;multi m(x, y, z);initial beginx = 10;y = 20;#1;assert(z == 200);$display("Test passed!");endendmodule上述代码中,testbench是一个测试程序的名字。

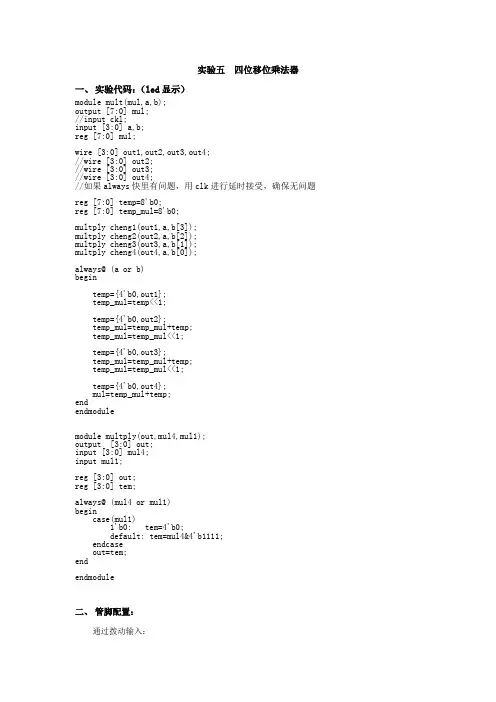

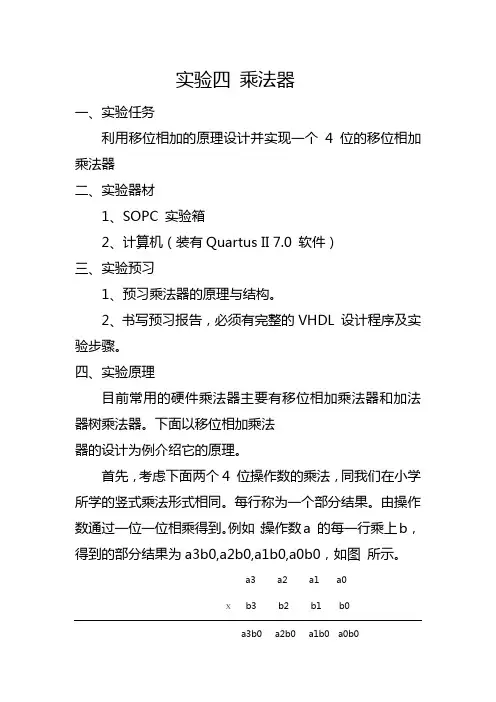

实验五四位移位乘法器一、实验代码:(led显示)module mult(mul,a,b);output [7:0] mul;//input ckl;input [3:0] a,b;reg [7:0] mul;wire [3:0] out1,out2,out3,out4;//wire [3:0] out2;//wire [3:0] out3;//wire [3:0] out4;//如果always快里有问题,用clk进行延时接受,确保无问题reg [7:0] temp=8'b0;reg [7:0] temp_mul=8'b0;multply cheng1(out1,a,b[3]);multply cheng2(out2,a,b[2]);multply cheng3(out3,a,b[1]);multply cheng4(out4,a,b[0]);always@ (a or b)begintemp={4'b0,out1};temp_mul=temp<<1;temp={4'b0,out2};temp_mul=temp_mul+temp;temp_mul=temp_mul<<1;temp={4'b0,out3};temp_mul=temp_mul+temp;temp_mul=temp_mul<<1;temp={4'b0,out4};mul=temp_mul+temp;endendmodulemodule multply(out,mul4,mul1);output [3:0] out;input [3:0] mul4;input mul1;reg [3:0] out;reg [3:0] tem;always@ (mul4 or mul1)begincase(mul1)1'b0: tem=4'b0;default: tem=mul4&4'b1111;endcaseout=tem;endendmodule二、管脚配置:通过拨动输入:a[0] input PIN_200a[1] input PIN_202a[2] input PIN_203a[3] input PIN_204b[0] input PIN_205b[1] input PIN_206b[2] input PIN_207b[3] input PIN_208led灯输出:mul[0] output PIN_191mul[1] output PIN_192mul[2] output PIN_193mul[3] output PIN_195mul[4] output PIN_196mul[5] output PIN_197mul[6] output PIN_198mul[7] output PIN_199三、实验连线:通过拨动输入:K1-K8:11-18Led灯显示连线:L1-L8:3-10四、电路工作原理手动拨动,开关k1-k8,根据Led灯的显示,亮表示1,不亮表示0来看结果。

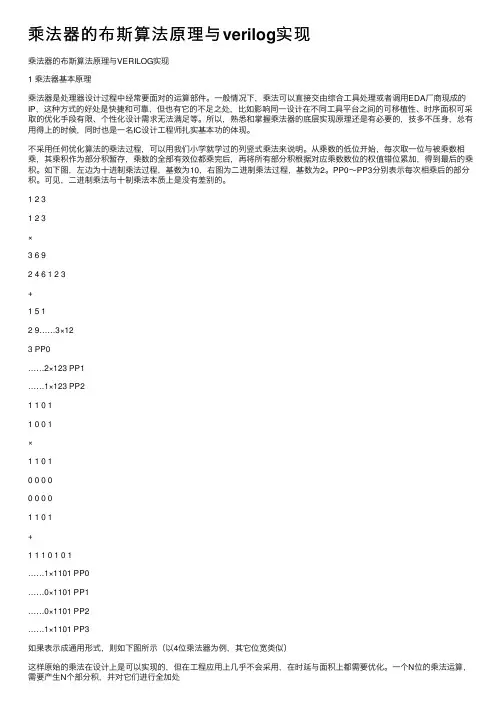

乘法器的布斯算法原理与verilog实现乘法器的布斯算法原理与VERILOG实现1 乘法器基本原理乘法器是处理器设计过程中经常要⾯对的运算部件。

⼀般情况下,乘法可以直接交由综合⼯具处理或者调⽤EDA⼚商现成的IP,这种⽅式的好处是快捷和可靠,但也有它的不⾜之处,⽐如影响同⼀设计在不同⼯具平台之间的可移植性、时序⾯积可采取的优化⼿段有限、个性化设计需求⽆法满⾜等。

所以,熟悉和掌握乘法器的底层实现原理还是有必要的,技多不压⾝,总有⽤得上的时候,同时也是⼀名IC设计⼯程师扎实基本功的体现。

不采⽤任何优化算法的乘法过程,可以⽤我们⼩学就学过的列竖式乘法来说明。

从乘数的低位开始,每次取⼀位与被乘数相乘,其乘积作为部分积暂存,乘数的全部有效位都乘完后,再将所有部分积根据对应乘数数位的权值错位累加,得到最后的乘积。

如下图,左边为⼗进制乘法过程,基数为10,右图为⼆进制乘法过程,基数为2。

PP0~PP3分别表⽰每次相乘后的部分积。

可见,⼆进制乘法与⼗制乘法本质上是没有差别的。

1 2 31 2 3×3 6 92 4 6 1 2 3+1 5 12 9……3×123 PP0……2×123 PP1……1×123 PP21 1 0 11 0 0 1×1 1 0 10 0 0 00 0 0 01 1 0 1+1 1 1 0 1 0 1……1×1101 PP0……0×1101 PP1……0×1101 PP2……1×1101 PP3如果表⽰成通⽤形式,则如下图所⽰(以4位乘法器为例,其它位宽类似)这样原始的乘法在设计上是可以实现的,但在⼯程应⽤上⼏乎不会采⽤,在时延与⾯积上都需要优化。

⼀个N位的乘法运算,需要产⽣N个部分积,并对它们进⾏全加处理,位宽越⼤,部分积个数越多,需要的加法器也越多,加法器延时也越⼤,那么针对乘法运算的优化,主要也就集中在两个⽅⾯:⼀是减少部分积的个数,⼆是减少加法器带来的延时。

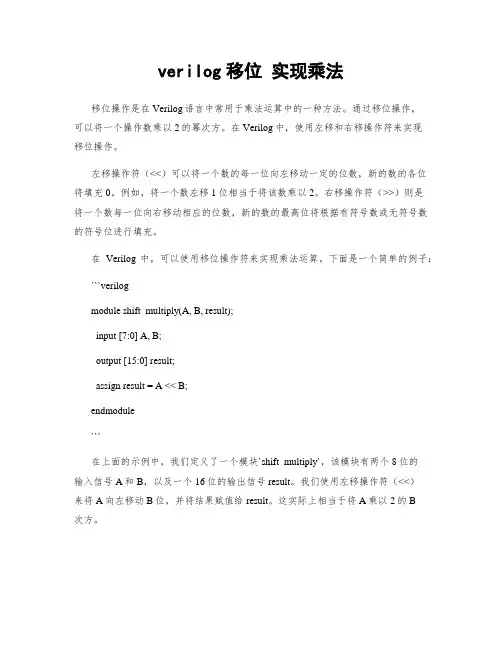

verilog移位实现乘法移位操作是在Verilog语言中常用于乘法运算中的一种方法。

通过移位操作,可以将一个操作数乘以2的幂次方。

在Verilog中,使用左移和右移操作符来实现移位操作。

左移操作符(<<)可以将一个数的每一位向左移动一定的位数,新的数的各位将填充0。

例如,将一个数左移1位相当于将该数乘以2。

右移操作符(>>)则是将一个数每一位向右移动相应的位数,新的数的最高位将根据有符号数或无符号数的符号位进行填充。

在Verilog中,可以使用移位操作符来实现乘法运算。

下面是一个简单的例子:```verilogmodule shift_multiply(A, B, result);input [7:0] A, B;output [15:0] result;assign result = A << B;endmodule```在上面的示例中,我们定义了一个模块`shift_multiply`,该模块有两个8位的输入信号A和B,以及一个16位的输出信号result。

我们使用左移操作符(<<)来将A向左移动B位,并将结果赋值给result。

这实际上相当于将A乘以2的B次方。

当我们实例化这个模块并在测试台中分配输入信号时,我们可以将一个数值作为A的输入,将另一个数作为B的输入。

模块将自动执行移位操作,并将结果输出到result信号中。

```verilogmodule testbench;reg [7:0] A, B;wire [15:0] result;shift_multiply SM(.A(A), .B(B), .result(result));initial begin// 分配输入信号A = 8'b10100010;B = 4'b0010;#10; // 等待10个时间单位$display("Result: %b", result);$finish;endendmodule```在上面的测试台中,我们定义了reg类型的输入信号A和B,以及wire类型的输出信号result。

verilog 乘法器命名Verilog乘法器命名引言Verilog是一种硬件描述语言,它用于描述数字电路和系统。

在数字电路中,乘法器是一个非常重要的组件。

在本文中,我们将讨论Verilog 乘法器的命名方法。

一、Verilog乘法器的简介Verilog乘法器是一种数字电路组件,用于执行两个数字之间的乘法运算。

它通常由多个逻辑门和寄存器组成,可以在FPGA或ASIC芯片上实现。

二、Verilog乘法器的设计1. 顺序乘法器顺序乘法器是最简单的乘法器之一。

它将两个数字逐位相乘,并将结果相加。

以下是一个顺序乘法器的Verilog代码:module sequential_multiplier(a, b, p);input [7:0] a, b;output [15:0] p;reg [15:0] p;integer i, j;always @(a or b) beginp = 0;for (i = 0; i <= 7; i = i + 1) beginfor (j = 0; j <= 7; j = j + 1) beginif ((i + j) <= 15) beginp[i+j] = p[i+j] + a[i] * b[j];endendendendendmodule2. Booth编码乘法器Booth编码乘法器利用Booth算法来减少乘法器的延迟。

它将两个数字转换为Booth编码,并使用加法器和移位器来计算结果。

以下是一个Booth编码乘法器的Verilog代码:module booth_multiplier(a, b, p);input [7:0] a, b;output [15:0] p;reg [15:0] p;integer i;always @(a or b) beginp = 0;for (i = 0; i <= 7; i = i + 1) beginif (b[i] == 1) beginp = p + (a << i);end else if (b[i] == -1) beginp = p - (a << i);endendendmodule3. Wallace树乘法器Wallace树乘法器使用Wallace算法来减少乘法器的面积。

verilog 乘法除法(实用版)目录1.引言2.Verilog 乘法和除法的基本概念3.Verilog 乘法和除法的实现方法4.Verilog 乘法和除法的应用实例5.总结正文【引言】Verilog 是一种硬件描述语言,常用于数字电路和模拟混合信号电路的描述。

在 Verilog 中,乘法和除法是数字电路设计中常见的运算。

本文将介绍 Verilog 中乘法和除法的基本概念、实现方法以及应用实例。

【Verilog 乘法和除法的基本概念】在 Verilog 中,乘法和除法运算是基于寄存器的。

乘法和除法运算的结果需要经过一定的时钟周期后才能得到。

乘法和除法的操作数可以是整数或者实数。

其中,整数乘法和除法通常使用位运算实现,实数乘法和除法则需要使用特殊的运算符和函数。

【Verilog 乘法和除法的实现方法】Verilog 中乘法和除法的实现方法主要有两种:一种是使用位运算实现,另一种是使用乘法和除法运算符实现。

1.使用位运算实现乘法和除法在 Verilog 中,可以使用位运算实现乘法和除法。

例如,可以使用“&”运算符实现乘法,使用“~”和“&”运算符实现除法。

2.使用乘法和除法运算符实现乘法和除法Verilog 中提供了专门的乘法和除法运算符:“*”和“/”。

使用这些运算符可以方便地实现乘法和除法运算。

【Verilog 乘法和除法的应用实例】下面是一个 Verilog 代码实例,演示了如何使用 Verilog 实现一个4 位整数乘法器和除法器:```verilogmodule multiplier_divider(input [3:0] a,input [3:0] b,output [7:0] product,output [7:0] quotient);reg [7:0] temp_product;reg [7:0] temp_quotient;always @(*) begintemp_product = a * b;temp_quotient = a / b;product = temp_product;quotient = temp_quotient;endendmodule```【总结】Verilog 中的乘法和除法运算是数字电路设计中常见的运算。

module chengfa(a,b,clk,rst,st,result,done);input[31:0]a,b;//乘数,被乘数input clk,st,rst;//时间信号,运算启动信号,复位信号reg[63:0] p1,p2,p3;output[63:0]result;// 结果输出output done;// 运算结束后的置位信号integer a1,b1;reg[1:0]sign;reg[6:0]i;//i用于控制运算在时序信号下按序进行reg don;assign done=don;assign result=p3;always@(posedge clk or negedge rst)beginif(!rst)i<=7'b0;else if(st&&i<7'd36)i<=i+1'b1;else if(!st)i<=7'b0;endalways@(posedge clk or negedge rst)beginif(!rst) don<=1'b0;else if(i==7'd34) don<=1'd1;//i为34时,运算结束else if(i==7'd36) don<=1'b0;endalways@(posedge clk or negedge rst)beginif(!rst)begina1=32'b0;//复位信号有效时,乘数,被乘数和运算结果全部置零b1=32'b0;p3=64'b0;endelse if(st)beginif(i==7'b0)begina1=a;//所锁存乘数和被乘数b1=b;endelse if(i>7'd0&&i<=7'd1)//利用一个时钟周期的时间来判断符号,将负数的补码表示变为其绝对值的原码。

乘法器的verilog实现(并⾏、移位相加、查找表)并⾏乘法器,也就是⽤乘法运算符实现,下⾯的代码实现8bit⽆符号数的乘法。

代码:1module mult_parrell(rst_n,2 clk,3 a,4 b,5 p6 );7parameter DATA_SIZE = 8;89input rst_n;10input clk;11input [DATA_SIZE - 1 : 0] a;12input [DATA_SIZE - 1 : 0] b;1314output [2*DATA_SIZE - 1 : 0] p;1516reg [DATA_SIZE - 1 : 0] a_r;17reg [DATA_SIZE - 1 : 0] b_r;1819wire [2*DATA_SIZE - 1 : 0] p_tmp;20reg [2*DATA_SIZE - 1 : 0] p;2122//输⼊数据打⼀拍23always@(posedge clk)24if(!rst_n)25begin26 a_r <= 8'd0;27 b_r <= 8'd0;28end29else30begin31 a_r <= a;32 b_r <= b;33end3435assign p_tmp = a*b; //只能做⽆符号数的相乘,若要做有符号数乘法,需将数据声明为signed类型3637//输出数据打⼀拍38always@(posedge clk)39if(!rst_n)40begin41 p <= 16'd0;42end43else44begin45 p <= p_tmp;46end4748endmodule移位相加乘法器,下⾯的代码可实现8bit有符号数的相乘,注意符号扩展以及MSB位的处理://输⼊数据取反assign a_r_inv = ~a_r + 1;assign a_shift0 = b_r[0] ? {{8{a_r[7]}},a_r} : 0;assign a_shift1 = b_r[1] ? {{7{a_r[7]}},a_r,1'b0} : 0;assign a_shift2 = b_r[2] ? {{6{a_r[7]}},a_r,2'b0} : 0;assign a_shift3 = b_r[3] ? {{5{a_r[7]}},a_r,3'b0} : 0;assign a_shift4 = b_r[4] ? {{4{a_r[7]}},a_r,4'b0} : 0;assign a_shift5 = b_r[5] ? {{3{a_r[7]}},a_r,5'b0} : 0;assign a_shift6 = b_r[6] ? {{2{a_r[7]}},a_r,6'b0} : 0;assign a_shift7 = b_r[7] ? {{1{a_r_inv[7]}},a_r_inv,7'b0} : 0; //被乘数为⽆符号数时,特别处理代码:1module mult_shift_add(rst_n,2 clk,3 a,4 b,5 p6 );7parameter DATA_SIZE = 8;89input rst_n;10input clk;11input [DATA_SIZE - 1 : 0] a;12input [DATA_SIZE - 1 : 0] b;1314output [2*DATA_SIZE - 2 : 0] p;1516//输⼊数据打⼀个时钟节拍17reg [DATA_SIZE - 1 : 0] a_r;18reg [DATA_SIZE - 1 : 0] b_r;1920//输⼊数据取反21wire [DATA_SIZE - 1 : 0] a_r_inv;2223//输⼊数据移位24wire [2*DATA_SIZE - 1 : 0] a_shift0;25wire [2*DATA_SIZE - 1 : 0] a_shift1;26wire [2*DATA_SIZE - 1 : 0] a_shift2;27wire [2*DATA_SIZE - 1 : 0] a_shift3;28wire [2*DATA_SIZE - 1 : 0] a_shift4;29wire [2*DATA_SIZE - 1 : 0] a_shift5;30wire [2*DATA_SIZE - 1 : 0] a_shift6;31wire [2*DATA_SIZE - 1 : 0] a_shift7;3233//输出数据打⼀个时钟节拍34wire [2*DATA_SIZE - 1 : 0] p_tmp;35reg [2*DATA_SIZE - 1 : 0] p;3637//输⼊数据打⼀个时钟节拍38always@(posedge clk)39if(!rst_n)40begin41 a_r <= 8'd0;42 b_r <= 8'd0;43end44else45begin46 a_r <= a;47 b_r <= b;48end49//输⼊数据取反50assign a_r_inv = ~a_r + 1;5152//输⼊数据移位,注意符号扩展,不仅仅是最⾼位扩展53//对每⼀个bit都需扩展54assign a_shift0 = b_r[0] ? {{8{a_r[7]}},a_r} : 0;55assign a_shift1 = b_r[1] ? {{7{a_r[7]}},a_r,1'b0} : 0;56assign a_shift2 = b_r[2] ? {{6{a_r[7]}},a_r,2'b0} : 0;57assign a_shift3 = b_r[3] ? {{5{a_r[7]}},a_r,3'b0} : 0;58assign a_shift4 = b_r[4] ? {{4{a_r[7]}},a_r,4'b0} : 0;59assign a_shift5 = b_r[5] ? {{3{a_r[7]}},a_r,5'b0} : 0;60assign a_shift6 = b_r[6] ? {{2{a_r[7]}},a_r,6'b0} : 0;61assign a_shift7 = b_r[7] ? {{1{a_r_inv[7]}},a_r_inv,7'b0} : 0; //被乘数为⽆符号数时,特别处理6263assign p_tmp = a_shift0 + a_shift1 + a_shift2 + a_shift3 + a_shift464 + a_shift5 + a_shift6 + a_shift7;6566always@(posedge clk)67if(!rst_n)68begin69//p <= 16'd0;70 p <= 15'd0;71end72else73begin74//p <= p_tmp[15:0];75 p <= p_tmp[14:0];76end7778endmoduletestbench:1module mult_shift_add_tb;23// Inputs4reg rst_n;5reg clk;6reg [7:0] a;7reg [7:0] b;89// Outputs10wire [14:0] p;1112// Instantiate the Unit Under Test (UUT)13 mult_shift_add uut (14 .rst_n(rst_n),15 .clk(clk),16 .a(a),17 .b(b),18 .p(p)19 );2021parameter CLK_PERIOD = 10;2223initial begin24 rst_n = 0;25 clk = 0;2627 #100;28 rst_n = 1;29end3031always #(CLK_PERIOD/2) clk = ~clk;3233always@(posedge clk)34if(!rst_n)35begin36 a = 8'd0;37 b = 8'd0;38end39else40begin41 a = a + 1;42 b = b - 1;43end4445endmoduleISIM仿真结果:移位相加乘法器树:将assign p_tmp = a_shift0 + a_shift1 + a_shift2 + a_shift3 + a_shift4 + a_shift5 + a_shift6 + a_shift7;换为:assign sum_01 = a_shift0 + a_shift1;assign sum_23 = a_shift2 + a_shift3;assign sum_45 = a_shift4 + a_shift5;assign sum_67 = a_shift6 + a_shift7;assign sum_0123 = sum_01 + sum_23;assign sum_4567 = sum_45 + sum_67;assign p_tmp = sum_0123 + sum_4567;就成为乘法器树。

verilog 移位实现乘法(原创版)目录一、Verilog 移位实现乘法的原理二、Verilog 移位实现乘法的方法三、Verilog 移位实现乘法的实例代码四、Verilog 移位实现乘法的优点与局限性正文一、Verilog 移位实现乘法的原理在 Verilog 中,移位运算是一种常见的数字电路实现方法,它可以用于实现乘法运算。

移位运算的原理是将一个数的二进制位向左或向右移动一定的位数,从而实现数字的扩大或缩小。

在 Verilog 中,移位运算通过使用位移运算符“<<”或“>>”来实现。

乘法运算可以通过移位运算实现,其基本原理是将一个数不断乘以 2,直到达到目标值。

例如,要实现 8 位二进制数相乘,可以将其中一个数不断左移 3 位,另一个数不断右移 3 位,这样就可以将乘法运算转化为移位运算。

二、Verilog 移位实现乘法的方法在 Verilog 中,移位实现乘法的方法主要有两种:一种是使用 for 循环,逐位相乘并累加结果;另一种是使用移位寄存器,不断对输入数据进行移位操作。

方法一:使用 for 循环实现乘法```verilogmodule multiplier(input a, input b, output [7:0] result);reg [7:0] sum;always @(*) beginfor (integer i = 0; i < 8; i = i + 1) beginsum[i] = a * b[7 - i];endendassign result = sum;endmodule```方法二:使用移位寄存器实现乘法```verilogmodule multiplier(input a, input b, output [7:0] result); reg [7:0] c;always @(*) beginif (a == 1"b0) beginc <= 1"b0;end else beginc <= c << 1;endendassign result = c;endmodule```三、Verilog 移位实现乘法的实例代码下面是一个 16 位乘法器的 Verilog 代码示例:```verilogmodule multiplier(input [15:0] a, input [15:0] b, output [31:0] result);reg [31:0] c;always @(*) beginif (a == 1"b0) beginc <= 1"b0;end else beginc <= c << 1;endendassign result = c;endmodule```四、Verilog 移位实现乘法的优点与局限性Verilog 移位实现乘法的优点是电路简单,易于实现,且计算速度快。

组合-时序逻辑电路Verilog-Testbench代码_带仿真代码和波形_1组合逻辑电路--基本门电路1.1基本门电路1.1.1结构化描述⽅式代码如下View Code1 module logics2 (3 input iA,4 input iB,5 output oAnd,6 output oOr,7 output oNot8 );910 and and_inst(oAnd,iA,iB);11 or or_inst(oOr,iA,iB);12 not not_inst(oNot,iA);1314 endmodule最底层的是门级原语and or not RTL级视图testbench如下View Code1 `timescale 1 ns/ 1 ns2 module logics_tb();34 reg ia;5 reg ib;67 wire oAnd;8 wire oOr;9 wire oNot;1011 initial12 begin13 ia=0;14 #40 ia=1;15 #40 ia=0;16 #40 ia=1;17 #40 ia=0;18 end1920 initial21 begin22 ib=0;23 #40 ib=0;24 #40 ib=1;25 #40 ib=1;26 #40 ib=0;27 end2829 logics logics_inst30 (31 .iA(ia),32 .iB(ib),33 .oAnd(oAnd),34 .oOr(oOr),35 .oNot(oNot)36 );37RTL级仿真图形如下GATE级仿真图如下可见RTL级仿真是理想的,GATE级仿真考虑了延迟和信号开始的不确定。

1.1.2采⽤流描述⽅法代码如下View Code1 module logics2 (3 input iA,4 input iB,5 output oAnd,6 output oOr,7 output oNot8 );910 assign oAnd=iA&iB11 assign oOr=iA|iB;12 assign oNot=~iA;1314 endmoduleRTL级视图,仿真图形同上。

verilog 移位实现乘法摘要:1.Verilog移位实现乘法的基本原理2.移位运算与乘法的关系3.具体实现步骤与代码示例4.代码解释与分析5.总结与展望正文:Verilog移位实现乘法是一种基于移位运算的数字电路设计方法,通过巧妙地利用移位运算替代乘法运算,可以实现高效且易于理解的乘法器设计。

本文将详细介绍Verilog移位实现乘法的基本原理、移位运算与乘法的关系、具体实现步骤以及代码示例,并对代码进行解释与分析,最后进行总结与展望。

1.Verilog移位实现乘法的基本原理Verilog移位实现乘法的关键在于利用移位运算模拟乘法过程。

在二进制乘法中,乘数和被乘数都是二进制数,我们可以通过将乘数不断左移,并与被乘数进行按位与操作,最后将得到的结果累加,即可实现乘法运算。

2.移位运算与乘法的关系在移位实现乘法的过程中,我们需要将乘数左移相应的位数,然后与被乘数进行按位与操作。

具体来说,对于一个n位的乘数,我们需要进行n-1次左移操作。

每次左移后,乘数相当于乘以2的幂次方,与被乘数进行按位与操作后,可以将乘法问题转化为加法问题。

3.具体实现步骤与代码示例下面以一个简单的16位乘法器为例,介绍Verilog移位实现乘法的具体步骤和代码:```module multiplier(input [15:0] a, [15:0] b, output [31:0] p);reg [31:0] sum;always @(*) beginsum = 0;for (int i = 0; i < 16; i++) {sum = sum + (a * b[i]);}p = sum;endendmodule```在这个代码示例中,我们使用了一个for循环将乘数a和被乘数b的每一位相乘,并将结果累加到sum中。

最后将sum输出到输出端口p中。

4.代码解释与分析上述代码中,我们利用了循环结构将乘数a和被乘数b的每一位相乘,并通过移位运算实现了乘法运算。

生命科学技术学院《CMOS专用集成电路》实验报告学院(系):生命科学技术学院专业:生物医学工程班级:151011学号:15101004学生姓名:柳琳2013年06 月29 日一、实验题目(1)更改测试文件相关部分的参数值,将该乘法器的数据位宽改为8-Bit。

(2)根据对实验电路的分析,绘制该移位式乘法器电路详细的电路结构框图,并对每一功能部件的功能及相关参数的意义进行说明;(3)采用Verilog HDL硬件描述语言设计一个16-Bit超前进位加法器;(4)在上面超前进位加法器基础上,将原电路的部分积求和电路改进成超前进位加法器。

二、实验结果与讨论(1)更改测试文件相关部分的参数值,将该乘法器的数据位宽改为8-Bit。

module multiplier_nbit ( rst, clk, x, y, result );parameter mwidth = 8;parameter rwidth = mwidth + mwidth;input rst, clk;…reg [1:0] stcnt;reg [2:0] mucnt;…assign mucnt_en = (stcnt == 2'b01) ? 1'b1 : 1'b0;assign mucnt_full = (mucnt == 3'b111) ? 1'b1 : 1'b0;assign stcnt_load = (stcnt == 2'b10) ? 1'b1 : 1'b0;…always @(posedge rst or posedge clk)beginif(rst)mucnt <= 3'b000;else if(mucnt_en)mucnt <= mucnt + 1;elsemucnt <= mucnt;endmodule test_mult;reg rst, clk;reg [7:0] x, y;wire [15:0] result;initialbeginclk = 1'b0;rst = 1'b0;#25 rst = 1'b1;x = 16'h01;y = 16'h02;#25 rst = 1'b0;#160 x = 16'h02;y = 16'h03;#160 x = 16'h01;y = 16'h02;#160 x = 16'h03;y = 16'h04;#160 x = 16'h05;y = 16'h06;endmodule adder_nbit(a, b, sum, co);parameter width = 8;input [width-1:0] a, b;output [width-1:0] sum;wire [width-1:0] sum;output co;wire co;wire [width-1:0] sum_mag;wire auxc_bit, sign_bit;assign sum_mag = {1'b0, a[width-2:0]} + {1'b0, b[width-2:0]};assign auxc_bit = sum_mag[width-1];assign sign_bit = a[width-1] ^ b[width-1] ^ auxc_bit;assign co = (a[width-1] & b[width-1]) | (a[width-1] & auxc_bit) | (b[width-1] & auxc_bit);assign sum = {sign_bit, sum_mag[width-2:0]};endmoduleFigure 1乘法器(2)根据对实验电路的分析,绘制该移位式乘法器电路详细的电路结构框图,并对每一功能部件的功能及相关参数的意义进行说明;(3)采用Verilog HDL硬件描述语言设计一个16-Bit超前进位加法器;(未完成)(4)在上面超前进位加法器基础上,将原电路的部分积求和电路改进成超前进位加法器。

(未完成)四、实验心得与意见反馈通过两次CMOS专用集成电路的上机,我了解了verilog语言的结构,并学会了Modelsim 仿真软件的初步使用。

学会了用modelsim软件对设计的电路进行仿真,通过修改变量了解到电路如何控制小灯的闪烁。

希望增加上机次数五、附程序源代码1、实用型移位式乘法器电路描述://******************************************************************////****** MODULE DESCRIPTION : 16-Bit Practical Shift Multiplier//****** AUTHOR : rzH//****** DATE : 06.20.2013//******************************************************************//module multiplier_nbit ( rst, clk, x, y, result );//data width definitionparameter mwidth = 16;parameter rwidth = mwidth + mwidth;//input rst, clk;//input operation data x and yinput [mwidth-1:0] x, y;//output multiply resultoutput [rwidth-1:0] result;reg [rwidth-1:0] result;//stcnt: state counter---3 state//state 0: input data registered//state 1: multiply operation//state 2: output data registeredreg [1:0] stcnt;//mucnt: multiply step counter---16 stepreg [3:0] mucnt;//multiplicand registerreg [mwidth-1:0] opx;//partial product register//also to save resource, multiplier are initially//stored in the low 16bit of the registerreg [rwidth-1:0] ptpro;//select data source to multiplicand registerwire tx_sel;//select data source to partial product registerwire [1:0] tp_sel;//select data source to ptadd according to//the lowest bit of the multiplier in multiply processwire adp_sel;wire [rwidth-1:0] ptshf1, ptshf0, ptadd;//partial product initialwire [rwidth-1:0] ptini;//temprorywire [mwidth-1:0] temp_x;reg [rwidth-1:0] temp_p;//output multiply result enablewire mout_en;//16-bit adder output: summary and carrywire [mwidth-1:0] sum;wire co;//stcnt state 1: start multiply processassign mucnt_en = (stcnt == 2'b01) ? 1'b1 : 1'b0;//multiply process endassign mucnt_full = (mucnt == 4'b1111) ? 1'b1 : 1'b0;//stcnt state end and load initial stateassign stcnt_load = (stcnt == 2'b10) ? 1'b1 : 1'b0;//stcnt count enableassign stcnt_en = ((!mucnt_en) || mucnt_full) ? 1'b1 : 1'b0; always @(posedge rst or posedge clk)beginif(rst)stcnt = 2'b00;else if(stcnt_load)stcnt = 2'b00;else if(stcnt_en)stcnt = stcnt + 1;elsestcnt = stcnt;endalways @(posedge rst or posedge clk)beginif(rst)mucnt <= 4'b0000;else if(mucnt_en)mucnt <= mucnt + 1;elsemucnt <= mucnt;end//select initial or intermediate resultassign tx_sel = (stcnt == 2'b00) ? 1'b1 : 1'b0;assign temp_x = tx_sel ? x : opx;assign tp_sel = stcnt;assign ptini = {{mwidth{1'b0}}, y};assign adp_sel = (ptpro[0] == 1'b1) ? 1'b1 : 1'b0;//the lowest bit of the multiplier is 1assign ptshf1 = {co, sum, ptpro[mwidth-1:0]} >> 1;//the lowest bit of the multiplier is 0assign ptshf0 = ptpro >> 1;assign ptadd = adp_sel ? ptshf1 : ptshf0;//select initial or intermediate resultalways @(tp_sel or ptini or ptadd or ptpro)begincase(tp_sel)2'b00: temp_p = ptini;2'b01: temp_p = ptadd;2'b10: temp_p = ptpro;default: temp_p = ptpro;endcaseend//register multiplicand and partial productalways @(posedge rst or posedge clk)beginif(rst)beginopx <= {mwidth{1'b0}};ptpro <= {rwidth{1'b0}};endelsebeginopx <= temp_x;ptpro <= temp_p;endend//output multiply resultassign mout_en = (stcnt == 2'b10) ? 1'b1 : 1'b0;always @(posedge rst or posedge clk)beginif(rst)result <= {rwidth{1'b0}};else if(mout_en)result <= ptpro;elseresult <= result;end//adder_nbit u0(.a(ptpro[rwidth-1:mwidth]), .b(opx), .sum(sum), .co(co));endmodule2、测试向量设计:module test_mult;reg rst, clk;reg [15:0] x, y;wire [31:0] result;initialbeginclk = 1'b0;rst = 1'b0;#25 rst = 1'b1;x = 16'h0000;y = 16'h0003;#25 rst = 1'b0;#160 x = 16'h0012;y = 16'h0013;#160 x = 16'h0134;y = 16'h0213;#160 x = 16'h1234;y = 16'h2587;#160 x = 16'hffff;y = 16'hffff;endalways #5 clk = ~clk;multiplier_nbit u0(.rst(rst), .clk(clk), .x(x), .y(y), .result(result)); endmodule。