EDA课程设计八位数码管扫描显示电路的设计 2解读

- 格式:doc

- 大小:678.49 KB

- 文档页数:12

实验一基本组合电路设计(1)实验目的:熟悉 Quartus U的文本输入设计法和原理图输入设计法,学习简单组合电路以及多层次电路的设计、仿真和硬件测试。

(2)实验内容:I.利用Quartus U完成2选1多路选择器的文本编辑输入。

【参考程序】:ENTITY mux21a ISPORT ( a, b, s: IN BIT;y : OUT BIT );END ENTITY mux21a;ARCHITECTURE one OF mux21a ISBEGINPROCESS (a,b,s)BEGINIF s = ' O' THEN y <= a ;ELSE y<= b ;END IF;END PROCESS;END ARCHITECTURE one ;n .将实验I中的2选1多路选择器生成一个元件 mux21a利用原理图输入设计方法实现图1-1的双2选1多路选择器,并将此文件放在同一目录中。

最后进行编译、仿真,并对其仿真波形作出分析说明。

川.对U进行引脚锁定及硬件下载测试。

建议选择实验电路模式5,用键1(PIOO, 引脚号为1)控制sO;用键2(PIO1,引脚号为2)控制s1; a3、a2和a1分别接clock5(引脚号为16)、clockO (引脚号为93)和clock2 (引脚号为17);输出信号outy接扬声器spker (引脚号为129)。

通过短路帽选择clock5接1024Hz 信号,clock0接256Hz信号,clock2接8Hz信号。

最后进行编译、下载和硬件测试实验(通过选择键1、键2、控制s0、s1,可使扬声器输出不同音调)。

(3)实验报告:1.实验U的原理图。

2•实验U的仿真波形报告分析说明。

3.实验川硬件测试的详细实验说明。

图1-1 双2选1多路选择器实验_二基本时序电路设计(1)实验目的:熟悉Quartus U的VHDL文本设计过程,学习简单时序电路的设计、仿真和硬件测试。

实验二:数码管扫描显示电路一、实验目的采用混合工程,将模4计数器,3选1多路复用器,2-3译码器以及7段译码器混合编程,最终使三位数码管显示1,2,3;二、实验方法采用基于FPGA进行数字逻辑电路设计的方法。

其中利用原理图,硬件描述语言画出最终电路原理图,从而达到实验结果;三、实验步骤1、编译好3选1多路复用器,2-3译码器并保存;2、新建工程名为scan-led3的文件,目标器件为EPF10K20TC144-3;3、将将模4计数器,3选1多路复用器,2-3译码器的源文件导入工程中;4、建立电路图文件并完成电路图连接;5、按照实验要求完成管脚分配;6、打开波形图文件,插入节点和节点集合,另外要把输入节点组中得din0,din1,din2改成16进制,其它为2进制;7、进行仿真,产生波形;8、将设计下载到芯片中并使三位数码管稳定显示1,2,3;四、实验原理1、3选1多路复用器程序设计为:library IEEE;use IEEE.std_logic_1164.all;entity mux4_3_1 isport(d0,d1,d2:in STD_LOGIC_VECTOR(3 downto 0);sel: in STD_LOGIC_VECTOR(1 downto 0);dout:out STD_LOGIC_VECTOR(3 downto 0));end mux4_3_1;architecture rtl of mux4_3_1 isbegindout<= d0 when sel="00"elsed1 when sel="01"elsed2;end rtl;2、2-3译码器电路图为:3、scan-led3的电路图为:4、scan-led3的仿真波形图:五、实验总结:这次实验由于是小组分工完成,所以我完成的是3-选1多路复用器和scan-led3的电路图绘制;虽然其他部分并非我单独完成,但还是熟悉了基本流程而且有了不同的了解和认识:首先在3选1多路复用器中认识到一种新的分配管脚的方法——就是有点击File-New-Tcl script File,利用TCL脚本语言分配管脚;(以前用的就是点击Assignments-Pins来分配管脚。

EDA与VHD1语言课程实验报告实验名称:班级:学号:姓名:实验日期:8位数码扫描显示电路设计2012.10.27实验五8位数码扫描显示电路设计一、实验目的:学习硬件扫描显示电路的设计。

二、实验原理:图1所示是8位数码扫描显示电路。

图1中g~a为数码管段信号输入端,每个数码管的七个段(g、f、e、d、c、b、a)都分别连在一起;k1~k8 为数码管的位选信号输入端。

8个数码管分别由8个位选信号k1、k2、…k8来选通,被选通的数码管才显示数据,未选通的数码管关闭。

如在某一时刻,k3为高电平,其余选通信号均为低电平,这时仅k3对应的数码管显示来自段信号端的数据,而其它7个数码管呈现关闭状态。

因此,如果希望在8个数码管上显示希望的数据,就必须使得8个选通信号k1、k2、…k8分别被单独选通,同时,在段信号输入口加上希望在该对应数码管上显示的数据,于是随着选通信号的扫变,就能实现扫描显示的目的。

AAAAAAAAK1 K2 K3 K4 K5 K6 K7 K3图1 8位数码扫描显示电路三、实验内容1:用VHDL语言设计8位数码扫描显示电路,显示输出数据直接在程序中给出。

1、程序设计LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY scan play ISPORT( CLK:IN STD_LOGIC;SI:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);BI:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END ;ARCHITECTURE bhv OF scan play ISSIGNAL S: STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL B: STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(CLK) --产生动态扫描显示的控制信号VARIABLE SIO: STD_LOGIC_VECTOR(3 DOWNTO 0); VARIABLE BIO:STD_LOGIC_VECTOR(3 DOWNTO 0); BEGINIF CLK'EVENT AND CLK='1' THENIF BIO < 8 THEN BIO:=BIO+1; ELSE BIO:=(others=>'0');END IF;IF SIO < 8 THEN SIO:=SIO+1; ELSE SIO:=(others=>'0');END IF;END IF;S<=SIO;B<=BIO;END PROCESS;PROCESS(S)BEGINCASE S ISWHEN "0000"=> SI<="00000001";WHEN "0001"=> SI<="00000010";WHEN "0010"=> SI<="00000100";WHEN "0011"=> SI<="00001000";WHEN "0100"=> SI<="00010000";WHEN "0101"=> SI<="00100000";WHEN "0110"=> SI<="01000000";WHEN "0111"=> SI<="10000000";WHEN OTHERS=> SI<="00000000"; END CASE;END PROCESS;PROCESS(B)BEGINCASE B ISWHEN "0000"=> BI<="0111111";WHEN "0001"=> BI<="0000110";WHEN "0010"=> BI<="1011011";WHEN "0011"=> BI<="1001111";WHEN "0100"=> BI<="1100110";WHEN "0101"=> BI<="1101101";WHEN "0110"=> BI<="1111101";WHEN "0111"=> BI<="0100111";WHEN "1000"=> BI<="1111111";WHEN "1001"=> BI<="1101111";WHEN "1010"=> BI<="1110111";WHEN "1011"=> BI<="1111100";WHEN "1100"=> BI<="0111001";WHEN "1101"=> BI<="1011110";WHEN "1110"=> BI<="1111001";WHEN OTHERS=> BI<="1110001"; END CASE; END PROCESS; END bhv;注意:编程下载之前,将扬声器下方的 JDSP 跳线开关跳至“ close ”任意电 路模式皆可。

EDA技术应用期末论文题目:八位数码管动态显示姓名:班级:学号:1.系统总体方案设计 (1)2. LED的工作原理 (2)2.1 LED工作原理 (3)2.2 LED动态扫描显示原理 (3)3.系统设计 (4)3.1硬件电路设计 (9)3.2 VHDL代码设计 (9)4.运行调试......................................................,,7 4.1时序仿真. (7)5 总结..............................................,,,,,,,,,,,,,,,96.参考文献 (10)1.系统总体方案设计设计流程图如下:首先,我们要对所要设计的八位数码管静态扫描显示电路充分理解,同时在了解了所给的硬件器材的基础上需进行“源程序的编辑和编译”——用一定的逻辑表达手段将设计表达出来;其次要进行“逻辑综合”——将用一定的逻辑表达手段表达出来的设计,经过一系列的操作,分解成一系列的基本逻辑电路及对应关系;然后要进行“目标器件的布线∕适配”——在选定的目标器件中建立这些基本逻辑电路及对应关系;最后,目标器件的编程下载——将前面的软件设计经过编程变成具体的设计系统,同时在设计过程中要进行有关“仿真”——模拟有关设计结果,看是否与设计构想相符。

系统结构框图如下:2. LED的工作原理2.1 LED工作原理LED为分段式半导体显示器,通常称为七段发光二极管显示器。

下图为七段发光二极管显示器共阴极和共阳极的电路图。

对共阴极显示器的公共端应接地,给a-g输入相应高电平,对应字段的发光二极管显示十进制数;对共阳极的公共端应接+5V电源,给a-g输入端相应低电平,对应字段的发光二极管也显示十进制数。

2.2 LED动态扫描显示原理LED有段码和位码之分,所谓段码就是让LED显示出“8.”的八位数据,一般情况下要通过一个译码电路,将输入的4位2进制数转换为与LED显示对应的8位段码。

实验2原理图输入法设计8位二进制全加器一、实验目的进一步熟悉QuartusⅡ的使用方法,学习时序仿真。

二、实验内容用V erilog HDL设计一个8位二进制全加器。

可以直接编写程序,也可以利用例化语句调用1位全加器构成8位全加器。

并进行编译、综合、适配和仿真。

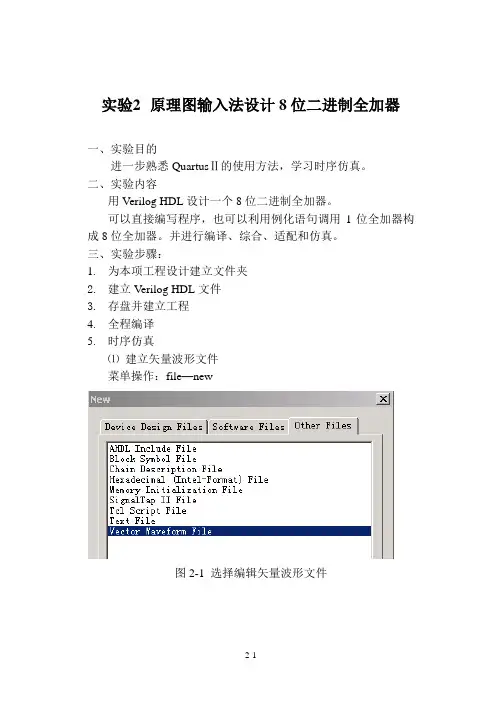

三、实验步骤:1.为本项工程设计建立文件夹2.建立V erilog HDL文件3.存盘并建立工程4.全程编译5.时序仿真⑴建立矢量波形文件菜单操作:file—new图2-1 选择编辑矢量波形文件图2-2 波形编辑器⑵设置仿真时间长度菜单操作:Edit—end time图2-3 设置仿真时间长度⑶存盘图2-4 vwf激励波形文件存盘⑷将工程test2的端口信号选入波形编辑器中。

菜单操作:View—Utility Windows—Node Finder,并按图2-5 向波形编辑器拖入信号节点选项:Look:工程名;filer:Pins all⑸编辑输入波形单击输入信号a使之变成蓝色条,激活波形编辑器图2-6波形编辑器按图2-7设置输入信号a的周期在Tool Zoom 状态下调整波形图图2-8 设置好的激励波形图⑹菜单操作:Assignments –setting进入以下窗口:图2-9 选择仿真控制图2-10 仿真波形输出图2-11 选择全时域显示⑺仿真:Processing-Start Simulation 或。

注:该实验也可用硬件测试的方法来验证其设计的正确性。

四、实验报告详细叙述实验内容所要求的设计流程;给出仿真波形图;给时序分析情况。

五、参考程序module ADDER8B(A,B,CIN,COUT,DOUT);output [7:0] DOUT; output COUT;input [7:0] A,B; input CIN; wire [8:0] DA TA;assign DA TA =A+B+CIN;assign COUT=DA TA[8];assign DOUT=DA TA[7:0];endmodule。

“八位数码管动态扫描”案例原理与测试说明

1程序设计目标及程序运行效果说明

本程序是动态扫描所有的数码管,从左到右8个数码管分别显示1、2、3、4、5、6、7、8。

2程序相关电路及工作原理说明

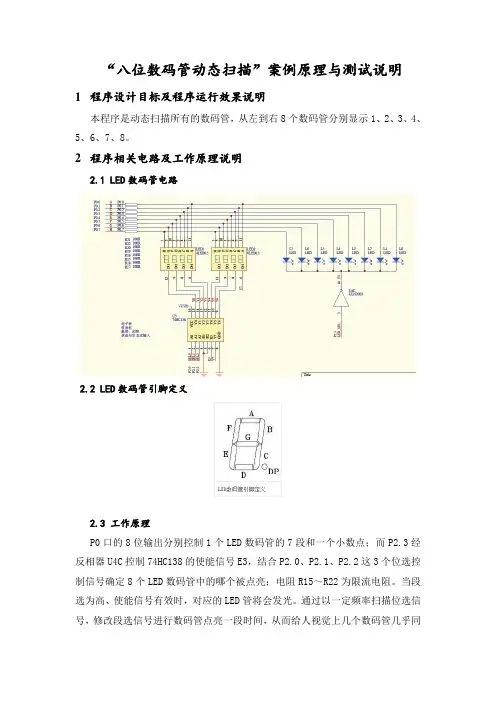

2.1 LED数码管电路

2.2 LED数码管引脚定义

2.3 工作原理

P0口的8位输出分别控制1个LED数码管的7段和一个小数点;而P2.3经反相器U4C控制74HC138的使能信号E3,结合P2.0、P2.1、P2.2这3个位选控制信号确定8个LED数码管中的哪个被点亮;电阻R15~R22为限流电阻。

当段选为高、使能信号有效时,对应的LED管将会发光。

通过以一定频率扫描位选信号,修改段选信号进行数码管点亮一段时间,从而给人视觉上几个数码管几乎同

时显示的效果。

3测试方法

(1)用STC ISP默认设置,打开工程中的HEX并下载

(2)下载后观察现象为:从左到右8个数码管分别显示1、2、3、4、5、6、7、8。

(3)本案例无需辅助操作。

电子课程设计—8位数码管动态显示电路设计学院:电子信息工程学院专业、班级:姓名:学号:指导老师:2014年12月目录一、设计任务与要求................................................. (3)二、总体框图................................................. (3)三、选择器件................................................. (3)四、功能模块................................................. (9)五、总体设计电路图................................................. . (10)六、心得体会.................................................. .. (12)8位数码管动态显示电路设计一、设计任务与要求1. 设计个8位数码管动态显示电路,动态显示1、2、3、4、5、6、7、8。

2. 要求在某一时刻,仅有一个LED数码管发光。

3. 该数码管发光一段时间后,下一个LED发光,这样8只数码管循环发光。

4. 当循环扫描速度足够快时,由于视觉暂留的原因,就会感觉8只数码管是在持续发光。

5、研究循环地址码发生器的时钟频率和显示闪烁的关系。

二、总体框图设计的总体框图如图2-1所示。

图2-1总体框图三、选择器件1、数码管数码管是一种由发光二极管组成的断码型显示器件,如图1所示。

U13DCD_HEX图1 数码管数码管里有八个小LED发光二极管,通过控制不同的LED的亮灭来显示出不同的字形。

数码管又分为共阴极和共阳极两种类型,其实共阴极就是将八个LED 的阴极连在一起,让其接地,这样给任何一个LED的另一端高电平,它便能点亮。

而共阳极就是将八个LED的阳极连在一起。

实验名称八位七段数码管动态显示电路的设计一、实验目的1、了解数码管的工作原理。

2、学习七段数码管显示译码器的设计。

3、学习Verilog的CASE语句及多层次设计方法。

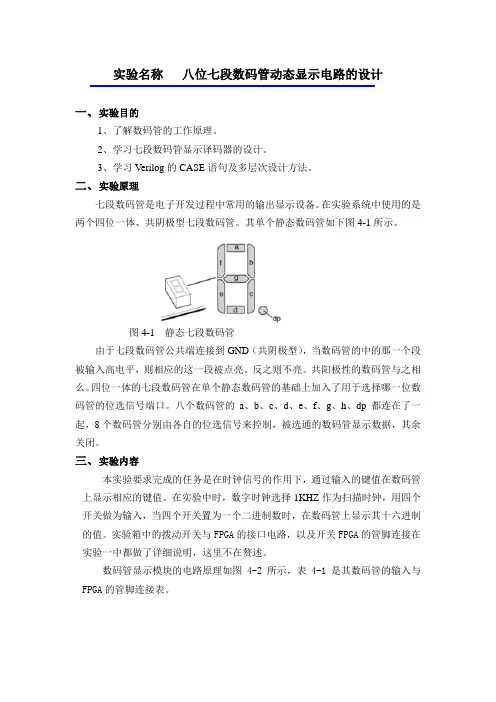

二、实验原理七段数码管是电子开发过程中常用的输出显示设备。

在实验系统中使用的是两个四位一体、共阴极型七段数码管。

其单个静态数码管如下图4-1所示。

图4-1 静态七段数码管由于七段数码管公共端连接到GND(共阴极型),当数码管的中的那一个段被输入高电平,则相应的这一段被点亮。

反之则不亮。

共阳极性的数码管与之相么。

四位一体的七段数码管在单个静态数码管的基础上加入了用于选择哪一位数码管的位选信号端口。

八个数码管的a、b、c、d、e、f、g、h、dp都连在了一起,8个数码管分别由各自的位选信号来控制,被选通的数码管显示数据,其余关闭。

三、实验内容本实验要求完成的任务是在时钟信号的作用下,通过输入的键值在数码管上显示相应的键值。

在实验中时,数字时钟选择1KHZ作为扫描时钟,用四个开关做为输入,当四个开关置为一个二进制数时,在数码管上显示其十六进制的值。

实验箱中的拨动开关与FPGA的接口电路,以及开关FPGA的管脚连接在实验一中都做了详细说明,这里不在赘述。

数码管显示模块的电路原理如图4-2所示,表4-1是其数码管的输入与FPGA的管脚连接表。

图4-2 数字时钟信号模块电路原理信号名称对应FPGA管脚名说明7SEG-A G6 七段码管A段输入信号7SEG-B G7 七段码管B段输入信号7SEG-C H3 七段码管C段输入信号7SEG-D H4 七段码管D段输入信号7SEG-E H5 七段码管E段输入信号7SEG-F H6 七段码管F段输入信号7SEG-G J4 七段码管G段输入信号7SEG-DP L8 七段码管dp段输入信号7SEG-SEL0 G5 七段码管位选输入信号7SEG-SEL1 G3 七段码管位选输入信号7SEG-SEL2 F4 七段码管位选输入信号表4-1 数码管与FPGA的管脚连接表四、实验步骤1、打开QUARTUSII软件,新建一个工程。

河南科技8位数码管显示电路设计2012——20113学年第五学期EDA技术课程考试专业班级:电气106姓名:耀学号:考核老师:1 引言EDA技术是当前数字系统设计领域比较火热的一种工具,他可以大大缩短设计需要的时间,降低成本的同时也提高了系统的稳定性。

使用VHDL语言描述硬件系统使得EDA技术有了更为广阔的空间。

本设计使用了基于Altera公司的开发软件工具Quartus II,使用Verilog HDL语言设计了一款很实用的八位共阴数码管显示驱动电路,由Quartus II生成的RTL图如下:2.1 设计思路设计总框图如下:2.2 总体原理图图1 总体原理图2.3 总体功能介绍由总体原理图可知,原理图中共有五个输入和两个输出。

CLK为时钟输入端,DATA为预显示数据的加载端,在实际应用中可用通信总线代替27位并行总线输入数据,将并口改为串口来简化电路。

LOAD为数据加载端DATA的使能端。

D为移位寄存器的数据加载端,MD 为数据加载端D的使能端。

输出端口LED为数码管显示数据输出端,端口K为数码管位选数据输出端。

总体功能介绍:由CLK输入时钟控制信号,DATA加载待显示的数据。

先将LOAD置0,使加载端DATA的数据被存入内部寄存器。

然后,随着时钟信号的输出,转制电路将内部寄存器中的数据按十进制,依次在输出端口DOUT输出低位到高位。

输出端口COUT为8位移位寄存器的时钟控制端,当寄存器DOUT中被存入数据时,COUT端被置1,使的移位寄存器的时钟输入信号变的有效。

D为移位寄存器的数据加载端,在D端输入FE,通过移位寄存器控制共阴数码管的位选。

MD为数据加载端D的使能端,先将MD置1,使D端口的数据存入移位寄存器中,在数据存入后,将MD置0阻止D端口的数据存入。

输出端口K接数码管的位选端1~8,以控制数码管的动态显示。

3 各个模块的实现3.1二进制转十进制二进制转十进制是通过将待显示的数据用内部的寄存器存储,然后对其除以10取整数部分和对其除以10取余数来实现二进制转十进制。

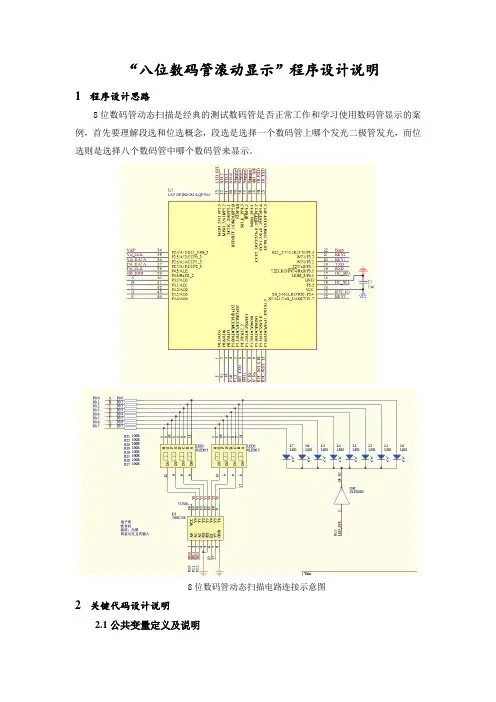

“八位数码管滚动显示”程序设计说明1程序设计思路8位数码管动态扫描是经典的测试数码管是否正常工作和学习使用数码管显示的案例,首先要理解段选和位选概念,段选是选择一个数码管上哪个发光二极管发光,而位选则是选择八个数码管中哪个数码管来显示。

8位数码管动态扫描电路连接示意图2关键代码设计说明2.1公共变量定义及说明sbit Sel0=P2^0;//sbit Sel1=P2^1;//sbit Sel2=P2^2;//位选的三个引脚控制位uchar show_w1;uchar show_w2;uchar show_w3;uchar show_w4;uchar show_w5;uchar show_w6;uchar show_w7;uchar show_w8;//show_wi(i=1,2,3,4,……,8)分别是对应左到右的各个数码管上的显示的数字uchar flag;//分频作用,同时用作位选下标uchar count;//分频作用的变量uchar duanxuan[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f,0x77,0x7c, 0x39,0x5e,0x79,0x71,0x40,0x00}; //段选,显示0-fuchar weixuan[]={0x00,0x01,0x02,0x03,0x04,0x05,0x06,0x07}; //位选,选择是0-7中的一个数码管2.2 Init():完成初始化配置;(1)P0和P2口需要设置成推挽模式输出,以驱动LED数码管正常显示。

P2M1=0x00; P2M0=0xff; P0M1=0x00; P0M0=0xff;(2)TMOD=0x01; //定时器0采用模式1(3)打开中断并允许定时器0中断EA=1;//打开总中断ET0=1;//允许定时器0中断TR0=1;//启动定时器0(4)设置定时器初始值TH0=(65535-1000)/256; TL0=(65535-1000)%256;(5)设置位选位flag初始值为0;(6)为每个数码管要显示的内容赋初值show_w1=0;show_w2=1;show_w3=2;show_w4=3;show_w5=4;show_w6=5;show_w 7=6;show_w8=7;2.3void timer0() interrupt 1当定时器0初始值不断加一最终溢出时激发的处理方法。

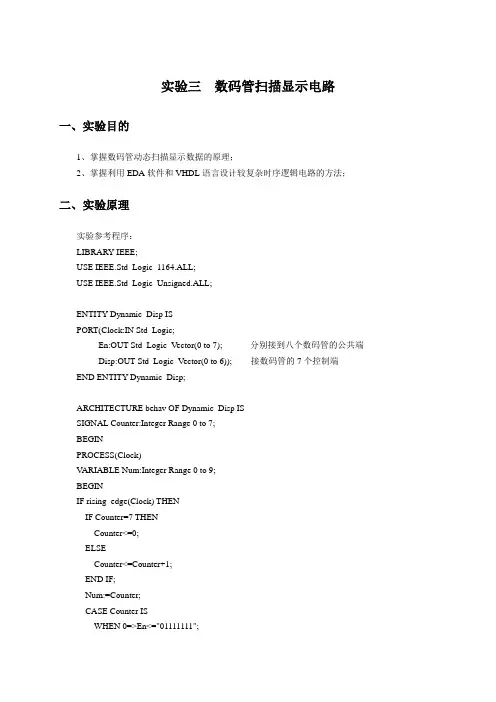

实验三数码管扫描显示电路一、实验目的1、掌握数码管动态扫描显示数据的原理;2、掌握利用EDA软件和VHDL语言设计较复杂时序逻辑电路的方法;二、实验原理实验参考程序:LIBRARY IEEE;USE IEEE.Std_Logic_1164.ALL;USE IEEE.Std_Logic_Unsigned.ALL;ENTITY Dynamic_Disp ISPORT(Clock:IN Std_Logic;En:OUT Std_Logic_Vector(0 to 7); --分别接到八个数码管的公共端Disp:OUT Std_Logic_Vector(0 to 6)); --接数码管的7个控制端END ENTITY Dynamic_Disp;ARCHITECTURE behav OF Dynamic_Disp ISSIGNAL Counter:Integer Range 0 to 7;BEGINPROCESS(Clock)V ARIABLE Num:Integer Range 0 to 9;BEGINIF rising_edge(Clock) THENIF Counter=7 THENCounter<=0;ELSECounter<=Counter+1;END IF;Num:=Counter;CASE Counter ISWHEN 0=>En<="01111111";WHEN 1=>En<="10111111";WHEN 2=>En<="11011111";WHEN 3=>En<="11101111";WHEN 4=>En<="11110111";WHEN 5=>En<="11111011";WHEN 6=>En<="11111101";WHEN 7=>En<="11111110";WHEN OTHERS=>En<="111111";END CASE;CASE Num ISWHEN 0 =>Disp<="1111110";WHEN 1 =>Disp<="0110000";WHEN 2 =>Disp<="1101101";WHEN 3 =>Disp<="1111001";WHEN 4 =>Disp<="0110011";WHEN 5 =>Disp<="1011011";WHEN 6 =>Disp<="1011111";WHEN 7 =>Disp<="1110000";WHEN 8 =>Disp<="1111111";WHEN 9 =>Disp<="1110011";WHEN OTHERS=>Disp<="0000000";END CASE;END IF;END PROCESS;END;常用的显示器件有发光二极管、数码管、液晶显示器等,其中最常用的是数码管。

《EDA技术》实验报告实验名称: 8位二进制全加器设计

姓名:

班级:

学号:

实验日期:2010-3-29

指导教师:

一、实验设计要求

以一位二进制全加器为基本元件,用例化语句写出8位并行二进制全加器的顶层文件,并讨论此加法器的电路特性。

二、设计原理

电路结构图或原理图

电路功能描述

定义了8位二进制全加器顶层设计元件端口信号,输入端口:AIN, BIN,是八个二进制数,数据类型被定义为STD_LOGIC_VECTOR。

CIN是输入的进位,数据类型IN STD_LOGIC;输出端口:SUM为和,数据类型IN STD_LOGIC COUT 为输出的进位。

三、实验程序

程序1:一位二进制全加器设计顶层描述

程序2:8位并行二进制全加器顶层文件

四、编译及仿真结果

选用器件型号cyclone

编译后使用器件资源情况、引脚配置情况(硬件实验)

仿真结果显示:

该设计是成功的。

输入的进位也要加上去。

0---255 全加器的COUNT 没有进位,而当加到256,COUNT=1,SUM输出0.

五、总结

.1 编译不通过,检查后发现在建立工程时,同一工程的所有文件都必须放在同一文件夹中,而这一步没做。

2 程序中没有将文件名与实体名保持一致出错。

输入半加器的VHDL程序保存文件,将输入的VHDL语言程序保存为h _adder.vhd.

3不知道如何将输入/输出引脚号都添加到矢量波形编辑窗口中。

解决办法:view—utility window—noder finder 将需要引脚拖拽。

EDA设计课程实验报告实验题目:数码管动态显示实验学院名称:专业:电子信息工程班级:姓名:高胜学号小组成员:指导教师:一、实验目的学习动态扫描显示的原理;利用数码管动态扫描显示的原理编写程序,实现自己的学号的显示。

二、设计任务及要求1、在SmartSOPC实验箱上完成数码管动态显示自己学号的后八个数字。

2、放慢扫描速度演示动态显示的原理过程。

三、系统设计1、整体设计方案数码管的八个段a,b,c,d,e,f,g,h(h是小数点)都分别连接到SEG0~SEG7,8个数码管分别由八个选通信号DIG0~DIG7来选择,被选通的数码管显示数据,其余关闭。

如果希望8个数码管显示希望的数据,就必须使得8个选通信号DIG0~DIG7分别被单独选通,并在此同时,在段信号输入口SEG0~SEG7加上该对应数码管上显示的数据,于是随着选通信号的扫描就能实现动态扫描显示的目的。

虽然每次只有1个数码管显示,但只要扫描显示速率足够快,利用人眼的视觉余辉效应,我们仍会感觉所有的数码管都在同时显示。

2、功能模块电路设(1)输入输出模块框图(见图1)图1(2)模块逻辑表达(见表1)表1(数码管显示真值表)clk_1k dig seg↑01111111 C0↑10111111 F9注:数码管显示为01180121(3)算法流程图(见图2)(4)Verilog源代码module scan_led(clk_1k,d,dig,seg); //模块名scan_ledinput clk_1k; //输入时钟input[31:0] d; //输入要显示的数据output[7:0] dig; //数码管选择输出引脚output[7:0] seg; //数码管段输出引脚reg[7:0] seg_r; //定义数码管输出寄存器reg[7:0] dig_r; //定义数码管选择输出寄存器reg[3:0] disp_dat; //定义显示数据寄存器reg[2:0]count; //定义计数寄存器assign dig = dig_r; //输出数码管选择assign seg = seg_r; //输出数码管译码结果always @(posedge clk_1k) //定义上升沿触发进程begincount <= count + 1'b1;endalways @(posedge clk_1k)begincase(count) //选择扫描显示数据3'd0:disp_dat = d[31:28]; //第一个数码管3'd1:disp_dat = d[27:24]; //第二个数码管3'd2:disp_dat = d[23:20]; //第三个数码管3'd3:disp_dat = d[19:16]; //第四个数码管3'd4:disp_dat = d[15:12]; //第五个数码管3'd5:disp_dat = d[11:8]; //第六个数码管3'd6:disp_dat = d[7:4]; //第七个数码管3'd7:disp_dat = d[3:0]; //第八个数码管endcasecase(count) //选择数码管显示位3'd0:dig_r = 8'b01111111; //选择第一个数码管显示3'd1:dig_r = 8'b10111111; //选择第二个数码管显示3'd2:dig_r = 8'b11011111; //选择第三个数码管显示3'd3:dig_r = 8'b11101111; //选择第四个数码管显示3'd4:dig_r = 8'b11110111; //选择第五个数码管显示3'd5:dig_r = 8'b11111011; //选择第六个数码管显示3'd6:dig_r = 8'b11111101; //选择第七个数码管显示3'd7:dig_r = 8'b11111110; //选择第八个数码管显示endcaseendalways @(disp_dat)begincase(disp_dat) //七段译码4'h0:seg_r = 8'hc0; //显示04'h1:seg_r = 8'hf9; //显示14'h2:seg_r = 8'ha4; //显示24'h3:seg_r = 8'hb0; //显示34'h4:seg_r = 8'h99; //显示44'h5:seg_r = 8'h92; //显示54'h6:seg_r = 8'h82; //显示64'h7:seg_r = 8'hf8; //显示74'h8:seg_r = 8'h80; //显示84'h9:seg_r = 8'h90; //显示94'ha:seg_r = 8'h88; //显示a4'hb:seg_r = 8'h83; //显示b4'hc:seg_r = 8'hc6; //显示c4'hd:seg_r = 8'ha1; //显示d4'he:seg_r = 8'h86; //显示e4'hf:seg_r = 8'h8e; //显示fendcaseendendmodule四、系统调试(1)仿真代码`timescale 1ns/1nsmodule scan_ledfz;reg clk_1k;reg[31:0] d;wire[7:0] dig;wire[7:0] seg;parameter dely=100;scan_led u1(clk_1k,d,dig,seg);always #(dely/2)clk_1k=~clk_1k;initial beginclk_1k=0;d=32'h01180134;#dely ;#dely ;#dely ;#dely ;#dely ;#(dely*20);#dely $finish;endinitial $monitor($time,,,"%b,%d,%h,%h",clk_1k,d,dig,seg); endmodulemodule scan_led(clk_1k,d,dig,seg); //模块名scan_ledinput clk_1k; //输入时钟input[31:0] d; //输入要显示的数据output[7:0] dig; //数码管选择输出引脚output[7:0] seg; //数码管段输出引脚reg[7:0] seg_r; //定义数码管输出寄存器reg[7:0] dig_r; //定义数码管选择输出寄存器reg[3:0] disp_dat; //定义显示数据寄存器reg[2:0] count=3'b000; //定义计数寄存器assign dig = dig_r; //输出数码管选择assign seg = seg_r; //输出数码管译码结果always @(posedge clk_1k) //定义上升沿触发进程begincount <= count + 1'b1;endalways @(posedge clk_1k)begincase(count) //选择扫描显示数据3'd0:disp_dat = d[31:28]; //第一个数码管3'd1:disp_dat = d[27:24]; //第二个数码管3'd2:disp_dat = d[23:20]; //第三个数码管3'd3:disp_dat = d[19:16]; //第四个数码管3'd4:disp_dat = d[15:12]; //第五个数码管3'd5:disp_dat = d[11:8]; //第六个数码管3'd6:disp_dat = d[7:4]; //第七个数码管3'd7:disp_dat = d[3:0]; //第八个数码管endcasecase(count) //选择数码管显示位3'd0:dig_r = 8'b01111111; //选择第一个数码管显示3'd1:dig_r = 8'b10111111; //选择第二个数码管显示3'd2:dig_r = 8'b11011111; //选择第三个数码管显示3'd3:dig_r = 8'b11101111; //选择第四个数码管显示3'd4:dig_r = 8'b11110111; //选择第五个数码管显示3'd5:dig_r = 8'b11111011; //选择第六个数码管显示3'd6:dig_r = 8'b11111101; //选择第七个数码管显示3'd7:dig_r = 8'b11111110; //选择第八个数码管显示endcaseendalways @(disp_dat)begincase(disp_dat) //七段译码4'h0:seg_r = 8'hc0; //显示04'h1:seg_r = 8'hf9; //显示14'h2:seg_r = 8'ha4; //显示24'h3:seg_r = 8'hb0; //显示34'h4:seg_r = 8'h99; //显示44'h5:seg_r = 8'h92; //显示54'h6:seg_r = 8'h82; //显示64'h7:seg_r = 8'hf8; //显示74'h8:seg_r = 8'h80; //显示84'h9:seg_r = 8'h90; //显示94'ha:seg_r = 8'h88; //显示a4'hb:seg_r = 8'h83; //显示b4'hc:seg_r = 8'hc6; //显示c4'hd:seg_r = 8'ha1; //显示d4'he:seg_r = 8'h86; //显示e4'hf:seg_r = 8'h8e; //显示fendcaseendendmodule位码代码仿真代码`timescale 1ns/1nsmodule smg_tp; //测试模块的名字reg [2:0] c; //测试输入信号定义为reg型wire[7:0] dig; //测试输出信号定义为wire型parameter DEL Y=100; //延时100秒wei u1(c,dig); //调用测试对象initial begin //激励波形设定c=3'b0;#DEL Y c=3'b001 ;#DEL Y c=3'b010 ;#DEL Y c=3'b100 ;#DEL Y c=3'b101 ;#DEL Y c=3'b110 ;#DEL Y c=3'b111 ;#DEL Y $finish;endinitial $monitor($time,,,"dig=%d,c=%b ",dig,c); //输出格式i定义endmodulemodule wei(c,dig); //命名模块名字input[2:0] c;output[7:0] dig; //定义输入与输出reg[7:0] dig_r;reg[2:0] c_r; // 定义dig_r与c_r2个reg型数据assign dig=dig_r; //将reg型数据转化为wire型数据always @(*) //检测c_r的数据是否变化begin c_r=c;case (c_r)3'b000:dig_r=8'b11111110; //c_r的数据变化而dig_r对于的数据变化3'b001:dig_r=8'b11111101;3'b010:dig_r=8'b11111011;3'b011:dig_r=8'b11110111;3'b100:dig_r=8'b11101111;3'b101:dig_r=8'b11011111;3'b110:dig_r=8'b10111111;3'b111:dig_r=8'b01111111;default: dig_r=8'b11111111;endcase //结束case语句end //结束always语句endmodule //结束程序译码器代码仿真代码`timescale 1ns/1nsmodule duan_tp; //测试模块的名字reg[3:0] a; //测试输入信号定义为reg型wire[7:0] seg; //测试输出信号定义为wire型parameter DEL Y=100; //延时100秒duan u1(a,seg); //调用测试对象initial begin //激励波形设定a=4'b0;#DELY a=4'b0001;#DELY a=4'b0010;#DELY a=4'b0011;#DELY a=4'b0100;#DELY a=4'b0101;#DELY a=4'b0110;#DELY a=4'b0111;#DELY a=4'b1000;#DELY a=4'b1001;#DELY a=4'b1010;#DELY a=4'b1011;#DELY a=4'b1100;#DELY a=4'b1101;#DELY a=4'b1110;#DELY a=4'b1111;#DELY $finish;endinitial $monitor($time,,,"seg=%d,a=%b",seg,a); //输出格式i定义endmodulemodule duan(a,seg); //命名模块名字input[3:0] a;output[7:0] seg; //定义输入与输出reg[7:0] seg_r;reg[3:0] a_r; // 定义seg_r与a_r2个reg型数据assign seg=seg_r; //将reg型数据转化为wire型数据always @(*) //检测c_r的数据是否变化begin a_r=a;case(a_r) //七段译码4'b0000:seg_r = 8'hc0; //显示04'b0001:seg_r = 8'hf9; //显示14'b0010:seg_r = 8'ha4; //显示24'b0011:seg_r = 8'hb0; //显示34'b0100:seg_r = 8'h99; //显示44'b0101:seg_r = 8'h92; //显示54'b0110:seg_r = 8'h82; //显示64'b0111:seg_r = 8'hf8; //显示74'b1000:seg_r = 8'h80; ///显示84'b1001:seg_r = 8'h90; //显示94'b1010:seg_r = 8'h88; //显示a4'b1011:seg_r = 8'h83; //显示b4'b1100:seg_r = 8'hc6; //显示c4'b1101:seg_r = 8'ha1; //显示d4'b1110:seg_r = 8'h86; //显示e4'b1111:seg_r = 8'h8e; ///显示f endcase //结束case语句end //结束always语句endmodule //结束程序(2)仿真波形图(3)引脚图五、实验感想通过这次实验,让我学习动态扫描显示的原理;利用数码管动态扫描显示的原理编写程序,实现自己的学号的显示。

WHEN "1111"=>LED7S<="01110001";WHEN OTHERS=>NULL;END CASE;END PROCESS;END one;Dec7s.vhd 源程序通过编译后,生成的元件符号中a[3..0]是数据输入端,接收cnt4e 的计数状态。

设计8位计数显示译码电路顶层文件。

生成的cnt4e 和Dec7s 图形符号只是代表两个分立的电路设计结果,并没有形成系统。

顶层设计文件就是调用cnt4e 和Dec7s 两个功能元件,将它们组装起来,形成一个完整的设计。

top.bdf 是本例的顶层设计文件,在Quartus II 集成环境下,首先为顶层设计建立工程项目(top ),然后打开一个新文件并进入图形编辑方式。

在图形编辑框中,调出cnt4e 元件符号两个和Dec7s 元件符号两个以及输入(input )和输出(output )元件符号。

top 顶层设计结果图编译顶层设计文件。

不管是用文本编辑方式还是用图形编辑方式形成的电路设计文件,都要通过计算机的编译。

在完成对图形编辑文件的编译后,若要生成元件符号,则要执行“File”→“Greate/Update”菜单下的“Create Symbol Files for Current File”命令,为图形设计文件生成元件符号。

仿真顶层设计文件8位计数显示译码电路的仿真波形【实验数据整理与归纳】Dec7s 元件符号top11.bdftop11.vwf【实验结果与分析】计数译码系统电路的仿真波形如图top11.vwf所示,其中数据“3F”是电路输出端q[0:15]送给七段数码管显示“00”的数据;“06”是显示“01”的数据;依此类推。

仿真结果验证了设计的正确性。

【实验中遇到的问题及解决方案】1.由于对软件不够熟悉,不知道如何生成元件符号。

解决方案:上网搜寻教程。

2.仿真失败。

解决方案:根据软件提示发现是没有生成网表,生成网表后仿真成功。

频率是电子技术领域内的一个基本参数,同时也是一个非常重要的参数。

稳定的时钟在高性能电子系统中有着举足轻重的作用,直接决定系统性能的优劣。

伴随着集成电路(IC)技术的发展,电子设计自动化(EDA)逐渐成为重要的设计手段,已经广泛应用于模拟与数字电路系统等许多领域。

EDA的一个重要特征就是使用硬件描述语言(HDL)来完成的设计文件,它与电子技术、微电子技术的发展密切相关,它吸收了计算机科学领域的大多数最新研究成果,以高性能的计算机作为工作平台,促进了工程发展,在电子设计领域受到了广泛的接受。

本文首先综述了EDA技术的发展概况,FPGA/CPLD开发的流程、优缺点,VHDL语言,MAX+pLUS II简介;然后介绍了频率测量的一般原理,接着使用EDA技术,用VHDL语言完成了数字频率计系统的软件、硬件设计工作;最后介绍了EDA技术的前沿发展趋势及其展望。

关键词:电子设计自动化(EDA);GW48 EDA系统;FPGA/CPLD;VHDL语言;数字频率计;频率测量;数码管扫描显示;波形仿真Frequency is a basic parameter of electronics field,meanwhile.I t’s a very important parameter.Stable clock is very important in high performance electronics system,determining the syetem performance directly. Follows the integrated circuit (IC) technology development, the electronic design automation (EDA) is becoming the important design method gradually.The key character of EDA uses the design document which hardware description language (HDL) completes, has received widespread acceptance in the electronic design domain.This article first summarized the EDA technology development survey, the FPGA/CPLD development flow, the good and bad points, the VHDL language history, development step and merit.Then uses the EDA technology, has completed the digital frequency meter system's project work with the VHDL language;Finally briefed in the EDA technology front trend of development and system development several experiences.Keywords:Electronic design automation (EDA);GW48 EDA system;FPGA/CPLD; VHDL language;Digital cymometer; Frequency measurement;Nixietube scanning demonstration;Profile simulation;目录引言 (1)第1章、EDA的发展历程及其应用 (2)1.1电子设计自动化(EDA)发展概述 (2)1.1.1什么是电子设计自动化(EDA) (2)1.1.2 EDA的发展阶段及特点 (2)1.1.3、EDA的应用 (3)1.2基于EDA的FPGA/CPLD的开发 (4)1.2.1 FPGA/CPLD的介绍 (4)1.2.2基于EDA工具的FPGA/CPLD开发流程 (4)1.2.3用FPGA/CPLD开发的优缺点 (5)1.3 VHDL语言 (5)1.4 MAX+PLUS II介绍 (6)第2章、数字频率计的设计 (8)2.1频率计设计背影 (8)2.2频率计设计原理 (8)2.2.1直接测频法 (8)2.2.2多周期同步测频法 (9)2.3频率计发展现状 (10)2.4频率计的设计实现 (11)第3章、基于EDA的数字频率计软件设计 (12)3.1系统顶层模块设计 (12)3.2各模块设计及源程序 (13)3.2.1测频控制信号模块TESTCTL: (14)3.2.2十进制计数模块 CNT10 : (15)3.2.3 32位锁存模块REG32B: (16)3.2.4数码显示电路 (17)3.3各系统仿真时序波形图 (18)第四章、基于EDA的数字频率计硬件设计 (20)4.1硬件实现 (20)4.2实验结果分析 (21)第五章结论 (22)第六章展望 (23)参考文献 (24)谢辞 (25)引言在电子设计领域中,EDA 技术是以大规模可编程逻辑器件为设计载体 ,以硬件语言为系统逻辑描述的主要方式 ,以计算机、大规模可编程逻辑器件的开发软件及实验开发系统为设计工具 ,通过有关的开发软件 ,自动完成用软件设计的电子系统到硬件系统的设计 ,最终形成集成电子系统或专用集成芯片的一门新技术。

EDA实验二八位七段数码管动态显示电路的设计八位七段数码管动态显示电路是一种常用的显示电路,用于将数字信号转换成七段数码管的显示形式。

本文将详细介绍八位七段数码管动态显示电路的设计原理和实现方法。

首先,我们先介绍一下七段数码管的基本原理和工作方式。

一、七段数码管的基本原理和工作方式七段数码管通常由七个独立的LED组成,分别代表数字0到9和字母A到F。

这七个LED分别为a,b,c,d,e,f,g,用于显示不同的数字。

通过控制每个LED的亮灭状态,可以显示出不同的数字。

七段数码管通常采用共阳极或共阴极的方式控制。

在共阳极的情况下,数码管的共阳极引脚接Vcc,每个LED的阴极引脚分别通过控制芯片上的开关来控制灯的亮灭;在共阴极的情况下,数码管的共阴极引脚接GND,每个LED的阳极引脚通过控制芯片上的开关来控制灯的亮灭。

根据实际需要选择共阳极或共阴极的七段数码管。

在七段数码管中,每个LED代表一个计算机的位数。

例如,数码管中的aLED表示计算机数据的最低位,而gLED表示计算机数据的最高位。

二、八位七段数码管动态显示电路的设计原理八位七段数码管动态显示电路的设计原理是将八个七段数码管连接在一起,通过改变每个数码管的亮灭状态,实现数字的动态显示。

具体的设计原理是通过一个计数器生成7个时序信号,然后再通过逻辑控制器将这些时序信号分配给各个数码管。

可以用三个个位计数器来实现生成的7个时序信号。

其中,一个计数器用于控制7个段的扫描,即a,b,c,d,e,f,g;另外两个计数器用于控制8位数码管中的8个数位,即1,2,3,4,5,6,7,8具体实现时,可以通过一个时钟信号来驱动计数器,每个计数器都有一个计数使能信号和一个计数复位信号。

通过适当的设计时钟信号的频率和计数使能/复位信号的控制,可以实现不同的动态显示效果。

三、八位七段数码管动态显示电路的实现方法八位七段数码管动态显示电路的实现方法可以分为三个步骤:计数器设计、逻辑控制器设计和电路布线。

电子课程设计—8位数码管动态显示电路设计学院:电子信息工程学院专业、班级:姓名:学号:指导老师:2014年12月目录一、设计任务与要求................................................. (3)二、总体框图................................................. (3)三、选择器件................................................. (3)四、功能模块................................................. (9)五、总体设计电路图................................................. . (10)六、心得体会.................................................. .. (12)8位数码管动态显示电路设计一、设计任务与要求1. 设计个8位数码管动态显示电路,动态显示1、2、3、4、5、6、7、8。

2. 要求在某一时刻,仅有一个LED数码管发光。

3. 该数码管发光一段时间后,下一个LED发光,这样8只数码管循环发光。

4. 当循环扫描速度足够快时,由于视觉暂留的原因,就会感觉8只数码管是在持续发光。

5、研究循环地址码发生器的时钟频率和显示闪烁的关系。

二、总体框图设计的总体框图如图2-1所示。

图2-1总体框图三、选择器件 1、数码管数码管是一种由发光二极管组成的断码型显示器件,如图1所示。

U13DCD_HEX图1 数码管数码管里有八个小LED 发光二极管,通过控制不同的LED 的亮灭来显示出不同的字形。

数码管又分为共阴极和共阳极两种类型,其实共阴极就是将八个LED 的阴极连在一起,让其接地,这样给任何一个LED 的另一端高电平,它便能点亮。

EDA技术应用期末论文题目:八位数码管动态显示姓名:班级:学号:1.系统总体方案设计 (1)2. LED的工作原理 (2)2.1 LED工作原理 (3)2.2 LED动态扫描显示原理 (3)3.系统设计 (4)3.1硬件电路设计 (9)3.2 VHDL代码设计 (9)4.运行调试......................................................,,7 4.1时序仿真. (7)5 总结..............................................,,,,,,,,,,,,,,,96.参考文献 (10)1.系统总体方案设计设计流程图如下:首先,我们要对所要设计的八位数码管静态扫描显示电路充分理解,同时在了解了所给的硬件器材的基础上需进行“源程序的编辑和编译”——用一定的逻辑表达手段将设计表达出来;其次要进行“逻辑综合”——将用一定的逻辑表达手段表达出来的设计,经过一系列的操作,分解成一系列的基本逻辑电路及对应关系;然后要进行“目标器件的布线∕适配”——在选定的目标器件中建立这些基本逻辑电路及对应关系;最后,目标器件的编程下载——将前面的软件设计经过编程变成具体的设计系统,同时在设计过程中要进行有关“仿真”——模拟有关设计结果,看是否与设计构想相符。

系统结构框图如下:2. LED的工作原理2.1 LED工作原理LED为分段式半导体显示器,通常称为七段发光二极管显示器。

下图为七段发光二极管显示器共阴极和共阳极的电路图。

对共阴极显示器的公共端应接地,给a-g输入相应高电平,对应字段的发光二极管显示十进制数;对共阳极的公共端应接+5V电源,给a-g输入端相应低电平,对应字段的发光二极管也显示十进制数。

2.2 LED动态扫描显示原理LED有段码和位码之分,所谓段码就是让LED显示出“8.”的八位数据,一般情况下要通过一个译码电路,将输入的4位2进制数转换为与LED显示对应的8位段码。

位码也就是LED的显示使能端,对于共阳级的LED而言,高电平使能。

要让8个LED同时工作,显示数据,就是要不停的循环扫描每一个LED,并在使能每一个LED的同时,输入所需显示的数据对应的8位段码。

虽然8个LED是依次显示,但是受视觉分辨率的影响,看到的现象是8个LED同时工作。

多个数码管动态扫描显示,是将所有数码管的相同段并联在一起,通过选通信号分时控制各个数码管的公共端,循环点亮多个数码管,并利用人眼的视觉暂留现象,只要扫描的频率大于50Hz,将看不到闪烁现象。

3 系统设计3.1 硬件电路设计3.2 VHDL程序设计library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_signed.all;entity scan_seg8 isport(clk3,clk5:in std_logic;rst: in std_logic;seg_da:out std_logic_vector(7 downto 0);seg_sel:out std_logic_vector(2 downto 0));end scan_seg8;architecture ado of scan_seg8 issignalseg_buf1,seg_buf2,seg_buf3,seg_buf4,seg_buf0:std_logic_vector(3 downto 0);signal seg_buf5,seg_buf6,seg_buf7,seg_buf8:std_logic_vector(3 downto 0);signal seg_cnt:std_logic_vector(2 downto 0);signal seg_temp:std_logic_vector(3 downto 0);signal clk:std_logic;beginprocess(clk5)beginif clk5'event and clk5='1' thenclk<=not clk;end if;end process;process(clk5,rst)beginif clk5' event and clk5='1' thenif clk='1' thenseg_buf1<="0010";seg_buf2<="0010";seg_buf3<="1000";seg_buf4<="0010";seg_buf5<="0000";seg_buf6<="0001";seg_buf7<="0000";seg_buf8<="0010";elseseg_buf1<="1111";seg_buf2<="1111";seg_buf3<="1111";seg_buf4<="1111";seg_buf5<="1111";seg_buf6<="1000";seg_buf7<="0001";seg_buf8<="0000";end if;end if;end process;process (clk3,rst)beginif clk3' event and clk3='1' thenif rst='1' thenseg_cnt<="000";elseseg_cnt<=seg_cnt+1;end if;end if;end process;seg_sel<=seg_cnt;process(seg_cnt,seg_buf1,seg_buf2,seg_buf3,seg_buf4,seg_buf5,seg_buf6 ,seg_buf7,seg_buf8)begincase seg_cnt iswhen o"0" => seg_temp<=seg_buf1;when o"1" => seg_temp<=seg_buf2;when o"2" => seg_temp<=seg_buf3;when o"3" => seg_temp<=seg_buf4;when o"4" => seg_temp<=seg_buf5;when o"5" => seg_temp<=seg_buf6;when o"6" => seg_temp<=seg_buf7;when o"7" => seg_temp<=seg_buf8;when others=> seg_temp<="XXXX";end case;end process;process(seg_temp)begincase seg_temp iswhen "0000"=> seg_da<="00111111";when "0001"=> seg_da<="00000110";when "0010"=> seg_da<="01011011";when "0011"=> seg_da<="01001111";when "0100"=> seg_da<="01100110";when "0101"=> seg_da<="01101101";when "0110"=> seg_da<="01111101";when "0111"=> seg_da<="00000111";when "1000"=> seg_da<="01111111";when "1001"=> seg_da<="01101111";when "1010"=> seg_da<="01110111";when "1011"=> seg_da<="01111100";when "1100"=> seg_da<="00111001";when "1101"=> seg_da<="01011110";when "1110"=> seg_da<="01111001";when "1111"=> seg_da<="00000000";when others=> null;end case;end process;end architecture ado;4 运行调试4.1 时序仿真(1)建立波形文件。

选择File项及其New,再选择New窗中的Waveform Editer..项,打开波形编辑窗。

(2)输入信号节点。

在波形编辑窗的上方选择Node项,在下拉菜单中选择输入信号,在弹出的窗口中首先点击List键,这时左窗口将列出设计所以信号节点。

由于设计者有时只需要观察其中部分信号的波形,因此要利用中间的“=>”键将需要观察的信号选到右栏中,然后点击OK键即可将测试信号。

(3)设置波形参量。