F2812外部接口XINTF资料

- 格式:docx

- 大小:20.37 KB

- 文档页数:7

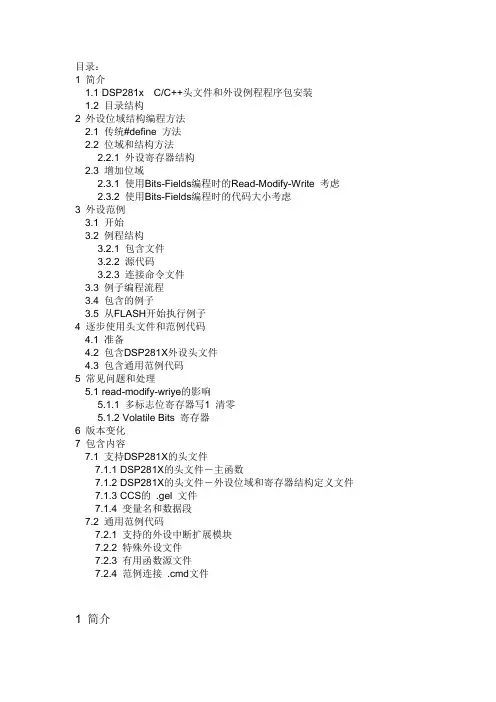

目录:1 简介1.1 DSP281x C/C++头文件和外设例程程序包安装1.2 目录结构2 外设位域结构编程方法2.1 传统#define 方法2.2 位域和结构方法2.2.1 外设寄存器结构2.3 增加位域2.3.1 使用Bits-Fields编程时的Read-Modify-Write 考虑2.3.2 使用Bits-Fields编程时的代码大小考虑3 外设范例3.1 开始3.2 例程结构3.2.1 包含文件3.2.2 源代码3.2.3 连接命令文件3.3 例子编程流程3.4 包含的例子3.5 从FLASH开始执行例子4 逐步使用头文件和范例代码4.1 准备4.2 包含DSP281X外设头文件4.3 包含通用范例代码5 常见问题和处理5.1 read-modify-wriye的影响5.1.1 多标志位寄存器写1 清零5.1.2 Volatile Bits 寄存器6 版本变化7 包含内容7.1 支持DSP281X的头文件7.1.1 DSP281X的头文件-主函数7.1.2 DSP281X的头文件-外设位域和寄存器结构定义文件7.1.3 CCS的 .gel 文件7.1.4 变量名和数据段7.2 通用范例代码7.2.1 支持的外设中断扩展模块7.2.2 特殊外设文件7.2.3 有用函数源文件7.2.4 范例连接 .cmd文件1 简介TI针对’DSP281x系列DSP芯片使用通用的C/C++语言编写了外设头文件和范例程序。

这些代码可以作为应用的工具或根据使用者的需要而作为开发平台的基础。

传统的编程方法需要程序员自行编写寄存器的H文件和所需的片内外设的初始化、配置文件,与传统的编程方法比较,基于C281x C/C++的头文件提供了软件开发的程序框架,其中包含有寄存器结构定义文件、外设头文件和器件的宏与类型定义等系统所需的各种文件。

通过在那新的或原有的工程文件使用外设头文件,开发者可很容易的使用C或C++语言来控制片上外设。

电气信息类专业课程DSP原理及应用——跟我动手学TMS320F2833xDSP原理及应用第5.2节外部接口(XINTF)外部接口XINTF:DSP与外部并口器件通信。

•F2833x系列芯片的XINTF映射到了3个固定的存储区域;•每个区域都可以配置为不同的等待状态数、建立及保持时序;•当在PCLKCR3寄存器中使能XINTF模块时钟时,所有区域均被使能。

外部地址总线XA是20位宽,被所有区域共享。

总线产生什么样的地址取决于哪一区域被访问。

•区域0:使用的外部地址是0x00000~0x00FFF,即当访问区域0第一个存储地址时,总线产生外部地址0x00000和片选信号0;当访问区域0最后一个存储地址时,总线产生外部地址0x00FFF和片选信号0;•区域6和区域7:这两个区域都使用外部地址0x00000~0xFFFFF,哪一片选信号变低,取决于哪一区域被访问。

“其后紧跟读的写操作流水线保护”•在28xCPU流水线中,一个操作的读阶段在写阶段之前,由于这个顺序,若一写访问后面跟着读操作,则实际中访问顺序可能会颠倒:先读后写。

•针对这一现象,在28x器件中设有相应的硬件保护,防止顺序颠倒。

这些区域被称作是“其后紧跟读的写操作流水线保护”。

“其后紧跟读的写操作流水线保护”•对同一存储单元访问,28xCPU将自动地保护其后紧跟读的写操作。

•区域0是默认受“其后紧跟读的写操作流水线保护”的区域。

•当外设寄存器映射到XINTF区域时,需关心读写的执行顺序。

对某一寄存器的写操作可能会导致另一寄存器状态的更新。

其它区域如何实现“其后紧跟读的写操作流水线保护”?•在写指令和读指令之间至少加三条NOP汇编指令。

如果对代码分析发现流水线因其它原因会暂停,则添加的NOP指令可以少于三条。

•把其它指令移到读指令之前,保证写指令和读指令之间至少隔了3个CPU指令周期。

•使用-mv编译选项,则写指令和读指令之间将自动插入NOP汇编指令。

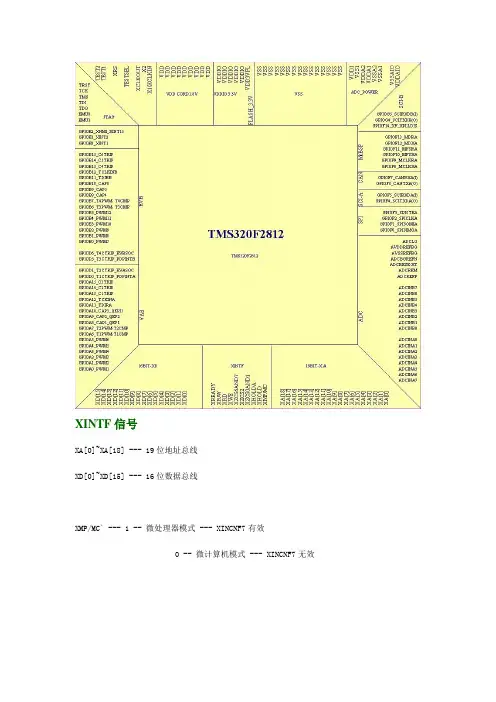

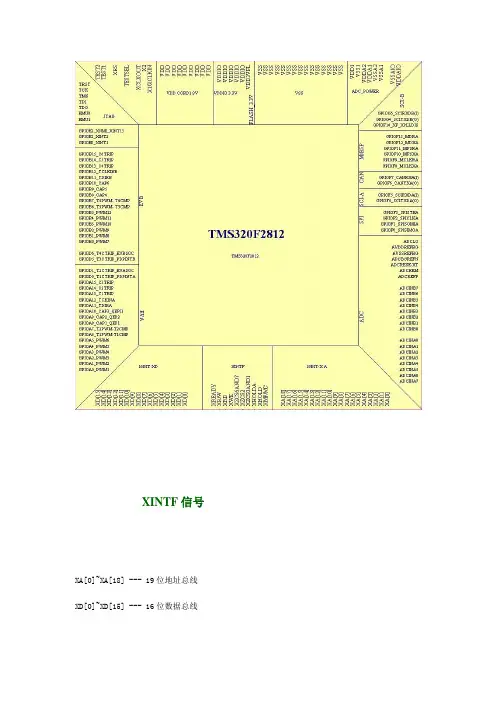

XINTF信号XA[0]~XA[18] --- 19位地址总线XD[0]~XD[15] --- 16位数据总线XMP/MC` --- 1 -- 微处理器模式 --- XINCNF7有效0 -- 微计算机模式 --- XINCNF7无效XHOLD` --- 外部DMA保持请求信号。

XHOLD为低电平时请求XINTF释放外部总线,并把所有的总线与选通端置为高阻态。

当对总线的操作完成且没有即将对XINTF进行访问时,XINTF释放总线。

此信号是异步输入并与XTIMCLK同步XHOLDA` --- 外部DMA保持确认信号。

当XINTF响应XHOLD的请求时XHOLDA呈低电平,所有的XINTF总线和选通端呈高阻态。

XHOLD和XHOLDA信号同时发出。

当XHOLDA有效(低)时外部器件只能使用外部总线XZCS0AND1` --- XINTF区域O和区域1的片选,当访XINTF区域0或1时有效(低)XZCS2` --- XINTF区域2的片选,当访XINTF区域2时有效(低)XZCS6AND7` --- XINTF区域6和区域7的片选,当访XINTF区域6或7时有效(低)XWE` --- 写有效。

有效时为低电平。

写选通信号是每个区域操作的基础,由XTIMINGX寄存器的前一周期、当前周期和后一周期的值确定XRD` --- 读有效。

低电平读选通。

读选通信号是每个区域操作的基础,由xTIMINGX寄存器的前一周期、当前周期和后一周期的值确定。

注意:XRD`和XWE`是互斥信号XR/W` --- 通常为高电平,当为低电平时表示处于写周期,当为高电平时表示处于读周期XREADY --- 数据准备输入,被置1表示外设已为访问做好准备。

XREADY可被设置为同步或异步输入。

在同步模式中,XINTF接口块在当前周期结束之前的一个XTIMCLK时钟周期内要求XREAD Y有效。

在异步模式中,在当前的周期结束前XINTF接口块以XTIMCLK的周期作为周期对XREAD Y采样3次。

XINTF信号XA[0]~XA[18] --- 19位地址总线XD[0]~XD[15] --- 16位数据总线XMP/MC` --- 1 -- 微处理器模式 --- XINCNF7有效0 -- 微计算机模式 --- XINCNF7无效XHOLD` --- 外部DMA保持请求信号。

XHOLD为低电平时请求XINTF释放外部总线,并把所有的总线与选通端置为高阻态。

当对总线的操作完成且没有即将对XINTF进行访问时,XINTF释放总线。

此信号是异步输入并与XTIMCLK同步XHOLDA` --- 外部DMA保持确认信号。

当XINTF响应XHOLD的请求时XHOLDA呈低电平,所有的XINTF总线和选通端呈高阻态。

XHOLD和XHOLDA信号同时发出。

当XHOLDA有效(低)时外部器件只能使用外部总线XZCS0AND1` --- XINTF区域O和区域1的片选,当访XINTF区域0或1时有效(低)XZCS2` --- XINTF区域2的片选,当访XINTF区域2时有效(低)XZCS6AND7` --- XINTF区域6和区域7的片选,当访XINTF区域6或7时有效(低)XWE` --- 写有效。

有效时为低电平。

写选通信号是每个区域操作的基础,由XTIMINGX寄存器的前一周期、当前周期和后一周期的值确定XRD` --- 读有效。

低电平读选通。

读选通信号是每个区域操作的基础,由xTIMINGX寄存器的前一周期、当前周期和后一周期的值确定。

注意:XRD`和XWE`是互斥信号XR/W` --- 通常为高电平,当为低电平时表示处于写周期,当为高电平时表示处于读周期XREADY --- 数据准备输入,被置1表示外设已为访问做好准备。

XREADY可被设置为同步或异步输入。

在同步模式中,XINTF接口块在当前周期结束之前的一个XTIMCLK时钟周期内要求XREAD Y有效。

在异步模式中,在当前的周期结束前XINTF接口块以XTIMCLK的周期作为周期对XREAD Y采样3次。

电气信息类专业课程DSP原理及应用——跟我动手学TMS320F2833xDSP原理及应用第5.2节外部接口(XINTF)外部接口XINTF:DSP与外部并口器件通信。

•F2833x系列芯片的XINTF映射到了3个固定的存储区域;•每个区域都可以配置为不同的等待状态数、建立及保持时序;•当在PCLKCR3寄存器中使能XINTF模块时钟时,所有区域均被使能。

外部地址总线XA是20位宽,被所有区域共享。

总线产生什么样的地址取决于哪一区域被访问。

•区域0:使用的外部地址是0x00000~0x00FFF,即当访问区域0第一个存储地址时,总线产生外部地址0x00000和片选信号0;当访问区域0最后一个存储地址时,总线产生外部地址0x00FFF和片选信号0;•区域6和区域7:这两个区域都使用外部地址0x00000~0xFFFFF,哪一片选信号变低,取决于哪一区域被访问。

“其后紧跟读的写操作流水线保护”•在28xCPU流水线中,一个操作的读阶段在写阶段之前,由于这个顺序,若一写访问后面跟着读操作,则实际中访问顺序可能会颠倒:先读后写。

•针对这一现象,在28x器件中设有相应的硬件保护,防止顺序颠倒。

这些区域被称作是“其后紧跟读的写操作流水线保护”。

“其后紧跟读的写操作流水线保护”•对同一存储单元访问,28xCPU将自动地保护其后紧跟读的写操作。

•区域0是默认受“其后紧跟读的写操作流水线保护”的区域。

•当外设寄存器映射到XINTF区域时,需关心读写的执行顺序。

对某一寄存器的写操作可能会导致另一寄存器状态的更新。

其它区域如何实现“其后紧跟读的写操作流水线保护”?•在写指令和读指令之间至少加三条NOP汇编指令。

如果对代码分析发现流水线因其它原因会暂停,则添加的NOP指令可以少于三条。

•把其它指令移到读指令之前,保证写指令和读指令之间至少隔了3个CPU指令周期。

•使用-mv编译选项,则写指令和读指令之间将自动插入NOP汇编指令。

引 言 TMS320F2812(以下简称F2812)是美国德州仪器公司(TI公司)推出的C2000家族中最新一代产品。

该芯片采用32位操作,大大提高了处理能力,主频可以工作在150 MHz(时钟周期可达6.67 ns),其先进的内部和外设结构使得该处理器主要用于大存储设备管理、高性能的控制场合。

较之C2000系列的其他产品,该芯片的时序操作更加灵活、独立。

为了进一步理解F2812和缓慢外设的接口和设计技术,有必要讨论该芯片时序操作的特点。

1 F2812的读写时序特点 在F2812中,对外部器件的读、写访问都是通过外部接口模块XINTF来实现的。

它类似于C240X的外部接口,但也作了三方面的改进。

①原来的TMS320LF240X系列,程序存储空间、数据存储空间和I/o空间都映射在相同的地址(0000~FFFF),对它们的访问是通过不同的指令来区分的;而在F2812中,外部接口模块分成了5个固定的存储映像区域:XZCS0、XZCSl、XZCS2、XZCS6、XZCS7,可寻址1 MB的片外存储器空间,具有独立的地址。

②F2812的每个XINTF区都 "",{tr}有一个片选信号。

其中,有地区域的片选信号在内部是“与”在一起的,组成了一个共享的芯片选择,比如XZCSo和XZXSl共享一个片选信号XZCSO、ANDI,XZCS6和XZCS7共享一个片选信号XZCS6XZCS7.在这种方式下,同一个外部器件可被连到两个区,或者可以用外部译码逻辑来区分这两个区。

③5个固定存储映像区域的每一个区还可以分别对等待状态数、读写选通信号的建立时间、激活时间和保持时间进行编程。

可编程的等待状态、芯片选择和可编程的选通时间使得该接口与外部存储器及外设脱离了联系,可以灵活、独立地进行外部扩展。

这里,对外部器件进行读、写访问的基时钟是xINTF内部时钟xTIMCLK。

通过写XINTF-CNJF2寄存器的XTIMCLK位,可以将该时钟配置成与SYSCLK0UT相等和等于SYSCLKOUT的1/2,并且,对任何一个映射在XINTF区的外部器件进行读、写访问都可划分为建立、激活和跟踪三个阶段。

第一章F2812头文件1.1 综述TMS320F2812C语言编程实验系统的头文件是由瑞泰科技创新根据TI公司的V.58版改变而来的,既体现了模块化编程的思想,又注意保持了与汇编语言结合使用的特色,非常适合于大型DSP系统软件的设计。

详细的了解头文件的组成,不仅仅有利于加深对于DSP外设寄存的使用,还有利于加强嵌入式系统变成的能力。

本章将首先系统介绍每个头文件的作用,然后将以定时器为例详细讲解结构特点以及语法特性,最后对于某些特别重要的语法现象以及容易出错的地方给出详细的注释。

1.2 头文件的组成以及作用DSP281x_CpuTimers.h 定义定时器寄存器组DSP281x_Adc.h 定义模拟数字转换器寄存器组DSP281x_Ev.h 定义事件管理器寄存器组DSP281x_ECan.h定义CAN通信寄存器组DSP281x_Gpio.h定义多功能输入输出选择寄存器组DSP281x_Mcbsp.h定义多通道缓冲串行口寄存器组DSP281x_Sci.h定义异步串行通信口寄存器组DSP281x_Spi.h定义串行外设接口寄存器组DSP281x_Xintf.h定义外部扩展接口寄存器组DSP281x_PieCtrl.h定义PIE中断控制寄存器组DSP281x_PieVect.h定义中断向量表DSP281x_SysCtrl.h定义系统控制寄存器组DSP281x_Device.h定义芯片功能性变量DSP281x_DevEmu.h定义芯片硬件仿真用寄存器组DSP281x_DefaultIsr.h定义中断服务程序f2812a.h定义开发板功能寄存器1.3定时器寄存组结构分析//########################################################################### //// FILE: DSP281x_CpuTimers.h//文件名称//标题名:反映文件的作用// TITLE: DSP281x CPU 32-bit Timers Register Definitions.//文件注释:版本信息以及修改内容,修订者,日期(符合程序编制标准化思想)// NOTES: CpuTimer1 and CpuTimer2 are reserved for use with DSP BIOS and// other realtime operating systems.//// Do not use these two timers in your application if you ever plan// on integrating DSP-BIOS or another realtime OS.//// For this reason, the code to manipulate these two timers is// commented out and not used in these examples.////########################################################################### //// Ver | dd mmm yyyy | Who | Description of changes//=====|=============|======|============================================= ==// 1.00| 11 Sep 2003 | L.H. | Changes since previous version (v.58 Alpha)// | | | Corrected the definition of the TCR register//############################################################################ifndef DSP281x_CPU_TIMERS_H//如果没有定义了符号,则。

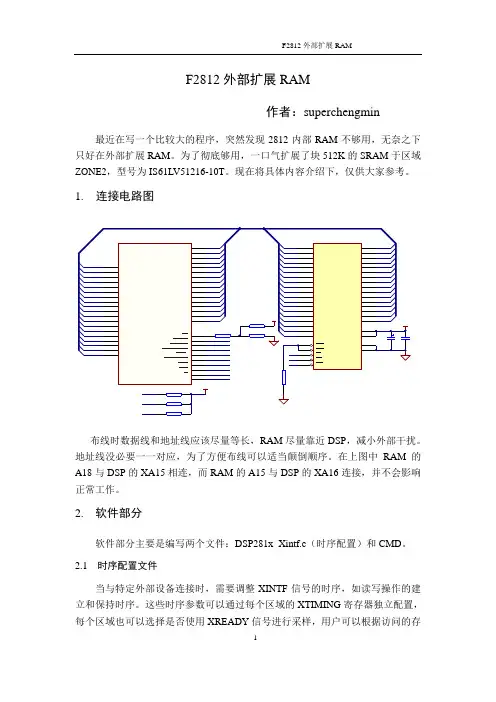

浅谈2812上的外扩接口XINTFXINTF全称是eXternalINTerFace。

一开始我还以为是外部中断,居然用了那么多管脚。

后来拿到现在用的实验板后看例子才知道是外扩接口。

这个功能(模块)只在2812上有,它把外设直接映射到寻址空间的五个区域内。

好处是显而易见的——外扩存储设备具有和片内内存相同的地址空间。

可以直接通过地址进行访问。

上图是来自2812数据手册的XINTF示意图,XINTF的地址范围并不连续,共分为5个区域∙8K的Zone0和Zone1∙512K的Zone2和Zone6∙16K的Zone7用例子来说,当你读取0x2001的时候,这个地址属于zone0,硬件就会在nXZCS0AND1引脚上产生选通信号,转换后的实际地址通过XA线传递给外扩部件,相应的数据通过XD返回到DSP。

从这个意义上来看,XINTF相当于是一个MMU(内存管理单元)。

1).XINTF接口总线映射到5个区,区0,1,2,6,7;2).每个区都有一个内部片选信号,区0,1的片选信号,区6,7的片选信号在内部AND(与)后,通过管脚输出,所以实际的片选信号为三个,XZCS0AND1, XZCS2, XZCS6AND7.3).区2,和区6共享相同的外部总线物理地址,起始外部总线物理地址为0x00000-0x7ffff,两者靠片选信号XZCS0AND1, XZCS2区分。

4). 区0,区1使用相同的片选XZCS0AND1,但是两者外部总线物理地址不同,区0为0x20000-0x3ffff,区1为0x40000-0x5ffff,因此两者的片选XZCS0AND1要和其地址总线的13,14位XA{13],XA[14]通过外部逻辑配合才能产生能够区分区两者的有效片选信号。

5).区7只有当XMP\MC引脚复位的时候被拉高才能被外部总线连接,如果该区复位时未连接,复位后,可以通过XINTCNF2的XMP|MC位,使能该区。

如果区7复位时连接,2812认为复位位置以及向量表存在该区域,因此区7可以存储用户引导程序。

F2812外部接口XINTF什么是外部接口,外部接口有什么作用,怎么去配置和使用这一块。

今天了解了这部分的知识,现将其详细的记录下来。

先看一下什么是外部接口。

外部接口是F2812与外部设备进行通信的重要接口,这些外部接口对应着CPU内部的某个存储空间,CPU通过对存储空间进行的读写操作间接控制外部接口。

书本上抄下来的定义,很是官方啊,不好懂。

再来看一下接的是一些什么,估计是不是会好理解一些呢?一般用于RAM,FLASH等。

哦...估计是内部数据或者是程序存不下了,找一个外面的片子来做存储区扩展用的接口。

外部接口有哪一些线呢?有片选信号线、数据总线、地址总线、读写使能信号线、以及其他信号线。

F2812中外部接口被映射到5个固定的存储空间区域,每个区域都有一个片选信号。

当系统使能片选信号后,数据自动存储到对应的存储空间内。

嘻嘻!就喜欢这一句自动存储。

所有的数字芯片不能少的一条主线就是时钟,这个模块的时钟怎样呢?答:XINTF模块的时序都是参照F2812的内部时钟XTIMCLK。

大小可以人为设定为系统时钟或系统时钟的一半。

F2812中XINTF的使用想使用XINTF先要弄清楚里面有些什么,外面有些什么引脚需要接线。

XINTF一共有5个空间,分别是Zone0、Zone1、Zone2、Zone6、Zone7,每个空间有相应的片选信号线连接到外面。

其中1、2共用一根片选线,6、7共用一根片选线;2、6共用相同的外部地址,外部首地址0x0 0000、尾地址0x7 ffff;1、2占用的外部总线地址不同,0的为0x2000~0x3fff、1的为0x4000~0x5fff;空间7可以作为外部启动的存储空间,由于这个空间的特殊性,所以暂时不打算用,也就不放在这里讨论了。

观察了一下开发板,CPLD的接线为8根数据线,五根地址线,空间0、1共用的片选线,还有R/W读写信号线,WE写使能信号线,RD读使能信号线。

对XINTF空间的操作分为以下三个部分,引导、激活、跟踪。

F2812外部接口XINTF

什么是外部接口,外部接口有什么作用,怎么去配置和使用这一块。

今天了解了这部分的知识,现将其详细的记录下来。

先看一下什么是外部接口。

外部接口是F2812与外部设备进行通信的重要接口,这些外部接口对应着CPU内部的某个存储空间,CPU通过对存储空间进行的读写操作间接控制外部接口。

书本上抄下来的定义,很是官方啊,不好懂。

再来看一下接的是一些什么,估计是不是会好理解一些呢?一般用于RAM,FLASH等。

哦...估计是内部数据或者是程序存不下了,找一个外面的片子来做存储区扩展用的接口。

外部接口有哪一些线呢?有片选信号线、数据总线、地址总线、读写使能信号线、以及其他信号线。

F2812中外部接口被映射到5个固定的存储空间区域,每个区域都有一个片选信号。

当系统使能片选信号后,数据自动存储到对应的存储空间内。

嘻嘻!就喜欢这一句自动存储。

所有的数字芯片不能少的一条主线就是时钟,这个模块的时钟怎样呢?答:XINTF模块的时序都是参照F2812的内部时钟XTIMCLK。

大小可以人为设定为系统时钟或系统时钟的一半。

F2812中XINTF的使用

想使用XINTF先要弄清楚里面有些什么,外面有些什么引

脚需要接线。

XINTF一共有5个空间,分别是Zone0、Zone1、Zone2、Zone6、Zone7,每个空间有相应的片选信号线连接到外面。

其中1、2共用一根片选线,6、7共用一根片选线;2、6共用相同的外

部地址,外部首地址0x0 0000、尾地址0x7 ffff;1、2占用的

外部总线地址不同,0的为0x2000~0x3fff、1的为0x4000~0x5fff;空间7可以作为外部启动的存储空间,由于这个空间的特殊性,所以暂时不打算用,也就不放在这里讨论了。

观察了一下开发板,CPLD的接线为8根数据线,五根地址线,空间0、1共用的片选线,还有R/W读写信号线,WE写使能信号线,RD读使能信号线。

对XINTF空间的操作分为以下三个部分,引导、激活、跟踪。

引导:访问区域的片选信号为低,相应地址放在外设总线上,引导部分的周期通过XTIMCLK来配置时序。

激活:访问外部设备,由于我只进行读操作,所以将读使能信号线拉低,外部接口的数据被锁存到DSP中。

暂不打算使

用XREADY信号采样。

跟踪:跟踪周期是指读写信号置成高电平之后片选信号仍然保持低电平一段时间。

由于是使用开发板,为了使DSP与片外的RAM和FLASH

不产生干扰,将数据配置在空间0、1的片选信号线上,在CPLD 端未接有效的片选信号,相当于不产生任何作用,以防导致整个系统出现不稳定的状态而死掉。

使用这一块的主要目的是接收CPLD发出来的8位并行数据,在激活部分仅仅使用了读信号为低,让DSP一直处于读数据的状态。

使用空间0、1的区别在于不同的地址,所以根据程序来修改,对XINTF模块寄存器做一个分析,其他的空间区域寄存

器也大同小异。

配置寄存器XINTCNF2,可以控制所有的区域空间一样,时序寄存器(XTIMINGx)个空间不同。

配置寄存器。

再给的学习板做给的程序中有这几位做了设定:XTIMCLK=1选择为1/2系统输出时钟;CLKOFF=1关闭XCLKOUT模式,为了节电和减少噪声,复位后该位被置1;CLKMODE=1使得XCLKOUT=XTIMCLK/2;WRBUFF=0没

有写缓冲,CPU等待外部接口访问结束才可以执行程序。

时序寄存器。

USEREADY=0访问区域时XREADY信号被

屏蔽;XSIZE=3只能这样设置呀,不知道是为什么,占有两位数据,其他的三中设置都是错误的哦;XWRACTIVE=7写操

作激活阶段等待状态周期选择为7;XWRTRAIL=3写操作跟

踪阶段周期为3;XWRLEAD=3写操作引导阶段周期为3;

XRDLEAD=3读操作引导;XDACTIVE=7读操作激活;XRDTRAIL=3读操作跟踪;X2TIMING确定上述的六个周期是否需要加倍,=0不加倍,=1为两倍。

XBANK寄存器。

BCYC=7,确定连续访问之间添加的XTIMCLK周期个数;BANK=0,因为暂时打算使用Zone0的空间区域。

好,该设置的寄存器都设置好了,是否能够正常工作了呢,先试一下看看数据能否从D0~D7的管脚锁进到DSP中。

浅谈2812上的外扩接口XINTF

XINTF全称是eXternal INTerFace。

一开始我还以为是外部中断,居然用了那么多管脚。

后来拿到现在用的实验板后看例子才知道是外扩接口。

这个功能(模块)只在2812上有,它把外设直接映射到寻址空间的五个区域内。

好处是显而易见的——外扩存储设备具有和片内内存相同的地址空间。

可以直接通过地址进行访问。

(插图)

上图是来自2812数据手册的XINTF示意图,XINTF的地址范围并不连续,共分为5个区域

8K的Zone0和Zone1

512K的Zone2和Zone6

16K的Zone7

用例子来说,当你读取0×2001的时候,这个地址属于zone0,硬件就会在nXZCS0AND1引脚上产生选通信号,转换后的实际地址通过XA线传递给外扩部件,相应的数据通过XD返回到DSP。

从这个意义上来看,XINTF相当于是一个MMU。

1.XINTF接口总线映射到5个区,区0,1,2,6,7;

2.每个区都有一个内部片选信号,区0,1的片选信号,区6,7

的片选信号在内部AND(与)后,通过管脚输出,所以实际的片选信号为三个,XZCS0AND1, XZCS2, XZCS6AND7. 3.区2,和区6共享相同的外部总线物理地址,起始外部总线物理地址为0x00000-0x7ffff,两者靠片选信号

XZCS0AND1, XZCS2区分。

4.区0,区1使用相同的片选XZCS0AND1,但是两者外部总线物理地址不同,区0为0x20000-0x3ffff,区1为0x40000-0x5ffff,因此两者的片选XZCS0AND1要和其地址总线的13,14位

XA{13],XA[14]通过外部逻辑配合才能产生能够区分区两者的有效片选信号。

(详细方法可见TI相关文档)

5. 区7只有当XMP\MC引脚复位的时候被拉高才能被外部总线连接,如果该区复位时未连接,复位后,可以通过XINTCNF2的XMP|MC位,使能该区。

如果区7复位时连接,2812认为复位位置以及向量表存在该区域,因此区7可以存储用户引导程序。

当区7未映射到外部总线上的时候,区6仍然可以访问区7的物理空间,因为区6的物理空间和区7 是重合的,并且两者使用相同的片选XZCS6AND7,就是说尽管区7未映射,区7的物理空间仍然可以通过区6来使用.

区7的逻辑空间0x3F C000 -0x3F FFFF对应的19位外部地址总线的物理地址为:0x7 c000-0x7 fff,

区6的逻辑空间为:0x10 0000-0x17 ffff,对应的19位外部地址总线的物理地址也为:0x0 0000-0x7 fff,

区7和区6的外部总线的高端物理地址重合.

6.“写紧接着读”流水线保护,由于流水线工作的时候,2812的读修改写操作机制为了提高效率,会先读后写,对于数据存储器来说提高了效率,但是对于外设寄存器会产生状态位错误,因此2812的内部寄存器都带有”写紧接着读”流水线保护保护机制,即写紧接着读这种情况下,仍然是先写后读。

XINTF的区1也有这种“写紧接着读”流水线保护保护机制,因此适合接外部外设。

其他区如果接外部外设,则要人工处理”写紧接着读”这种情况(插入NOP指令)。