MAX4551CEE中文资料

- 格式:pdf

- 大小:330.82 KB

- 文档页数:16

General DescriptionThe MAX9591 evaluation kit (EV kit) demonstrates the MAX9591 reference-voltage generator for gamma cor-rection in TFT-LCD panels, such as those found in high-resolution TVs, high-end monitors, or for general industrial reference-voltage generation. The MAX9591EV kit provides 14 programmable reference-voltage outputs (DAC outputs) and four static buffered refer-ence-voltage outputs (reference outputs). The EV kit uses a 9V to 20V DC power supply for powering the application circuit.The EV kit features a USB-to-I 2C interface circuit.Windows ®2000/XP/Vista ®-compatible software, with a graphical user interface (GUI), is available for exercis-ing the MAX9591 features. The EV kit can also connect to a user-supplied I 2C interface circuit for stand-alone MAX9591 operation.The MAX9591 EV kit can also be used to evaluate the MAX9590ETU+.Features♦14 8-Bit Programmable Reference Voltages (DAC Outputs)♦Four Static Buffered Reference Voltages (Reference Outputs)♦400mA Peak Current on Reference Outputs and DAC Outputs 1, 7, 8, and 14♦200mA Peak Current on DAC Outputs 2–6 and 9–13♦9V to 20V DC Power-Supply Operation ♦USB-Powered USB-to-I 2C Interface Circuit ♦Windows 2000/XP/Vista (32-Bit)-Compatible Software♦Lead-Free and RoHS Compliant ♦Proven PCB Layout♦Fully Assembled and TestedEvaluates: MAX9590/MAX9591MAX9591 Evaluation Kit19-4258; Rev 0; 8/08For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642,or visit Maxim’s website at .Ordering Information+Windows and Windows Vista are registered trademarks of Microsoft Corp.________________________________________________________________Maxim Integrated Products1E v a l u a t e s : M A X 9590/M A X 9591MAX9591 Evaluation Kit 2_______________________________________________________________________________________Quick StartRequired Equipment Before beginning, the following equipment is needed:•MAX9591 EV kit (USB cable included)• A user-supplied Windows 2000/XP/Vista PC with a spare USB port•9V to 20V DC power supply at 500mA•One digital voltmeter (DVM)Note:I n the following sections, software-related items are identified by bolding. Text in bold refers to items directly from the EV kit software. Text in bold and under-lined refers to items from the Windows operating system.Procedure The MAX9591 EV kit is fully assembled and tested. Follow the steps below to verify board operation:1)Visit /evkitsoftware to down-load the latest version of the EV kit software, 9591Rxx.ZIP. Save the EV kit software to a tempo-rary folder and uncompress the ZIP file.2)Install the EV kit software on your computer by run-ning the I NSTALL.EXE program inside the tempo-rary folder. The program files are copied and icons are created in the Windows Start | Programs menu.3)Connect the USB cable from the PC to the EV kitboard. A N ew Hardware Found window pops up when installing the USB driver for the first time. I f you do not see a window that is similar to the one described above after 30s, remove the USB cable from the board and reconnect it. Administrator privi-leges are required to install the USB device driver on Windows.4)Follow the directions of the Add N ew HardwareWizard to install the USB device driver. Choose the Search for the best driver for your device option.Specify the location of the device driver to be C:\Program Files\MAX9591(default installation directory) using the Browse button. During devicedriver installation, Windows might show a warning message indicating that the device driver Maxim uses does not contain a digital signature. This is not an error condition and it is safe to proceed with installation. Refer to the USB_Driver_Help.PDF doc-ument included with the software if there are any problems during this step.5)Once the software and hardware installation is com-plete, disconnect the USB cable from the EV kit.6)Verify that shunts are installed on:•Jumper JU5: Pins 1-2 (on-board 3.3V digital power supply)•Jumper JU6: Pins 1-2 (MAX9591 write address = 0xE8)7)Connect the USB cable to the EV kit.8)Connect the DVM negative terminal to the AGNDPCB pad next to the REFL_L PCB pad.9)Connect a voltage probe to the DVM positive terminalfor later use.10)Set the power supply to 15V and disable the power-supply output.11)Connect the power-supply positive terminal to theAVDD PCB pad and the negative terminal to the AGND PCB pad next to AVDD.12)Enable the power-supply output.13)Start the MAX9591 EV kit software by opening itsicon in the Start | Programs menu. The EV kit soft-ware main window appears, as shown in Figure 1. 14)Use the DVM voltage probe to measure the refer-ence input voltages on the REFU_H, REFU_L, REFL_H and REFL_L PCB pads, and type those val-ues into the corresponding edit boxes of the Reference Voltages (V)group box.15)Press the Quick Start button.16)Use the DVM voltage probe to verify that the DACoutput voltages are close to the voltages shown in the Output (V)edit boxes for the respective channel. Evaluates: MAX9590/MAX9591MAX9591 Evaluation Kit_______________________________________________________________________________________3E v a l u a t e s : M A X 9590/M A X 9591Detailed Description of SoftwareThe MAX9591 evaluation kit (EV kit) software main win-dow is shown in Figure 1. The GUI software automati-cally detects the MAX9591 device address and displays it in the I2C Address Setting drop-down list and in the software status bar. The DAC output volt-ages in the Upper DAC Channels /Lower DAC Channels group boxes are calculated using the upper and lower reference input voltages on PCB pads REFU_H, REFU_L, REFL_H, and REFL_L. The reference input voltages MUST be measured at the appropriate PCB pads and the values entered in the respective Reference Voltages (V)edit boxes for the DAC output calculations to be correct.Upon I C startup, the DAC outputs wake up in high-impedance mode. To exit high-impedance mode, click the Quick Start button or perform the following steps:1)Select the Bank A radio button in the Output BankSelect group box. Select the Bank A Register Settings tab.2)Select the Burst radio button in the RegisterAddressing Mode group box.3)Modify any of the DAC channel’s register values.See the Output Register Values section for more information.4)Press the Load All Values To Registers button.5)Select the Bank B radio button in the Output BankSelect group box. Select the Bank B Register Settings tab. Repeat steps 3 and 4.The Quick Start button loads all bank A and bank B registers with a predefined set of values.MAX9591 Evaluation Kit 4_______________________________________________________________________________________Figure 1. MAX9591 Evaluation Software Main WindowRegister banks A and B are selectable using the radio buttons in the Output Bank Select group box. Register values are modified and loaded to registers using the buttons, edit boxes, and scrollbars of the Bank _Register Settings tabs where _ is either A or B .I 2C Address SettingThe MAX9591’s I 2C slave address is displayed in the status bar of the software window and the I2C Address Setting drop-down list. I f an address is manually selected in the drop-down list, the software verifies the address and changes the address displayed appropri-ately. If no acknowledge is received from the EV kit, a pop-up window is opened directing the user to properly set jumper JU6 on the EV kit. I f the Auto Detect Address checkbox is checked, the software automati-cally detects the I 2C address of the MAX9591.Upper and Lower DAC Output VoltagesThe upper and lower DAC output voltages are generat-ed using an on-board resistor-divider network. The user can also apply external references to the REFU_H,REFU_L, REFL_H, and REFL_L, and AGND PCB pads.The voltages on these four pads MUST be captured and typed into the appropriate edit boxes in the Reference Voltages (V)group box for the calculated DAC output voltages shown in the Upper DAC Channels/Lower DAC Channels group boxes to be correct.The transfer function for the upper DAC channels is:The transfer function for the lower DAC channels is:In both equations, D is the decimal register value. Refer to the MAX9591 IC data sheet for more details.When the evaluation software is run for the first time, the reference input-voltage values in the Reference Voltages (V)group box are loaded from an initialization file (REF.INI). When the program is closed, the current values are logged in to the initialization file. The next time the program is run, the latest values are loaded automatically.Output Bank SelectThe Bank A , Bank B , and A, B Alternating radio but-tons in the Output Bank Select group box choose the set of reference voltages buffered to the outputs between bank A, bank B, or alternating between banks A and B, with 1s hold time for each bank.Output Register ValuesEach DAC channel’s register value can be set in three different ways within the Upper DAC Channels /Lower DAC Channels group boxes by:1)Moving the channel’s scrollbar.2)Typing register values directly into the channel’sReg Value edit box (decimal 8-bit equivalent).3)Typing the expected output voltage in the chan-nel’s Output (V)edit box. The software uses a reg-ister value that generates a voltage closest to the desired voltage value.When a register value is changed, the corresponding field changes its color to red. A user should synchro-nize the GUI fields and actual device registers by pressing either the channel’s Load button (in single mode) or the Load All Values To Registers button (in burst mode).The Load All Reg Values From File button is used to load all the register values and reference voltages from a text file. The Save All Reg Values To File button is used to save all the register values and reference volt-ages on the current GUI to a user-named text file.Register read/write operations can take place regard-less of the output bank setting; for example, the user can change bank B registers when bank A is buffered to the outputs.Register Addressing ModeThe Burst and Single radio buttons in the Register Addressing Mode group box set the MAX9591 soft-ware operation mode.When the Burst radio button is selected, all registers for a single bank are updated using the Load All Values To Registers or Load All Reg Values From File buttons. The individual register’s Load buttons are disabled.When the Single radio button is selected, single regis-ter values are updated using the individual register’s Load buttons. The Load All Values To Registers and Load All Reg Values From File buttons are disabled.Register Mode I 2C ActivityThe Register Mode I2C Activity group box is used for the convenience of debugging when the Single radio button is selected. When an individual register is writ-ten, the bits sent to the MAX9591 through the I 2C inter-face are displayed.Evaluates: MAX9590/MAX9591MAX9591 Evaluation Kit_______________________________________________________________________________________5E v a l u a t e s : M A X 9590/M A X 9591Advanced User InterfaceA serial interface can be used by advanced users by selecting Options | Interface (Advanced Users)from the menu bar.Click on the 2-wire interface tab shown in Figure 2.Press the Hunt for active listeners button to obtain the current MAX9591 slave address in the Target Device Address combo box. I n the General commands tab,select 1 – SMBusWriteByte(addr,cmd,data8)from the Command (SMBus Protocols, Raw Block Read/Write,EEPROM Read/Write)drop-down list. Enter the desired values into the Command byte and Data Out combo boxes and then press the Execute button.Detailed Description of HardwareThe MAX9591 evaluation kit (EV kit) demonstrates the MAX9591 reference-voltage generator in a 38-pin TQFN surface-mount package with an exposed pad.EV kit applications include gamma correction in TFT-LCD panels, such as those found in high-resolution TVs, high-end monitors, or for general industrial refer-ence-voltage generation. The MAX9591 EV kit provides 14 programmable reference-voltage outputs (DAC out-puts) and four static buffered reference-voltage outputs (DAC reference outputs) using four input reference volt-ages (DAC reference inputs).To monitor the MAX9591 EV kit’s 14 DAC outputs (OUT1–OUT14) and four reference outputs (OUT_REFU_H,OUT_REFU_L, OUT_REFL_H, and OUT_REFL_L), useMAX9591 Evaluation Kit 6_______________________________________________________________________________________Figure 2. Advanced I 2C Users Interface Window | 2-Wire Interface Tabheader J1 or the labeled test points. Reference outputs OUT_REFU_H, OUT_REFU_L, OUT_REFL_H, OUT_REFL_L,and DAC outputs OUT1, OUT7, OUT8, and OUT14 pro-vide 400mA of peak current. DAC outputs OUT2–OUT6and OUT9–OUT13 provide 200mA of peak current. Stay within the MAX9591 I C’s power rating. Refer to the MAX9591 IC data sheet for more information.The on-board resistor-divider network (R37–R41) gener-ates the reference inputs (REFU_H, REFU_L, REFL_H,and REFL_L). The user can also apply external refer-ence voltages to the REFU_H, REFU_L, REFL_H, and REFL_L PCB pads after removing R37–R41.The EV kit uses a 9V to 20V DC power supply, connected across the AVDD and AGND PCB pads, for powering the EV kit application circuit. The EV kit might require up to 500mA of supply current depending on output loading.Digital Supply ConfigurationThe MAX9591 EV kit provides two options to power the MAX9591 digital supply input (DVDD). DVDD can oper-ate from the 3.3V supply generated by the USB-to-I 2C interface circuit or from a user-supplied 2.7V to 5.5V DC power supply connected across the DVDD and DGND PCB pads. See Table 1 to configure DVDD using jumper JU5.Caution:Always ensure that DVDD is powered before AVDD.MAX9591 Slave Address DescriptionThe MAX9591 I 2C slave address can be set by jumper JU6. The slave address can be set to one of four dif-ferent addresses. See Table 2 for slave address configuration.Stand-Alone User-SuppliedI 2C CommunicationThe EV kit can be used in stand-alone operation to interface with a user’s I 2C system without using a PC.To use the MAX9591 EV kit with a user-supplied I 2C interface, perform the following steps:1)Viewing Figure 6, cut the SDA, SCL, STD_REG, andBANK_SEL traces immediately to the left of the cor-responding PCB pad.2)Disconnect the USB cable from the EV kit.3)Move jumper JU5 shunt to pins 2-3.4)Connect the positive terminal of a user-supplied 2.7Vto 5.5V DC power supply to the DVDD PCB pad and the negative terminal to the nearby DGND PCB pad.5)I nstall 2.2k Ω0603 surface-mount resistors at loca-tions R35 and R36 to pull up user-supplied signals SDA and SCL to DVDD if needed.6)Connect the user-supplied I 2C interface signals,general-purpose output (GPO) control signals, and signal ground return to the EV kit PCB pads, as shown in Table 3.Evaluates: MAX9590/MAX9591MAX9591 Evaluation Kit_______________________________________________________________________________________7Table 2. Slave Address Description***Disconnect the USB cable from the EV kit.E v a l u a t e s : M A X 9590/M A X 9591MAX9591 Evaluation Kit 8_______________________________________________________________________________________Figure 3a. MAX9591 EV Kit Schematic—Application Circuit (Sheet 1 of 2)Evaluates: MAX9590/MAX9591MAX9591 Evaluation Kit_______________________________________________________________________________________9Figure 3b. MAX9591 EV Kit Schematic—USB-to-I C Circuit (Sheet 2 of 2)E v a l u a t e s : M A X 9590/M A X 9591MAX9591 Evaluation Kit 10______________________________________________________________________________________Figure 4. MAX9591 EV Kit Component Placement Guide—Component SideFigure 5. MAX9591 EV Kit PCB Layout—Component Side分销商库存信息: MAXIMMAX9591EVKIT+。

General Description The MAX3483, MAX3485, MAX3486, MAX3488,MAX3490, and MAX3491 are 3.3V , low-power transceivers forRS-485 and RS-422 communication. Each part containsone driver and one receiver. The MAX3483 and MAX3488feature slew-rate-limited drivers that minimize EMI andreduce reflections caused by improperly terminatedcables, allowing error-free data transmission at data ratesup to 250kbps. The partially slew-rate-limited MAX3486transmits up to 2.5Mbps. The MAX3485, MAX3490, andMAX3491 transmit at up to 10Mbps.Drivers are short-circuit current-limited and are protectedagainst excessive power dissipation by thermal shutdowncircuitry that places the driver outputs into a high-imped-ance state. The receiver input has a fail-safe feature thatguarantees a logic-high output if both inputs are opencircuit.The MAX3488, MAX3490, and MAX3491 feature full-duplex communication, while the MAX3483, MAX3485, andMAX3486 are designed for half-duplex communication.Applications ●Low-Power RS-485/RS-422 Transceivers ●Telecommunications ●Transceivers for EMI-Sensitive Applications ●Industrial-Control Local Area NetworksFeatures●Operate from a Single 3.3V Supply—No Charge Pump!●Interoperable with +5V Logic ●8ns Max Skew (MAX3485/MAX3490/MAX3491)●Slew-Rate Limited for Errorless Data Transmission (MAX3483/MAX3488)●2nA Low-Current Shutdown Mode (MAX3483/MAX3485/MAX3486/MAX3491)●-7V to +12V Common-Mode Input Voltage Range ●Allows up to 32 Transceivers on the Bus ●Full-Duplex and Half-Duplex Versions Available ●Industry Standard 75176 Pinout (MAX3483/MAX3485/MAX3486)●Current-Limiting and Thermal Shutdown for Driver Overload Protection 19-0333; Rev 1; 5/19Ordering Information continued at end of data sheet.*Contact factory for for dice specifications.PARTTEMP . RANGE PIN-PACKAGE MAX3483CPA0°C to +70°C 8 Plastic DIP MAX3483CSA0°C to +70°C 8 SO MAX3483C/D0°C to +70°C Dice*MAX3483EPA-40°C to +85°C 8 Plastic DIP MAX3483ESA-40°C to +85°C 8 SO MAX3485CPA0°C to +70°C 8 Plastic DIP MAX3485CSA0°C to +70°C 8 SO MAX3485C/D0°C to +70°C Dice*MAX3485EPA-40°C to +85°C 8 Plastic DIP MAX3485ESA -40°C to +85°C 8 SO PARTNUMBERGUARANTEED DATA RATE (Mbps)SUPPLY VOLTAGE (V)HALF/FULL DUPLEX SLEW-RATE LIMITED DRIVER/RECEIVER ENABLE SHUTDOWN CURRENT (nA)PIN COUNT MAX34830.25 3.0 to 3.6Half Yes Yes 28MAX348510Half No No 28MAX34862.5Half Yes Yes 28MAX34880.25Half Yes Yes —8MAX349010Half No No —8MAX349110Half No Yes 214MAX3483/MAX3485/MAX3486/MAX3488/MAX3490/MAX3491Selection TableOrdering Information找电子元器件上宇航军工Figure 1. MAX3483/MAX3485/MAX3486 Pin Configuration and Typical Operating Circuit Figure 2. MAX3488/MAX3490 Pin Configuration and Typical Operating Circuit Figure 3. MAX3491 Pin Configuration and Typical Operating CircuitMAX3486/MAX3488/MAX3490/MAX3491True RS-485/RS-422 TransceiversFigure 22. MAX3488/MAX3490/MAX3491 Full-Duplex RS-485 NetworkFigure 23. Line Repeater for MAX3488/MAX3490/MAX3491MAX3486/MAX3488/MAX3490/MAX3491True RS-485/RS-422 Transceivers。

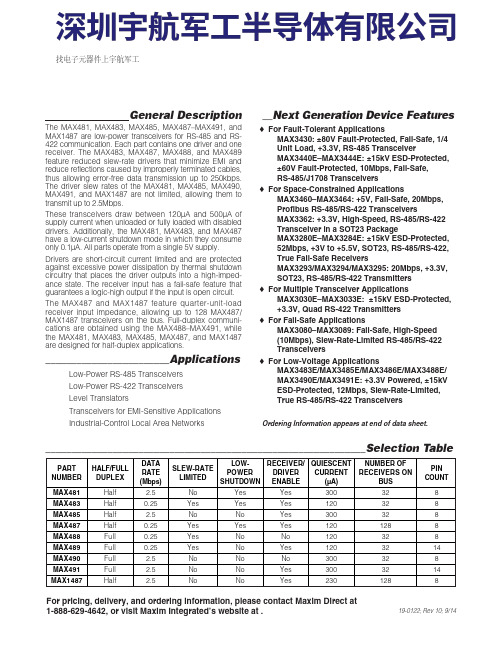

General DescriptionThe MAX481, MAX483, MAX485, MAX487–MAX491, andMAX1487 are low-power transceivers for RS-485 and RS-422 communication. Each part contains one driver and onereceiver. The MAX483, MAX487, MAX488, and MAX489feature reduced slew-rate drivers that minimize E MI andreduce reflections caused by improperly terminated cables,thus allowing error-free data transmission up to 250kbps.The driver slew rates of the MAX481, MAX485, MAX490,MAX491, and MAX1487 are not limited, allowing them totransmit up to 2.5Mbps.These transceivers draw between 120µA and 500µA ofsupply current when unloaded or fully loaded with disableddrivers. Additionally, the MAX481, MAX483, and MAX487have a low-current shutdown mode in which they consumeonly 0.1µA. All parts operate from a single 5V supply.Drivers are short-circuit current limited and are protectedagainst excessive power dissipation by thermal shutdowncircuitry that places the driver outputs into a high-imped-ance state. The receiver input has a fail-safe feature thatguarantees a logic-high output if the input is open circuit.The MAX487 and MAX1487 feature quarter-unit-loadreceiver input impedance, allowing up to 128 MAX487/MAX1487 transceivers on the bus. Full-duplex communi-cations are obtained using the MAX488–MAX491, whilethe MAX481, MAX483, MAX485, MAX487, and MAX1487are designed for half-duplex applications.________________________Applications Low-Power RS-485 Transceivers Low-Power RS-422 Transceivers Level Translators Transceivers for EMI-Sensitive Applications Industrial-Control Local Area Networks__Next Generation Device Features o For Fault-Tolerant Applications MAX3430: ±80V Fault-Protected, Fail-Safe, 1/4Unit Load, +3.3V, RS-485 Transceiver MAX3440E–MAX3444E: ±15kV ESD-Protected,±60V Fault-Protected, 10Mbps, Fail-Safe, RS-485/J1708 Transceivers o For Space-Constrained Applications MAX3460–MAX3464: +5V, Fail-Safe, 20Mbps,Profibus RS-485/RS-422 Transceivers MAX3362: +3.3V, High-Speed, RS-485/RS-422Transceiver in a SOT23 Package MAX3280E–MAX3284E: ±15kV ESD-Protected,52Mbps, +3V to +5.5V, SOT23, RS-485/RS-422,True Fail-Safe Receivers MAX3293/MAX3294/MAX3295: 20Mbps, +3.3V,SOT23, RS-485/RS-422 Transmitters o For Multiple Transceiver Applications MAX3030E–MAX3033E: ±15kV ESD-Protected,+3.3V, Quad RS-422 Transmitters o For Fail-Safe Applications MAX3080–MAX3089: Fail-Safe, High-Speed (10Mbps), Slew-Rate-Limited RS-485/RS-422Transceiverso For Low-Voltage ApplicationsMAX3483E/MAX3485E/MAX3486E/MAX3488E/MAX3490E/MAX3491E: +3.3V Powered, ±15kVESD-Protected, 12Mbps, Slew-Rate-Limited,True RS-485/RS-422 Transceivers For pricing, delivery, and ordering information, please contact Maxim Direct at1-888-629-4642, or visit Maxim Integrated’s website at .______________________________________________________________Selection Table19-0122; Rev 10; 9/14PARTNUMBERHALF/FULL DUPLEX DATA RATE (Mbps) SLEW-RATE LIMITED LOW-POWER SHUTDOWN RECEIVER/DRIVER ENABLE QUIESCENT CURRENT (μA) NUMBER OF RECEIVERS ON BUS PIN COUNT MAX481Half 2.5No Yes Yes 300328MAX483Half 0.25Yes Yes Yes 120328MAX485Half 2.5No No Yes 300328MAX487Half 0.25Yes Yes Yes 1201288MAX488Full 0.25Yes No No 120328MAX489Full 0.25Yes No Yes 1203214MAX490Full 2.5No No No 300328MAX491Full 2.5No No Yes 3003214MAX1487 Half 2.5No No Yes 2301288Ordering Information appears at end of data sheet.找电子元器件上宇航军工MAX481/MAX483/MAX485/MAX487–MAX491/MAX1487Low-Power, Slew-Rate-LimitedRS-485/RS-422 TransceiversPackage Information For the latest package outline information and land patterns, go to . Note that a “+”, “#”, or “-”in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.16Low-Power, Slew-Rate-Limited RS-485/RS-422 TransceiversMAX481/MAX483/MAX485/MAX487–MAX491/MAX1487Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.Maxim Integrated 160 Rio Robles, San Jose, CA 95134 USA 1-408-601-100017©2014 Maxim Integrated Products, Inc.Maxim Integrated and the Maxim Integrated logo are trademarks of Maxim Integrated Products, Inc.。

AO4459中⽂资料SymbolTyp Max 33406275R θJL 1824Maximum Junction-to-Lead CSteady-State°C/WThermal Characteristics ParameterUnits Maximum Junction-to-AmbientAt ≤ 10s R θJA °C/W Maximum Junction-to-Ambient ASteady-State °C/W AO4459AO4459SymbolMin TypMaxUnits BV DSS -30V -1T J =55°C-5I GSS ±100nA V GS(th)-1.5-1.85-2.5V I D(ON)-30A 3846T J =125°C53685872m ?g FS 11S V SD -0.78-1V I S-3.5A C iss 668830pF C oss 126pF C rss 92pF R g69?Q g (10V)12.716nC Q g (4.5V) 6.4nC Q gs 2nC Q gd 4nC t D(on)7.7ns t r 6.8ns t D(off)20ns t f 10ns t rr 2230ns Q rr15nCTHIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN,FUNCTIONS AND RELIABILITY WITHOUT NOTICE.DYNAMIC PARAMETERS Maximum Body-Diode Continuous CurrentGate resistanceV GS =0V, V DS =0V, f=1MHzV GS =0V, V DS =-15V, f=1MHz Input Capacitance Output Capacitance Turn-On Rise Time Turn-Off DelayTime V GS =-10V, V DS =-15V, R L =2.5?, R GEN =3?Turn-Off Fall TimeTurn-On DelayTime SWITCHING PARAMETERSTotal Gate Charge (4.5V)Gate Source Charge Gate Drain Charge Total Gate Charge (10V)V GS =-10V, V DS =-15V, I D =-6.5Am ?V GS =-4.5V, I D =-5AI S =-1A,V GS =0V V DS =-5V, I D =-6.5AR DS(ON)Static Drain-Source On-ResistanceForward TransconductanceDiode Forward VoltageI DSS µA Gate Threshold Voltage V DS =V GS I D =-250µA V DS =-24V, V GS =0VV DS =0V, V GS =±20V Zero Gate Voltage Drain Current Gate-Body leakage current Electrical Characteristics (T J =25°C unless otherwise noted)STATIC PARAMETERS ParameterConditions Body Diode Reverse Recovery Time Body Diode Reverse Recovery ChargeI F =-6.5A, dI/dt=100A/µsDrain-Source Breakdown Voltage On state drain currentI D =-250µA, V GS =0V V GS =-10V, V DS =-5V V GS =-10V, I D =-6.5AReverse Transfer Capacitance I F =-6.5A, dI/dt=100A/µs A: The value of R θJA is measured with the device mounted on 1in 2FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The value in any a given application depends on the user's specific board design. The current rating is based on the t ≤ 10s thermal resistance rating.B: Repetitive rating, pulse width limited by junction temperature.C. The R θJA is the sum of the thermal impedence from junction to lead R θJL and lead to ambient.D. The static characteristics in Figures 1 to 6 are obtained using < 300µs pulses, duty cycle 0.5% max.E. These tests are performed with the device mounted on 1 in 2FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The SOA curve provides a single pulse rating. Rev0 Sept 2006AO4459AO4459。

General DescriptionThe MAX19515 dual-channel, analog-to-digital convert-er (ADC) provides 10-bit resolution and a maximum sample rate of 65Msps.The MAX19515 analog input accepts a wide 0.4V to 1.4V input common-mode voltage range, allowing DC-coupled inputs for a wide range of RF , IF , and base-band front-end components. The MAX19515 provides excellent dynamic performance from baseband to high input frequencies beyond 400MHz, making the device ideal for zero-intermediate frequency (ZIF ) and high-intermediate frequency (IF) sampling applications. The typical signal-to-noise ratio (SNR) performance is 60.1dBF S and typical spurious-free dynamic range (SFDR) is 82dBc at f IN = 70MHz and f CLK = 65MHz.The MAX19515 operates from a 1.8V supply.Additionally, an integrated, self-sensing voltage regula-tor allows operation from a 2.5V to 3.3V supply (AVDD).The digital output drivers operate on an independent supply voltage (OVDD) over the 1.8V to 3.5V range.The analog power consumption is only 43mW per chan-nel at V AVDD = 1.8V. In addition to low operating power, the MAX19515 consumes only 1mW in power-down mode and 15mW in standby mode.Various adjustments and feature selections are avail-able through programmable registers that are accessed through the 3-wire serial-port interface.Alternatively, the serial-port interface can be disabled,with the three pins available to select output mode,data format, and clock-divider mode. Data outputs are available through a dual parallel CMOS-compatible out-put data bus that can also be configured as a single multiplexed parallel CMOS bus.The MAX19515 is available in a small 7mm x 7mm 48-pin thin QFN package and is specified over the -40°C to +85°C extended temperature range.Refer to the MAX19505, MAX19506, and MAX19507data sheets for pin- and feature-compatible 8-bit,65Msps, 100Msps, and 130Msps versions, respectively.Refer to the MAX19516 and MAX19517 data sheets for pin- and feature-compatible 10-bit, 100Msps and 130Msps versions, respectively.ApplicationsIF and Baseband Communications, Including Cellular Base Stations and Point-to-Point Microwave ReceiversUltrasound and Medical ImagingPortable Instrumentation and Low-Power Data AcquisitionDigital Set-Top BoxesFeatureso Very-Low-Power Operation (43mW/Channel at 65Msps)o 1.8V or 2.5V to 3.3V Analog Supply o Excellent Dynamic Performance60.1dBFS SNR at 70MHz 82dBc SFDR at 70MHzo User-Programmable Adjustments and Feature Selection through an SPI™Interface o Selectable Data Bus (Dual CMOS or Single Multiplexed CMOS)o DCLK Output and Programmable Data Output Timing Simplifies High-Speed Digital Interface o Very Wide Input Common-Mode Voltage Range (0.4V to 1.4V)o Very High Analog Input Bandwidth (> 850MHz)o Single-Ended or Differential Analog Inputs o Single-Ended or Differential Clock Input o Divide-by-One (DIV1), Divide-by-Two (DIV2), and Divide-by-Four (DIV4) Clock Modes o Two’s Complement, Gray Code, and Offset Binary Output Data Format o Out-of-Range Indicator (DOR)o CMOS Output Internal Termination Options (Programmable)o Reversible Bit Order (Programmable)o Data Output Test Patternso Small 7mm x 7mm 48-Pin Thin QFN Package with Exposed PadMAX19515Dual-Channel, 10-Bit, 65Msps ADC________________________________________________________________Maxim Integrated Products1Ordering Information19-4195; Rev 1; 10/08For pricing, delivery, and ordering information,please contact Maxim Direct at 1-888-629-4642,or visit Maxim’s website at .*EP = Exposed pad.Pin Configuration appears at end of data sheet.SPI is a trademark of Motorola, Inc.M A X 19515Dual-Channel, 10-Bit, 65Msps ADC 2_______________________________________________________________________________________ABSOLUTE MAXIMUM RATINGSELECTRICAL CHARACTERISTICS(V AVDD = V OVDD = 1.8V, internal reference, differential clock, V CLK = 1.5V P-P , f CLK = 65MHz, A IN = -0.5dBFS, data output terminationStresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.OVDD, AVDD to GND............................................-0.3V to +3.6V CMA, CMB, REFIO, INA+, INA-, INB+,INB- to GND ......................................................-0.3V to +2.1V CLK+, CLK-, SYNC, SPEN , CS , SCLK, SDINto GND..........-0.3V to the lower of (V AVDD + 0.3V) and +3.6V DCLKA, DCLKB, D9A–D0A, D9B–D0B, DORA, DORBto GND..........-0.3V to the lower of (V OVDD + 0.3V) and +3.6VContinuous Power Dissipation (T A = +70°C)48-Pin Thin QFN, 7mm x 7mm x 0.8mm (derate 40mW/°C above +70°C).............................................................3200mW Operating Temperature Range ...........................-40°C to +85°C Junction Temperature......................................................+150°C Storage Temperature Range.............................-65°C to +150°C Lead Temperature (soldering, 10s).................................+300°CMAX19515Dual-Channel, 10-Bit, 65Msps ADC_______________________________________________________________________________________3ELECTRICAL CHARACTERISTICS (continued)(V AVDD = V OVDD = 1.8V, internal reference, differential clock, V CLK = 1.5V P-P , f CLK = 65MHz, A IN = -0.5dBFS, data output terminationM A X 19515Dual-Channel, 10-Bit, 65Msps ADC 4_______________________________________________________________________________________ELECTRICAL CHARACTERISTICS (continued)(V AVDD = V OVDD = 1.8V, internal reference, differential clock, V CLK = 1.5V P-P , f CLK = 65MHz, A IN = -0.5dBFS, data output terminationMAX19515Dual-Channel, 10-Bit, 65Msps ADC_______________________________________________________________________________________5ELECTRICAL CHARACTERISTICS (continued)(V AVDD = V OVDD = 1.8V, internal reference, differential clock, V CLK = 1.5V P-P , f CLK = 65MHz, A IN = -0.5dBFS, data output terminationM A X 19515Dual-Channel, 10-Bit, 65Msps ADC 6_______________________________________________________________________________________ELECTRICAL CHARACTERISTICS (continued)(V AVDD = V OVDD = 1.8V, internal reference, differential clock, V CLK = 1.5V P-P , f CLK = 65MHz, A IN = -0.5dBFS, data output terminationMAX19515Dual-Channel, 10-Bit, 65Msps ADC_______________________________________________________________________________________7ELECTRICAL CHARACTERISTICS (continued)(V AVDD = V OVDD = 1.8V, internal reference, differential clock, V CLK = 1.5V P-P , f CLK = 65MHz, A IN = -0.5dBFS, data output termination175MHz TWO-TONE IMDFREQUENCY (MHz)A M P L I T U D E (dB F S )-120-100-80-60-40-200f IN1 = 172.49286MHz f IN2 = 177.50202MHz70MHz TWO-TONE IMD PLOTFREQUENCY (MHz)A M P L I T U D E (dB F S )-120-100-80-60-40-200f IN1 = 71.496925MHz f IN2 = 68.504600MHz175MHz INPUT FFT PLOTFREQUENCY (MHz)A M P L I T U D E (dB F S )-120-100-80-60-40-200f IN = 175.096626MHz A IN = -0.512dBFS SNR = 59.073dB SINAD = 59.022dB THD = -78.338dBc SFDR1 = 81.806dBc SFDR2 = 84.255dBc70MHz INPUT FFT PLOTFREQUENCY (MHz)A M P L I T U D E (dB F S )-120-100-80-60-40-200f IN = 70.1014328MHz A IN = -0.532dBFS SNR = 59.432dB SINAD = 58.388dB THD = -79.349dBc SFDR1 = 84.227dBc SFDR2 = 81.877dBc3MHz SINGLE-ENDED INPUT FFT PLOTFREQUENCY (MHz)A M P L I T U D E (dB F S )-120-100-80-60-40-200f IN = 2.99877166748047MHz A IN = -0.546dBFS SNR = 59.675dB SINAD = 59.632dB THD = -79.673dBc SFDR1 = 88.737dBc SFDR2 = 82.290dBcM A X 19515Dual-Channel, 10-Bit, 65Msps ADC 8_______________________________________________________________________________________Typical Operating Characteristics(V AVDD = V OVDD = 1.8V, internal reference, differential clock, V CLK = 1.5V P-P , f CLK = 65MHz, A IN = -0.5dBFS, data output termination = 50Ω, T A = +25°C, unless otherwise noted.)3MHz INPUT FFT PLOTFREQUENCY (MHz)A M P L I T U D E (dB F S )-120-100-80-60-40-200f IN = 2.99877166MHz A IN = -0.532dBFS SNR = 59.682dB SINAD = 59.641dB THD = -79.826dBc SFDR1 = 83.946dBc SFDR2 = 82.852dBcINTEGRAL NONLINEARITY vs. DIGITAL OUTPUT CODEDIGITAL OUTPUT CODEI N L (L S B )2565127681024-1.0-0.8-0.6-0.4-0.200.20.40.60.81.0DIFFERENTIAL NONLINEARITY vs. DIGITAL OUTPUT CODEDIGITAL OUTPUT CODED N L (L S B )2565127681024-1.0-0.8-0.6-0.4-0.200.20.40.60.81.0PERFORMANCE vs. INPUT FREQUENCYINPUT FREQUENCY (MHz)P E R F O R M A N C E (d BF S )5010015020025030035040050556065707580859095ANALOG SUPPLY CURRENT vs. SUPPLY VOLTAGESUPPLY VOLTAGE (V)A N A L O G S U P P L Y C U R R E N T (m A )M A X 19515 o c 181.65 1.701.75 1.80 1.85 1.90 1.954041424344454647484950PERFORMANCEvs. ANALOG INPUT AMPLITUDEANALOG INPUT AMPLITUDE (dBFS)P E R F O R M A N C E (d B F S )-80-70-60-50-40-30-20-1005060708090100110SINGLE-ENDED PERFORMANCEvs. INPUT FREQUENCYINPUT FREQUENCY (MHz)S I N G L E -E N D E D P E R F O R M A N C E (d B F S )1020304050607050556065707580859095Typical Operating Characteristics (continued)(V AVDD = V OVDD = 1.8V, internal reference, differential clock, V CLK = 1.5V P-P , f CLK = 65MHz, A IN = -0.5dBFS, data output termination = 50Ω, T A = +25°C, unless otherwise noted.)MAX19515Dual-Channel, 10-Bit, 65Msps ADC_______________________________________________________________________________________9PERFORMANCEvs. SAMPLING FREQUENCYSAMPLING FREQUENCY (Msps)P E R F O R M A N C E (d B F S )202530354045505560657050556065707580859095PERFORMANCEvs. COMMON-MODE VOLTAGECOMMON-MODE VOLTAGE (V)P E R F O R M A N C E (d B F S)0.350.550.750.95 1.15 1.3550556065707580859095PERFORMANCEvs. ANALOG SUPPLY VOLTAGEANALOG SUPPLY VOLTAGE (V)P E R F O R M A N C E (d B F S)1.651.70 1.75 1.80 1.85 1.90 1.95505560657075808590PERFORMANCEvs. ANALOG SUPPLY VOLTAGEANALOG SUPPLY VOLTAGE (V)P E R F O R M A N C E (d B F S)2.32.5 2.7 2.93.1 3.3 3.5505560657075808590ANALOG SUPPLY CURRENT vs. SAMPLING FREQUENCYSAMPLING FREQUENCY (MHz)A N A L O G S U P P L Y C U R R E N T (m A )M A X 19515 t o c 1620253035404550556065703032343638404244464850ANALOG SUPPLY CURRENTvs. TEMPERATURETEMPERATURE (°C)A N A L O G S U P P L Y C U R R E N T (m A )M A X 19515 t o c 17-40-20020********4142434445464748495010______________________________________________________________________________________Typical Operating Characteristics (continued)(V AVDD = V OVDD = 1.8V, internal reference, differential clock, V CLK = 1.5V P-P , f CLK = 65MHz, A IN = -0.5dBFS, data output termination = 50Ω, T A = +25°C, unless otherwise noted.)ANALOG SUPPLY CURRENT vs. SUPPLY VOLTAGESUPPLY VOLTAGE (V)A N A L O G S U P P L Y C U R R E N T (m A )M A X 19515 t o c 192.32.52.7 2.93.1 3.33.54041424344454647484950M A X 19515Dual-Channel, 10-Bit, 65Msps ADC DIGITAL SUPPLY CURRENT vs. SAMPLING FREQUENCYSAMPLING FREQUENCY (Msps)D I G I T A L S U P P L Y C U R RE N T (mA )202530354045505560657024681012DIGITAL SUPPLY CURRENT vs. SAMPLING FREQUENCYSAMPLING FREQUENCY (Msps)D I G I T A L S U P P L Y C U R RE N T (m A )2025303540455055606570510152025DIGITAL SUPPLY CURRENT vs. TEMPERATURETEMPERATURE (°C)S U P P L Y C U R R E N T (m A )-40-200204060805791113151719212325DIGITAL SUPPLY CURRENT vs. SUPPLY VOLTAGESUPPLY VOLTAGE (V)D I G I T A L S U P P L Y C U R RE N T(m A )1.7 1.92.1 2.3 2.5 2.7 2.93.1 3.3 3.5510152025DIGITAL SUPPLY CURRENT vs. SUPPLY VOLTAGESUPPLY VOLTAGE (V)D I G I T A L S U P P L Y C U R RE N T (m A )1.7 1.92.1 2.3 2.5 2.7 2.93.1 3.3 3.551015202530PERFORMANCE vs. CLOCK DUTY CYCLECLOCK DUTY CYCLE (%)P E R F O R M A N C E (d B F S )30354045505560655560657075808590PERFORMANCE vs. TEMPERATURETEMPERATURE (°C)P E R F O R M A N C E (d B F S )-40-2002040608050556065707580859095GAIN ERROR vs. TEMPERATURETEMPERATURE (°C)G A I N E R R O R (%)M A X 19515 t o c 27-40-20020406080-0.05-0.04-0.03-0.02-0.0100.010.020.030.040.05Typical Operating Characteristics (continued)(V AVDD = V OVDD = 1.8V, internal reference, differential clock, V CLK = 1.5V P-P , f CLK = 65MHz, A IN = -0.5dBFS, data output termination = 50Ω, T A = +25°C, unless otherwise noted.)COMMON-MODE REFERENCE VOLTAGEvs. TEMPERATURETEMPERATURE (°C)C O M M O N -M ODE R EF E R E N C E V O L T AG E (V )-40-2002040608000.20.40.60.81.01.21.41.6OFFSET ERROR vs. TEMPERATURETEMPERATURE (°C)O F F S E T E R R O R (m V )M A X 19515 t o c 28-40-20020406080-0.7-0.6-0.5-0.4-0.3-0.2-0.100.10.2MAX19515Dual-Channel, 10-Bit, 65Msps ADCREFERENCE VOLTAGE vs. TEMPERATURETEMPERATURE (°C)R E F E R E N C E V O L T A G E (V )M A X 19515 t o c 29-40-200204060801.24321.24531.24741.24951.2516GAIN ERROR vs. SUPPLY VOLTAGESUPPLY VOLTAGE (V)G A I N E R R O R (%)1.6 1.82.0 2.2 2.4 2.6 2.83.0 3.2 3.4 3.6-0.08-0.06-0.04-0.0200.020.040.060.08INPUT CURRENTvs. COMMON-MODE VOLTAGECOMMON-MODE VOLTAGE (V)I N P U T C U R R E N T (µA )M A X 19515 t o c 320.40.50.60.70.80.9 1.0 1.1 1.2 1.3 1.4202530354045505560M A X 19515Dual-Channel, 10-Bit, 65Msps ADCMAX19515Dual-Channel, 10-Bit, 65Msps ADCDetailed DescriptionThe MAX19515 uses a 10-stage, fully differential,pipelined architecture (F igure 1) that allows for high-speed conversion while minimizing power consump-tion. Samples taken at the inputs move progressivelythrough the pipeline stages every half clock cycle.From input to output the total latency is 9 clock cycles.Each pipeline converter stage converts its input voltageto a digital output code. At every stage, except the last,the error between the input voltage and the digital out-put code is multiplied and passed on to the nextpipeline stage. Digital error correction compensates forADC comparator offsets in each pipeline stage andensures no missing codes. F igure 2 shows theMAX19515 functional diagram.Analog Inputs and Common-ModeReference Apply the analog input signal to the analog inputs (INA+/INA- or INB+/INB-), which are connected to the input sampling switch (F igure 3). When the input sam-pling switch is closed, the input signal is applied to the sampling capacitors through the input switch resistance. The input signal is sampled at the instant the input switch opens. The pipeline ADC processes the sampled voltage and the digital output result is available 9 clock cycles later. Before the input switch is closed to begin the next sampling cycle, the sampling capacitors are reset to the input common-mode potential.Common-mode bias can be provided externally or internally through 2kΩresistors. In DC-coupled applica-tions, the signal source provides the external bias and the bias current. In AC-coupled applications, the input current is supplied by the common-mode input voltage. For example, the input current can be supplied through the center tap of a transformer secondary winding. Alternatively, program the appropriate internal register through the serial-port interface to supply the input DC current through internal 2kΩresistors (Figure 3). When the input current is supplied through the internal resis-tors, the input common-mode potential is reduced by the voltage drop across the resistors. The common-mode input reference voltage can be adjusted through programmable register settings from 0.45V to 1.35V in 0.15V increments. The default setting is 0.90V. Use this feature to provide a common-mode output reference to a DC-coupled driving circuit.Figure 1. Pipeline Architecture—Stage BlocksM A X 19515Dual-Channel, 10-Bit, 65Msps ADCFigure 2. Functional DiagramFigure 3. Internal Track-and-Hold (T/H) CircuitMAX19515 Dual-Channel, 10-Bit, 65Msps ADCReference Input/Output (REFIO) REF IO adjusts the reference potential, which, in turn, adjusts the full-scale range of the ADC. Figure 4 shows a simplified schematic of the reference system. An internal bandgap voltage generator provides an internal reference voltage. The bandgap potential is buffered and applied to REFIO through a 10kΩresistor. Bypass REF IO with a 0.1µF capacitor to AGND. The bandgap voltage is applied to a scaling and level-shift circuit, which creates internal reference potentials that estab-lish the full-scale range of the ADC. Apply an external voltage on REFIO to trim the ADC full scale. The allow-able adjustment range is +5/-15%. The REF IO-to-ADC gain transfer function is:V FS= 1.5 x [V REFIO/1.25] VoltsProgramming and Interface There are two ways to control the MAX19515 operating modes. Full feature selection is available using the SPI interface, while the parallel interface offers a limited set of commonly used features. The programming mode is selected using the SPEN input. Drive SPEN low for SPI interface; drive SPEN high for parallel interface.Parallel Interface The parallel interface offers a pin-programmable inter-face with a limited feature set. Connect SPEN to AVDD to enable the parallel interface. See Table 1 for pin functionality; see Figure 5 for a simplified parallel-inter-face input schematic.Figure 4. Simplified Reference SchematicFigure 5. Simplified Parallel-Interface Input SchematicM A X 19515Dual-Channel, 10-Bit, 65Msps ADC Serial Programming InterfaceA serial interface programs the MAX19515 control reg-isters through the CS , SDIN, and SCLK inputs. Serial data is shifted into SDIN on the rising edge of SCLK when CS is low. The MAX19515 ignores the data pre-sented at SDIN and SCLK when CS is high. C S must transition high after each read/write operation . SDIN also serves as the serial-data output for reading control registers. The serial interface supports two-byte transfer in a communication cycle. The first byte is a control byte, containing the address and read/write instruction,written to the MAX19515. The second byte is a data byte and can be written to or read from the MAX19515.Figure 6 shows a serial-interface communication cycle.The first SDIN bit clocked in establishes the communi-cation cycle as either a write or read transaction (0 for write operation and 1 for read operation). The following 7 bits specify the address of the register to be written or read. The final 8 SDIN bits are the register data. All address and data bits are clocked in or out MSB first.During a read operation, the MAX19515 serial port dri-ves read data (D7) into SDIN after the falling edge of SCLK following the 8th rising edge of SCLK. Since the minimum hold time on SDIN input is zero, the master can stop driving SDIN any time after the 8th rising edge of SCLK. Subsequent data bits are driven into SDIN on the falling edge of SCLK. Output data in a read opera-tion is latched on the rising edge of SCLK. F igure 7shows the detailed serial-interface timing diagram.Figure 6. Serial-Interface Communication CycleFigure 7. Serial-Interface Timing DiagramMAX19515Dual-Channel, 10-Bit, 65Msps ADCRegister address 0Ah is a special-function register.Writing data 5Ah to register 0Ah initiates a register reset. When this operation is executed, all control regis-ters are reset to default values. A read operation of reg-ister 0Ah returns a status byte with information described in Table 2.The SHDN input (pin 7) toggles between any twopower-management states. The Power Management register defines each power-management state. In thedefault state, SHDN = 1 shuts down the MAX19515 and SHDN = 0 returns to full power.M A X 19515Dual-Channel, 10-Bit, 65Msps ADCIn addition to power management, the HPS_SHDN1and HPS_SHDN0 activate an A+B adder mode. In this mode, the results from both channels are averaged.The MUX_CH bit selects which bus the (A+B)/2 data is presented.**HPS_SHDN1, STBY_SHDN1, CHA_ON_SHDN1, and CHB_ON_SHDN1 are active when SHDN = 1.X = Don’t care.Note:When HPS_SHDN_ = 1 (A+B adder mode), CHA_ON and CHB_ON must BOTH equal 0 for power-down or standby.Bit 4BIT_ORDER_B: Reverse CHB output bit order 0 = Defined data bus pin order (default)1 = Reverse data bus pin orderBit 3BIT_ORDER_A: Reverse CHA output bit order 0 = Defined data bus pin order (default)1 = Reverse data bus pin orderBit 2MUX_CH: Multiplexed data bus selection0 = Multiplexed data output on CHA (CHA data presented first, followed by CHB data) (default)1 = Multiplexed data output on CHB (CHB data presented first, followed by CHA data)Bit 1MUX: Digital output mode0 = Dual data bus output mode (default)1 = Single multiplexed data bus output modeMUX_CH selects the output bus Bit 0Set to 0 for proper operationDual-Channel, 10-Bit, 65Msps ADCMAX19515Bit 3, 2PD_DOUT_1, PD_DOUT_0: Power-down digital output state control00 = Digital output three state (default)01 = Digital output low10 = Digital output three state11 = Digital output highBit 1DIS_DOR: DOR driver disable0 = DOR active (default)1 = DOR disabled (three state)Bit 0DIS_DCLK: DCLK driver disable0 = DCLK active (default)1 = DCLK disabled (three state)M A X 19515Dual-Channel, 10-Bit, 65Msps ADC0 = Nominal1 = Bypasses data aligner delay line to minimize output data latency with respect to the input clock.Rising clock to data transition is approximately 6ns with DTIME = 000b settings (default)Bit 6DLY_HALF_T: Data and DCLK delayed by T/20 = Normal, no delay (default)1 = Delays data and DCLK outputs by T/2Disabled in MUX data bus modeBit 5, 4, 3DCLKTIME_2, DCLKTIME_1, DCLKTIME_0: DCLK timing adjust (controls both channels)000 = Nominal (default)001 = +T/16010 = +2T/16011 = +3T/16100 = Reserved, do not use 101 = -1T/16110 = -2T/16111 = -3T/16Bit 2, 1, 0DTIME_2, DTIME_1, DTIME_0: Data timing adjust (controls both channels)000 = Nominal (default)001 = +T/16010 = +2T/16011 = +3T/16100 = Reserved, do not use 101 = -1T/16110 = -2T/16111 = -3T/16MAX19515Dual-Channel, 10-Bit, 65Msps ADCBit 5, 4, 3CT_DCLK_2_A, CT_DCLK_1_A, CT_DCLK_0_A: CHA DCLK termination control 000 = 50Ω(default)001 = 75Ω010 = 100Ω011 = 150Ω1xx = 300ΩBit 2, 1, 0CT_DATA_2_A, CT_DATA_1_A, CT_DATA_0_A: CHA data output termination control 000 = 50Ω(default)001 = 75Ω010 = 100Ω011 = 150Ω1xx = 300ΩCHB Data Output Termination Control (05h)Bit 5, 4, 3CT_DCLK_2_B, CT_DCLK_1_B, CT_DCLK_0_B: CHB DCLK termination control 000 = 50Ω(default)001 = 75Ω010 = 100Ω011 = 150Ω1xx = 300ΩBit 2, 1, 0CT_DATA_2_B, CT_DATA_1_B, CT_DATA_0_B: CHB data output termination control 000 = 50Ω(default)001 = 75Ω010 = 100Ω011 = 150Ω1xx = 300ΩM A X 19515Dual-Channel, 10-Bit, 65Msps ADCReserved (07h)—Do not write to this register0 = Ramps from 0 to 1023 (offset binary) and repeats (subsequent formatting applied) (default)1= Data alternates between D[9:0] = 010*******, DOR = 1, and D[9:0] = 1010101010,DOR = 0 on both channels Bit 6TEST_DATA: Data test mode 0 = Normal data output (default)1 = Outputs test data patternBit 5, 4FORMAT_1, FORMAT_0: Data numerical format 00 = Two’s complement (default)01 = Offset binary 10 = Gray code11 = Two’s complementBit 3TERM_100: Select 100Ωclock input termination 0 = No termination (default)1 = 100Ωtermination across differential clock inputs Bit 2SYNC_MODE: Divider synchronization mode select 0 = Slip mode (Figure 11) (default)1 = Edge mode (Figure 12)Bit 1, 0DIV1, DIV0: Input clock-divider select 00 = No divider (default)01 = Divide-by-210 = Divide-by-411 = No dividerMAX19515Dual-Channel, 10-Bit, 65Msps ADCSoftware Reset (0Ah)Bit 7CMI_SELF_B: CHB connect input common-mode to analog inputs 0 = Internal common-mode voltage is NOT applied to inputs (default)1 = Internal common-mode voltage applied to analog inputs through 2k ΩresistorsBit 6, 5, 4CMI_ADJ_2_B, CMI_ADJ_1_B, CMI_ADJ_0_B: CHB input common-mode voltage adjustment 000 = 0.900V (default)001 = 1.050V 010 = 1.200V 011 = 1.350V 100 = 0.900V 101 = 0.750V 110 = 0.600V 111 = 0.450VBit 3CMI_SELF_A: CHA connect input common-mode to analog inputs 0 = Internal common-mode voltage is NOT applied to inputs (default)1 = Internal common-mode voltage applied to analog inputs through 2k Ωresistors Bit 2, 1, 0CMI_ADJ_2_A, CMI_ADJ_1_A, CMI_ADJ_0_A: CHA input common-mode adjustment 000 = 0.900V (default)001 = 1.050V 010 = 1.200V 011 = 1.350V 100 = 0.900V 101 = 0.750V 110 = 0.600V 111 = 0.450VBit 7–0SWRESET: Write 5Ah to initiate software resetClock InputsThe input clock interface provides for flexibility in the requirements of the clock driver. The MAX19515accepts a fully differential clock or single-ended logic-level clock. F or differential clock operation, connect a differential clock to the CLK+ and CLK- inputs. In this mode, the input common mode is established internally to allow for AC-coupling. The differential clock signal can also be DC-coupled if the common mode is con-strained to the specified 1V to 1.4V clock input com-mon-mode range. For single-ended operation, connect CLK- to GND and drive the CLK+ input with a logic-level signal. When the CLK- input is grounded (or pulled below the threshold of the clock mode detection comparator) the differential-to-single-ended conversion stage is disabled and the logic-level inverter path is activated.Clock DividerThe MAX19515 offers a clock-divider option. Enable clock division either by setting DIV0 and DIV1 through the serial interface; see the Clock Divide/DataM A X 19515Dual-Channel, 10-Bit, 65Msps ADCFigure 8. Simplified Clock Input SchematicFigure 9. Dual-Bus Output Mode TimingMAX19515 Dual-Channel, 10-Bit, 65Msps ADCF ormat/Test Pattern register (06h) for clock-divider options, or in parallel programming configuration (SPEN = 1) by using the DIV input.System Timing Requirements F igures 9 and 10 depict the relationship between the clock input and output, analog input, sampling event, and data output. The MAX19515 samples on the rising edge of the sampling clock. Output data is valid on the next rising edge of DCLK after a nine-clock internal latency. For applications where the clock is divided, the sample clock is the divided internal clock derived from:[(CLK+ - CLK-)/DIVIDER]Synchronization When using the clock divider, the phase of the internal clock can be different than that of the FPGA, microcon-troller, or other MAX19515s in the system. There are two mechanisms to synchronize the internal clock: slip synchronization and edge synchronization. Select the synchronization mode using SYNC_MODE (bit 2) in the Clock Divide/Data F ormat/Test Pattern register (06h) and drive the SYNCIN input high to synchronize.Slip Synchronization Mode, SYNC_MODE = 0 (default):On the third rising edge of the input clock (CLK) after the rising edge of SYNC (provided set-up and hold times are met), the divided output is forced to skip a state transition (Figure 11).Edge Synchronization Mode, SYNC_MODE = 1:On the third rising edge of the input clock (CLK) after the rising edge of SYNC (provided set-up and hold times are met), the divided output is forced to state 0. A divid-ed clock rising edge occurs on the fourth(/2 mode) or fifth (/4 mode) rising edge of CLK, after a valid rising edge of SYNC (Figure 12).Figure 10. Multiplexed Output Mode Timing。

General DescriptionThe MAX4754/MAX4754A/MAX4755/MAX4756/MAX4756A low on-resistance, analog switches operate from a single +1.8V to +5.5V supply. The MAX4754/MAX4754A and MAX4755 are dual, double-pole, double-throw (DPDT)switches. The MAX4756/MAX4756A are quad, single-pole double-throw (SPDT) switches. They are configured to route either audio or data signals.The MAX4754/MAX4754A have four 0.5ΩSPDT switches for audio-signal routing and two logic control inputs. The MAX4755 has four 0.5ΩSPDT switches (with two switches that have an additional 11Ωseries resistor at the NC terminals). This allows users to drive an 8Ωspeaker as a 32Ωload (ear speaker). The MAX4756/MAX4756A have four 0.5ΩSPDT switches controlled by one logic control input and an enable input (EN ) to dis-able the switches.The MAX4754/MAX4754A/MAX4755/MAX4756/MAX4756A are available in a space-saving 16-pin TQFN and a tiny 16-bump, 2mm x 2mm chip-scale package (UCSP™).ApplicationsSpeaker-Headset Switching Audio-Signal Routing Cellular PhonesPDAs/Handheld Devices Notebook ComputersFeatures♦Data and Audio-Signal Routing♦Low R ON (0.5Ω typ) Audio Switches♦0.1Ω(typ) Channel-to-Channel Matching ♦0.2Ω(typ) On-Resistance Flatness ♦0.035% (typ) THD♦Improved Power-Supply Current for Non-Rail-to-Rail Control Logic Inputs (MAX4754A/MAX4756A)♦+1.8V to +5.5V Supply Range ♦Rail-to-Rail Signal Handling ♦16-Bump UCSP (2mm x 2mm)MAX4754/MAX4754A/MAX4755/MAX4756/MAX4756A________________________________________________________________Maxim Integrated Products 1Ordering InformationFor pricing, delivery, and ordering information,please contact Maxim/Dallas Direct!at 1-888-629-4642, or visit Maxim’s website at .Functional DiagramsUCSP is a trademark of Maxim Integrated Products, Inc.Pin Configurations appear at end of data sheet.Note:These devices operate over the -40°C to +85°C operating temperature range.*Future product—contact factory for availability.**EP = Exposed paddle.+Denotes lead-free package.M A X 4754/M A X 4754A /M A X 4755/M A X 4756/M A X 4756A0.5Ω, Quad SPDT Switches in UCSP/QFNABSOLUTE MAXIMUM RATINGSELECTRICAL CHARACTERISTICS(V+ = +2.7V to +5.25V, T = -40°C to +85°C, unless otherwise noted. Typical values are at +3V and T = +25°C.) (Notes 2, 3)Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.(All voltages referenced to GND.)V+, IN_, EN ...............................................................-0.3V to +6V COM_, NO_, NC_ (Note 1)...........................-0.3V to (V+ + 0.3V)Continuous CurrentNC1, NC2, COM1, COM2 (MAX4755)........................±100mA NO_, NC_, COM_ (remaining terminal connections)....±300mA Peak Current NC1, NC2, COM1, COM2 (MAX4755)(Pulsed at 1ms, 10% duty cycle)................................±200mA (Pulsed at 1ms, 50% duty cycle)................................±150mA Peak Current NO_, NC_,COM__ (remaining terminal connections)(Pulsed at 1ms, 10% duty cycle)............................±500mA (Pulsed at 1ms, 50% duty cycle)............................±400mAContinuous Power Dissipation (T A = +70°C)16-Bump UCSP (derate 8.2mW/°C above +70°C)......660mW 16-Pin TQFN (derate 16.9mW/°Cabove +70°C)............................................................1349mW ESD per Method 3015.7...................................................±2kV Operating Temperature Range ...........................-40°C to +85°C Junction Temperature......................................................+150°C Storage Temperature Range.............................-65°C to +150°C Bump Temperature (soldering)Infrared (15s)...............................................................+220°C Vapor Phase (60s).......................................................+215°C Lead Temperature (soldering, 10s).................................+300°CNote 1:Signals on NO_, NC_, COM_ exceeding V+ or GND are clamped by internal diodes. Limit forward-diode current to maximumcurrent rating.ELECTRICAL CHARACTERISTICS (continued)MAX4754/MAX4754A/MAX4755/MAX4756/MAX4756A0.5Ω, Quad SPDT Switches in UCSP/QFNM A X 4754/M A X 4754A /M A X 4755/M A X 4756/M A X 4756A0.5Ω, Quad SPDT Switches in UCSP/QFN 4_______________________________________________________________________________________Note 3:UCSP parts are 100% tested at +25°C and limits across the full temperature range are guaranteed by correlation anddesign. TQFN parts are 100% tested at +85°C and limits across the full temperature range are guaranteed by correlation and design.Note 4:R ON and ΔR ON matching specifications are guaranteed by design and correlation.Note 5:ΔR ON = R ON(MAX)- R ON(MIN).Note 6:Flatness is defined as the difference between the maximum and minimum value of on-resistance as measured over thespecified analog signal ranges.Note 7:Guaranteed by design, not production tested.Note 8:Off-Isolation = 20log 10[V COM / (V NO or V NC )], V COM = output, V NO or V NC = input to off switch.Note 9:Between any two switches.ELECTRICAL CHARACTERISTICS (continued)(V+ = +2.7V to +5.25V, T A = -40°C to +85°C, unless otherwise noted. Typical values are at +3V and T A = +25°C.) (Notes 2, 3)MAX4754/MAX4754A/MAX4755/MAX4756/MAX4756A0.5Ω, Quad SPDT Switches in UCSP/QFN_______________________________________________________________________________________5Typical Operating Characteristics(V+ = 3V, T A = +25°C, unless otherwise noted.)01.00.52.52.01.54.03.53.04.521345ON-RESISTANCE vs. V COM (MAX4754A/MAX4756A)V COM (V)R O N (Ω)00.30.20.10.40.50.60.70.80.91.0123ON-RESISTANCE vs. V COM AND TEMPERATUREV COM (V)R O N (_)00.30.20.10.40.50.60.70.80.91.021345ON-RESISTANCE vs. V COM AND TEMPERATUREV COM (V)R O N (_)ON-RESISTANCE vs. V COMV COM (V)R O N (Ω)4.54.03.0 3.51.0 1.5 2.0 2.50.510.511.011.512.012.513.010.05.0ON-RESISTANCEvs. V COM AND TEMPERATUREV COM (V)R O N (Ω)3.02.52.01.51.00.510.511.011.512.012.513.010.0ON-RESISTANCEvs. V COM AND TEMPERATUREV COM (V)R O N (Ω)5.04.53.52.5 4.03.02.01.51.00.510.511.011.512.012.513.010.0NO/NC OFF-LEAKAGE CURRENTvs. TEMPERATURE(MAX4754/MAX4755/MAX4756)TEMPERATURE (°C)N O /N C O F F -L E A K A G E (n A )603510-150.11100.01-4085COM ON-LEAKAGE CURRENTvs. TEMPERATURETEMPERATURE (°C)C O M O N -L E A K A G E C U R R E N T (n A )603510-150.11100.01-4085CHARGE INJECTION vs. V COM (MAX4754/MAX4755/MAX4756)V COM (V)C H A R G E I N J E C T I O N (p C )432110203040506070809010011012005M A X 4754/M A X 4754A /M A X 4755/M A X 4756/M A X 4756A0.5Ω, Quad SPDT Switches in UCSP/QFN 6_______________________________________________________________________________________Typical Operating Characteristics (continued)(V+ = 3V, T A = +25°C, unless otherwise noted.)CHARGE INJECTION vs. V COMV COM (V)C H A R G E I N J E C T I O N (p C )432150100150200250005SUPPLY CURRENT vs. SUPPLY VOLTAGEM A X 4754A -56A t o c 11SUPPLY VOLTAGE (V)S U P P L Y C U R R E N T (n A )54320.20.40.60.81.01.21.41.61.82.0016SUPPLY CURRENT vs. TEMPERATURE (MAX4754/MAX4755/MAX4756)TEMPERATURE (°C)S U P P L Y C U R R E N T (n A )603510-150.010.11101000.001-4085SUPPLY CURRENT vs. TEMPERATURE(MAX4754A/MAX4756A)TEMPERATURE (°C)S U P P L Y C U R R E N T (n A )6035-10-150.010.11101000.001-4085LOGIC THRESHOLD vs. SUPPLY VOLTAGE(MAX4754/MAX4755/MAX4756)SUPPLY VOLTAGE (V)L O G I C T H R E S H O L D (V )5.04.54.03.53.02.52.00.40.81.21.62.02.401.55.5LOGIC THRESHOLD vs. SUPPLY VOLTAGE(MAX4754A/MAX4756A)SUPPLY VOLTAGE (V)L O G I C T H R E S H O L D (V )4.53.52.50.20.40.60.81.01.21.40.01.55.5TURN-ON/OFF TIMES vs. SUPPLY VOLTAGE(MAX4754/MAX4755/MAX4756)SUPPLY VOLTAGE (V)t O N /t O F F (n s )5.04.54.03.53.02.52.01020304050607001.55.5TURN-ON/OFF TIMES vs. SUPPLY VOLTAGE(MAX4754A)SUPPLY VOLTAGE (V)t O N /t O F F (n s )1.52.53.54.55.5100200300400500600700800TURN-ON/OFF TIMES vs. TEMPERATURE(MAX4754/MAX4755/MAX4756)TEMPERATURE (°C)t O N /t O F F (n s )603510-1510203040500-4085MAX4754/MAX4754A/MAX4755/MAX4756/MAX4756A0.5Ω, Quad SPDT Switches in UCSP/QFN_______________________________________________________________________________________7Typical Operating Characteristics (continued)(V+ = 3V, T A = +25°C, unless otherwise noted.)TURN-ON/OFF TIMES vs. TEMPERATURE(MAX4754A)SUPPLY VOLTAGE (V)t O N /t O F F (n s )-40-1510356085050100150200250300350400450SUPPLY CURRENT vs. LOGIC CONTROL INPUTIN_ (V)CR O W B A R C U R R E N T (n A )01234565001000150020002500300035004000FREQUENCY REPSONSEFREQUENCY (MHz)O N -L O S S (d B )1010.0010.010.1-120-100-80-60-40-20020-1400.0001100TOTAL HARMONIC DISTORTION PLUS NOISE vs. FREQUENCYFREQUENCY (kHz)T H D + N (%)1010.10.010.11.00.0010.01100M A X 4754/M A X 4754A /M A X 4755/M A X 4756/M A X 4756A0.5Ω, Quad SPDT Switches in UCSP/QFN 8_______________________________________________________________________________________MAX4754/MAX4754A/MAX4755/MAX4756/MAX4756A0.5Ω, Quad SPDT Switches in UCSP/QFN_______________________________________________________________________________________9Detailed DescriptionThe MAX4754/MAX4754A/MAX4755/MAX4756/MAX4756A low on-resistance analog switches operate from a single +1.8V to +5.5V supply. The devices are fully specified for nominal 3V applications.The MAX4754/MAX4754A DPDT switch have two logic control inputs with each input controlling two SPDT switches. Each switch has a 0.5Ωon-resistance in the NO and NC terminals making it ideal for switching audio signals.The MAX4755 DPDT switch also has four 0.5ΩSPDT switches with the switch pairs 1 and 2 adding an 11.5Ωseries resistor to the NC terminal. This feature allows the user to drive an 8Ωspeaker as a 32Ωload, allowing it to be used as an ear speaker. Two logic control inputs are used to control the four switches.The MAX4756/MAX4756A has four 0.5ΩSPDT switches controlled by one logic control input (INA) and EN input to disable the switches.Applications InformationDigital Control InputsThe MAX4754/MAX4754A/MAX4755/MAX4756/MAX4756A logic inputs accept up to +5.5V regardless of the sup-ply voltage. For example, with a +3.3V supply IN_ can be driven low to GND and high to +5.5V, which allows mixed logic levels in a system. Driving the control logicinputs rail-to-rail also minimizes power consumption.For a +3V supply voltage, the logic thresholds are 0.5V (low) and 1.4V (high).For the MAX4756/MAX4756A, drive EN low to enable the COM_. When EN is high, COM _ is high impedance.Analog Signal LevelsAnalog signal inputs over the full voltage range (0V to V+) are passed through the switch with minimal change in on-resistance (see the Typical Operating Charac-teristics ). The switches are bidirectional so NO_, NC_,and COM_ can be either inputs or outputs.Power-Supply BypassingPower-supply bypassing improves noise margin and pre-vents switching noise from propagating from the V+ sup-ply to other components. A 0.1µF capacitor connected from V+ to GND is adequate for most applications.UCSP Applications InformationFor the latest application details on UCSP construction,dimensions, tape carrier information, printed circuit board techniques, bump-pad layout, and recommend-ed reflow temperature profile, as well as the latest infor-mation on reliability testing results, go to the Maxim website at /ucsp for the Application Note: UCSP—A Wafer-Level Chip-Scale Package .Typical Operating CircuitM A X 4754/M A X 4754A /M A X 4755/M A X 4756/M A X 4756A0.5Ω, Quad SPDT Switches in UCSP/QFN 10______________________________________________________________________________________Timing Circuits/Timing DiagramsFigure 1. Switching TimeFigure 2. Break-Before-Make IntervalFigure 3. Charge InjectionTiming Circuits/Timing Diagrams (continued)MAX4754/MAX4754A/MAX4755/MAX4756/MAX4756A0.5Ω, Quad SPDT Switches in UCSP/QFNFigure4. On-Loss, Off-Isolation, and CrosstalkFigure5. Channel On-/Off-Capacitance______________________________________________________________________________________11M A X 4754/M A X 4754A /M A X 4755/M A X 4756/M A X 4756A0.5Ω, Quad SPDT Switches in UCSP/QFN 12______________________________________________________________________________________Pin Configurations/Truth TablesChip InformationPROCESS: CMOSPackage Information MAX4754/MAX4754A/MAX4755/MAX4756/MAX4756A0.5Ω, Quad SPDT Switches in UCSP/QFN (The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information,go to /packages.)M A X 4754/M A X 4754A /M A X 4755/M A X 4756/M A X 4756A0.5Ω, Quad SPDT Switches in UCSP/QFN 14______________________________________________________________________________________MAX4754/MAX4754A/MAX4755/MAX4756/MAX4756A0.5Ω, Quad SPDT Switches in UCSP/QFNMaxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 ____________________15©2006 Maxim Integrated Productsis a registered trademark of Maxim Integrated Products, Inc.Package Information (continued)(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information,go to /packages .)Revision HistoryPages changed at Rev 1: 1–5, 7, 8, 13, 14, 15。

用于Peltier模块的集成温度控制器概论MAX1978 / MAX1979是用于Peltier热电冷却器(TEC)模块的最小, 最安全, 最精确完整的单芯片温度控制器。

片上功率FET和热控制环路电路可最大限度地减少外部元件, 同时保持高效率。

可选择的500kHz / 1MHz开关频率和独特的纹波消除方案可优化元件尺寸和效率, 同时降低噪声。

内部MOSFET的开关速度经过优化, 可降低噪声和EMI。

超低漂移斩波放大器可保持±0.001°C的温度稳定性。

直接控制输出电流而不是电压, 以消除电流浪涌。

独立的加热和冷却电流和电压限制提供最高水平的TEC保护。

MAX1978采用单电源供电, 通过在两个同步降压调节器的输出之间偏置TEC, 提供双极性±3A输出。

真正的双极性操作控制温度, 在低负载电流下没有“死区”或其他非线性。

当设定点非常接近自然操作点时, 控制系统不会捕获, 其中仅需要少量的加热或冷却。

模拟控制信号精确设置TEC 电流。

MAX1979提供高达6A的单极性输出。

提供斩波稳定的仪表放大器和高精度积分放大器, 以创建比例积分(PI)或比例积分微分(PID)控制器。

仪表放大器可以连接外部NTC或PTC热敏电阻, 热电偶或半导体温度传感器。

提供模拟输出以监控TEC温度和电流。

此外, 单独的过热和欠温输出表明当TEC温度超出范围时。

片上电压基准为热敏电阻桥提供偏置。

MAX1978 / MAX1979采用薄型48引脚薄型QFN-EP 封装, 工作在-40°C至+ 85°C温度范围。

采用外露金属焊盘的耐热增强型QFN-EP封装可最大限度地降低工作结温。

评估套件可用于加速设计。

应用光纤激光模块典型工作电路出现在数据手册的最后。

WDM, DWDM激光二极管温度控制光纤网络设备EDFA光放大器电信光纤接口ATE特征♦尺寸最小, 最安全, 最精确完整的单芯片控制器♦片上功率MOSFET-无外部FET♦电路占用面积<0.93in2♦回路高度<3mm♦温度稳定性为0.001°C♦集成精密积分器和斩波稳定运算放大器♦精确, 独立的加热和冷却电流限制♦通过直接控制TEC电流消除浪涌♦可调节差分TEC电压限制♦低纹波和低噪声设计♦TEC电流监视器♦温度监控器♦过温和欠温警报♦双极性±3A输出电流(MAX1978)♦单极性+ 6A输出电流(MAX1979)订购信息* EP =裸焊盘。

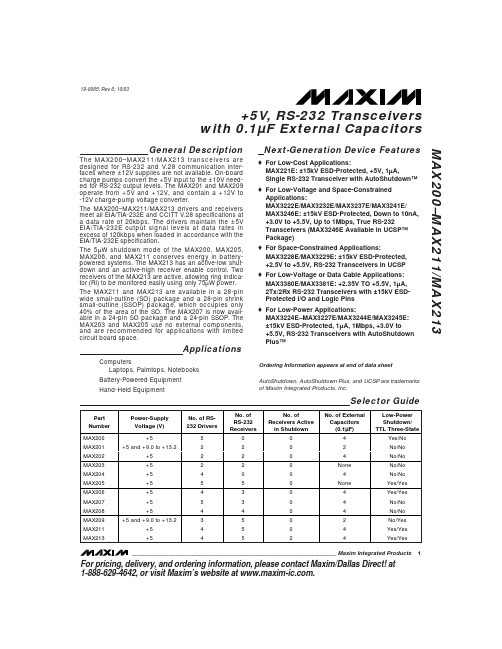

General DescriptionThe MAX200–MAX211/MAX213 transceivers are designed for RS-232 and V.28 communication inter-faces where ±12V supplies are not available. On-board charge pumps convert the +5V input to the ±10V need-ed for RS-232 output levels. The MAX201 and MAX209operate from +5V and +12V, and contain a +12V to -12V charge-pump voltage converter.The MAX200–MAX211/MAX213 drivers and receivers meet all EIA/TIA-232E and CCITT V.28 specifications at a data rate of 20kbps. The drivers maintain the ±5V EIA/TIA-232E output signal levels at data rates in excess of 120kbps when loaded in accordance with the EIA/TIA-232E specification.The 5µW shutdown mode of the MAX200, MAX205,MAX206, and MAX211 conserves energy in battery-powered systems. The MAX213 has an active-low shut-down and an active-high receiver enable control. Two receivers of the MAX213 are active, allowing ring indica-tor (RI) to be monitored easily using only 75µW power.The MAX211 and MAX213 are available in a 28-pin wide small-outline (SO) package and a 28-pin shrink small-outline (SSOP) package, which occupies only 40% of the area of the SO. The MAX207 is now avail-able in a 24-pin SO package and a 24-pin SSOP. The MAX203 and MAX205 use no external components,and are recommended for applications with limited circuit board space.ApplicationsComputersLaptops, Palmtops, Notebooks Battery-Powered Equipment Hand-Held Equipment Next-Generation Device Features ♦For Low-Cost Applications:MAX221E: ±15kV ESD-Protected, +5V, 1µA, Single RS-232 Transceiver with AutoShutdown™♦For Low-Voltage and Space-Constrained Applications:MAX3222E/MAX3232E/MAX3237E/MAX3241E/MAX3246E: ±15kV ESD-Protected, Down to 10nA,+3.0V to +5.5V, Up to 1Mbps, True RS-232Transceivers (MAX3246E Available in UCSP™Package)♦For Space-Constrained Applications:MAX3228E/MAX3229E: ±15kV ESD-Protected,+2.5V to +5.5V, RS-232 Transceivers in UCSP ♦For Low-Voltage or Data Cable Applications:MAX3380E/MAX3381E: +2.35V TO +5.5V, 1µA,2Tx/2Rx RS-232 Transceivers with ±15kV ESD-Protected I/O and Logic Pins ♦For Low-Power Applications:MAX3224E–MAX3227E/MAX3244E/MAX3245E:±15kV ESD-Protected, 1µA, 1Mbps, +3.0V to+5.5V, RS-232 Transceivers with AutoShutdown Plus™MAX200–MAX211/MAX213+5V , RS-232 Transceivers with 0.1µF External Capacitors ________________________________________________________________Maxim Integrated Products 119-0065; Rev 6; 10/03For pricing, delivery, and ordering information,please contact Maxim/Dallas Direct!at 1-888-629-4642, or visit Maxim’s website at .Ordering Information appears at end of data sheetAutoShutdown, AutoShutdown Plus, and UCSP are trademarks of Maxim Integrated Products, Inc.MAX200–MAX211/MAX213+5V , RS-232 Transceiverswith 0.1µF External Capacitors______________________________________________________________________________________19Ordering Information*Contact factory for dice specifications.M A X 200–M A X 211/M A X 213+5V , RS-232 Transceiverswith 0.1µF External Capacitors Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.20____________________Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600©2003 Maxim Integrated ProductsPrinted USAis a registered trademark of Maxim Integrated Products.Package Information(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information,go to /packages .)。

max3485eesa + T概述Max3485eesa + T是3.3V电源±15kV ESD保护,真正的RS485 / RS422收发器,采用8引脚nsoic封装。

该低功耗收发器包含一个驱动器和一个接收器。

max3485e传输速率高达15Mbps。

它具有增强的静电保护。

所有发送器输出和接收器输入均具有±15kV保护,并通过IEC 1000-4-2气隙放电;±8Kv保护是通过IEC 1000-4-2接触放电,±15kV保护是通过人体模型。

驱动器受到短路电流的限制,并通过将驱动器输出置于高阻抗状态的热关断电路来防止过多的功耗。

接收器输入具有故障安全功能,如果两个输入均打开,则提供逻辑高电平输出。

Max3485e适用于EMI敏感应用,集成服务,数字网络和数据包交换电源电压范围:3V至3.6V工作温度范围-40°C至85°C半双工通讯该操作由单个+ 3.3V电源供电,无电荷泵兼容+ 5V逻辑2Na小电流关闭模式共模输入电压范围:-7V至+ 12V工业标准75176引脚输出驱动器/接收器启用功能工业控制LAN,ISDN,低功耗RS-485 / RS-422收发器;分组交换;电信;用于EMI敏感应用的收发器Max3483,max3485,max3486,max3488,max3490和max3491是用于RS-485和RS-422通信的3.3V低功耗收发器,每个收发器都有一个驱动器和一个接收器。

Max3483和max3488具有有限速率驱动器,可以降低EMI并减少由于端子匹配电缆不合适而引起的反射,从而实现高达250kbps的无错误数据传输。

由于其有限的摆幅速率,Max3486可以实现最大2.5mbps 的传输速率。

Max3485,max3490和max3491可以实现高达10Mbps的传输速率。

驱动器具有短路电流限制,并且可以通过热关断电路将驱动器的输出设置为高阻状态,以防止过多的功率损耗。