半导体工艺英语名词解释

- 格式:doc

- 大小:20.00 KB

- 文档页数:5

1. 何谓PIE PIE的主要工作是什幺答:Process Integration Engineer(工艺整合工程师), 主要工作是整合各部门的资源, 对工艺持续进行改善, 确保产品的良率(yield)稳定良好。

2. 200mm,300mm Wafer 代表何意义答:8吋硅片(wafer)直径为200mm , 直径为300mm硅片即12吋.3. 目前中芯国际现有的三个工厂采用多少mm的硅片(wafer)工艺未来北京的Fab4(四厂)采用多少mm的wafer工艺答:当前1~3厂为200mm(8英寸)的wafer, 工艺水平已达工艺。

未来北京厂工艺wafer将使用300mm(12英寸)。

4. 我们为何需要300mm答:wafer size 变大,单一wafer 上的芯片数(chip)变多,单位成本降低200→300 面积增加倍,芯片数目约增加倍5. 所谓的um 的工艺能力(technology)代表的是什幺意义答:是指工厂的工艺能力可以达到um的栅极线宽。

当栅极的线宽做的越小时,整个器件就可以变的越小,工作速度也越快。

6. 从>>>> 的technology改变又代表的是什幺意义答:栅极线的宽(该尺寸的大小代表半导体工艺水平的高低)做的越小时,工艺的难度便相对提高。

从-> -> -> -> 代表着每一个阶段工艺能力的提升。

7. 一般的硅片(wafer)基材(substrate)可区分为N,P两种类型(type),何谓N, P-type wafer答:N-type wafer 是指掺杂negative元素(5价电荷元素,例如:P、As)的硅片, P-type 的wafer 是指掺杂positive 元素(3价电荷元素, 例如:B、In)的硅片。

8. 工厂中硅片(wafer)的制造过程可分哪几个工艺过程(module)答:主要有四个部分:DIFF(扩散)、TF(薄膜)、PHOTO(光刻)、ETCH(刻蚀)。

``半导体工艺名词及解答1、影响工厂成本的主要因素有哪些?答:Direct Material 直接材料,例如:芯片Indirect Material间接材料,例如气体… Labor人力Fixed Manufacturing机器折旧,维修,研究费用……等Production Support其它相关单位所花费的费用2、在FAB内,间接物料指哪些?答:Gas 气体Chemical 酸,碱化学液PHOTO Chemical 光阻,显影液Slurry 研磨液Target 靶材Quartz 石英材料Pad & Disk 研磨垫Container 晶舟盒(用来放芯片) Control Wafer 控片Test Wafe r测试,实验用的芯片3、什么是变动成本(Variable Cost)?答:成本随生产量之增减而增减.例如:直接材料,间接材料4、什么是固定成本(Fixed Cost)?答:此种成本与产量无关,而与每一期间保持一固定数额.例如:设备租金,房屋折旧及檵器折旧5、Yield(良率)会影响成本吗?如何影响?答:Fab yield= 若无报废产生,投入完全等于产出,则成本耗费最小CP Yield:CP Yield 指测试一片芯片上所得到的有效的IC数目。

当产出芯片上的有效IC数目越多,即表示用相同制造时间所得到的效益愈大.6、生产周期(Cycle Time)对成本(Cost)的影响是什么?答:生产周期愈短,则工厂制造成本愈低。

正面效益如下: (1) 积存在生产线上的在制品愈少(2) 生产材料积存愈少(3) 节省管理成本(4) 产品交期短,赢得客户信赖,建立公司信誉FAC1、根据工艺需求排气分几个系统?答:分为一般排气(General)、酸性排气(Scrubbers)、碱性排气(Ammonia)和有机排气(Solvent)四个系统。

2、高架地板分有孔和无孔作用?答:使循环空气能流通,不起尘,保证洁净房内的洁净度; 防静电;便于HOOK-UP。

半导体行业英文术语English:Some common terms in the semiconductor industry include:1. Integrated Circuit (IC): A small electronic device made out of a semiconductor material that can perform an extensive range of functions.2. Semiconductor manufacturing: The process of creating integrated circuits and semiconductor devices, including design, fabrication, and packaging.3. Wafer: A thin slice of semiconductor material used as the substrate for the fabrication of integrated circuits.4. Photolithography: A process used to transfer circuit patterns onto the wafer surface using light and photoresist materials.5. Die: A single piece of an integrated circuit, typically cut from a wafer after fabrication and packaging.6. Yield: The percentage of functional and operational semiconductor devices produced during the manufacturing process.7. Moore's Law: The observation that the number of transistors in a dense integrated circuit doubles approximately every two years, leading to exponential growth in processing power.8. Quantum tunneling: A phenomenon in which electrons penetrate through a potential barrier they classically shouldn't be able to cross, crucial for the operation of semiconductor devices.中文翻译:半导体行业的一些常见术语包括:1. 集成电路(IC):由半导体材料制成的小型电子器件,可执行广泛的功能。

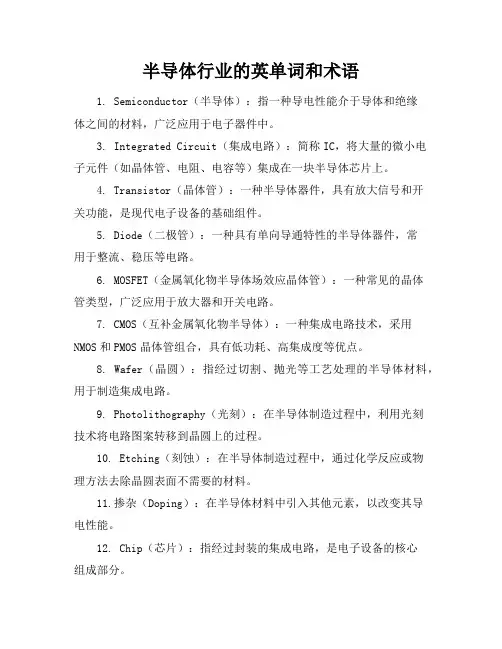

半导体行业的英单词和术语1. Semiconductor(半导体):指一种导电性能介于导体和绝缘体之间的材料,广泛应用于电子器件中。

3. Integrated Circuit(集成电路):简称IC,将大量的微小电子元件(如晶体管、电阻、电容等)集成在一块半导体芯片上。

4. Transistor(晶体管):一种半导体器件,具有放大信号和开关功能,是现代电子设备的基础组件。

5. Diode(二极管):一种具有单向导通特性的半导体器件,常用于整流、稳压等电路。

6. MOSFET(金属氧化物半导体场效应晶体管):一种常见的晶体管类型,广泛应用于放大器和开关电路。

7. CMOS(互补金属氧化物半导体):一种集成电路技术,采用NMOS和PMOS晶体管组合,具有低功耗、高集成度等优点。

8. Wafer(晶圆):指经过切割、抛光等工艺处理的半导体材料,用于制造集成电路。

9. Photolithography(光刻):在半导体制造过程中,利用光刻技术将电路图案转移到晶圆上的过程。

10. Etching(刻蚀):在半导体制造过程中,通过化学反应或物理方法去除晶圆表面不需要的材料。

11.掺杂(Doping):在半导体材料中引入其他元素,以改变其导电性能。

12. Chip(芯片):指经过封装的集成电路,是电子设备的核心组成部分。

13. PCB(印刷电路板):一种用于支撑和连接电子元件的板材,上面布满了导电线路。

14. Moore's Law(摩尔定律):指集成电路上可容纳的晶体管数量大约每两年翻一番,预测了半导体行业的发展趋势。

15. EDA(电子设计自动化):指利用计算机软件辅助设计电子系统,包括电路设计、仿真、验证等环节。

16. Foundry(代工厂):专门为其他公司生产半导体芯片的企业。

17. Semiconductor Equipment Manufacturer(半导体设备制造商):为半导体行业提供生产设备的公司。

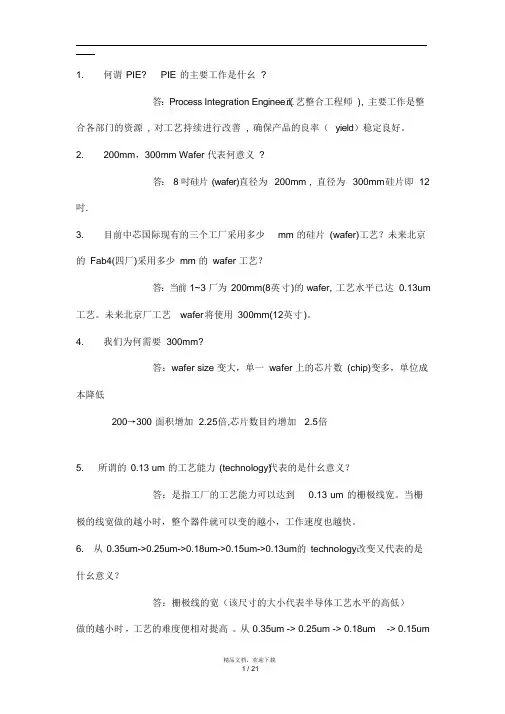

1. 何谓PIE? PIE 的主要工作是什幺?答:Process Integration Enginee工r( 艺整合工程师), 主要工作是整合各部门的资源, 对工艺持续进行改善, 确保产品的良率(yield)稳定良好。

2. 200mm,300mm Wafer 代表何意义?答:8 吋硅片(wafer)直径为200mm , 直径为300mm 硅片即12 吋.3. 目前中芯国际现有的三个工厂采用多少mm 的硅片(wafer)工艺?未来北京的Fab4(四厂)采用多少mm 的wafer 工艺?答:当前1~3 厂为200mm(8英寸)的wafer, 工艺水平已达0.13um 工艺。

未来北京厂工艺wafer 将使用300mm(12英寸)。

4. 我们为何需要300mm?答:wafer size 变大,单一wafer 上的芯片数(chip)变多,单位成本降低200→300 面积增加 2.25倍,芯片数目约增加 2.5倍5. 所谓的0.13 um 的工艺能力(technology代)表的是什幺意义?答:是指工厂的工艺能力可以达到0.13 um 的栅极线宽。

当栅极的线宽做的越小时,整个器件就可以变的越小,工作速度也越快。

6. 从0.35um->0.25um->0.18um->0.15um->0.13um的technology改变又代表的是什幺意义?答:栅极线的宽(该尺寸的大小代表半导体工艺水平的高低)做的越小时,工艺的难度便相对提高。

从0.35um -> 0.25um -> 0.18um -> 0.15um-> 0.13um 代表着每一个阶段工艺能力的提升。

7. 一般的硅片(wafer)基材(substrate可)区分为N,P 两种类型(type),何谓N, P-type wafer?答:N-type wafer 是指掺杂negative元素(5 价电荷元素,例如:P、As)的硅片, P-type 的wafer 是指掺杂positive 元素(3 价电荷元素, 例如:B、In)的硅片。

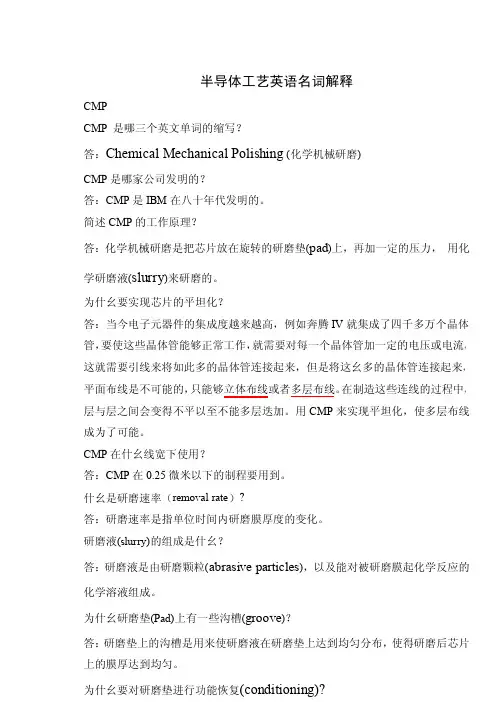

半导体工艺英语名词解释CMPCMP是哪三个英文单词的缩写?答:Chemical Mechanical Polishing(化学机械研磨)CMP是哪家公司发明的?答:CMP是IBM在八十年代发明的。

简述CMP的工作原理?答:化学机械研磨是把芯片放在旋转的研磨垫(pad)上,再加一定的压力,用化学研磨液(slurry)来研磨的。

为什幺要实现芯片的平坦化?答:当今电子元器件的集成度越来越高,例如奔腾IV就集成了四千多万个晶体管,要使这些晶体管能够正常工作,就需要对每一个晶体管加一定的电压或电流,这就需要引线来将如此多的晶体管连接起来,但是将这幺多的晶体管连接起来,平面布线是不可能的,只能够立体布线或者多层布线。

在制造这些连线的过程中,层与层之间会变得不平以至不能多层迭加。

用CMP来实现平坦化,使多层布线成为了可能。

CMP在什幺线宽下使用?答:CMP在0.25微米以下的制程要用到。

什幺是研磨速率(removal rate)?答:研磨速率是指单位时间内研磨膜厚度的变化。

研磨液(slurry)的组成是什幺?答:研磨液是由研磨颗粒(abrasive particles),以及能对被研磨膜起化学反应的化学溶液组成。

为什幺研磨垫(Pad)上有一些沟槽(groove)?答:研磨垫上的沟槽是用来使研磨液在研磨垫上达到均匀分布,使得研磨后芯片上的膜厚达到均匀。

为什幺要对研磨垫进行功能恢复(conditioning)?答:研磨垫在研磨一段时间后,就有一些研磨颗粒和研磨下来的膜的残留物留在研磨垫上和沟道内,这些都会影响研磨液在研磨垫的分布,从而影响研磨的均匀性。

什幺是blanket wafer ?什幺是pattern wafer ?答:blanket wafer 是指无图形的芯片。

pattern wafer 是指有图形的芯片。

Blanket wafer 与pattern wafer 的removal rate 会一样吗?答:一般来说,blanket wafer 与pattern wafer 的removal rate 是不一样的。

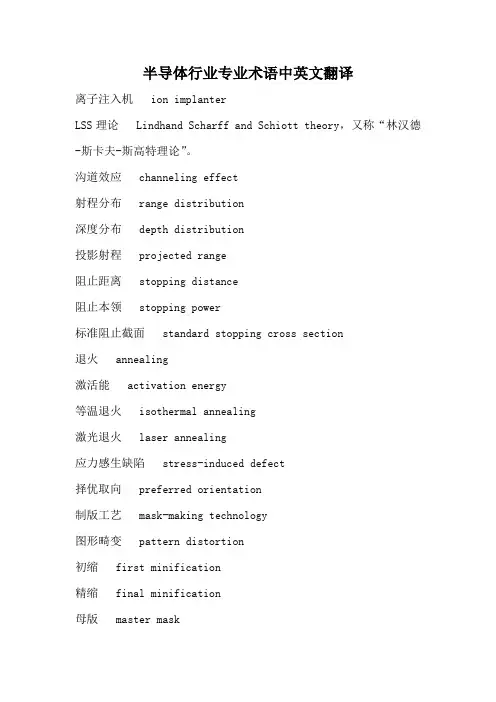

半导体行业专业术语中英文翻译离子注入机 ion implanterLSS理论 Lindhand Scharff and Schiott theory,又称“林汉德-斯卡夫-斯高特理论”。

沟道效应 channeling effect射程分布 range distribution深度分布 depth distribution投影射程 projected range阻止距离 stopping distance阻止本领 stopping power标准阻止截面 standard stopping cross section退火 annealing激活能 activation energy等温退火 isothermal annealing激光退火 laser annealing应力感生缺陷 stress-induced defect择优取向 preferred orientation制版工艺 mask-making technology图形畸变 pattern distortion初缩 first minification精缩 final minification母版 master mask铬版 chromium plate干版 dry plate乳胶版 emulsion plate透明版 see-through plate高分辨率版 high resolution plate, HRP超微粒干版 plate for ultra-microminiaturization 掩模 mask掩模对准 mask alignment对准精度 alignment precision光刻胶 photoresist,又称“光致抗蚀剂”。

负性光刻胶 negative photoresist正性光刻胶 positive photoresist无机光刻胶 inorganic resist多层光刻胶 multilevel resist电子束光刻胶 electron beam resistX射线光刻胶 X-ray resist刷洗 scrubbing甩胶 spinning涂胶 photoresist coating后烘 postbaking光刻 photolithographyX射线光刻 X-ray lithography电子束光刻 electron beam lithography离子束光刻 ion beam lithography深紫外光刻 deep-UV lithography光刻机 mask aligner投影光刻机 projection mask aligner曝光 exposure接触式曝光法 contact exposure method接近式曝光法 proximity exposure method光学投影曝光法 optical projection exposure method 电子束曝光系统 electron beam exposure system分步重复系统 step-and-repeat system显影 development线宽 linewidth去胶 stripping of photoresist氧化去胶 removing of photoresist by oxidation等离子[体]去胶 removing of photoresist by plasma 刻蚀 etching干法刻蚀 dry etching反应离子刻蚀 reactive ion etching, RIE各向同性刻蚀 isotropic etching各向异性刻蚀 anisotropic etching反应溅射刻蚀 reactive sputter etching离子铣 ion beam milling,又称“离子磨削”。

半导体工艺英文缩写半导体工艺是半导体行业中的一个重要领域,涉及到半导体材料和器件的制造过程。

由于该领域技术含量高,专业术语较多,因此人们常常使用英文缩写来简化表达。

下面是一些常见的半导体工艺英文缩写及其解释:1.CMOS: 压缩氧化法半导体互补金属-氧化物半导体CMOS是一种常见的半导体工艺,它使用压缩氧化法在半导体材料上形成金属-氧化物半导体结构。

这种结构可以实现低功耗、低电压操作,并且在集成电路中应用广泛。

2.PVD: 物理气相沉积物理气相沉积是一种半导体材料薄膜制备的技术,它利用物理过程将固体材料转化为气体,然后在半导体表面沉积成薄膜。

这种技术可以实现高质量的薄膜制备,并且广泛用于半导体器件的制造。

3.CVD: 化学气相沉积化学气相沉积是一种半导体材料薄膜制备的技术,它利用化学反应将气体转化为固体材料,并在半导体表面沉积成薄膜。

这种技术可以实现较高的沉积速度和较大的沉积面积,并且在集成电路制造中得到广泛应用。

4.RTP: 快速热退火快速热退火是一种半导体工艺,它通过快速升温和冷却的方式来进行热处理。

这种工艺可以实现材料的结晶、再结晶和晶格调控,从而提高半导体器件的电学性能和稳定性。

5.DUV: 深紫外深紫外是一种波长较短的紫外光,通常用于半导体制造中的光刻工艺。

它具有较高的分辨率和较小的曝光误差,可以实现微细结构的制造和高精度印刷。

6.BEOL: 背端工艺背端工艺是指半导体制造中从晶圆电路层到封装层的工艺步骤,主要包括金属线路的布线、电压与数据传输的测试、集成电路封装等工作。

这些工艺步骤对于确保电路的正常运行和稳定性至关重要。

7.FEOL: 前端工艺前端工艺是指半导体制造中从晶圆加工到背端工艺之前的工艺步骤,主要包括晶圆清洁、刻蚀、沉积、光刻、扩散等工作。

这些工艺步骤对于制备高质量的半导体材料和器件起着关键作用。

总结起来,半导体工艺英文缩写是半导体行业中常用的专业术语,它简化了表达,加快了交流。

半导体行业英语专业术语1.Angle of incidence:入射角。

2.Dielectric:介电质。

3.Epitaxial Growth:外延生长。

4.Junction:结。

5.MOS transistor:MOS晶体管。

6.Lithography:光刻。

7.Photoresist:光刻胶。

8.Picking:取片。

9.Reflow soldering:热风焊接。

10.Deposition:沉积。

11.Diffusion:扩散。

12.Doping:掺杂。

13.Epitaxy:外延。

14.Furnace:炉。

15.Gate oxide:栅极氧化层。

16.Grinding:研磨。

17.Ion Implantation:离子注入。

18.Polishing:抛光。

19.Substrate:基底。

20.Chip:芯片。

21.Wafer:晶圆。

22.Yield:良率。

23.Masking:掩模。

24.Electrical Characterization:电性测试。

25.Suitability Test:可靠性测试。

26.Failure Analysis:失效分析。

27.Annealing:退火。

28.Threshold Voltage:阈值电压。

29.Voltage Transfer Curve:电压传递曲线。

30.Contact Resistance:接触电阻。

31.Electromigration:电迁移。

32.Inspection:检验。

33.CMP:表面处理。

34.CVD:化学气相沉积。

35.Metallization:金属化。

36.Microscopy:显微镜。

37.Ohmic Contact:正性接触。

38.Oxidation:氧化。

39.PECVD:电演化学气相沉积。

40.Photolithography:光刻工艺。

41.Sputtering:溅射。

42.Thermal Oxidation:热氧化。

半导体工艺英语名词解释CMPCMP 是哪三个英文单词的缩写?答: Chemical Mechanical Polishing (化学机械研磨)CMP是哪家公司发明的?答: CMP是IBM在八十年代发明的。

简述CMP的工作原理?答: 化学机械研磨是把芯片放在旋转的研磨垫(pad)上, 再加一定的压力, 用化学研磨液(slurry)来研磨的。

为什幺要实现芯片的平坦化?答: 当今电子元器件的集成度越来越高, 例如奔腾IV就集成了四千多万个晶体管, 要使这些晶体管可以正常工作, 就需要对每一个晶体管加一定的电压或电流, 这就需要引线来将如此多的晶体管连接起来, 但是将这幺多的晶体管连接起来, 平面布线是不也许的, 只可以立体布线或者多层布线。

在制造这些连线的过程中, 层与层之间会变得不平以至不能多层迭加。

用CMP来实现平坦化, 使多层布线成为了也许。

CMP在什幺线宽下使用?答: CMP在0.25微米以下的制程要用到。

什幺是研磨速率(removal rate)?答: 研磨速率是指单位时间内研磨膜厚度的变化。

研磨液(slurry)的组成是什幺?答: 研磨液是由研磨颗粒(abrasive particles), 以及能对被研磨膜起化学反映的化学溶液组成。

为什幺研磨垫(Pad)上有一些沟槽(groove)?答: 研磨垫上的沟槽是用来使研磨液在研磨垫上达成均匀分布, 使得研磨后芯片上的膜厚达成均匀。

为什幺要对研磨垫进行功能恢复(conditioning)?答: 研磨垫在研磨一段时间后, 就有一些研磨颗粒和研磨下来的膜的残留物留在研磨垫上和沟道内,这些都会影响研磨液在研磨垫的分布,从而影响研磨的均匀性。

什幺是blanket wafer ?什幺是pattern wafer ?答: blanket wafer 是指无图形的芯片。

pattern wafer 是指有图形的芯片。

Blanket wafer 与pattern wafer的removal rate会同样吗?答: 一般来说, blanket wafer 与pattern wafer的removal rate是不同样的。

``半导体工艺名词及解答1、影响工厂成本的主要因素有哪些?答:Direct Material 直接材料,例如:芯片Indirect Material间接材料,例如气体… Labor人力Fixed Manufacturing机器折旧,维修,研究费用……等Production Support其它相关单位所花费的费用2、在FAB内,间接物料指哪些?答:Gas 气体Chemical 酸,碱化学液PHOTO Chemical 光阻,显影液Slurry 研磨液Target 靶材Quartz 石英材料Pad & Disk 研磨垫Container 晶舟盒(用来放芯片) Control Wafer 控片Test Wafe r测试,实验用的芯片3、什么是变动成本(Variable Cost)?答:成本随生产量之增减而增减.例如:直接材料,间接材料4、什么是固定成本(Fixed Cost)?答:此种成本与产量无关,而与每一期间保持一固定数额.例如:设备租金,房屋折旧及檵器折旧5、Yield(良率)会影响成本吗?如何影响?答:Fab yield= 若无报废产生,投入完全等于产出,则成本耗费最小CP Yield:CP Yield 指测试一片芯片上所得到的有效的IC数目。

当产出芯片上的有效IC数目越多,即表示用相同制造时间所得到的效益愈大.6、生产周期(Cycle Time)对成本(Cost)的影响是什么?答:生产周期愈短,则工厂制造成本愈低。

正面效益如下: (1) 积存在生产线上的在制品愈少(2) 生产材料积存愈少(3) 节省管理成本(4) 产品交期短,赢得客户信赖,建立公司信誉FAC1、根据工艺需求排气分几个系统?答:分为一般排气(General)、酸性排气(Scrubbers)、碱性排气(Ammonia)和有机排气(Solvent)四个系统。

2、高架地板分有孔和无孔作用?答:使循环空气能流通,不起尘,保证洁净房内的洁净度; 防静电;便于HOOK-UP。

半导体名词解释Last updated at 10:00 am on 25th December 2020 1.何谓PIE PIE的主要工作是什幺答:Process Integration Engineer(工艺整合工程师),主要工作是整合各部门的资源,对工艺持续进行改善,确保产品的良率(yield)稳定良好。

2.200mm, 300mm Wafer 代表何意义答:8寸硅片(wafer)直径为200mm ,直径为300mm硅片即12寸.3.目前中芯国际现有的三个工厂采用多少mm的硅片(wafer)工艺未来北京的Fab4 (四厂)采用多少mm的wafer工艺答:当前广3厂为200mm(8英寸)的wafer,工艺水平已达工艺。

未来北京厂工艺wafer 将使用300mm(12英寸)。

4.我们为何需要300mm答:wafer size变大,单一wafer上的芯片数(chip)变多,单位成本降低200-300面积增加倍,芯片数L1约增加倍5.所谓的um的工艺能力(technology)代表的是什幺意义答:是指工厂的工艺能力可以达到um的栅极线宽。

当栅极的线宽做的越小时,整个器件就可以变的越小,工作速度也越快。

6.从〉>〉>的technology改变乂代表的是什幺意义答:栅极线的宽(该尺寸的大小代表半导体工艺水平的高低)做的越小时,工艺的难度便相对提高。

从-〉-〉-〉-〉代表着每一个阶段工艺能力的提升。

7.—般的硅片(wafer)基材(substrate)可区分为N, P两种类型(type),何谓N, P- type wafer答:N-type wafer是指掺杂negative元素(5价电荷元素,例如:P、As)的硅片,P- type 的wafer是指掺杂positive元素(3价电荷元素,例如:B、In)的硅片。

8.工厂中硅片(wafer)的制造过程可分哪儿个工艺过程(module)答:主要有四个部分:DIFF (扩散)、TF(薄膜)、PHOTO (光刻)、ETCH (刻蚀)。

半导体工艺英语名词解释CMPCMP 是哪三个英文单词的缩写答:Chemical Mechanical Polishing (化学机械研磨)CMP是哪家公司发明的答:CMP是IBM在八十年代发明的。

简述CMP的工作原理答:化学机械研磨是把芯片放在旋转的研磨垫(pad)上,再加一定的压力,用化学研磨液(slurry)来研磨的。

为什幺要实现芯片的平坦化答:当今电子元器件的集成度越来越高,例如奔腾IV就集成了四千多万个晶体管,要使这些晶体管能够正常工作,就需要对每一个晶体管加一定的电压或电流,这就需要引线来将如此多的晶体管连接起来,但是将这幺多的晶体管连接起来,平面布线是不可能的,只能够立体布线或者多层布线。

在制造这些连线的过程中,层与层之间会变得不平以至不能多层迭加。

用CMP来实现平坦化,使多层布线成为了可能。

CMP在什幺线宽下使用答:CMP在微米以下的制程要用到。

什幺是研磨速率(removal rate)答:研磨速率是指单位时间内研磨膜厚度的变化。

研磨液(slurry)的组成是什幺答:研磨液是由研磨颗粒(abrasive particles),以及能对被研磨膜起化学反应的化学溶液组成。

为什幺研磨垫(Pad)上有一些沟槽(groove)答:研磨垫上的沟槽是用来使研磨液在研磨垫上达到均匀分布,使得研磨后芯片上的膜厚达到均匀。

为什幺要对研磨垫进行功能恢复(conditioning)答:研磨垫在研磨一段时间后,就有一些研磨颗粒和研磨下来的膜的残留物留在研磨垫上和沟道内,这些都会影响研磨液在研磨垫的分布,从而影响研磨的均匀性。

什幺是blanket wafer 什幺是pattern wafer答:blanket wafer 是指无图形的芯片。

pattern wafer 是指有图形的芯片。

Blanket wafer 与pattern wafer的removal rate会一样吗答:一般来说,blanket wafer与pattern wafer的removal rate是不一样的。

为什幺Blanket wafer 与pattern wafer的removal rate会不一样答:Blanket wafer 与pattern wafer的removal rate不一样是由于pattern wafer上有的地方高,有的地方低,高的地方压强(pressure)大,研磨速度大(回想Preston关系式)。

而且,总的接触到研磨的面积要比Blanket wafer接触到研磨的面积要小,所以总的压强大,研磨速度大。

在研磨后,为什幺要对芯片进行清洗答:芯片在研磨后,会有大量的研磨颗粒和其它一些残留物留在芯片上,这些是对后面的工序有害,必须要清洗掉。

CMP (process tool)分为几类答:对不同膜的研磨,CMP分为Oxide, W, Poly, Cu CMP等。

CMP常见的缺陷(defect)是什幺答:CMP常见的缺陷有划伤(scratch), 残留物(residue), 腐蚀(corrosion).W Remove Rate 用什幺方法来测答:W是指Tungsten (钨), remove rate是指化学机械研磨速率,即单位时间内厚度的变化。

由于钨是不透光的物质,其厚度的测试需由测方块电阻(sheet resistance or Rs)的机台来测量。

用来测定Oxide Thickness的方法是什幺答:由于二氧化硅(Oxide)是透明的,所以通常测量二氧化硅的厚度(Thickness)用椭偏光法。

为什幺要测particle(尘粒)答:外来的particle对半导体器件的良率有很大的影响,所以在半导体器件的制造过程中一定要对尘粒进行严格的控制。

用光学显微镜检查芯片的重点是什幺答:用光学显微镜(Optical Microscope or OM)可以观察到大的缺陷如(1) 划伤(scratch),(2) 残留物(residue)CMP 区Daily monitor日常测机主要做哪些项目答:任何机台的特性(performance)会随时间的变化而变化。

日常测机是用来检测机台是否处于正常的工作状态。

CMP的日常测机通常要测以下一些项目:(1) removal rate (2) particle (3) uniformityCMP区域哪些机台可以共享一种dummy wafer,哪些不能答:W DUMMY 只能用于w机台,poly dummy 只能用于poly机台,OXIDE dummy可以共享。

什幺是over polish答:化学机械研磨是去掉芯片上的膜的高低不平的部分,从而达到平坦化或所需要的图形。

如果研磨掉膜的厚度比预定的厚度要大,就叫overpolish。

Overpolish后的芯片是不可挽救的。

什幺是under polish答:如果研磨掉膜的厚度比预定的厚度要小,就叫underpolish。

Underpolish后的芯片可以通过重新研磨来补救。

CMP 研磨机台由哪几部分组成答:CMP机台由芯片机械传送装置,研磨和清洗等组成CMP区域的consumables (易耗品)通常是指哪些答:CMP区域的consumables (易耗品)通常是指研磨液,研磨垫,清洗用的刷(brush), diamond disk(金刚石盘)等。

FA 1. SEM 的用途答:用途:形貌观察与量测参考,截面观察与TOP VIEW观察2. SEM-4700和SEM-5200的加速电压分别为多少答:~30KV 3. 送TEMcase时工程师要注意什幺事答:(1) 送件时:Please cap oxide or nitride layer以方便分析者分辨其接口以及避免研磨时peeling (2) Request需用OM相片或手绘清楚地标示其top view and X-section structure (3) FA engineer会与委托者讨论与建议其试片之处理方式4.我们所用TEM的加速电压为多少答:200KV 5. EDX的用途答:Fast Element Microanalysis(快速元素微分析)Line scanning (线扫描)Mapping (面扫描) 6. EDX 是那三个字的缩写答:Energy Dispersive Spectrometry(能量分析光谱仪) 7. FIB的用途答:(1) 作定点切削并边切边观察(2) 电路修补(3) TEM样品制作8. 做FIB case时工程师要注意什幺事答:(1) Top layer is polyimide or Oxide layer时需提前二小时送件以便有充份时间处理样品(2) 请注明试片之Top layer是何种材质. (3) Request KLA defect map analysis须提前将data file transfer 至Knight system 9. SEM是哪三个字的缩写中文名称是什幺答:Scanning Electron Microscope,中文是扫描式电子显微镜10. SEM-4700和SEM-5200的分辨率分别为多少答:@30KV 11. SEM-4700和SEM-5200 主要的区别是什幺答:(1) S-5200 比S-4700的分辨率高,(S-5200分辨率为at 30kV, at 1KV)(S-4700分辨率为at 15kV, at 1KV )(2) S-4700一次能同时放约8片试片而S-5200只能一次一个试片,而S-5200只能看样品的Cross section. (3) 倍率低于150kx在S-4700分析,倍率高于150kx在S-5200分析12. TEM是哪三个字的缩写中文名称是什幺答:Transmission Electron Microscope,中文是穿透式电子显微镜13. 当使用TEM来观测样品时,为求图象清晰,需要镀金或用Chemical吗答:不需要,只要将样品处理到一定的厚度(大约1um),便于电子束穿过即可。

14. 我们的TEM需用到底片拍照吗答:不需要。

我们的TEM是用CCD成像,照片以电子档的形式提供给客户。

15. 我们所用TEM的分辨率为多少答:点分辨率(能分辨一点与另一点);线分辨率(能分辨线与线之间距离)。

16. TEM有哪些应用答:微区结构,形貌观察;晶体结构分析;微区成份分析;超薄氧化层厚度测量等。

17. 我们的SEM,FIB,TEM需要用到底片吗答:不需要,照片都是以电子档的形式提供给客户。

18. EDX对样品有何要求答:(1) 样品要尽可能地使表面平滑(2) 取样的样品数要足够(如粉末状样品)以便置于SEM内做EDX分析(3) 如charging样品中确定不含有导电物铂(Pt),则可以镀金以防charging 19. EDX 中加液氮的作用是什幺答:冷却EDX探头。

20. TEM EDX和SEM EDX相比有哪些优缺点答:(1) TEM EDX 空间分辨率较SEM EDX高. (2) TEM试片较SEM试片薄所以其电子束穿透(3) TEM试片准备较SEM试片复杂21. FIB是哪三个字的缩写中文名称是什幺答:Focus Ion Beam,中文是聚焦离子束22. Auger 仪器能分析到多少深度的信号答:大约是表面50 23. 申请做FA case的一般过程是什幺答:要详细填好FA request form(detailed background information& expectation)。

并由manager签署认可,委托单若信息模糊,描述不清将会被拒收。

与FA人员讨论,进一步提供表格上不便表达的信息24. Wafer sent to FA lab注意事项答:芯片需用芯片盒装好, 不可以夹在笔记本内或用塑料袋装, 尤其是光阻或需要表面分析的芯片表面更不能压到或污染, 另外送TEM表面分析的芯片最好再上一层OXIDE or NITEIDE以保护欲观察layer避免PEELIN。