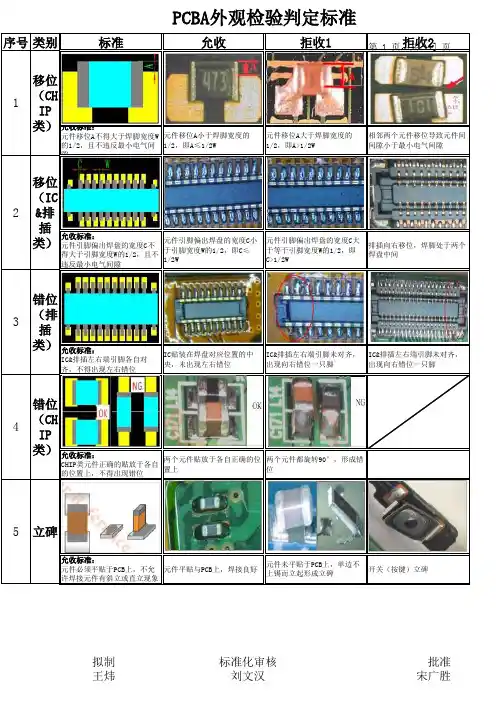

PCBA外观检验规范

- 格式:doc

- 大小:6.03 MB

- 文档页数:15

PCBA(Printed Circuit Board Assembly)外观检验标准与手法如下:一、外观检验标准元件焊点:焊锡球应符合最小电气间隙,焊锡球应固定在免清除的残渣内或覆盖在保形涂覆下。

焊锡球的直径应≤0.13mm,否则会被拒收。

元件侧立:宽度对高度比例不超过二比一,元件可焊端与PAD表面应完全润湿,元件大于1206类时将被拒收。

元件立碑:片式元件末端翘起(立碑)将无法通过检验。

元件扁平、L形和翼形引脚偏移:最大侧面偏移不大于引脚宽度或0.5mm(0.02英寸),否则会被拒收。

圆柱体端帽可焊端侧面偏移:侧面偏移≤元件直径宽度或PAD宽度25%,否则会被拒收。

片式元件矩形或方形可焊端元件侧面偏移:侧面偏移≤元件可焊端宽度或PAD宽度50%,否则会被拒收。

J形引脚侧面偏移:侧面偏移≤引脚宽度50%,否则会被拒收。

元件反向:元件上的极性点与PCB二极管丝印方向一致,否则将被拒收。

元件锡量过多:最大高度焊点可以超出PAD或延伸至可焊端的端帽金属镀层顶部,但不可延伸至元件体,否则将被拒收。

元件空焊:元件引脚与PAD之间焊接点良湿润饱满,元件引脚无翘起,否则将被拒收。

元件冷焊:回流过程锡膏完全延伸,焊接点上的锡完全湿润且表面光泽,否则将被拒收。

元件少件或多件:BOM清单要求某个贴片位号需要贴装元件却未贴装元件或不需要贴装元件却已贴装元件,将被拒收。

元件损件:任何边缘剥落小于元件宽度或元件厚度25%,末端顶部金属镀层缺失最大为50%(各末端),否则将被拒收。

元件起泡和分层:起泡和分层的区域不超出镀通孔间或内部导线间距的25%,否则将被拒收。

二、外观检验手法目视检验:通过肉眼或低倍放大镜对PCBA进行外观检查,主要查看上述问题点。

自动光学检测(AOI):通过高倍放大镜和摄像机对PCBA进行自动扫描,对图像进行识别和处理,发现和记录存在的问题。

电子显微镜检测(SEM):利用电子显微镜对PCBA进行高倍放大,以便发现更细微的问题。

1.目的建立PCBA外观目视检验,使产品检验之判定有所依循,同时依此检验结果的回馈、分析、矫正,以确保产品之质量。

2.适用范围本标准通用于本公司生产任何产品PCBA的外观检验(在无特殊规定的情况外)。

包括公司内部生产和发外加工的产品。

特殊规定是指:因零件的特性或其它特殊需求,则PCBA的标准可加以适当修订,但其有效性应超越通用型的外观标准。

3.职责3.1IQC负责根据本规范对公司外协加工返回的PCBA进行检验。

3.2IPQC负责根据本规范对公司自加工的PCBA进行检验。

4.作业程序及标准要求4.1产品来料包装4.1.1为防止PCBA损坏,来料需双层防护:防护外箱(防静电周转箱或纸箱)+内部隔离(防静电珍珠棉或气泡棉),PCBA板之间以及PCBA板与箱体之间应用适当的空间,不可挤压。

4.1.2每层PCBA板应用纸板或防静电珍珠棉隔开,顶层加一层防静电珍珠棉。

若为周转箱则顶面有大于50mm的空间,保证周转箱叠放时不要压到。

4.2检验作业规范4.2.1检验前应先确保检验环境的光照应充足,工作平台清洁、接地。

4.2.2在接触前,为防止元件被静电击坏、手指污染,应戴上ESD防护手套或指套、防静电手环并确保接地。

4.2.3若在无可靠的静电防护条件时,应手持电路板边缘部位,禁止用裸手触摸导体、焊接点及层压板表面。

4.2.4检验目视距离约30-40cm,必要时以放大镜等工具辅助确认。

4.2.5检验发现的不合格时应贴上不合格指示标签,同时单独存放于不合格品区或框内。

4.2.6返修或返工PCBA时应将原不合格指示标签贴回原处,以便品质重点核查。

4.2.7返修或返工后的产品应按正常程序报检,检验除原不合格处重点检查外,其余也需按正常流程作全面检验。

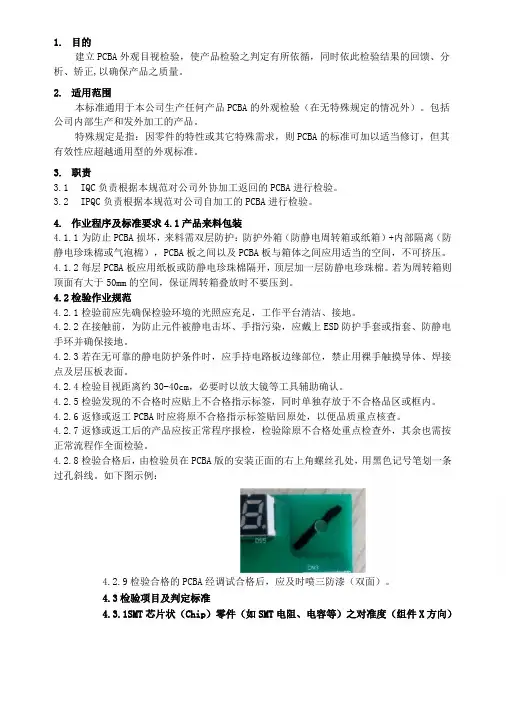

4.2.8检验合格后,由检验员在PCBA版的安装正面的右上角螺丝孔处,用黑色记号笔划一条过孔斜线。

如下图示例:4.2.9检验合格的PCBA经调试合格后,应及时喷三防漆(双面)。

PCBA外观检验规范1 目的建立PCBA外观检验规范,为工艺编制、生产加工、产品检验提供依据,保证产品的品质。

2 适用范围2.1本规范适用于本公司生产任何产品的外观检验(客户有特殊规定的情况除外)。

2.2特殊规定是指:因元件的特性,或其它特殊需求,《PCBA外观检验规范》可适当做修订。

3 定义3.1标准定义3.1.1允收标准 (Accept Criterion):允收标准包括理想状况、允收状况、拒收状况三种状况。

3.1.2理想状况 (Target Condition):接近理想与完美的组装情形。

具有良好组装可靠度。

3.1.3允收状况 (Accept Condition):是指组件不必完美,但要在使用环境下保持完整性和可靠度的特性。

3.1.4拒收状况 (Reject Condition):是指组件在其最终使用环境下不足以确保外形、装配和功能的情况。

3.2缺陷定义3.2.1严重缺陷 (Critical Defect):指缺陷会使人体或机器产生伤害,或危及生命财产安全的缺陷,称为严重缺陷,用CR表示。

3.2.2主要缺陷 (Major Defect):指缺陷在产品的功能上已失去实用性或造成可靠度降低,产品损坏、功能不良称为主要缺陷,用MA表示。

3.2.3次要缺陷 (Minor Defect):指个别此类缺陷的存在,实质上并无降低其实用性,且仍能达到所期望目的,一般为外观或机构组装上的差异,用MI表示。

3.3本规范若与其它规定文件相冲突时,依据顺序如下3.3.1客户所提供的或内部制定的工艺文件,作业指导书,特殊要求等。

3.3.2本规范。

3.3.3若有外观标准争议时,由质量部与技术部共同核判是否允收。

3.4检验方式操作人员做好自检、互检,在线QC做100%检验,QA按照《GB/T2828.1 -2003一次抽样方案》中II级水平进行抽样检验(AQL:MA 0.4,MI 1.0), 当检验结果持续变好或变差时,依附件一对产品实行加严检验或放宽检 验。

pcba外观检验标准PCBA外观检验标准。

PCBA(Printed Circuit Board Assembly)是印刷电路板组装的简称,是电子产品中不可或缺的一部分。

在PCBA生产过程中,外观检验是非常重要的环节,它直接关系到产品的质量和可靠性。

因此,建立一套科学、合理的PCBA外观检验标准对于保证产品质量具有重要意义。

首先,PCBA外观检验标准应包括以下几个方面:1.焊接质量,焊接是PCBA组装中最为关键的环节之一,焊接质量直接关系到产品的可靠性。

在外观检验中,应该检查焊接点的光洁度、焊接渣的情况、焊接点的位置和形状是否符合要求等。

2.元器件安装,元器件的安装质量直接关系到PCBA的性能稳定性。

在外观检验中,应该检查元器件的安装位置、方向、间距、高度等是否符合要求,同时还要检查元器件的外观是否完整,表面是否有损坏。

3.印刷电路板,印刷电路板作为PCBA的基础,其外观质量也至关重要。

在外观检验中,应该检查印刷电路板的表面是否平整,有无划伤、氧化、变形等情况,同时还要检查线路的连接是否良好、有无短路、断路等情况。

其次,建立PCBA外观检验标准的目的主要有以下几点:1.保证产品质量,通过建立科学的外观检验标准,可以有效地保证PCBA产品的质量,减少因外观缺陷而导致的性能问题和故障率。

2.提高生产效率,有了明确的外观检验标准,可以使检验工作更加规范化和标准化,提高检验效率,减少不必要的人为因素对产品质量的影响。

3.降低成本,通过外观检验,可以及时发现和处理产品的外观缺陷,避免将缺陷产品流入下道工序,减少了因外观缺陷而导致的报废和返工,从而降低了生产成本。

最后,建立一套科学、合理的PCBA外观检验标准需要注意以下几点:1.结合实际情况,在建立外观检验标准时,需要结合具体的产品特点和生产工艺,制定出符合实际情况的标准,避免过于理想化或不切实际。

2.不断改进,外观检验标准并非一成不变的,随着技术的不断发展和产品的不断更新,外观检验标准也需要不断改进和完善,以适应新的产品和新的生产工艺。

1. 目的:为使生产、检验过程中有依据可循,特制订本检验规范。

2. 定义2.1 CR——严重缺陷单位产品的极严重质量特性不符合规定或者单位产品的质量特性极严重不符合规定。

2.1.1可靠性能达不到要求。

2.1.2对人身及财产可能带来危害,或不符合法规规定.2.1.3极严重的外观不合格(降低产品等级,影响产品价格)。

2.1.4与客户要求完全不一致.2.2 MA——主要缺陷单位产品的严重质量特性不符合规定或者单位产品的质量特性严重不符合规定。

2.2.1产品性能降低。

2.2.2产品外观严重不合格。

2.2.3功能达不到规定要求。

2.2.4客户难于接受的其它缺陷。

2.3 Ml——次要缺陷单位产品的一般质量特性不符合规定或者单位产品的质量特性轻微不符合规定。

2.3.1轻微的外观不合格。

2.3.2不影响客户接受的其它缺陷。

2.4短路和断路:2.4.1. 短路:是指两个独立的相邻的焊点之间,在焊锡之后形成接合,造成不应导通而导通的结果2.4.2. 断路:线路该导通而未导通2.5沾锡情况:2.5.1. 良好沾锡:0 ° <接触角W 60° (接触角:焊锡与金属面所成的角度),焊锡均匀扩散,焊点形成良好的轮廓且光亮.要形成良好的焊锡,应有清洁的焊接表面,正确的锡丝和适当的加热.按焊锡在金属面上的扩散情况可分为全扩散(0 ° <接触角W 30° )和半扩散(30 ° <接触角W 60° ).如图:2.5.2 不良沾锡:60° <接触角<180° ,焊锡熔化后形成不均匀的锡膜覆盖在金属表面上,而未紧贴其上•形成不良沾锡的可能原因有:不良的操作方法,加热或加锡不均匀,表面有油污,助焊剂未达到引导扩散的效果等等•按焊锡在金属面上的扩散情况,可分为劣扩散(60 ° <接触角W 90° )和无扩散(90 ° <接触角<180° ).如图所示:2.5.3不沾锡:焊锡熔化后,瞬间沾附于金属表面,随后溜走•不沾锡的可能原因有:焊接表面被严重玷污,加热不足、焊锡由烙铁头流下,烙铁太热破坏了焊锡结构或使焊锡表面氧化部品分类:按部品的外观形状,将SMT 实装部品分为:2.6.有引脚产品2.6.1. 异形引脚电极:引脚从部品本体伸出,弯曲后向外侧凸出•如:QFP、SOP等.2.6.2. 平面引脚电极:引脚从部品下面平直伸出.如:连接器、晶体管等.2.6.3. 内曲引脚电极:引脚从部品侧面伸出,向内伸卷曲.如钽质电感、J形部品等.2.7无引脚部品.2.7.1. 晶体电极:部品两端面被镀成电极.如电阻、电容、电感等.2.8良好焊点:2.8.1. 要求:2.8.1.1. 结合性好:光泽好且表面呈凹形曲线.2.8.1.2. 导电性佳:不在焊点处形成高电阻(不在凝固前移动零件),不造成短路、断路.2.8.1.3. 散热性好:扩散均匀,全扩散.2.8.1.4. 易于检验: 焊锡不得太多, 务必使零件轮廓清晰可判.2.8.1.5. 易于修理: 勿使零件重叠实装.2.8.1.6. 不伤及零件: 烫伤零件或加热过久(常伴随有松香焦化), 会损及零件寿命.2.8.2. 现象:2.8.2.1. 所有表面沾锡良好.2.8.2.2. 焊锡外观光亮且成凹形圆滑曲线.2.8.2.3. 所有零件轮廓清晰可见.2.8.2.4. 若有松香锡球残留, 则须作清洁而不焦化.2.8.3. 形成条件:2.8.3.1. 正确的操作程序:手工作业时, 应注意烙铁、焊锡丝的收放次序及位置.2.8.3.2. 应保持两焊锡面清洁.2.8.3.3. 应使用规定的锡丝并注意使用量.2.8.3.4. 正确使用焊锡器具并按时保养.2.8.3.5. 应掌握正确的焊锡时间.2.8.3.6. 手工作业时,应注意冷却前不可移动被焊物, 以免造成焊点结晶不良,导致高电阻.3. 检验内容:3.1. 基板外观检查标准:3.1.1. 在任一方向,基板弯曲变形量:每100mm不可超过0.75mm.3.1.2. 基板不可出现分层、气泡、裂痕及凹陷现象.如有分层,只允许距离铜箔1mm以上开始轻微分离,不允许从铜箔下开始分离; 如有轻微凹陷, 则应小于线路厚度的30%.3.1.3. 经过焊锡后,允许保护漆起皱,但不可以脱落.3.1.4. 基板线路不可因铜氧化而发黑; 基板上铜箔氧化不可.3.1.5. 非导线区域内的保护漆最多可脱落5点,每一点的面积都必须在0.5mm以内,各点相距须在0.25mm 以上且距离导线0.25mm以上.3.1.6. 零件符号、印字不可印在焊点上.3.1.7. 基板上不可有油墨残渣、油污或其它异物.3.1.8. 基板不可因过热烧焦而变色; 基板上不可有铜箔浮起.3.1.9. 基板上的锡渣或锡球不可造成任何短路, 且外径小于0.3mm. 焊接的部品上不可残留锡渣或锡球.4. 不良图标SMT部分4.1零件贴装位置图标图示说明1、鸥翼形引脚理想状况1、弓I线脚在板子焊垫的轮廓内且没有突出现象。

文件批准Approval Record文件修订记录Revision Record:1、目的Purpose:建立PCBA外观检验标准,为生产过程的作业以及产品质量保证提供指导。

2、适用范围Scope:2.1本标准通用于本公司生产任何产品PCBA的外观检验(在无特殊规定的情况外)。

包括公司内部生产和发外加工的产品。

2.2 特殊规定是指:因零件的特性,或其它特殊需求,PCBA的标准可加以适当修订,其有效性应超越通用型的外观标准。

3、定义Definition:3.1标准【允收标准】 (Accept Criterion):允收标准为包括理想状况、允收状况、拒收状况等三种状况。

【理想状况】 (Target Condition):此组装情形接近理想与完美的组装结果。

能有良好组装可靠度,判定为理想状况。

【允收状况】 (Accept Condition):此组装情形未符合接近理想状况,但能维持组装可靠度故视为合格状况,判定为允收状况。

【拒收状况】(Reject Condition):此组装情形未能符合标准,其有可能影响产品的功能性,但基于外观因素以维持本公司产品的竞争力,判定为拒收状况。

3.2 缺陷定义【致命缺陷】(Critical Defect):指缺陷足以造成人体或机器产生伤害,或危及生命财产安全的缺陷,称为致命缺陷,以CR表示的。

【主要缺陷】(Major Defect):指缺陷对制品的实质功能上已失去实用性或造成可靠度降低,产品损坏、功能不良称为主要缺陷,以MA表示的。

【次要缺陷】(Minor Defect):系指单位缺陷的使用性能,实质上并无降低其实用性,且仍能达到所期望目的,一般为外观或机构组装上的差异,以MI表示的。

3.3焊锡性名词解释与定义:【沾锡】(Wetting) :系焊锡沾覆于被焊物表面,沾锡角愈小系表示焊锡性愈良好。

【沾锡角】 (Wetting Angle) 被焊物表面与熔融焊锡相互接触的各接线所包围的角度(如附件),一般为液体表面与其它被焊体或液体的界面,此角度愈小代表焊锡性愈好。

PCBA外观检验标准1. 引言PCBA〔Printed Circuit Board Assembly〕是指印刷电路板组装,也是电子产品的核心组成局部之一。

外观检验是在PCBA生产过程中的一项重要环节,旨在确保PCBA外观的质量和一致性。

本文将介绍PCBA外观检验的标准,包括检验准备、检验要求以及相关检验方法。

2. 检验准备在进行PCBA外观检验之前,需要做一些准备工作,以确保检验的准确性和可靠性。

2.1 检验设备 - 放大镜:用于观察细小的PCBA外观缺陷。

- 光源:提供充足的照明条件,以确保PCBA外表的缺陷能够清晰可见。

- 直尺和量具:用于测量PCBA的尺寸和间距。

- 存储介质:用于记录PCBA 外观检验结果。

2.2 检验环境 - 清洁桌面:确保检验过程中PCBA不会受到杂质和灰尘的干扰。

- 静电防护措施:防止静电对PCBA产生的损害,例如使用防静电手套和地垫。

3. 检验要求PCBA外观检验的要求包括以下几个方面:3.1 焊接质量 - 焊盘:焊盘应平整,无明显凹陷、松动或露锡现象。

- 焊接引脚:焊接引脚应完整,无断裂、错位或残留焊渣。

- 过度焊接:应防止过度焊接现象,如焊渣过多或焊盘间有短路。

3.2 容积件安装 - 元件位置:元件应正确安装在指定位置,无明显偏移或倾斜。

- 烧焊现象:不得出现烧焊、烧损或烧痕。

- 元件损坏:元件外表不得有明显刮痕、裂纹或破损。

3.3 插件安装 - 插件位置:插件应正确安装在插座或插槽中,无明显松动或倾斜。

- 插件卡塞:插件的引脚应顺利插入插座或插槽中,不得有卡塞情况。

3.4 标识和打码 - 标识清晰:PCBA上的标识应清晰可辨,不得有模糊、偏斜或褪色现象。

- 打码准确:PCBA上的打码应准确无误,不得有错位、缺漏或重复打码。

4. 检验方法PCBA外观检验可以采用目视检查和工具辅助检测相结合的方式。

4.1 目视检查通过目视观察PCBA的外观进行初步检查,包括焊盘、焊接引脚、元件安装、插件安装、标识和打码等方面。

pcba板检验及接收标准

PCBA板的检验及接收标准包括以下方面:

1.外观检查:检查PCBA板的尺寸精度、位置精度、表面处理以及

电气安全。

尺寸精度应符合设计要求,如孔径、线宽、线距等。

位置精度应准确,无偏差,如元件间距、焊盘位置等。

表面处理应符合要求,如是否有划痕、氧化、油污、裂纹、凹陷、变色、腐蚀等。

电气连接应可靠,无短路、开路现象。

2.允收条件:零件有损坏,但本体保持良好,内部金属组件无外露,

并且文字标示规格,极性可辨识。

IC虽有损坏,但无破裂现象。

IC脚与本体封装处没有破裂。

零件脚无损伤。

零件面吃锡以孔内填锡量达PCB板厚的75%以上。

焊点上的针孔大小小于零件脚截面积1/4,任一点之针孔都没有贯穿过PCB。

这些标准都是为了确保PCBA板的品质和性能,以保证其在实际使用中的稳定性和可靠性。

外观检验标准1.所有元件都需按工艺要求插件;2.极性元件方向正确;3.吸锡焊点饱满光亮;严重缺陷主要缺陷次要缺陷严重缺陷主要缺陷1缺件V 11透锡V2错件V 12透锡3反向V 13锡尖V4错孔V 14镙丝孔多锡V项次项次缺陷类别不良现象描述图片说明缺陷类别该插件的零件没有插件焊料透锡未超过50%缺陷类别不良现象描述图片说明缺陷类别未按工艺要求插上正确的元件(A)焊料透锡超过75%零件脚位插入相零其它元件孔内(B)螺丝孔上锡过多,焊料表面不平滑极性元件方向未按工艺要求摆放(C)长度超过1MM PCBA 外 观 检 验 标 准(插 件 元 件5多件V 15损件V6跪脚V 16损件V7空焊V 17损件8短路V 18元件脚跨导线V9虚焊V 19浮高V10少锡V 20浮高不应插件的位置插上元件元件破损、裂缝影响性能元件脚未插入元件孔,被压在元件底部元件破损明显,但未影响性能绝缘套管破裂未造成导体间短路(A),引线跨越导体高度未超过0.5mm,未加绝缘套管(B)焊料润湿为焊盘大小的60%~80%水平安装元件本体与板面高度在0.5~1mm之间焊点外观良好,但未与焊盘连接在一起元件及焊盘无焊料填充元件破损轻微,不影响性能水平安装元件本体与板面高度超过1MM焊点或元件脚之间不应导通而导通注:参考文件《IPC-A-610E-2010 中文版 电子组件的可接受性》Good is not enough,each product must be perfect! 好是不够的,术语定义:缺陷: 指组件在其最终使用环境下影响了外形、装配和功能的现象。

致命缺陷:指缺陷足以造成人体或机器产生伤害或危及生命财产安全的缺陷;主要缺陷:指缺陷对制品的实质功能上已失去实用性或造成可靠度降低,产品损坏、功能不良;次要缺陷:指单位缺陷的使用性能,实质上并无降低其实用性 ,且仍能达到所期望目的;次要缺陷严重缺陷主要缺陷次要缺陷21浮高V22倾斜V23连接器倾斜V24连接器倾斜V垂直安装元件,本体距板面超过1.5MM缺陷类别不良现象描述图片说明缺陷类别类别项次角度超过20°角度超过20°,影响脚的焊接角度在10~20°之间,不影响脚的焊接;但不出元件脚元 件 面)25IC倾斜V26脚长VV 27脚长V 28脏污V29脏污VV30PCB涂层起泡烧伤V 角度在5~10°之间;不影响脚的焊接,有出脚距在0.8MM以上L脚长超过1.0MM板面助焊剂残留或其它脏污呈黄色或黑色,严重影响外观面积超过1~2平方毫米(注:没有铜铂)L脚长超过2.5MM板面有助焊剂残留或其它脏污,但面积较小呈透明状,外观影响轻微够的,每个产品必须完美!。

汽车产品pcba外观检验标准

汽车产品PCBA外观检验标准应包括以下方面:

1.外观整体:PCBA应呈现平整、光滑、干净的外观,不能有划痕、凹凸、灰尘等问题。

2.引脚排列:引脚排列应整齐、对称,不能存在错位、偏移等问题。

3.焊点质量:PCBA上的焊点应呈现导电性良好、焊接均匀、无异常缺陷(如裂纹、气孔、虚焊等)等情况。

4.标识清晰:PCBA上的标识(如组件名、编号、生产日期等)应清晰、规范,不能存在漏打、损坏等问题。

5.器件尺寸:各类器件(如电容、电阻、芯片、插件等)的尺寸应符合相关规范,不能存在配合过紧或过松等问题。

6.器件摆放:各类器件的摆放应符合相关要求(如间距、平整度、过孔等),不能存在摆放偏斜、垂直度差等问题。

7.打样样品与设计图纸的一致性:PCBA打样样品应与设计图纸完全一致,无任何偏差或变形。

8.其它特殊要求:根据具体情况(如防爆、防水、耐高温等要求),可增加相关检验项。

总体来说,汽车产品PCBA的外观检验应全面细致,确保产品质量和安全性。

pcba出货检验标准PCBA出货检验标准。

PCBA(Printed Circuit Board Assembly)是指印刷电路板组装,是电子产品的核心部件之一。

在PCBA生产过程中,出货检验是非常重要的环节,它直接关系到产品的质量和性能。

因此,建立科学、合理的PCBA出货检验标准对于保障产品质量具有重要意义。

一、外观检查。

1.1 外观检查是PCBA出货检验的首要步骤,包括检查焊接质量、元器件安装质量、PCB板表面状态等。

焊接质量应该均匀、光滑,无明显的焊接飞溅和虚焊现象;元器件应该安装牢固,无偏位、漏装等现象;PCB板表面应该整洁、无划痕、氧化等现象。

1.2 外观检查还需要关注PCBA的标识和标签,包括产品型号、生产日期、批次号等信息是否清晰、完整。

二、功能检测。

2.1 功能检测是PCBA出货检验的关键环节,通过对PCBA进行电气测试,验证其各项功能是否正常。

包括通电测试、信号测试、通讯测试等。

2.2 在进行功能检测时,需要根据产品的具体要求,制定相应的测试方案和测试标准。

并严格按照标准进行测试,确保产品的性能符合要求。

三、环境适应性测试。

3.1 为了验证PCBA在不同环境条件下的稳定性和可靠性,需要进行环境适应性测试。

包括高温试验、低温试验、湿热试验等。

3.2 环境适应性测试可以有效评估PCBA在极端环境下的工作状态,对于保障产品的可靠性具有重要意义。

四、包装检查。

4.1 包装检查是PCBA出货检验的最后一道工序,主要检查产品的包装是否完好、标识是否清晰、防静电措施是否到位等。

4.2 合格的包装可以有效保护PCBA免受运输过程中的损坏,确保产品在出货后的安全到达客户手中。

总结:PCBA出货检验标准的建立和执行,对于保障产品质量、提高客户满意度具有重要意义。

只有严格执行出货检验标准,确保产品的每一个环节都符合要求,才能生产出高质量的PCBA产品,赢得客户的信赖和支持。

因此,我们每一个PCBA 出货检验人员都应该严格按照标准操作,不放过任何一个细节,为客户提供最优质的产品和服务。

pcba检验标准PCBA(Printed Circuit Board Assembly)是指将已经完成印制电路板(PCB)上贴有电子元器件的组装过程。

在PCBA生产过程中,为了保证产品质量和可靠性,需要进行各种检验。

本文将介绍PCBA的常见检验标准及其内容要求。

一、外观检验外观检验主要通过目视观察和使用显微镜等设备来检查PCBA的外观表面。

外观检验的标准包括:1.焊接质量:焊接点是否完整、焊接是否有虚焊、漏焊、锡球、破损等情况。

2.元器件安装质量:元器件是否平整、正立、定位准确、引脚对称等。

3.印刷错误:印刷电路板上的标识、文字、图形是否正确、清晰。

二、电气性能检验电气性能检验是通过使用电气测试设备来评估PCBA的电气特性。

电气性能检验的标准包括:1.引脚连通性:检查PCBA上各元器件引脚的连通性是否良好,避免开路或短路等问题。

2.电压测试:在给定电源电压下,检查PCBA上各电路的电压是否正常,避免电压偏离范围。

3.信号测试:检查PCBA上各信号线路的传输是否正常,避免信号干扰或失真。

三、功能性检验功能性检验是通过应用场景或特定工作负载来评估PCBA的功能和性能。

功能性检验的标准包括:1.开机测试:检查PCBA在通电的情况下是否能够正常启动和运行。

2.通信测试:测试PCBA上的通信接口是否能够正常连接和传输数据。

3.特定工作负载测试:对特定功能模块或处理器进行负载测试,如处理器性能、温度等。

四、环境可靠性检验环境可靠性检验是通过将PCBA置于不同的环境条件下进行测试,以评估其在不同环境下的可靠性和稳定性。

环境可靠性检验的标准包括:1.温度循环测试:将PCBA放置在不同温度下进行循环测试,以模拟实际工作环境中的温度变化。

2.湿度测试:将PCBA放置在高湿度环境下进行测试,以评估其抗潮湿性能。

3.振动和冲击测试:对PCBA进行振动和冲击测试,以评估其抗震性能。

五、安全性检验安全性检验是评估PCBA在使用过程中的电气、机械和环境安全性能。

PCBA外观检验标准_完整PCBA是电子产品中十分重要的零部件之一,它也是电子产品中的大脑,其质量直接影响到整个电子产品的稳定性和功能性。

PCBA外观的好坏,不仅直接影响消费者对产品的认可度和品牌忠诚度,同时也是评价电子厂商技术水平和态度的重要标准。

一、PCBA的外观检验标准1.焊盘:通过观察焊盘是否整齐,在表面是否有明显氧化或损伤,是否有拼焊、漏焊、棱焊等现象来判断焊盘的质量。

2.元器件位置:不同元器件在不同区域的位置要求不同,位置不准确的元器件会影响到整个电路的通断。

通过外观检查,可以判断元器件的位置是否准确,是否与设计相符。

3.元器件旁的夹具:元器件旁通常会有夹具,用作固定元器件呈现统一的姿态,外观检验时应判断夹具的大小、颜色和夹紧力度是否与设计文档相符。

4.自动贴装的质量:在现今的工厂中,大量的PCBA要使用自动化贴装技术,自动贴装的PCBA质量好坏影响较大。

外观检查时,应判断自动贴装元器件的间距、排列情况、元器件是否倾斜以及是否拼装在错误的位置。

5.清晰度:检查PCBA时,应该是清晰明确的,看是否是完整的。

如果是人工焊制的PCBA板,需要检查捆绑是否整齐,焊点是否精细,清晰度和一致性是否符合要求。

6.元器件的表面质量:判断元器件表面是否有污垢或污迹,如发现元器件表面有污迹,则需要进一步查明污迹来源,并采取必要步骤处理。

7.钝化子:如果PCBA板使用了钝化剂,检查电路板上的钝化子是不是均匀的,颜色是否相近,是否符合设计要求。

8.印刷标签:印刷标签是PCBA中一个重要的信息来源,内容是组装电路板的相关信息。

外观检查时,应注意检查印刷标签是否缺失、完整,字体大小和颜色是否清晰,是否与设计要求一致。

二、PCBA质量影响1.元器件焊接质量:PCBA焊接质量直接影响到整个产品的可靠性和性能。

如果PCBA焊接不良,将会导致整个产品在使用过程中频繁出现故障,严重的甚至会影响到产品使用安全。

2.元器件的插座质量:如果PCBA板的插座质量不理想,容易出现卡插、松动、焦糊等现象。

PCBA成品出厂检验标准引言PCBA(Printed Circuit Board Assembly)是指将元器件焊接到印刷电路板上,完成电路板的组装过程。

为确保产品质量,PCBA成品出厂前需要进行严格的检验。

本文档旨在制定PCBA成品出厂检验标准,以确保产品质量达到客户要求和行业标准。

1. 检验对象PCBA成品出厂检验的对象为已完成组装并通过功能测试的PCBA 产品。

2. 检验内容PCBA成品出厂检验的内容包括以下几个方面:2.1 外观检验外观检验主要包括以下几个方面的检查:•PCB板表面是否有破损、变形等现象;•元器件是否完好无损、焊接是否牢固;•是否存在电路短路、焊接错误等问题;•颜色、印刷是否符合要求;•表面涂层是否均匀、无划痕。

2.2 功能检验功能检验是通过对PCBA产品进行各项功能测试,验证产品的功能是否正常。

功能检验需要根据产品的设计要求和相关标准制定相应的测试方案和测试步骤。

2.3 电性能检验电性能检验主要包括以下几个方面:•电压测试:根据设计要求和标准,对PCBA产品进行电压测试,确保电压值在允许范围内;•电流测试:根据设计要求和标准,对PCBA产品进行电流测试,确保电流值在允许范围内;•电阻测试:根据设计要求和标准,对PCBA产品的电阻进行测试,确保电阻值在允许范围内;•纹波测试:根据设计要求和标准,对PCBA产品的纹波进行测试,确保纹波值在允许范围内。

3. 检验方法PCBA成品出厂检验的方法主要包括以下几个方面:3.1 外观检验方法外观检验方法主要包括目视检查、使用显微镜进行观察等。

3.2 功能检验方法功能检验方法需要根据产品的功能要求制定相应的测试方案和测试步骤。

测试方法可以包括使用测试仪器进行测试、手动操作等。

3.3 电性能检验方法电性能检验方法需要使用相应的测试仪器进行测试,根据设计要求和标准制定测试方案和测试步骤。

4. 检验标准PCBA成品出厂的检验标准应与设计要求和行业标准相一致。

1.0. 目的:

5.1.13 缺件:应该装的元件而未装上;

5.1.14 多件:PCB上元件比BOM表单上备注的元件多,即多出了元件在PCB板上;

5.1.15 损件:元件有裂痕或缺失等损伤;

5.1.16 错件:装错非BOM表单内备注的元件;

5.1.17 极性反:有极性的元件被放置颠倒;

5.1.18 多锡:引脚折弯处的焊锡接触组件体或密封端,或焊锡覆盖了插件引脚使其未露出,

或影响组装;

5.1.19 少锡:贴片引脚处焊锡不足或插件孔内填充焊锡不足;

5.1.20 拉尖:元器件引脚头部有焊锡拉出呈尖形;

5.1.21 最小电气间隙:不绝缘的非公共导体之间的最小间距,任何违反最小电气间隙的状况

均为缺陷;

5.1.22 灯面:贴装或插件LED元件一面,也称为主面;

5.1.23 驱动面:装有芯片IC及连接器的一面,也称为辅面或焊接面;

5.2 理想焊点概述:

5.2.1 在焊锡面上出现的焊点应为实心平顶的的凹锥体,焊锡在被连接部位上形成羽毛状边

缘,剖面图的两外缘应呈现新月型的均勻弧状凹面,通孔中的填锡应将零件脚均勻且

完整地包裹住;

5.2.2 锡量的多少应以填满焊垫边缘及零件脚为宜,沾锡角越小越好,表示有良好的焊锡性;

5.2.3 锡面应呈现光泽(除非受到其他因素的影响,如沾到化学品等会使之失去光泽);其表

面应平滑、均勻且不可存有任何不規則現象如小缺口、起泡、异物或有凸点等状况;

5.2.4 对贯穿孔的焊锡,应自焊锡面爬进孔中且要升至零件面;在焊锡面的焊锡应平滑,良

好的焊錫性,应有光亮的锡面与接近零度的沾锡角。

6.0.检验前准备:

6.1检验条件:室內照明 500~800LUX,必要时以(五倍以上)放大镜检验确认;

6.2 ESD防护:凡接触PCBA半成品必須佩戴良好的防静电手环及防静电手套;

6.3 检验前需先确认所使用工作台无杂物,避免脏污或损伤PCBA;

6.4 PCB板半成品的握法:配带静电手套、静电手环,握持板边或板角来检验,如图:

7.0.外观标准:

7.1 SMT外观检验标准:

7.1.1 元件侧面偏移标准:

侧面偏移大于焊盘宽度或元件端子宽度的25%;IC引脚偏移符合此要求或小于0.5mm;

均取其中较小者;灯面LED需做到不偏移,以不影响LED一致性为最终标准;

缺陷图片

7.1.2 元件末端偏移标准:

1/2以上贴片末端长度需与焊盘重叠;元件引脚不能超出焊盘边缘;灯面LED需做到不偏移,以不影响LED一致性为最终标准;

缺陷图片

7.1.3 元件端子最大填充高度标准:

焊锡可以超出焊盘,或着延伸至端子顶部,但不可以与元件本体接触(塑封SOIC及SOT

元件本体除外);

缺陷图片可接收图片

7.1.4 元件端子最小填充高度标准:

焊锡高度需大于元件端子高度25%或者0.5MM,取两者中较小者;

缺陷图片目标图片

7.1.5 元件侧立:

元件侧立为缺陷;贴片侧立以下条件均满足可接收:

a)元件尺寸小于1206,宽度与高度比不超过2/1;

b)元件端子与焊盘之间100%重叠接触;

c)元件有3个或3个以上端面,且均有明显润湿。

缺陷图片可接收图片 7.1.6 元件翻白:

元件翻白为缺陷;

目标图片

缺陷图片

7.1.7 元件立碑:

元件立碑为缺陷,为断路的一种;

缺陷图片

7.1.8 元件连焊:

在不同线路上的焊盘被焊锡相连为缺陷,此判定同样适用于波峰后焊检验;

缺陷图片

7.1.9 焊接异常——锡球/锡渣残留

锡球/锡渣残留为缺陷;当锡球被助焊剂包裹或固定、直径小于0.13mm且不违反最小

电气间隙,可接收,此判定同样适用于波峰后焊检验;

缺陷图片

7.1.10 焊接异常—锡裂

锡裂现象为缺陷,此判定同样适用于波峰后焊检验;

缺陷图片

7.1.11 焊接异常—锡未融(锡膏再流不完全)

锡未融为缺陷;

缺陷图片

7.1.12 焊接异常—拒焊(焊料与焊盘或元件端子不润湿):

拒焊为缺陷;当符合其他所有标准时,可接收;此判定同样适用于波峰后焊检验;

缺陷图片

7.1.13 元件损伤—金属镀层缺失

元件任何端面的金属镀层缺失超过了元件宽度或厚度的25%均为缺陷;

缺陷图片

7.2 波峰后焊检验标准:

7.2.1 元件安放引脚成型弯曲标准:

不允许成直角弯曲引脚,需成圆弧弯曲,具体要求如下表格;

缺陷图片

7.2.2 元件引脚成型损伤标准:

元件引脚损伤均为制程警示状况,其中损伤小于引脚直径、宽度或厚度的10%允许接收;

超出此要求或引脚多次扭曲、严重压痕(锯齿状等)状态为缺陷;

制程警示图片缺陷图片

7.2.3 元件水平安放标准:

元件最少一边或一面接触PCB板面允许接收;

可接收图片缺陷图片

7.2.4 元件引脚伸出焊接面长度标准:

要求引脚伸出焊接面最大长度或高度小于2mm,最小长度在焊料中可识别出引脚末端;

引脚伸出焊接面最大长度或高度

小于2mm

缺陷图片

7.2.5 元件引脚折弯标准:

引脚末端平行板面,沿着焊盘相连的导线折弯;引脚沿着非公共导体折弯并违反最小

电气间隙判为缺陷;

目标图片缺陷图片

7.2.6 元件引脚垂直填充标准:

贯穿孔最少填充75%体积;

目标图片可接收图片

7.2.7 元件引脚在辅面与贯穿孔的焊接标准:

引线、孔壁和端子区域最少润湿330°,如图1所示;锡面焊盘区域最少需被润湿的

焊料覆盖75%,如图2所示:

图1 图2

7.2.8 多锡判定标准:

引脚处焊锡接触元件本体为缺陷(塑封SOIC及SOT 元件本体除外);多锡影响组装

或者违反最小电气间隙为缺陷,此判定同样适用于SMT外观检验;

缺陷图片

7.2.9 元件浮高、倾斜标准:

7.2.9.1 非连接性能插件:

元件底部平贴PCB板表面为目标,浮高或倾斜不大于1mm可接收;浮高或

影响组装

为缺陷

倾斜小于1mm 或影响组装为缺陷;

目标图片 可接收图片

7.2.9.2 连接器插件:

元件底部平贴PCB 板表面为目标,浮高或倾斜不大于0.5mm 可接收;浮高 或倾斜小于0.5mm 或影响组装为缺陷;

目标图片 可接收图片

7.2.9.3 铜柱机构件

元件底部平贴PCB 板表面为目标,浮高或倾斜不大于0.1mm 可接收;浮高 或倾斜大于0.1mm 为缺陷;

目标图片

7.2.9.4 LED 插件

不允许LED 插件倾斜或浮高,以不影响LED 一致性为最终标准;

浮高或倾斜大于0.1mm 为缺陷

LED 插件倾斜或浮高为缺陷

7.2.10 锡尖现象:

焊点端部有焊锡拉出呈尖形或违反最小电气间隙均为缺陷:

缺陷图片

7.2.11 锡裂现象:

锡裂现象为缺陷:

缺陷图片

7.3 清洁度标准:

7.3.1 颗粒状物质残留:

在PCBA 上存在污物、颗粒状物质、纤维和残渣等等均为制程警示;此类物质没有被 助焊剂等阻焊物包裹固定,或违法最小电气间隙为缺陷;

缺陷图片

7.3.2 氯化物、碳化物以及白色物残留

违反最小电气间隙均为缺陷

此类化学物残留均为缺陷;除已经通过鉴定并有文件记录其特性是良性的,则可以

接受;

缺陷图片

7.3.3 腐蚀现象;

清洁后表面转暗可接收;腐蚀现象为缺陷;

缺陷图片

7.4标记标准:

7.4.1 标记—蚀刻标准:

标记中字符缺失或模糊无法识别;

标记违反最小电气间距极限;

字符之内或字符/导体之间焊料桥接,妨碍了字符的识别;

字符缺线或断线,使字符不清楚,或很可能与其它字符混淆;

以上均为蚀刻标记缺陷;

缺陷图片

7.4.2 标记—丝印标准:

丝印上焊盘;

表示元件位置或元件外框的标记或参考标识缺失、模糊无法识别;

形成字符的笔画缺失或无法识别,或可能与其它字符相混淆;

以上均为丝印缺陷;

缺陷图片

7.4.3 标记——标签标识:

使用读码器试读两次均无法读出条形码;

标记缺失或模糊不清;

标签翘起面积大于整体面积的10%;

以上均为缺陷;

缺陷图片

缺陷图片

8.0.注意事项:

8.1 以上所有标准均来源于IPC-A-610E,未详尽项可查询此标准参考;

8.2 客户要求优先于此标准;按此标准影响组装时,优先按组装要求;图案说明与文字描述

不符时,按文字描述要求执行;

8.3 所有违反最小电气间隙状况,所有影响组装的状况,均为缺陷;

9.0. 附件:

9.1 回流焊后全检日报表

9.2 测试记录表

9.3电气间隙要求一览表:。