(完整版)13.DMA讲解

- 格式:ppt

- 大小:1.33 MB

- 文档页数:53

[基础知识]什么叫做DMA?DMA=Direct Memory Access。

这是一种通过硬件实现的数据传输机制。

简单的说,就是不在CPU的参与下完成数据的传输。

[/基础知识]不太明白?我举个简单的例子:比如有个数组a,我希望把这个数组中的内容传输到另一个数组b中。

我们假设这两个数组都是一样大。

比如int a[10000];int b[10000];。

那么我可以这样做:[code=c]for(int x=0;xb[x]=a[x];}[/code]循环将数组中的每个元素进行传递。

这是最简单的一种方法,也是最容易理解的方法。

不过这种方法虽然简单,效率可算不上高。

如果你了解微机原理和汇编的话就明白了,b[x]=a[x];这句话并非像你看到的那样,把a[x]中的元素值赋给b[x]。

那是怎么一个过程?实际上是这样的:首先a[x]中的元素值赋给某CPU中的寄存器,然后再将该寄存器的值赋给b[x]。

为什么会这样?这是因为a和b都是在内存中的,而CPU不允许内存直接进行数据传输。

所以在这个过程中CPU必须参一脚当中介。

可想而知每赋值一次都要中介,效率就这么被降下去了。

既然问题是出在CPU当中介这个地方,那么有什么方法可以回避掉这个瓶颈呢?有。

那就是DMA。

DMA是一种硬件设备。

这种设备的工作原理是这样的:——首先CPU告诉DMA设备,要有一堆数据需要传输,为了效率而请它出马。

(DMA请求)——DMA收到CPU的消息,开始准备。

此时CPU把数据源地址、数据目标地址、传输数据量、传输模式等等参数告诉它。

(DMA初始化)——DMA初始化完,向CPU发送消息“借你的总线用一用,我要开始传输数据了!”(总线出借,DMA启动)——CPU收到消息后,暂时切断自己与总线的联系。

DMA开始传输数据。

(DMA数据)——DMA传输完数据之后,向CPU发送消息“搞定了!总线还给你。

”(总线归还)——CPU说:“干得好!老将出马一个顶俩!辛苦了,你先歇着吧。

龙芯1B处理器用户手册2016年5月龙芯中科技术有限公司版权声明本文档版权归龙芯中科技术有限公司所有,并保留一切权利。

未经书面许可,任何公司和个人不得将此文档中的任何部分公开、转载或以其他方式散发给第三方。

否则,必将追究其法律责任。

免责声明本文档仅提供阶段性信息,所含内容可根据产品的实际情况随时更新,恕不另行通知。

如因文档使用不当造成的直接或间接损失,本公司不承担任何责任。

龙芯中科技术有限公司Loongson Technology Corporation Limited地址:北京市海淀区中关村环保科技示范园龙芯产业园2号楼Building No.2, Loongson Industrial Park, Zhongguancun Environmental Protection Park,电话(Tel):************传真(Fax):************阅读指南《龙芯1B处理器用户手册》主要介绍龙芯1B架构与寄存器描述。

修订历史文档更新记录文档编号:文档名:龙芯1B处理器用户手册版本号V2.3创建人:研发中心创建日期2016-5-4更新历史序号.更新日期更新人版本号更新内容12010-6-7 研发中心V1.0 1B处理器初稿完成22010-11-13 研发中心V1.1 增加了芯片引脚排布,DDR控制器信息等32010-11-15 研发中心V1.2 修改并进行标准排版42010-11-15 研发中心V1.3 修正了第五章DDR的部分错误52011-05-08 研发中心V1.4 修订了调试发现的错误62011-05-17 研发中心V1.5 修订了多个小问题72011-11-15 研发中心V1.6GMAC0/1的RGMII和MII模式需要配置才能使用GPIO配置和复用中修改bugSPI部分,分频时钟明确是DDR2_clk/2DDR2部分,配置16/32位可配置时钟分频部分有改动添加了LCD PAD在不同显示模式下的对应关系GPIO寄存器描述修改82012-4-11 研发中心V1.7 NAND部分寄存器说明修改XTALI/O 与外部有源晶振、无源晶体连接方法92012-4-20 研发中心V1.8 PAD封装位置和封装延迟GPIO复位值和方向GMAC0/1在MII模式下信号处理Wdog地址修改USB启动需要复位10 2012-05-26 研发中心V1.9 针对修改意见,做了GPIO/ LCD/ DMA/ SPI/ UART/I2C/ NAND /CLOCK的修改11 2014-07-30 研发中心V2.0 增加质量等级和封装顶视图12 2015-3-11 研发中心V2.1 增加电特性,CAN的速率计算13 2015-4-1 研发中心V2.2 补充质量等级描述14 2016-5-4 研发中心V2.3 24.1节增加RTC功耗说明,增加焊接要求手册信息反馈:*******************目录 (1)1概述 (1)1.1体系结构框图 (1)1.2芯片主要功能 (2)1.2.1GS232 CPU (2)1.2.2DDR2 (3)1.2.3LCD Controller (3)1.2.4USB2.0 (3)1.2.5AC97 (3)1.2.6GMAC (4)1.2.7SPI (4)1.2.8UART (4)1.2.9I2C (4)1.2.10PWM (4)1.2.11CAN (5)1.2.12RTC (5)1.2.13GPIO (5)1.2.14NAND (5)1.2.15INT controller (5)1.2.16Watchdog (5)1.2.17功耗 (5)1.2.18其它 (7)1.3质量等级 (7)2芯片引脚定义 (9)2.11B引脚分布图 (9)2.2封装顶视图 (16)2.3系统相关引脚定义(6) (17)2.4LCD引脚定义(20) (17)2.5PLL引脚定义(4) (17)2.6VR引脚定义(6) (18)2.7DDR2引脚定义(71) (18)2.8USB引脚定义(10) (19)2.9EJTAG引脚定义(6) (20)2.10GMAC0引脚定义(15) (20)2.11GMAC1引脚定义(4) (20)2.12AC97引脚定义(5) (21)2.13SPI引脚定义(7) (21)2.14UART引脚定义(20) (21)2.15I2C引脚定义(2) (22)2.16CAN引脚定义(4) (22)2.17NAND引脚定义(14) (22)2.18PWM引脚定义(4) (22)2.19电源/地引脚(58) (23)3地址空间分配 (24)3.1一级AXI交叉开关上模块的地址空间 (24)3.2AXI MUX下各模块的地址空间 (24)3.3APB各模块的地址空间分配 (24)4CPU (26)4.1MIPS32指令系统结构 (26)4.1.1CPU寄存器 (27)4.1.2CPU指令集 (27)4.1.3CP0指令集 (31)4.1.4存储空间 (32)4.1.5例外处理 (33)4.1.6CP0寄存器 (35)4.2CP0指令 (53)4.3EJTAG设计 (53)4.3.1EJTAG介绍 (53)4.3.2调试控制寄存器(Debug Control Register) (54)4.3.3硬件断点 (56)4.3.4EJTAG相关的处理器核扩展 (61)4.3.5TAP接口 (64)5DDR2 (72)5.1DDR2SDRAM控制器特性 (72)5.2DDR2SDRAM读协议 (72)5.3DDR2SDRAM写协议 (73)5.4DDR2SDRAM参数设置顺序 (73)5.5DDR2SDRAM采样模式配置 (74)5.6DDR2SDRAM PAD驱动配置 (74)5.7DDR216位工作模式配置 (74)6LCD (75)6.1特性 (75)6.1.1数据格式 (75)6.2寄存器 (75)7GMAC0 (81)7.1配置成MAC的连接和复用方式 (81)7.2DMA寄存器描述 (81)7.3GMAC控制器寄存器描述 (90)7.4DMA描述符 (101)7.4.1DMA描述符的基本格式 (101)7.4.2DMA接收描述符 (102)7.4.3RDES0 (103)7.4.4RDES (104)7.4.5RDES2 (105)7.4.6RDES3 (105)7.4.7DMA发送描述符 (106)7.4.8TDES0 (106)7.4.9TDES1 (107)7.4.10TDES2 (109)7.4.11TDES3 (109)7.5软件编程向导(S OFTWARE P ROGRAMMING G UIDE): (110)8GMAC1 (112)8.1配置成MAC的连接和复用方式 (112)8.2GMAC1外部信号复用和配置 (112)8.3寄存器描述 (113)9USB HOST (114)9.1总体概述 (114)9.2USB主机控制器寄存器 (115)9.2.1EHCI相关寄存器 (115)9.2.2Capability寄存器 (115)9.2.3Operational寄存器 (116)9.2.4EHCI 实现相关寄存器 (116)INSNREG00寄存器(disable) (117)INSNREG01寄存器 (117)INSNREG02寄存器 (117)INSNREG03寄存器 (117)INSNRE04寄存器(仅用于调试,软件不必更改此寄存器) (117)INSNRE05寄存器 (118)INSNREG06寄存器 (118)INSNREG07寄存器 (118)INSNREG08寄存器 (118)9.3OHCI相关寄存器 (119)9.3.1Operational寄存器 (119)9.3.2OHCI 实现相关寄存器 (119)INSNREG06寄存器 (120)INSNREG07寄存器 (120)9.4USB主机控制器时序 (120)9.4.1数据接收时序 (120)9.4.2数据传输时序 (121)10SPI0 (123)10.1SPI控制器结构 (123)10.2SPI控制器寄存器 (124)10.2.1控制寄存器(SPCR) (124)10.2.2状态寄存器(SPSR) (124)10.2.3数据寄存器(TxFIFO/RxFIFO) (125)10.2.4外部寄存器(SPER) (125)10.2.5参数控制寄存器(SFC_PARAM) (125)10.2.6片选控制寄存器(SFC_SOFTCS) (126)10.2.7时序控制寄存器(SFC_TIMING) (126)10.3接口时序 (126)SPI主控制器外部接口时序图 (126)SPI Flash访问时序图 (127)10.4SPI F LASH控制器使用指南 (128)SPI主控制器的读写操作 (128)硬件SPI Flash读 (128)混合访问SPI Flash和SPI主控制器 (129)11SPI1 (130)11.1SPI主控制器结构 (130)12Conf and Interrupt (131)12.1配置和中断控制器总体描述 (131)12.2中断控制器寄存器描述 (132)13DMA (134)13.1DMA控制器结构描述 (134)13.2DMA控制器与APB设备的交互 (134)13.3DMA控制器 (134)13.3.1ORDER_ADDR_IN (134)13.3.2DMA_ORDER_ADDR (135)13.3.3DMA_SADDR (135)13.3.4DMA_DADDR (136)13.3.5DMA_LENGTH (136)13.3.6DMA_STEP_LENGTH (136)13.3.7DMA_STEP_TIMES (137)13.3.8DMA_CMD (137)14UART (139)14.1UART控制器结构 (139)14.2UART控制器寄存器 (140)14.2.1数据寄存器(DAT) (141)14.2.2中断使能寄存器(IER) (141)14.2.3中断标识寄存器(IIR) (141)14.2.4FIFO控制寄存器(FCR) (142)14.2.5线路控制寄存器(LCR) (142)14.2.6MODEM控制寄存器(MCR) (143)14.2.7线路状态寄存器(LSR) (143)14.2.8MODEM状态寄存器(MSR) (144)14.2.9分频锁存器 (144)15CAN (146)15.1概述 (146)15.2CAN控制器结构 (146)15.3标准模式 (147)15.3.1标准模式地址表 (147)15.3.2控制寄存器(CR) (148)15.3.3命令寄存器(CMR) (149)15.3.4状态寄存器(SR) (149)15.3.5中断寄存器(IR) (149)15.3.6验收代码寄存器(ACR) (150)15.3.7验收屏蔽寄存器(AMR) (150)15.3.8发送缓冲区列表 (150)15.3.9接收缓冲区列表 (150)15.4扩展模式 (151)15.4.1扩展模式地址表 (151)15.4.2模式寄存器(MOD) (151)15.4.3命令寄存器(CMR) (152)15.4.4状态寄存器(SR) (152)15.4.5中断寄存器(IR) (152)15.4.6中断使能寄存器(IER) (153)15.4.7仲裁丢失捕捉寄存器(IER) (153)15.4.8错误警报限制寄存器(EMLR) (154)15.4.9RX错误计数寄存器(RXERR) (155)15.4.10TX错误计数寄存器(TXERR) (155)15.4.11验收滤波器 (155)15.4.12RX信息计数寄存器(RMCR) (155)15.5公共寄存器 (155)15.5.1总线定时寄存器0(BTR0) (155)15.5.2总线定时寄存器1(BTR1) (156)15.5.3输出控制寄存器(OCR) (156)16AC97 (157)16.1AC97结构描述 (157)16.2AC97控制器寄存器 (157)16.2.1CSR寄存器 (158)16.2.2OCC寄存器 (158)16.2.3ICC寄存器 (158)16.2.4(输入输出)通道寄存器配置 (159)16.2.5Codec寄存器访问命令 (159)16.2.6中断状态寄存器/中断掩膜寄存器 (160)16.2.7中断状态/清除寄存器 (160)16.2.8OC中断清除寄存器 (160)16.2.9IC中断清除寄存器 (160)16.2.10CODEC WRITE 中断清除寄存器 (161)16.2.11CODEC READ 中断清除寄存器 (161)17I2C (162)17.1概述 (162)17.2I2C控制器结构 (162)17.3I2C控制器寄存器说明 (163)17.3.1分频锁存器低字节寄存器(PRERlo) (163)17.3.2分频锁存器高字节寄存器(PRERhi) (163)17.3.3控制寄存器(CTR) (164)17.3.4发送数据寄存器(TXR) (164)17.3.5接受数据寄存器(RXR) (164)17.3.6命令控制寄存器(CR) (164)17.3.7状态寄存器(SR) (165)18PWM (166)18.1概述 (166)18.2PWM寄存器说明 (166)19RTC (168)19.1概述 (168)19.2寄存器描述 (168)19.2.1寄存器地址列表 (168)19.2.2SYS_TOYWRITE0 (169)19.2.3SYS_TOYWRITE1 (169)19.2.4SYS_TOYMATCH0/1/2 (169)19.2.5SYS_RTCCTRL (170)19.2.6SYS_RTCMATCH0/1/2 (171)20NAND (172)20.1NAND控制器结构描述 (172)20.2NAND控制器寄存器配置描述 (172)20.2.1NAND_CMD(地址:BFE7_8000) (172)20.2.2ADDR_L(地址:BFE7_8004) (173)20.2.3ADDR_H(地址:BFE7_8008) (173)20.2.4NAND_TIMING(地址:BFE7_800C) (173)20.2.5ID_L(地址:BFE7_8010) (173)20.2.6STATUS & ID_H(地址:BFE7_8014) (173)20.2.7NAND_PARAMETER(地址:BFE7_8018) (173)20.2.8NAND_OP_NUM(地址:BFE7_801C) (173)20.2.9CS_RDY_MAP(地址:BFE7_8020) (174)20.2.10DMA_ADDRESS(地址:BFE7_8040) (174)20.3NAND ADDR说明 (174)21WATCHDOG (177)21.1概述 (177)21.2WATCH DOG寄存器描述 (177)21.2.1WDT_EN地址:(0XBFE5_C060) (177)21.2.2WDT_SET(地址:0XBFE5_C068) (178)21.2.3WDT_timer(地址:0XBFE5_C064) (178)22Clock Management (179)22.1C LOCK模块结构描述 (179)22.2C LOCK配置描述 (179)22.3系统其它C LOCK描述 (180)23GPIO and MUX (181)23.1GPIO结构描述 (181)23.2GPIO寄存器描述 (184)23.3MUX寄存器描述 (185)24AC/DC (187)24.1电源域 (187)24.2系统复位 (187)24.3推荐的工作条件 (187)24.4绝对最大额定值 (188)25热特性 (189)25.1焊接温度 (189)图目录图1-1 1B芯片结构图 (2)图 4-1 TLB表项内容 (33)图 4-2 Index 寄存器 (36)图 4-3 Random寄存器 (37)图 4-4 EntryLo0和EntryLo1寄存器 (37)图 4-5 Context寄存器 (38)图 4-6 PageMask寄存器 (38)图 4-7 Wired寄存器界限 (39)图 4-8 Wired寄存器 (40)图 4-9 HWREna寄存器 (40)图 4-10 BadVAddr寄存器 (40)图 4-11 Count寄存器和Compare寄存器 (41)图 4-12 EntryHi寄存器 (41)图 4-13 Status寄存器 (42)图 4-14 IntCtl寄存器 (43)图 4-15SRSCtl寄存器 (44)图 4-16 SRSMap寄存器 (44)图 4-17 Cause寄存器 (45)图 4-18 EPC寄存器 (46)图4-19 Processor Revision Identifier 寄存器 (46)图 4-20 Config寄存器 (47)图 4-21 Config寄存器 (48)图 4-22 Config寄存器 (48)图 4-23 Config寄存器 (49)图 4-24 Config寄存器 (49)图 4-25 WatchLo寄存器 (50)图 4-26 WatchHi寄存器 (50)图 4-27 控制寄存器性能计数寄存器 (51)图 4-28 性能计数器寄存器 (51)图 4-29 TagLo 寄存器(P-Cache) (52)图 4-30 ErrorEPC寄存器 (53)图 4-31 EJTAG调试连接示意图 (54)图 4-32 DCR寄存器格式 (55)图 4-33 硬件指令、数据断点概况 (56)图 4-34 IBS寄存器格式 (57)图 4-35 IBAn寄存器格式 (58)图 4-36 IBMn寄存器格式 (58)图 4-37 IBCn寄存器格式 (58)图 4-38 DBS寄存器格式 (59)图 4-39 DBAn寄存器格式 (60)图 4-40 DBMn寄存器格式 (60)图 4-41 DBCn寄存器格式 (60)图4-42 TAP主要部分 (64)图4-43 ALL指令示意图 (65)图4-44 Fastdata 指令示意图 (65)图 4-45 IDCODE寄存器格式 (66)图 4-46 IMPCADE寄存器示意图 (67)图 4-47 数据寄存器格式 (68)图 4-48 地址寄存器格式 (69)图 4-49 ECR格式 (69)图9-1 USB主机控制器模块图 (114)图9-2 USB主机控制器细节模块图(带EHCI控制器细节) (115)图9-3 接收时序图(16 bit UTMI接口,偶数个数据) (121)图9-4 接收时序图(16 bit UTMI接口,奇数个数据) (121)图9-5 传输时序图(16 bit UTMI接口,偶数个数据) (122)图9-6 传输时序图(16bit UTMI接口,奇数个数据) (122)图10-1 SPI 主控制器结构 (124)图10-2SPI主控制器时序图 (127)图16-1 AC97应用系统 (157)图21-1 看门狗的结构图 (177)图25.1 焊接回流曲线 (189)表目录表 4-1 CPU指令集:访存指令 (27)表 4-2 CPU 指令集:算术指令 (ALU 立即数) (28)表 4-3 CPU 指令集:算术指令 (2操作数) (28)表 4-4 CPU指令集:算术指令(3操作数, R-型) (28)表 4-5 CPU指令集:乘法和除法指令 (29)表 4-6 CPU指令集:跳转和分支指令 (29)表 4-7 CPU指令集:移位指令 (30)表 4-8 CPU指令集:特殊指令 (30)表 4-9 CPU指令集:异常指令 (30)表 4-10 CPU指令集:CP0指令 (31)表 4-11 GS232的CP0指令 (31)表 4-12 GS232IP地址空间的分配 (32)表 4-13 例外编码及寄存器修改 (33)表 4-14 例外入口地址 (34)表 4-15 GS232IP实现的CP0 寄存器 (35)表 4-16 Index寄存器各域描述 (36)表 4-17 Random寄存器各域 (37)表 4-18 EntryLo寄存器域 (37)表 4-19 Context寄存器域 (38)表 4-20 不同页大小的掩码(Mask)值 (39)表 4-21 Wired寄存器域 (40)表 4-22 HWREna寄存器域 (40)表 4-23 EntryHi寄存器域 (41)表 4-24 Status 寄存器域 (42)表 4-25 IntCtl寄存器域 (43)表 4-26 SRSCtl寄存器域 (44)表 4-27Cause寄存器域 (45)表 4-28 Cause寄存器的ExcCode域 (45)表 4-29 PRId 寄存器域 (46)表 4-30 Config 寄存器域 (47)表 4-31 Config 寄存器域 (48)表 4-32 Config 寄存器域 (48)表 4-33 Config 寄存器域 (49)表 4-34 Config 寄存器域 (49)表 4-35 WatchLo寄存器域 (50)表 4-36 WatchHi寄存器域 (50)表 4-37控制域格式 (51)表 4-38 计数使能位定义 (51)表 4-39 计数器0/1事件 (51)表 4-40 Cache Tag寄存器域 (52)表 4-41 CP0指令 (53)表 4-42 DCR寄存器域 (55)表 4-43 硬件断点寄存器 (56)表 4-44 IBS域描述 (57)表 4-45 IBCn域描述 (58)表 4-46 DBS域描述 (59)表 4-47 DBCn域描述 (60)表 4-48 调试例外优先级表 (61)表 4-49 例外屏蔽表 (62)表 4-50 Dseg划分 (63)表 4-51 Dmseg的访问情况 (63)表 4-52 Drseg的访问情况 (63)表 4-53 调试例外中断入口地址 (64)表 4-54 EJTAG指令 (64)表 4-55 TAP数据寄存器 (66)表 4-56 IDCODE寄存器说明 (66)表 4-57 IMPCODE寄存器说明 (67)表 4-58 Psz位的含义 (68)表 4-59 ECR域描述 (69)表 4-60 Sample寄存器说明 (70)表18-18-1 四路控制器描述 (166)表18-18-2 控制寄存器描述 (166)表18-18-3 主计数器设置 (166)表18-18-4 高脉冲计数器设置 (166)表18-18-5 低脉冲计数器设置 (167)表18-18-6 控制寄存器设置 (167)表24-1 1B电源域 (187)表24-2 1B上电配置引脚汇总 (187)表24-3推荐的工作条件 (187)表24-4绝对最大额定值 (188)表25-1 回流焊接温度要求 (189)1 概述龙芯1B芯片是基于GS232处理器核的片上系统,具有高性价比,可广泛应用于工业控制、家庭网关、信息家电、医疗器械和安全应用等领域。

DMA基本知识计算机系统中各种常用的数据输入/输出方法有查询方式(包括无条件及条件传送方式)和中断方式,这些方式适用于CPU与慢速及中速外设之间的数据交换。

但当高速外设要与系统内存或者要在系统内存的不同区域之间进行大量数据的快速传送时,就在一定程度上限制了数据传送的速率。

直接存储器存取(DMA)就是为解决这个问题提出的,采用DMA方式,在一定时间段内,由DMA控制器取代CPU,获得总线控制权,来实现内存与外设或者内存的不同区域之间大量数据的快速传送。

典型DMA控制器(以下简称DMAC ),其数据传送工作过程如下:1.外设向DMAC发出DMA传送请求;2.DMAC通过连接到CPU的HOLD信号向CPU提出DMA请求;3.CPU在完成当前总线操作后会立即对DMA请求做出响应。

CPU的响应包括两个方面:一方面,CPU 将控制总线、数据总线和地址总线浮空,即放弃对这些总线的控制权;另一方面,CPU将有效的HLDA 信号加到DMAC上,以通知DMAC CPU己经放弃了总线的控制权;4.CPU将总线浮空,即放弃了总线控制权后,由DMAC接管系统总线的控制权,并向外设送出DMA 的应答信号;5.DMAC送出地址信号和控制信号,实现外设与内存或内存之间大量数据的快速传送。

6.DMAC将规定的数据字节传送完之后,通过向CPU发HOLD信号,撤消对CPU的DMA请求。

CPU 收到此信号,一方面使HLDA无效,另一方面又重新开始控制总线,实现正常取指令、分析指令、执行指令的操作。

s3c2440提供了4个通道的DMA,它们不仅可以实现内存之间的数据交换,还可以实现内存与外设,以及外设与外设之间的数据交换。

要用好s3c2440的DMA,关键是配置好它的源、目的寄存器,和必要的控制寄存器。

寄存器DISRCn是初始DMA源寄存器,它是用于设置DMA数据传输的源基址,而寄存器DIDSTn是初始DMA目的寄存器,它是用于设置DMA数据传输的目的基址。

1.DMA,全称Direct Memory Access,即直接存储器访问。

DMA传输将数据从一个地址空间复制到另一个地址空间,提供在外设和存储器之间或者存储器和存储器之间的高速数据传输。

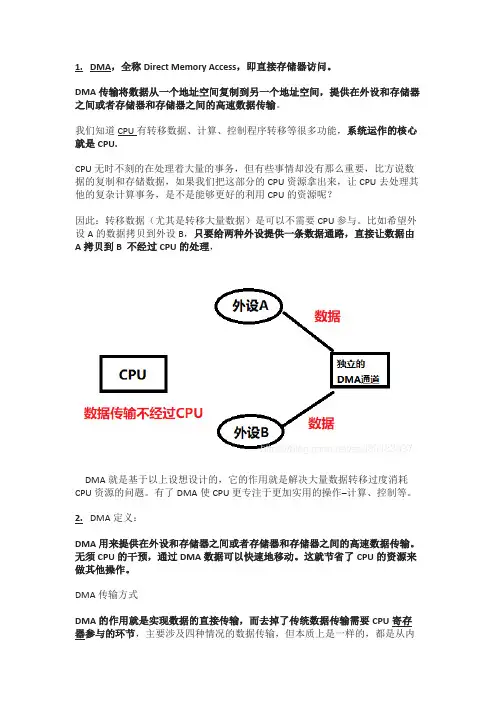

我们知道CPU有转移数据、计算、控制程序转移等很多功能,系统运作的核心就是CPU.CPU无时不刻的在处理着大量的事务,但有些事情却没有那么重要,比方说数据的复制和存储数据,如果我们把这部分的CPU资源拿出来,让CPU去处理其他的复杂计算事务,是不是能够更好的利用CPU的资源呢?因此:转移数据(尤其是转移大量数据)是可以不需要CPU参与。

比如希望外设A的数据拷贝到外设B,只要给两种外设提供一条数据通路,直接让数据由A拷贝到B 不经过CPU的处理,DMA就是基于以上设想设计的,它的作用就是解决大量数据转移过度消耗CPU资源的问题。

有了DMA使CPU更专注于更加实用的操作–计算、控制等。

2.DMA定义:DMA用来提供在外设和存储器之间或者存储器和存储器之间的高速数据传输。

无须CPU的干预,通过DMA数据可以快速地移动。

这就节省了CPU的资源来做其他操作。

DMA传输方式DMA的作用就是实现数据的直接传输,而去掉了传统数据传输需要CPU寄存器参与的环节,主要涉及四种情况的数据传输,但本质上是一样的,都是从内存的某一区域传输到内存的另一区域(外设的数据寄存器本质上就是内存的一个存储单元)。

四种情况的数据传输如下:外设到内存内存到外设内存到内存外设到外设3.DMA传输参数我们知道,数据传输,首先需要的是1 数据的源地址 2 数据传输位置的目标地址,3 传递数据多少的数据传输量,4 进行多少次传输的传输模式 DMA所需要的核心参数,便是这四个当用户将参数设置好,主要涉及源地址、目标地址、传输数据量这三个,DMA 控制器就会启动数据传输,当剩余传输数据量为0时达到传输终点,结束DMA传输,当然,DMA 还有循环传输模式当到达传输终点时会重新启动DMA传输。

第七章一.填空题1 CPU响应中断时需要保存当前现场,这里现场指的是和的内容,它们被保存到中。

2在中断服务程序中,保护和恢复现场之前需要中断。

3 DMA只负责总线上进行数据传送,在DMA写操作中,数据从传送到。

4总线的裁决方式速度最高。

5某机有四个中断源,优先顺序按1→2→3→4降序排列,若想将中断处理次序改为3→1→4→2,则1、2、3、4中断源对应地屏蔽字分别是、、和。

6 I/O接口电源通常具有、、和功能。

7 I/O的编址方式可分为和两大类,前者需有独立的I/O指令,后者可通过指令和设备交换信息。

8主机与设备交换信息的控制方式中,方式主机与设备是串行工作的,方式和方式主机与设备是并行工作的,且方式主程序与信息传送是并行进行的。

9 I/O与主机交换信息的方式中,和都需通过程序实现数据传送,其中体现CPU与设备是串行工作的。

10 CPU响应中断时要保护现场,包括对和的保护,前者通过实现,后者可通过实现。

11一次中断处理过程大致可分为、、、和等五个阶段。

12 在DMA方式中,CPU和DMA控制器通常采用三种方法来分时使用主存,它们是、、和。

13 中断接口电路通过总线将向量地址送至CPU.14 I/O与主机交换信息共有、、、和五种控制方式。

15 单重中断的中断服务程序的执行顺序为、、、和中断返回。

16 多重中断的终端服务程序的执行顺序为、、、和中断返回。

二.选择题1.将外围设备与主存统一编址,一般是指。

A. 每台设备占一个地址码B.每个外围接口占一个地址码C.接口中的有关寄存器各占一个地址码D.每台外设由一个主存单元管理2.主机与设备传送数据时,采用,主机与设备是串行工作的。

A. 程序查询方式B.中断方式C.DMA方式D.通道方式3.当有中断源发出请求时,CPU可执行相应的中断服务程序。

提出中断请求的可以是。

A. 通用寄存器B.专用寄存器C.外部事件D.cache4.在中断周期,CPU主要完成以下工作:。

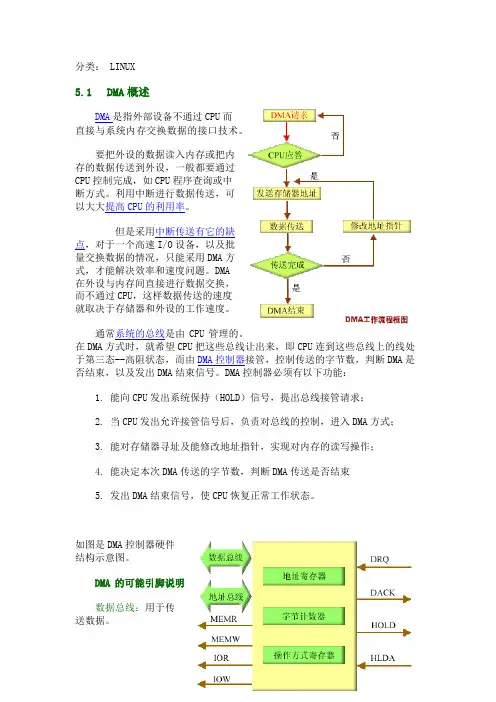

分类: LINUX5.1DMA概述DMA是指外部设备不通过CPU而直接与系统内存交换数据的接口技术。

要把外设的数据读入内存或把内存的数据传送到外设,一般都要通过CPU控制完成,如CPU程序查询或中断方式。

利用中断进行数据传送,可以大大提高CPU的利用率。

但是采用中断传送有它的缺点,对于一个高速I/O设备,以及批量交换数据的情况,只能采用DMA方式,才能解决效率和速度问题。

DMA在外设与内存间直接进行数据交换,而不通过CPU,这样数据传送的速度就取决于存储器和外设的工作速度。

通常系统的总线是由CPU管理的。

在DMA方式时,就希望CPU把这些总线让出来,即CPU连到这些总线上的线处于第三态--高阻状态,而由DMA控制器接管,控制传送的字节数,判断DMA是否结束,以及发出DMA结束信号。

DMA控制器必须有以下功能:1. 能向CPU发出系统保持(HOLD)信号,提出总线接管请求;2. 当CPU发出允许接管信号后,负责对总线的控制,进入DMA方式;3. 能对存储器寻址及能修改地址指针,实现对内存的读写操作;4. 能决定本次DMA传送的字节数,判断DMA传送是否结束5. 发出DMA结束信号,使CPU恢复正常工作状态。

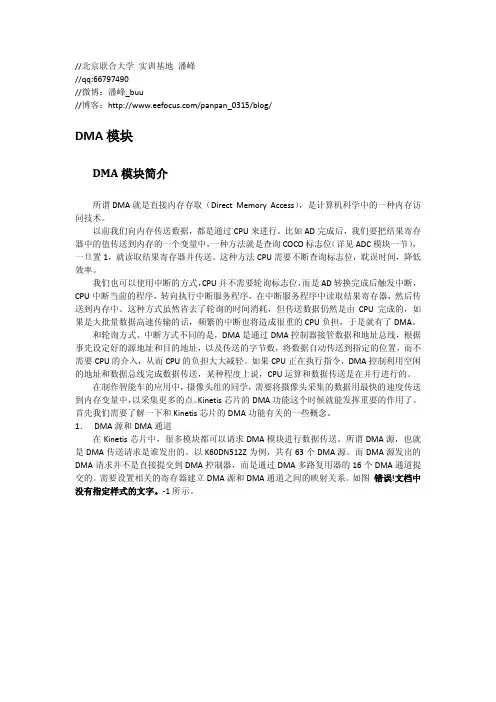

如图是DMA控制器硬件结构示意图。

DMA的可能引脚说明:数据总线:用于传送数据。

地址总线:用于选择存储器地址。

数据传送信号:MEMR为存储器读操作信号,MEMW为存储器写操作信号,IOR为外设读操作信号,IOW为外设写操作信号。

DRQ:DMA请求信号。

是外设向DMA控制器提出要求DMA操作的申请信号。

DACK:DMA响应信号。

是DMA控制器向提出DMA请求的外设表示已收到请求和正进行处理的信号。

HOLD:总线请求信号。

是DMA控制器向CPU要求让出总线的请求信号。

HLDA:总线响应信号,是CPU向DMA控制器表示允许总线请求的应答信号。

5.2DMA工作方式随着大规模集成电路技术的发展,DMA传送已不局限于存储器与外设间的信息交换,而可以扩展为在存储器的两个区域之间,或两种高速的外设之间进行DMA传送,如图所示。

//北京联合大学实训基地潘峰//qq:66797490//微博:潘峰_buu//博客:/panpan_0315/blog/DMA模块DMA模块简介所谓DMA就是直接内存存取(Direct Memory Access),是计算机科学中的一种内存访问技术。

以前我们向内存传送数据,都是通过CPU来进行。

比如AD完成后,我们要把结果寄存器中的值传送到内存的一个变量中,一种方法就是查询COCO标志位(详见ADC模块一节),一旦置1,就读取结果寄存器并传送。

这种方法CPU需要不断查询标志位,耽误时间,降低效率。

我们也可以使用中断的方式,CPU并不需要轮询标志位,而是AD转换完成后触发中断,CPU中断当前的程序,转向执行中断服务程序,在中断服务程序中读取结果寄存器,然后传送到内存中。

这种方式虽然省去了轮询的时间消耗,但传送数据仍然是由CPU完成的,如果是大批量数据高速传输的话,频繁的中断也将造成很重的CPU负担,于是就有了DMA。

和轮询方式、中断方式不同的是,DMA是通过DMA控制器接管数据和地址总线,根据事先设定好的源地址和目的地址,以及传送的字节数,将数据自动传送到指定的位置,而不需要CPU的介入,从而CPU的负担大大减轻。

如果CPU正在执行指令,DMA控制利用空闲的地址和数据总线完成数据传送,某种程度上说,CPU运算和数据传送是在并行进行的。

在制作智能车的应用中,摄像头组的同学,需要将摄像头采集的数据用最快的速度传送到内存变量中,以采集更多的点。

Kinetis芯片的DMA功能这个时候就能发挥重要的作用了。

首先我们需要了解一下和Kinetis芯片的DMA功能有关的一些概念。

1.DMA源和DMA通道在Kinetis芯片中,很多模块都可以请求DMA模块进行数据传送。

所谓DMA源,也就是DMA传送请求是谁发出的。

以K60DN512Z为例,共有63个DMA源。

而DMA源发出的DMA请求并不是直接提交到DMA控制器,而是通过DMA多路复用器的16个DMA通道提交的。

STM32学习之:DMA详解JawSoW个人分类:STM32DMA部分我用到的相对简单,当然,可能这是新东西,我暂时还用不到它的复杂功能吧。

下面用问答的形式表达我的思路。

DMA有什么用?直接存储器存取用来提供在外设和存储器之间或者存储器和存储器之间的高速数据传输。

无须CPU的干预,通过DMA数据可以快速地移动。

这就节省了CPU的资源来做其他操作。

有多少个DMA资源?有两个DMA控制器,DMA1有7个通道,DMA2有5个通道。

数据从什么地方送到什么地方?外设到SRAM(I2C/UART等获取数据并送入SRAM);SRAM的两个区域之间;外设到外设(ADC读取数据后送到TIM1控制其产生不同的PWM占空比);SRAM到外设(SRAM中预先保存的数据送入DAC产生各种波形);……还有一些目前还搞不清楚的。

DMA可以传递多少数据?传统的DMA的概念是用于大批量数据的传输,但是我理解,在STM32中,它的概念被扩展了,也许更多的时候快速是其应用的重点。

数据可以从1~65535个。

直接存储器存取(Direct Memory Access,DMA)是计算机科学中的一种内存访问技术。

它允许某些电脑内部的硬体子系统(电脑外设),可以独立地直接读写系统存储器,而不需绕道 CPU。

在同等程度的CPU负担下,DMA是一种快速的数据传送方式。

它允许不同速度的硬件装置来沟通,而不需要依于 CPU的大量中断请求。

【摘自Wikipedia】现在越来越多的单片机采用DMA技术,提供外设和存储器之间或者存储器之间的高速数据传输。

当 CPU 初始化这个传输动作,传输动作本身是由DMA 控制器来实行和完成。

STM32就有一个DMA控制器,它有7个通道,每个通道专门用来管理一个或多个外设对存储器访问的请求,还有一个仲裁器来协调各个DMA请求的优先权。

DMA 控制器和Cortex-M3核共享系统数据总线执行直接存储器数据传输。

当CPU和DMA同时访问相同的目标(RAM或外设)时,DMA请求可能会停止 CPU访问系统总线达若干个周期,总线仲裁器执行循环调度,以保证CPU至少可以得到一半的系统总线(存储器或外设)带宽。

第一课:现成的三维物体建模1-1、3Dmax2010软件简介和安装3D Studio Max,常简称为3ds Max或MAX,是Autodesk公司开发的基于PC系统的三维模型制作和动画渲染软件,其广泛应用于室内设计、建筑设计、影视、工业设计、多媒体制作、游戏、辅助教学以及工程可视化等领域。

3Dmax2010中文版下载地址:我要自学网首页→ 学习辅助→ 常用软件1-2、3dmax2010界面组成和界面优化快速工具栏“文件”菜单3Dsmax2010界面优化:1、改变界面风格:自定义---加载自定义用户界面方案UI文件的位置在C:\Program Files\Autodesk\3ds Max 2010\ui2、隐藏动画轨迹栏:自定义---显示---3、隐藏石墨建模工具栏:4、以小图标来显示工具栏:自定义---首选项---常规---5、自定义布局:在“视图控制区”右击1-3、3dmax2010视图控制1-4、3Dmax2010标准基本体长方体、球体、圆柱体、圆环、茶壶、圆锥体、几何球体、管状体、四棱锥、平面1-5和1.6、实例:装饰品知识点:(1)、学习堆积木式的建模方法,(2)、学习“选择、移动、修改、复制”物体1-7、实例:桌几尺寸:1300*800 1000*500 25*480知识点:(1)、使用标准尺寸建模1-8、3Dmax2010扩展基本体异面体、切角长方体、油罐,纺锤,油桶、球棱柱、环形波,软管,环形结、切角圆柱体、胶囊、L-Ext , C-Ext、棱柱。

1-9、1-10 实例:简约茶几尺寸:玻璃半径:500mm 高10mm 环形结:半径:335mm P:1 Q:3 横截面半径:15mm知识点:(1)、借助其它物体来确定尺寸(2)、学习“对齐”和“旋转”物体1-11、综合实例:沙发尺寸:总的800*800*100 坐垫650*650*150 柱子两侧150*300 柱子后面150*500 脚25*50知识点:把前面学习的知识综合应用。