第1章绪论

1.1数字下变频技术的应用及前景

随着近年来现场可编程门阵列(FPGA)器件和通用数字信号处理器(DSPor)在芯片逻辑规模和处理速度等方面性能的迅速提高,用硬件编程或软件编程方式实现无线功能的软件无线电技术在理论和实用化上都趋于成熟和完善。软件无线电技术只需通过软件上的更新就能够选择不同的业务或调制方式、追加和修改功能,具有传统硬件方式所无法比拟的灵活性、开放性和可扩展性。因此,软件无线电技术已经被越来越广泛地应用于蜂窝通信及各种军用和民用的无线系统中。

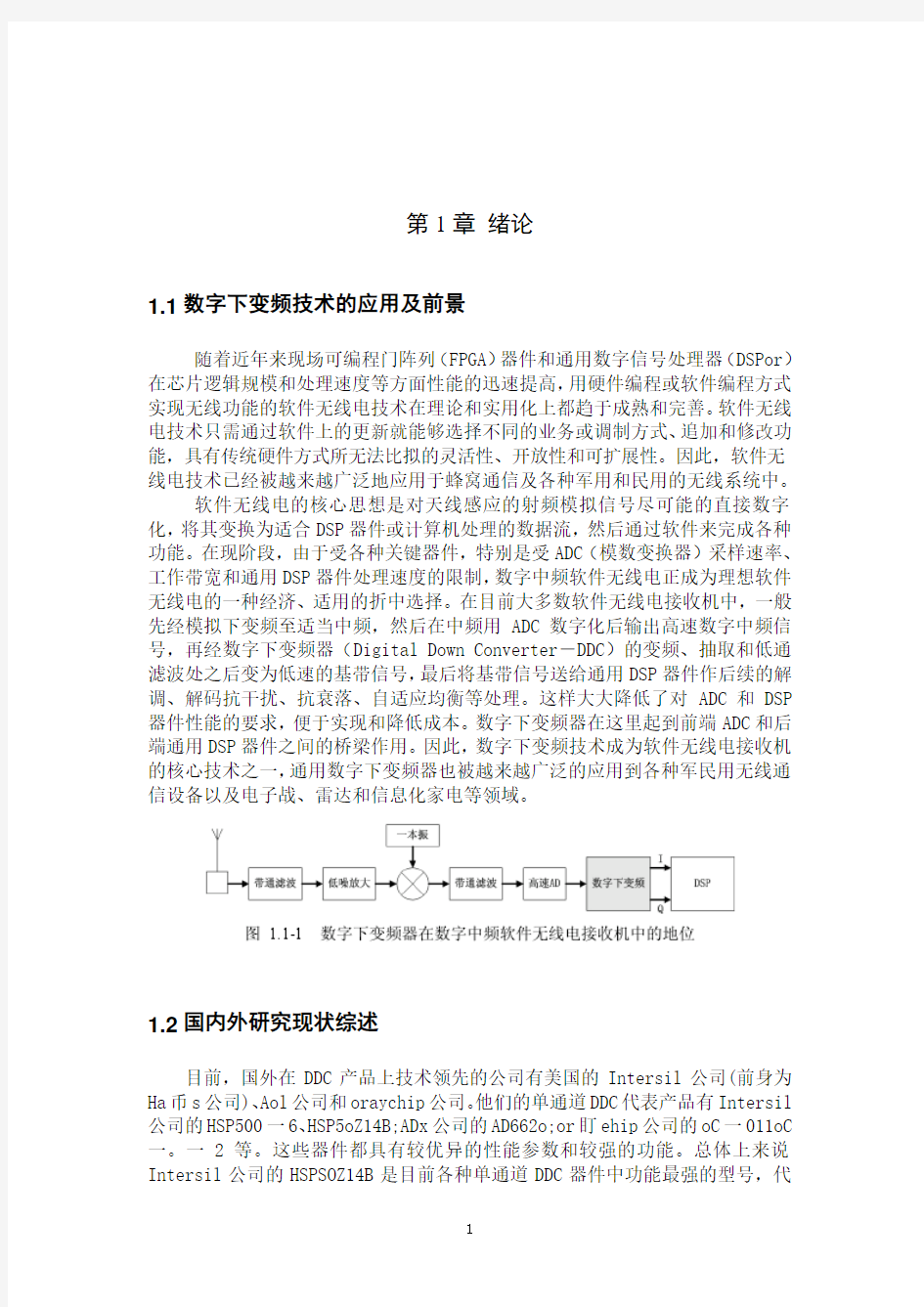

软件无线电的核心思想是对天线感应的射频模拟信号尽可能的直接数字化,将其变换为适合DSP器件或计算机处理的数据流,然后通过软件来完成各种功能。在现阶段,由于受各种关键器件,特别是受ADC(模数变换器)采样速率、工作带宽和通用DSP器件处理速度的限制,数字中频软件无线电正成为理想软件无线电的一种经济、适用的折中选择。在目前大多数软件无线电接收机中,一般先经模拟下变频至适当中频,然后在中频用ADC数字化后输出高速数字中频信号,再经数字下变频器(Digital Down Converter-DDC)的变频、抽取和低通滤波处之后变为低速的基带信号,最后将基带信号送给通用DSP器件作后续的解调、解码抗干扰、抗衰落、自适应均衡等处理。这样大大降低了对ADC和DSP 器件性能的要求,便于实现和降低成本。数字下变频器在这里起到前端ADC和后端通用DSP器件之间的桥梁作用。因此,数字下变频技术成为软件无线电接收机的核心技术之一,通用数字下变频器也被越来越广泛的应用到各种军民用无线通信设备以及电子战、雷达和信息化家电等领域。

1.2国内外研究现状综述

目前,国外在DDC产品上技术领先的公司有美国的Intersil公司(前身为Ha币s公司)、Aol公司和oraychip公司。他们的单通道DDC代表产品有Intersil 公司的HSP500一6、HSP5oZ14B;ADx公司的AD662o;or盯ehip公司的oC一011oC 一。一2等。这些器件都具有较优异的性能参数和较强的功能。总体上来说Intersil公司的HSPSOZ14B是目前各种单通道DDC器件中功能最强的型号,代

表了单通道DDC器件的领先水平。

然而,从国内外发展来看,用FPGA来实现比用以上专用芯片具有更多的好处,FPGA器件具有很强的稳定性和高效的处理能力,它可以工作在几十甚至上百MHz的频率上,其高速强大的处理能力,是实现数字中频处理的理想器件。使用FPGA芯片实现的下变频器件可以更加方便的采用软件方法将存储器、控制器等外围器件集成到芯片内部,提高了整个系统的稳定行和集成度。虽然用硬件实现,FPGA的重复可配置能力,使其可以根据不同的系统要求,采用不同的结构来完成相应的功能,具有很强的灵活性,便于进行系统功能扩展和性能升级。并且设计和修改非常容易,其灵活性与方便性与软件实现相差无几,适合软件无线电灵活性的要求。目前在软件无线电设计时,一般都采用软硬件相结合的方式进行。所以采用FPGA来设计数字下变频器更是一种好的解决方案。从价格上来说,最便宜的DDC芯片也需要20美元,而xihnLx公司的sPartan_3系列芯片,40万门刁‘需要8美元。所以从性价比来看,用FPGA来实现DDC是以后发展的方向。基于这种思想,本设计采用FPGA器件来实现数字下变频,并进行了设计、仿真与验证。

1.3 FPGA在数字下变频领域的应用

近年来FPGA器件在工艺方面的进步和设计思想上的创新为之带来了前所未有的逻辑规模和强大的处理性能。例如,Altera公司采用0.13μm工艺的Stratix 系列FPGA逻辑资源最大达到8万个逻辑单元(Logical Element——LE),内置176个300MHz的9×9乘法器,可组合成22个36×36乘法器,可专门面向DSP 设计应用,片内RAM容量最高达7,427,520 bits(928,440 bytes),完全可以

用来实现一个高性能的DDC;而最新的采用90nm工艺的StratixII系列FPGA 其逻辑资源最大可达到18万个LE,内置384个420MHz的18×18乘法器,已

经可以在一片FPGA中实现一个功能强大的软件无线电接收机系统。而且芯片

逻辑资源相同时,StratixII器件的价格比Stratix器件还要低。随着FPGA性能越来越强,规模越来越大,成本不断降低,利用FPGA实现高速专用数字下变频器已经成为通信系统设计中常用的手段。

在经过FPGA充分验证的基础上,还可以将FPGA设计转为ASIC,降低芯

片成本,使其市场化。Altera公司最新推出的HardCopyII技术,可以在10~12 周内将一个成熟的FPGA设计转成量产的ASIC,并且保证ASIC的功能和时序

与FPGA芯片完全一致,pin to pin的管脚兼容,大大减少了设计者验证和仿真的工作量,免除使用者重新Layout PCB的麻烦,其100%的流片成功率大大减

少了从设计到产品的移植周期。

1.4 本论文章节的安排

全文分为6章,具体章节安排如下:

第2章对数字下变频的基本原理,系统结构,基本性能进行了介绍,并对设计中的关键技术、影响性能的主要因素和应注意的问题进行了说明。

第3章对数字下变频系统所涉及的理论分模块进行了详细的介绍,即可编程下变频模块与高效抽取滤波模块,并对数字下变频所要用到的算法进行了介绍。

第4章对数字下变频各模块基于FPGA进行了设计与实现,并对参数设计、设计中要考虑到的问题和实现步骤进行了说明,提出了解决方法。最后给出了资源利用报告和顶层原理图。

第5章对基于FPGA的各个模块及整个系统进行了仿真验证。

第6章为论文的结束语部分,总结了论文的主要工作并指出了尚待进一步研究的问题和研究展望。

第2章数字下变频的框架结构

2.1数字下变频的基本原理

数字下变频(DigitalDownConverte DDC)技术是软件无线电核心技术之一,其组成与模拟下变频器类似,包括数字混频器、数字控制振荡器(Numerican ControlledOsillator一NCO)和低通滤波器(LPF)三部分组成,如图2.1所示:

从工作原理上讲,数字下变频与模拟下变频是一样的,是一个输入信号与一个本地振荡信号的乘法运算。与模拟下变频相比,数字下变频的运算速度受DSP 处理速度的限制,同时其运算速度决定了其输入信号数据流可达到的最高速率。数字下变频的数据精度和运算精度也影响着接收机的性能,所以,数字下变频器需要进行优化设计。

数字下变频的任务是将刀D输出的高速数字信号经过一系列处理提取出来。其基本功能主要有三方面:第一是变频,包括数控本振和数字混频两部分,从输入的宽带高数据流的数字信号中提取所需的窄带信号,将其下变频为数字基带信号。数控振荡器(NCO)的分辨率做的越高,其提取单载波的能力就越好。数字下变频经两个相乘器所构成的混频器,将输入的数字信号和数控振荡器产生的两路正交正(余)弦信号相乘,相乘结果为I,Q两路信号。第二是低通滤波,这部分由高效抽取滤波器和有限长冲击响应(FIR)滤波器进行处理,功能是低通滤和抽取,滤除带外信号,提取感兴趣的信号。其输出是数据流降低了的数字基带信号。第三是采样速率转换,降低采样速率,以利于后续信号处理。在具体设计实现中,低通滤波和降采样是结合在一起进行的。

2.2 数字下变频的系统结构

由于对DDC输出信号的后续处理,主要是完成信号解调、解码、调制样式识别以及信号参数估计等工作,而正交分解后的两路基带信号,对上述后续处理往往带来很大的便利和更好的性能,因此,几乎所有的DDC产品都是采用这样的结

构。

数字下变频系统结构框图,如图2.2所示:

(1)可编程下变频模块(proamm的leoowneonverte:)

这部分负责产生数字本振信号和数字混频,数字本振信号和输入信号相乘,仅将载频附近的频谱分量搬移到零中频,而后产生的信号分为有用信号和谐波两部分。这两部分信号是混叠在一起的,将会在后续处理过程中进行滤波,保留有用信号。

(2)高效抽取滤波模块(EfficientDeeimateFilterModule)

这部分是设计的最重要部分,混频后的有用信号可能速率仍然很高,超DS 器件处理能力。抽取滤波器模块主要目的是降低信号的采样速率,在降采程中不可避免的产生频率混叠与加入噪声,由于任何一种滤波器单独使用都能达到想要的大的抽取速率的降低和滤波整形的完整效果,所以设计采用滤波级联与三种滤波器分级进行逐级降采样与滤波器整形。这一部分的设计主要由部分组成:分别是积分梳状滤波器抽取组(CIC)、半带滤波器(HB)、FIR滤波器CIC滤波器和HB 滤波器的滤波器特性本文将在第三章详细介绍。CIC、HB滤波抽取组的主要目的是完成采样速率的抽取功能,通过大的抽取,使数据流快速降下来。本设计采用CIC滤波器作为首级低通滤波和抽取的原因是:我们知道滤波运算就是卷积运算,不外做乘加运算,DSP做乘运算比加法运算要费事得多,而输入到抽取系统的速率就是ADC的采样速率,是非常高的(如50MHz),这样高的速率DSP很难胜任。由于CIC滤波器具有系数全为1的特性,只有加减法运算,因此滤波运算非常简单且容易实现,只需将顺序输入的样本数据按抽取因子个数相加后输出,就完成了抽取滤波。所以CIC滤波器,特别适合位于抽取模块的第一级和进行大的抽取因子工作,使高速率信号大幅度降低,以利于后续器件对信号的处理。由于CIC的过渡带和阻带衰减性能不是很好,设计中采用了级联的方法加大过渡带和阻带的衰减,级联后(一般为五级)有很陡的衰减幅度(主瓣),适合作为滤波器组的第一级。下一级HB滤波器,因为HB滤波器具有一半系数为0的特点,使用其实现取样率变换时,只需要一半的计算量,特别适合实时处理。HB的抽取因子

固定为2,因此特别适合采样率降低一半的要求。如果仅仅用这两种滤波器实现滤波,信号在通带内的失真会很大,且不能滤出临信道的干扰信号,信道分离能力差。所以后续还要用一个FIR滤波器负责对整个信道进行整形滤波,也可以做匹配滤波器和抽取滤波器使用,此处设计采用升余弦滤波器。这级滤波器设计成为可编程的FIR滤波器后还能再进行进一步的抽取。

2.3 影响性能的主要因素和技术指标

(l)影响数字下变频性能的主要因素有两个:一是表示数字本振、输入信号以及混频乘法运算的样本数值有限字长所引起的误差;二是数字本振相位分辨率不够而引起数字本振样本数值的近似取值。也就是说数字混频器和数字本振数据位数不够宽,存在尾数截断的情况。数字本振相位的样本值存在近似的情况根据截断和近似的程度,会或多或少地影响DDC的性能。

(2)滤波器的阶数越高,过渡带越陡,而阶数的大小又决定了FPGA内部资源的使用,所以滤波器的阶数跟FPGA的资源如何做到适中是一个关键问题。

(3)抽取因子即不能太大也不能太小,抽取因子太大不能有效的表示信号。

(4)数字下变频的输入、输出数据精度和内部运算精度都影响着接收机的性能。如何既满足精度要求,又不使用过多的资源是设计的问题。

2.4 本章小结

本章对数字下变频系统的原理、功能、框架结构和各模块的配置关系进行了详细的介绍,是整个下变频系统的概括,了解这一部分的理论有利于后续工作的进行。

第3章数字下变频的关键模块3.1 DDC基于FPGA的设计流程

3.2可编程下变频模块

这一部分是数字下变频结构中的第一个坏节,这一部分主要由两个模块完成:一个是直接频率合成器(DDS),一个是乘法器。乘法器是数字信号处理的基本运算单元,在实现混频时,由于只需要两个乘法器,通过FPGA中芯片含有的内置乘法器,可以实现很高的运算速度,使资源使用更有效。直接频率合成是数字通信解调必不可少的部分,要在数据率很高的情况下产生可数控的本振。

3.2.1 DDS介绍

频率合成技术经过几十年的发展先后经历了从直接频率合成(DS)到锁相环频率合成(PLL),再到直接数字频率合成(DDS)的两次飞跃。直接数字频率合成ons(nireetnigitalFrequeneys”thesis)技术是频率合成技术的一次革命,最早是由美国学者JosephTiemey等三人于197一年提出的。005技术是一种把一系列数字形式的信号,通过数模转换变成模拟形式的信号合成技术,目前使用最广泛的一种DDS方式是利用高速存储器作查找表,然后通过高速DAC输出已经用数字形式存入的正弦波。

DDS的主要优点是:相位连续、频率分辨率高、频率转换速度快以及良好的可复制性能,它以有别于其他频率合成方法的优越性能和特点,成为现代频率合成技术中的佼佼者。DDS广泛应用于接收机本振、信号发生器、通信系统以及雷达系统等。

3.2.2 DDS的系统结构

DDS的基本原理框图如图3.2,频率控制字K和相位控制字分别控制DDS输出正(余)弦波的频率和相位。DDS系统的核心是相位累加器,它由一个累加器和一个N位相位寄存器组成。每到来一个时钟脉冲,相位寄存器就以步长K增加。相位寄存器的输出与相位控制字相加,其结果作为正(余)弦查找表的地址。正(余)弦查找表由ROM构成,内部存有一个完整的周期正(余)弦波的数字幅度信息,每个查找表的地址对应正弦波中0一2二范围的一个相位点。查找表把输入的地址信息映射成正(余)弦波幅度信号,同时输出到数模转换器的输入端,输出的模拟信号经过低通滤波器可得到一个频谱纯净的正(余)弦波。

相位寄存器每经过2N/K个关时钟周期后回到初始状态,相应地正(余)弦查找表经过一个循环回到初始位置,DDS输出一个正(余)弦波。即输出正(余)弦波周期为:

(3.1) 输出频率为:

(3.2) DDS最小分辨率:

(3.3)

当K=2N-1,时,DDS最高的基波合成频率为。对于一

般应用商业

成熟的DDS器件而一言,合成的最高频率一般不超过系统时钟频率的40%。

3.3 高效抽取滤波模块

3.3.1 CIC滤波器

所谓级联积分梳状(CascadedIntegratorcom卜一CIC)滤波器,是指该滤波器的冲激响应具有如下形式:

(3.4)式中,D即为CIC滤波器的阶数(同时也为CIC抽取器的抽取因子)。根据Z变换的定义,CIC滤波器冲激响应之Z变换为:

(3.5)式(3.5)中

(3.6)

(3.7)H(z)(即CIC滤波器)的原理框图如图3.3所示。

如图3.3所示,此处的抽取D在最后一级,当抽取器的抽取信数等于CIC 滤波器的阶数时,根据网络结构等效变换原理f”],可以将抽取部分提前,这样能够使计算量大大的降低。

从图3.4中可以看出HI(z)在实现上就是一个累加器,因此被称作积分器;而HZ(z)之所以称为梳状滤波器,可以从它的幅频特性来说明〕把Z=E jw代入式

(3.6)和式(3.7),可得H

1(z)和H

2

(z)的频率响应为:

分别画出H

2(e jw)和H

1

(e jw)的幅频和相频响应特性曲线,如图3.5和图3.6

所示。

从图3.6中可以清晰地看出,| H

2

(e jw)|的形状女口同一把梳子,因此被形象的称为梳状滤波器。CIC滤波器由积分器和梳状滤波器两部分级联而成,因此被成为级联积分梳状滤波器。

由H

1(e jw)和H

2

(e jw)可计算出总的频率响应H (e jw) 为

(3.10)

H (e jw)积分梳状滤波器幅频响应曲线如图3.7所示。

图3.7中(O-2π/D)的区间称为CIC滤波器的主瓣,而其他区间称为旁瓣。

(e jw)|=D,由图3.7可见,随着频率的增大,旁瓣电平不断

主瓣电平为| H

2

减小,其中第一旁瓣电平为:

(3.11)当D>>1时,|sin(3π)|≈3π/(2D),所以第一旁瓣电平,A

为

1

(3.12)

它与主瓣电平(D)的差值α

:

s

(3.13)

可见,单级CIC滤波器的旁瓣电平是比较大的,只比主瓣低13.46dB,这也就意味着阻带衰减很差,难以满足一般的应用要求。

为了降低旁瓣电平,可以采用多级CIC滤波器级联的办法来解决。级联积分梳状滤波器是EB.Hogenauer在1981年提出的,它的优点在于可以有效的降低由于抽取引起的频谱混叠。

Q级clc实现时的频率响应为:

(3.14) 同理可求得Q级clc滤波器的旁瓣抑制为:

(3.15)

Q=67.3dB

当D=5时,α

S

可见5级CIC滤波器具有67dB左右的阻带衰减,基本能满足实际要求。级联CIC抽取滤波器的实现框图如图3.8所示:

如图3.8,可以看出CIC滤波器只有加减运算,没有乘法运算,实现简单,所以多用于抽取滤波的第一级,便于把高速率降到相对较低的速率上,易于后级HB滤波器和FIR滤波器的进一步处理。

5级CIC滤波器级联后的幅频响应曲线如图3.9所示:

设计中应注意的几点问题:

由于单级CIC的过渡带和阻带的衰减性能不是很好,设计采用了级联的方法来加大过渡带和阻带的衰减。但在进行CIC滤波器设计时,即级数及阶数的选择,在阻带衰减与带内容差之间要折中考虑,不能过分追求某一指标,下面本文将对CIC滤波器的性能与参数的设计进行详细的分析。

(1)CIC滤波器的处理增益

(e jw)表达式

在使用CIC抽取滤波器时由于Q级CIC滤波器的频率响应H

Q

(3.16)

可见,CIC抽取滤波器有一个处理增益DQ。而且随着级数Q的增多和抽取因子D 的加大,处理的增益也越大,所以在用软件或硬件实现CIC滤波器时,每一级必须保留足够的运算精度,否则就可能引起溢出错误,或运算精度的降低。

(3)CIC滤波器非线性相位

由图3.9可见,CIC相位每隔2π/D就会发生一次跳变,也就是说在整个相位区间O一2π内相位是非线性的,但是在每一个间隔2π/D区间内,相位是线性

的。因此CIC滤波器的输入信号落在0一2π区间内,其余区间信号被抑制,对

滤波和抽取后的结果没有影响。所以CIC滤波器在工作范围内可以看作是线性相位滤波器。

(4)CIC的抗混叠问题:

如图3.10,如果抽取的信号带宽很窄(如图ω

1所示)且当ω

2

=2π/D-ω

1

处衰

减足够大时,在其信号带宽内,抽取后产生的混叠是可以忽略不计的,而其他部分的混叠本来就是在有效带宽之外,可以由后级的FIR滤除。

下面分析无混叠带宽ω

1与衰减值A

1

的关系。

对于单级CIC滤波器的衰减A

1

:

(3.17)

(3.18)引入带宽比例因子b,设ω

1

=b(2π/D),则

(3.19)

带宽比例因子实际上是抽取信号的带宽B与抽取后的输出采样率f

s

与抽取

因子D(即f

s

/D)的比值,即

(3.20)

由式(3.20)可见,为使b值尽可能的小,以便获得足够的阻带衰减,降低混叠影响,在信号带宽B一定的条件下,应可能的采用小的抽取因子D或增大输入

采样率f

s

,后者就意味着CIC抽取滤波器一般要用在抽取系统的第一级(输入采样率高)或是内插系统的最后一级。

当b≤1,D≥1时,上式可以简化为

(3.21)

当采用多级级联的时候,阻带衰减为A

1N=-N(20lgb)=NA

1

,即为单级时的N

倍。

(5)通带衰减

由图 3.10,在ω=ω

1

时,滤波器有一定的衰减,此处下降幅度不能太大,也就是说信号通带内幅值容差不能太大,否则会造成通带信号的高频成分衰减过度,导致信号失真。设幅值容差为δs,则可求得

(3.22)

(3.23) 当D/b?1时,sin(bπ/D)≈bπ/D,

(3.24)

例如当b=0.1时,δs=0.143dB

当b=0.05时,δs=o.036dB

可见,从带内平坦度考虑,带宽因子b不能选的太大,也就是说信号带宽不能选的太宽,否则会引起高频失真(高频成分被衰减)。

同理,Q级CIC滤波器的带内容差为:

(3.25)

也就是说Q级clc的带内容差是单级时的Q倍。可见,多级级联虽然增大了阻带衰减,减小混叠影响,但会增大带内容差,即带内平坦度降低。所以CIC 滤波器的级数是有限的,一般以5级为限。

由以上分析可以看出,CIC滤波器无论是阻带衰减式还是带内幅值容差δs,都只与带宽比例因子b有关,也就是说只与信号带宽(相对于输出采样率的信号带宽)有关,而与绝对信号带宽无关。这样在绝对信号带宽较宽时,可以通过降低抽取因子D来提高输出采样率,从而达到减小相对信号带宽,也就是减小带宽比例因子b的目的。所以CIC滤波器的抽取因子(或滤波阶数)不能随意选取,否则会影响抽取性能。在实现数字下变频的设计中为获得较大的阻带衰减,降低混叠影响,在信号带宽一定的情况下应尽可能的采用小的抽取因子或增大采样率fs(增大采样率fs意味着CIC抽取滤波器一般要用在抽取系统的第一级,此时的采样率最高)。

3.3.2 HB滤波器

半带滤波器(HalfBandFilter-eeseHBF)在多速率信号处理中有着特别重要

的位置,因为这种滤波器特别适合实现I=2M的抽取或内插,而且计算效率高,

实时性强。所谓半带滤波器是,旨其频率响应H(e jw),满足关系: ω

A =π-ω

C

和δ

s=δp=δ,或者说半带滤波器的阻带宽度(π-ω

A )与通带宽度ω

C

是相等的,且通

带纹波δs与阻带纹波δp也相等,如图3.11。

基于数字下变频的低通滤波器设计 一、实验原理 窗口设计法是根据给定的指标所要求的频响H d(e jw),求出相应的序列h d(n)。其长度一般为无限长,为了满足FIR滤波器设计的要求,得到一个有限长度的脉冲响应,可用一定形状的窗口函数截取成有限长的h(n),以此来逼近理想的h d (n),从而使频率响应H d(e jw)也逼近理想的频率响应H d(e jw)。 频率采样法是指在脉冲响应h(n)为有限长度的条件下,根据频率取样定理,对所要求的频率响应进行取样,从样点中恢复原来的频率特性,达到设计滤波器的目的。 二、实验设计方法 窗函数设计技术是FIR滤波器设计的主要方法之一,由于其运算简便,物理意义直观,已成为工程实际中应用最广泛的方法。 在设计一个滤波器之前,必须首先确定一些技术指标。这些技术指标需要根据工程实际的需要来制定。在很多实际应用中,数字滤波器常常被用来实现选频操作。因此,指标的形式一般确定为频域中幅度和相位响应。幅度指标主要以两种方式给出,第一种是绝对指标,它提供对幅度响应函数的要求,这些指标一般应用于FIR滤波器的设计;第二种指标是相对指标,它以分贝值的形式给出要求,在工程实际中,这种指标最受欢迎。对于相位响应指标形式,通常希望系统在

通频带中具有线性相位。运用相位响应指标进行滤波器设计具有如下优点:①只包含实数算法,不涉及复数运算;②不存在延迟失真,只有固定数量的延迟;③长度为M的滤波器(阶数为M-1),它的计算量为M/2数量级。本文中FIR滤波器的设计就是着重于线性相位滤波器的设计。 为了建立一个具有线性相位和稳定的非递归特性的有限脉冲响应滤波器即FIR滤波器,要考虑两个方面:一是使用有限长的单位取样响应来逼近理想低通,二是单位取样响应对(N一1)/2对称,从而保证线性相位。

一种新型直接抽取算法的数字下变频设计 【摘要】为了简化卫星导航接收机框架,提出一种基于数字信号抽取的下变频方法。通过分离和累计法,人们发现了一种具有高频率数字载波信号的直接下变频方法。这种方法不仅具有结构简单、速度高和计算简单的特点,还能够很好的保持导航电文和多普勒信息,但这种方法有可能会使S/N信号和接收机的灵敏度降低:分析和仿真结果显示,它对接收机的定位灵敏度没有任何的影响。 【关键词】数字下变频;抽取算法;BPSK 1.引言 卫星导航接收机通常采用超外差的体系结构,在模拟的超外差接收机前端,许多的数字下变频是通过使用混频器和本地振荡器接收IF信号。低通滤波器消除了高频率分量,然后便可以得到不同频率的下变频信号,与低IF模式和零IF 模式相比,它具有高增益、高抑制和无本地振荡泄漏的特点,但是它的结构复杂和功率损耗较高[2]。 数字接收器具有高集成度、低功耗和低成本的特点,因此,它是无线电接收器的发展趋势[3]。数字下变频方法能够通过数字调音台、CIC滤波器或者重采样方法把一个高频率信号转变成低频率信号[4-5]。在本文中,抽取算法和提取信号是为了得到BPSK调制信号的下变频,与CORDIC方法相比,数字下变频方法只需要添加点操作就可以节省许多的时间和CPU空间。在处理导航数据或CDMA数据时,除了采样IF算法外,还需要重采样和复杂的数字算法。 2.抽取算法的原理 假设在模数转换之前,信号的频率为,抽样频率是。对于BPSK调制的信号,载波频率和振幅是不变的。经过A/D转换后,信号为是一个行向量,向量的位数等于A/D转换器的位数。无相位转换的载波抽样信号有如下关系: 如果相位在周期发生转换,并且是在和周期之间发生,由于相位变化是,最后的抽样值不如前个抽样值,。如果>,在抽取的过程中相变不会发生,那么便会在下个周期发生。因此,在抽取期发生的相变将提前或推迟以适应周期的开始或结束,从而导致部分代码相位误差。 3.灵敏度和准确度的影响 抽取和量化将会造成信号信息的丢失,此量化误差是依赖于量化比特数和阀值。通过选择合适的阀值可以使量化的损失减少,通常情况下,实验中的量化是0.55dB[7]。抽取值可以改变相变的位置。如果累计的最大数目是,它可以使相位的过渡时间提前或滞后正确点的,是抽样周期。相变错误也影响相关积分结果,这会使接收器的灵敏度降低。考虑了多普勒频移,相变误差均匀分布的区域是,

2011 年第 4 期 (总第 140 期)

大 众 科 技

DA ZHONG KE JI

No.4, 2011 (Cumulatively No.140)

雷洪涛 1

张桂花

2

(1.电子科技大学,四川 成都 611731;2.成都火控技术中心,四川 成都 610000)

【摘 要】文章探讨了一种利用 Matlab 和 System Generator 联合设计宽带数字上变频器的实现方法。先利用 Matlab 自带的 Fdatool 工具生成数字变频器中滤波器所需要的系数,然后利用 Xilinx 的设计工具 System Generator 进行模块设计和仿真,最后 将代码自动生成,加载到 FPGA 中进行验证。 【关键词】数字上变频;内插;半带滤波器;软件无线电 【中图分类号】TP311.5 【文献标识码】A 【文章编号】1008-1151(2011)04-0011-02

(一)引言

RRU(Remote Radio Uint)是现代无线通信基站的重要组 成部分。它可将低采样率的基带信号通过内插提高采样率, 在通过消峰和数字预失真(DPD)之后,送到天线口。数字上 变频器则是 RRU 的重要模块之一。传统的 RRU 大多采用专用 的芯片来实现数字上变频的功能,其优点是集成度高,应用 方便,但是研制周期长,不够灵活的特点并不符合理想的软 件无线电系统,而 FPGA 则具有高速率、可编程、功耗低等特 点,并且可以通过快速修改设计来适应不同的系统和使用环 境,非常适合实现数字上变频器。 本文将利用 Xilinx 的 FPGA 和 SystemGen 软件和 Matlab 联合开发基于 TD-LTE 制式下单载 20M 带宽的数字上变频器 (DUC) 。这种设计不仅能简化硬件电路,缩短开发流程,而 且由于 FPGA 的可编程性,可以实现设计的快速修改和移植, 降低开发成本,是现在最为可行的一种设计方法。

图1

数字上变频器设计方案

DUC 提供了频谱整型和提高采样率的功能, 它的设计必须满足 3GPP 的标准和要求。不仅要满足 20M 的宽带要求,而且还要 实现采样率的 3 倍提高,具体指标如表 1 所示。 表1

参数 带宽 输入采样率 输出采样率 EVM 纹波 阻带

DUC 设计要求

要求 20M 30.72Msps 92.16Msps <1% <0.1db >=80db

(二)数字上变频器的设计方案

数字上变频器(DUC)实现了从“复”基带(Baseband) 信号到“实”带通(Passband)信号的转换。因为从基带输 入的复基带信号采样率相对较低,通常是数字调制的符号率, 不能满足射频发射的要求。所以通常基带信号要经过滤波和 内插,然后被转换成一个更高的采样率,从而调制到 NCO 的 中频载波频率。由于 LTE 下行多采用零中频的方案,因此不 需要 NCO 进行混频,只需要进行滤波和内插。3GPP 标准规定 LTE 单载波 20M 带宽的基带采样率为 30.72Msps, 因此需要进 行 3 倍内插使得采样率达到 92.16Msps, 然后送到 DAC 进行模 拟转换。本文将完成一个 TDD-LTE 制式单载波 20M 带宽的宽 带无线数字上变频器的设计,其设计思路如图 1 所示。

(三)数字上变频滤波器设计

数字上变频器的滤波器分为通道滤波器和内插滤波器两 种,通道滤波器完成基带信号的频谱整型,通常由 FIR 实现。 内插滤波器完成信号采样率变换和滤波功能,可以用半带滤 波器来实现。 1.通道滤波器 基带信号首先要通过通道滤波器使得带外功率满足频谱 限制要求。因为 LTE 基带信号基于 OFDM 调制方式,输入到通 道滤波器的信号功率谱密度(PSD)从占用信号的带宽边缘开 始已经有了自然的衰减。但是由于原始基带信号只有大约

【收稿日期】2011-01-17 【作者简介】雷洪涛(1984-) ,男,电子科技大学硕士研究生,研究方向为软件无线电、SOC 片上系统;张桂花(1982-) , 女,成都火控技术中心助理工程师,研究方向为软件无线电、图形图像及多媒体技术、软件工程。

- 11 -

一、课程设计问题的提出: 试设计一数字下变频器,并用matlab 仿真; 二、二、解决问题的原理、技术方案解决问题的原理、技术方案解决问题的原理、技术方案以及以及matlab 验证验证: :数字下变频器的原理说明: 数字下变频器(D DC)是接收机A /D 变换后,首先要完成的处理工作,一般的DDC 由本地 振荡器(NCO)、混频器、低通滤波器和抽取器组成.主要作用:其一是把中频信号变为零中频信号;其二是降低采样率。从频谱上看,数字下变频将A/D 采样后信号从中频变换,到基带。这样的处理由两步完成:首先是将输入信号与正交载波相乘,然后进行数字滤波滤除不需要的频率分量。NCO ,混频器,数字滤波器速率要等于采样率,采样率低于600MHz ,很难实时的在FPGA 中进行处理。 数字下变频器的基本结构: NCO :产生正余弦序列,即I/Q 两路信号。 CIC 滤波器,适用于系统中的第一级抽取和进行大的抽取因子的抽取工作,并降低速率。FIR 滤波器,完成对整个信道的整形滤波。DDC 主要有三种实现途径:采用专用芯片、自制专用芯片、基于DSP 或FPGA 等通用芯片。

NCO采用的直接数字频率合成技术(DDS)是一种实用的频率合成技术,DDS由相位概念出发直接合成所需波形的一种新的频率合成技术。DDS合成技术采用了简便和有效的查表法。 运用matlab进行NCO的仿真: 程序: t=0:0.001*10^(-6):10^-6; I=110*cos(7*(10^7)*t-0.5*pi); subplot(2,1,1);plot(t,I);grid on; Q=110*sin(7*(10^7)*t+0.5*pi); subplot(2,1,2);plot(t,Q);grid on; 信号的频率为11.2MHz CIC滤波器: CIC滤波器,即级联积分梳状滤波器,具有结构简单,便于处理,运算速度快等特点。CIC 滤波器的积分器H1(Z)是不稳定系统,如果不采取措施,它们级联后会出现溢出现象。另外,

数字下变频仿真原理: 信号采样的频谱 调频信号:02 ()cos *(2/2)s x K t n f nt π=+ 00022 02 *cos(2/)cos(2)cos(2) cos(4*/2*/2)cos(*/2) s s s s x f n f f nt f nt f nt K t K t K t ππππ=+=++ 0002022 *sin(2/)cos(2)sin(2) sin(*/2*/2)sin(*/24) s s s s K t K t K x f n f f nt f nt f nt t ππππ+-=-+=-+ 因为f 0=30MHz ,整体向左平移30MHz 。 -40-20 带宽为5MHz 通过仿真得到()x n 的时域波形和频域波形,如下图所示。 clc;clear all;close all; f0=30e6; 中心频率 B=5e6; 带宽 T=30e-6; 脉冲宽度 fs=40e6; 采样频率 N=T*fs; 采样点数 K=B/T; 频率变换率 ts=1/fs; 采样周期

t=-T/2:ts:T/2-ts; x=cos(2*pi*(f0*t+K*t.^2/2)); figure(1); title('时域波形'); xlabel('point '); figure(2); plot(abs(fft(x))); title('频域波形'); xlabel('point'); I路信号和Q路信号: ddc_i = x.*cos(2*pi*f0*(1:N)/fs); I路信号ddc_q = -x.*sin(2*pi*f0*(1:N)/fs); Q路信号figure(3); subplot(211); plot(t,ddc_i);grid; title('I路波形');

通信系统中的数字上变频和下变频 数字上变频器(DUC)和数字下变频器(DDC)不仅仅是通信应用(如软件无线电)中的关键,而且在需要窄带信号高速流的应用中也是重要的。另外,DDC结构容易控制所有取样速率下的混淆防止分样。 让我们看看数字记录5MHz带宽(中心在50MHz)信号的问题。此信号可以是来自RF-IF模拟下变频器的信号或者是直接从天线接收的信号。为了满足尼奎斯特准则,我们需要以 105ms/s取样率取样此信号。然而,为了合理地捕获此信号,应该在较高的取样率(至少200ms/s)取样此信号。假设ADC为16位,在该速率下被取样的信号会产生400MB/s数据。也许更难办的是以这样高速率采集和存储数据缺乏商业可用的方案。大多数可用的PC基数字器仅能在大约几分之几秒内存储此数据。 数字下变频 DDC在持续时间期间可以数字记录RF信号。在此实例中,我们仅需要记录5MHz信号(中心频率50MHz),而不是ADC的整个尼奎斯特带宽。DDC允许除去其余数据,并降低数据率。在现场可编程门阵列(FPGA)中实现时,简单的数字下变频分为3个性质不同的步:频率变换、滤波和分样(图1)。 频率变换和滤波 第1步是频率变换。5MHz频带需要降低变换到基带,靠乘或与载频(fc)正弦信号混频实现这种变换。用数字控制振荡器(NCO)数字产生正弦波。NCO通常也称之为本机振荡器(LO),它可以在精确频率和相位下产生取样波形。 随着信号从50MHz变频到基带,信号拷贝也从50 MHz变频到100 MHz。基于此原因,新的基带信号必须滤波,去除较高频率的信号。然而,到此我们的任务没有完成。我们仍有1个在200ms/s取样的低频基带信号。传输额外不必要数据时不希望PC总线过载,我们重新取样信号来降低有效取样率。这靠分样实现,在规则的时间间隔内从数字化的信号中去除数据点。在此例中,取样从200ms/s下降到10ms/s,每20个取样去除19个取样。 防止混淆的分样 采用分样,数字化器的采集引擎继续以同样的最大速率进行取样。然而,仅有少量的采集点被存储、被取出和传输到PC,这降低取样率到所希望的水平。但是,此技术不是极简单的。 为便于说明,假定数字化器的最大取样率是100MS/s,使其尼奎斯特频率为50 MHz,而信号有两个分量:10 MHz基频和20MHz激励频率分量。若数字化器分辨率为14位,则在100MS/S总数据率是200MB/s,这远远高于PCI总线理论极限132MB/s。这是采用较低取样率(如25MS/s)的1个原因。现在尼奎斯特频率应该是12.5MHz。然而,20MHz频率分量混淆回到5MHz。现在,不可能告知信号实际上是否是5MHz信号或混淆到5MHz的另外较高频率信号(20MHz,30MHz,45MHz)。 解决此问题的1种方案是称之为防止混淆分样的增强分样技术。在此技术中,数字化器继续在100MS/s最高取样率下采集数据,但加1个低通数字滤波器,在分样前截止尼奎斯特频率(图2)。 正交数字下变频 图1所示DDC只适用于单维调制信号。这种信号的1个实例是AM无线电的双边带幅度调制信号,它用比实际所需两倍的带宽。这样的信号在低和高于载频是相同的。

第九章数字下变频的设计 数字下变频又称数字I、Q复解调。它广泛应用于雷达、声纳和无线电接收机中。数字下变 频的原理已经在第一章和第八章得到阐述。在本章中先介绍主要的数字下变频芯片,然后介绍 数字I、Q复解调板的设计。 第一节主要的数字下变频芯片 对于不同的厂商,数字下变频(digital down converter)芯片有时又被称为数字解调器(digital tuner)或数字接收信号处理器(digital receive signal processor) 。目前世界上生产数字下变频芯片 的厂家主要有GrayChip、Harris Semiconductor、Analog Device、National Semiconductor等,其 中GrayChip公司虽然是一个小公司,但它却是一个专门生产数字下变频ASIC芯片的专业公司。 其生产的品种多、功能全、是选择数字下变频芯片的首选公司。Harris公司生产数字下变频芯 片的历史也较长。由于其具备产生高速A/D变换器的功能,所以其数字下变频芯片和ADC芯 片配合良好,可以配套使用。由于软件无线电技术的发展和市场对数字接收机的大量需求,近 几年来,半导体芯片的头号厂商Analog Device和National Semiconductor也涉足数字下变频芯 片市场,并且发展势头非常迅猛。特别是生产ADC芯片的龙头老大Analog Device公司,凭借 其雄厚的模拟和数字电路芯片的设计和生产技术,开发了先进的数字接收器芯片AD6620和 AD6624。与此同时,Analog Device公司还将其新一代中频A/D转换器芯片和DSP芯片与其数 字下变频芯片相结合,提出了多套完整的数字接收机的完整解决方案。表9-1-1是市场上常用的 数字下变频芯片。 表9-1-1 常用的数字下变频芯片的对照表 名称AD6620 HSP50214 CLC5902 GC1012A 生产厂家ADI Harris NS Graychip 输入数据宽度16bit 16bit 16bit 12bit 输入数据速率65MHz 52MHz 52MHz 80MHz NCO精度0.02Hz 0.02Hz 0.02Hz 0.1Hz CIC5 CIC4 无 CIC滤波器CIC2 CIC5 固定系数FIR 系数FIR RAM系数FIR1, FIR滤波器 RAM 系数FIR RAM FIR2 随着软件无线电的发展,通信、雷达、声纳等领域将需要更多的数字下变频芯片,从而也 会出现更多的新芯片和厂家。 9-1-1. 窄带数字下变频芯片AD6620 AD6620数字接收器芯片主要由四部分组成,如图9-1-1所示,包括一个频率转换部分(NCO 和混频器)、两个固定系数的抽选滤波器、一个程控系数的抽选滤波器。

线性调频信号脉冲压缩-数字下变频程序DDC clc; clear all; close all; B=5e6; %%信号带宽 f0=30e6; %中频 fs=40e6; %采样频率 fs1=(20/3)*1e6; %%抽取后频率 T=24.9e-6; %%时宽 k=B/T; fk=127; %%做DDC时的低通滤波器的阶数 fid=fopen('20090724fc1yindao4-0.dat','r'); sss=fread(fid,32*4096,'int16'); fclose(fid); figure(100);plot(sss);grid on;xlabel('点数');ylabel('幅度');title('32个周期信号时域波形');grid on; L=length(sss); N=4096; R=fix(L/N); for r=1:R ss(r,:)=sss((r-1)*N+1:1:r*N); end figure(1);plot(ss(R,:));xlabel('点数');ylabel('幅度');title('信号时域波形');grid on; %%%%%%%%%%%%%%% 低通滤波器%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% ff=[0 1/8 1/4 1]; aa=[1 1 0 0]; b=firpm(fk,ff,aa); [h,w]=freqz(b,1,1024); % figure(2); % f=linspace(0,fs/2,1024); % plot(f/1e6,20*log10(abs(h)));xlabel('f/Mhz');ylabel('dB');title('低通滤波器的幅频响应');grid on; %%%%%%%%%%%%%%% DDC %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% ddcs=zeros(R,N+fk); for r=1:1:R n=-N/2:1:N/2-1; si=ss(r,:).*cos(2*pi*f0*n/fs); sq=-ss(r,:).*sin(2*pi*f0*n/fs); I=conv(si,b);

因为最近在做宽带数字信号的数字下变频,所以重点看了这一方面的论文。下文重点对IEEE 上的一篇论文Real-time wideband DDC based on parallel architecture in synthetic instrument 做了个读书笔记,并对自己在这方面的工作做了一个小结。 主要内容:这篇论文主要解决宽带数字中频信号处理过程中的一些问题,并行处理结构可以有效的降低采样率,多通道并行处理则可以有效降低处理成本。该论文介绍了数字下变频技术,分析了多种数控振荡器导致输出相位的不同,并总结了减少信噪比的误差因素,提供了特殊工程设计的指数分布依据。 图1DDC总体结构 原理:数字下变频器(D DC)是接收机A/D变换后,首先要完成的处理工作,一般的DDC 由本地振荡器(NCO)、混频器、低通滤波器和抽取器组成.主要作用:其一是把中频信号变为零中频信号;其二是降低采样率。从频谱上看,数字下变频将A/D采样后信号从中频变换,到基带。这样的处理由两步完成:首先是将输入信号与正交载波相乘,然后进行数字滤波滤除不需要的频率分量。NCO,混频器,数字滤波器速率要等于采样率,采样率低于600MHz,很难实时的在FPGA中进行处理。 结构: NCO:产生正余弦序列,即I/Q两路信号。 CIC滤波器,适用于系统中的第一级抽取和进行大的抽取因子的抽取工作,并降低速率。FIR滤波器,完成对整个信道的整形滤波。 DDC主要有三种实现途径:采用专用芯片、自制专用芯片、基于DSP或FPGA等通用芯片。论文主体: 1.并行处理结构:抽取滤波器模块通过多相滤波器结构降低采样率和实现低通滤波。 图2 DDC并行处理结构

基于FPGA的DDC(数字下变频)设计与实现

微系统设计、测试与控制 课程大作业之 基于FPGA的DDC(数字下变频) 的设计与仿真

摘要 (1) ABSTRACT (2) 第一章绪论 (3) 1.1 数字下变频(DDC)研究背景 (3) 1.2 DDC概述 (4) 1.3 本文研究内容和结构安排 (5) 第二章数字下变频(DDC)基础理论 (7) 2.1 数字下变频器 (7) 2.1.1 数字变频的基本原理与结构 (7) 2.1.2影响数字变频器性能的主要因素7 2.2 数字信号采样理论 (8) 2.2.1低通信号采样理论 (8) 2.2.2 带通信号采样理论 (9) 2.3 数字正交检波 (10) 2.3.1 低通滤波法 (10) 2.3.2 多相滤波结构变换法 (11) 2.4 多抽样率数字信号处理理论 (13)

2.4.1 整数倍抽取和内插 (13) 2.4.2 多抽样率系统的恒等变换 (16) 2.4.3 多相滤波结构 (17) 2.5 相关算法介绍 (19) 2.5.1 CORDIC算法 (19) 2.5.2 FIR滤波器 (21) 2.6 本章小结 (22) 第三章数字下变频(DDC)各模块设计 (23) 3.1 数字下变频的基本实现方案 (23) 3.2 基于DDS的数控振荡器的设计 (23) 3.2.1 混频器模块设计 (23) 3.2.2 DDS的特点 (25) 3.3抽取滤波 (27) 3.4 本章小结 (29) 第四章数字下变频器设计验证和逻辑综合 (30) 4.1基于DDS的数控振荡器的仿真和验证30 4.2 FIR滤波器的仿真和验证 (32)

用FPGA实现数字下变频 杨力生,谭晓衡,杨士中 (重庆大学通信工程学院,重庆 400044) 摘要:在接收信号的数字化、软化的实现中,数字下变频起着重要的作用。本文首先介绍了数字下变频的组成结构,然后详细分析了数字下变频的工作原理,描述了在实现数字下变频时,设计方案所采用的高效滤波器——CIC滤波器和多相抽取滤波器的结构和原理。最后,用通过Simulink对数字下变频的性能进行了仿真。在仿真的基础上使用Insight公司的FPGA开发系统,用测试电路实测了数字下变频的性能。 关键词:数字下变频器;FPGA;CIC数字滤波器;多相滤波器 Realize Digital Downconversion by FPGA YANG Li-sheng, TAN Xiao-heng, YANG Shi-zhong (Communication Engineering School, Chongqing University, Chongqing400044, China) Abstract: Digital downcoversion plays a key role in the digitized and software-oriented process of the received signal. First, the architecture of the digital downconvertor (DDC) is introduced.Then the operational principle of DDC is analysed.At the same time, the efficient structure of digital filter is described in which DDC is adopted.Finally, the performance simulation results of the DDC is given by Simulink, and on this base,the perfomance of DDC is tested with the FPGA devoloping system of Insight corp. Keywords:Digital downcovertor; FPGA;CIC digital filter;Polyphase filter 一、序言 在数字接收机中,数字下变频器(DDC)一般执行信道的访问功能。DDC接收经过高速采样的中频信号,将所需的频带下变为基带。现代基站收发器为了支持多载波环境或实现下变频,以便将很多窄带信道组合成一个宽带的数字信号,常常需要大量的DDC。DDC通常位于信号处理链的前端,靠近A/D,一般要求DDC 支持100 MSPS以上的采样率。 数字下变频由数字振荡器、数字乘法器、数字滤波器三部分组成,其组成的系统框图如图1所示。

基于AD6620的数字下变频(DDC)的频率 变换器 O引言AD6620是一个宽带中频到基带的解调器。它的内部信号处理单元由四个串联单元组成。分别为频率变换单元、二阶固定系数梳状滤波抽取滤波器(CIC2)单元、五阶固定系数梳状滤波抽取滤波器(CIC5)单元和一个系数可编程的RAM 系数抽取滤波器(RCF)单元。通过串行微处理器接口可以完成对芯片的编程和控制。AD6620具有16位线性比特补码输入(另加3bit指数输入),其单信道实数输入模式的最大输入数据速率可高达67Msps,双信道实数输入模式与 O 引言 AD6620是一个宽带中频到基带的解调器。它的内部信号处理单元由四个串联单元组成。分别为频率变换单元、二阶固定系数梳状滤波抽取滤波器(CIC2)单元、五阶固定系数梳状滤波抽取滤波器(CIC5)单元和一个系数可编程的RAM系数抽取滤波器(RCF)单元。通过串行微处理器接口可以完成对芯片的编程和控制。 AD6620具有16位线性比特补码输入(另加3bit指数输入),其单信道实数输入模式的最大输入数据速率可高达67 Msps,双信道实数输入模式与单信道复数 输入模式的最大输入数据速率高达33.5 Msps。同时,AD6620还具有可编程抽取FIR滤波器与增益控制功能,抽取率在2~163 84之间可编程;输出具有并行、串行两种输出模式,并行模式为16比特补码输出。 1 频率变换器的原理及配置 实现数字下变频(DDC)的频率变换器通常由两个16 bit乘法器和32 bit的数控振频器(NCO)组成。数控振荡器产生的本振信号频率的分辨率可达 ,并可产生 的本振信号。NCO利用数字频率合成器(DDS),并由频率控制字寄存器、相位控制字寄存器、相位累加器和正弦查找表组成,可以灵活地控制本振信号的振荡频率和初始相位。这一级单元可完成对输入信号从射频(IF)到基带的频率搬移。

FPGA数字上变频总结 一、上变频要求: 模拟器数字中频从20.42MHz提高到70.42MHz。 二、两种方案选择: 第一种方案:内插+低通滤波器+混频器+带通滤波器 为了使得中频输出f0=70.42M,根据奈奎斯特定理,采样频率至少为2f0,因此FPGA内插时工作时钟选择150M可满足要求,同时原来模拟器使用的62M 工作时钟更改为75M,即可进行2倍数字内插。整体结构图如下图1所示。 图1 整体结构图 (1)数字内插模块: 内插的作用是提升采样率,将75MHz时钟送来的采样信号按照150MHz时钟等间隔地在两个采样点之间插入一个零值,采样率从75MHz变为150MHz。 内插前后信号matlab仿真频谱图分别如图2和图3所示。

图2 内插前 图3 内插后 (2)低通滤波器模块: 数字内插后会得到高频的镜像频率(54.58MHz ),因此需进行低通滤波滤除 -4 -3-2-10123 4 x 10 7 0500 1000 1500 2000 2500 3000 -8 -6 -4 -2 2 4 6 8 x 10 7 020040060080010001200140016001800 2000

高频分量。 低通滤波后matlab仿真频谱图如图4所示。 x 107 图4 低通滤波后 (3)混频模块: FPGA在150M的工作时钟下,利用NCO生成一个50MHz的载波,然后与内插滤波后的20.42M中频进行相乘混频,混频后得到70.42M和29.58的两个频率的载波。 混频输出matlab仿真频谱图如图5所示。 x 107 图5 混频输出

示波器的DDC(数字下变频)技术详解 如今随着电子产品设计的日趋复杂,DDC介绍R&S示波器硬件实现的DDC3.1 I/Q解调中的DDC3.2 频谱分析中的DDC 示波器频谱分析功能一般采用FFT(Fast Fourier Transformation)即快速傅里叶变换。传统数字示波器的频谱分析原理框图如图13所示。 图13 传统数字示波器频谱分析框图 模拟信号经过ADC后变成数字信号,之后选择不同的窗函数进行加窗处理,最后直接做FFT将信号变换到频域。通过该种处理方式得到的频谱范围为0Hz至最大频率(通常数值上等于ADC采样率的一半),例如ADC采样率为5GSa/s,那么FFT得到的频谱范围为0Hz至2.5GHz。如果要观测某一段的频谱,则通过软件显示放大(Zoom)的方式将频谱放大显示到该频段。这种传统示波器频谱分析方式的好处在于,所有处理过程采用软件计算,且算法简单,因此便于实现。但如果追求更快的实时频谱测量或者更高精度的频谱分析,这种传统的处理方式就会显得非常困难。由于采用全软件的处理方式以及一直是对整个频率范围(0Hz至最大频率)做计算,因此处理速度会很慢,无法做到实时或者准实时的频谱分析。另外在示波器设置方面也会很复杂,需要不断的调整时域参数(如时基、采样率等)来满足需要的频域参数设置。最重要的是,受到示波器存储深度的限制,并且通常使用的FFT点数只有几K,因此频率分辨率即最小能区分的频率大小会非常有限,通常情况下很难达到一个理想的频率分辨率。 一般来讲,频率分辨率有两种解释。一种解释是,表示在FFT中,两个相邻频率点间的最小频率间隔,如公式(5)所示:?f = fs / N = 1 / t (5) 其中,?f表示频率分辨率,fs表示ADC采样频率,N表示FFT的计算点数,t表示采集信号的时间长度,也就是捕获时间。可以看出,信号采集时间t越长,频率分辨率?f越小,也就是频率分辨力就越好。 第二种解释是,频率分辨率可以用分辨率带宽(RBW)来表示。RBW定义为窗函数主瓣3dB带宽,如图14所示:

基于数字下变频的低通滤波器设计 周遐1金瑞2钟思佳3李瑞锋 4(昆明冶金高等专科学校自动化与电力学院云南昆明650033) 摘要:本文在了解数字下变频技术的基础上,对数字下变频器中的低通滤波器的结构进行了研究,然后先用MATLAB 软件根据对滤波器结构的分析进行了具体的设计,以得到VHDL 程序语言设计的相关参数和对滤波器性能的分析,最后对结果进行分析和总结。 关键词:数字低通滤波器;MATLAB ;FIR Based on DDC low pass filter design Zhou Xia Jin Rui Zhong Si-jia LI rui-feng (The faculty of Automation and Electric power,kunming Metallurgy college,Kunming, 650033,China ) Abstract:This article in understood the DDC technology in the foundation,has conducted the research to in the DDC low pass filter structure,then used the MATLAB software basis to carry on the concrete design first to the filter structure analysis,by obtained the VHDL program language design related parameter and to the filter performance analysis,finally carried on the analysis and the summary to the result. Key words :digital lowpass filter ;MATLAB ;FIR 0引言 现行的软件无线电实现方案大多采用数字变频技术,通过对数字信号的采样率进行变换,以缓解DSP 处理速度的压力。数字下变频,就是通过混频、多级抽取滤波、重采样等步骤,降低射频带通采样信号或中频采样信号的采样频率,从而使DSP 进行实时信号处理。1 数字下变频与数字低通滤波器1.1数字下变频技术 数字下变频技术是数字接收机的核心技术之一,它包括数字混频正交变换、抽取及高效率数字滤波等。其中数字混频正交变换部分完成频谱搬移工作,抽取改变采样率,而高效数字滤波保证信号抽取前后的抗混叠问题。从工作原理讲,数字下变频与模拟下变频是一样的,就是输入信号与一个本地振荡信号混频(相乘),再通过低通滤波器滤除混频过程产生的带外信号。 图一:数字下变频基本结构 目前有很多实现DDC 功能的专用器件已经商品化,如HSP50214B ,AD6620AS 等等,1周遐(1959~),男,1982年毕业于云南大学,高级工程师副教授研究方向:电子技术、通信技术NCO 抽取滤波抽取滤波cos sin I Q 数字 中频

*收稿日期:2006-09-11 文章编号:1008-8652(2007)02-84-06一种基于FPGA 的数字下变频方法 涂维政 刘书明 (西安电子科技大学 西安 710071) =摘要> 提出用FPGA 器件实现一个完整的数字下变频系统的方法,给出VerilogH DL 语言 的描述,实现高效的运算结构,减小了运算量,提高了系统性能。本系统已经在某型气象雷达的数字接收系统中得到采用,参数得到验证,性能优良。 关键词:FPGA ;VerilogH DL;欠采样技术;数字下变频;多抽样率系统 中图分类号:T N74211 文献标识码:A A Method of Digital Down Converting Based on FPGA T u Weizheng Liu Shuming (X idian Univ ersity ,X i .an,710071) Abstract :A method of using FPGA device to realize dig ital dow n converting system is presented,and the descr iptio n of Verilog H DL language is g iv en so that the hig h efficiency operational structure is fu-l filled,and the oper and is reduced and the system perform ance is enhanced.T his m ethod has been adopted in the digital receiving subsy stem of a certain m eteoro logical radar,and the specificatio ns are verified and the perfo rmance is perfect. Keywords :FPGA;Verilog H DL;under sampling techno log y;digital dow n converter;multiple sam -pling rate system 随着数字技术的飞速进步和发展,FPGA 器件因其高速、可编程、模块化的特点而被大量采用。同时,诸如数字下变频等一系列新的数字信号处理方法的提出,为降低系统成本提供了可能,相关的多抽样率系统理论,更是大大的降低了数字系统的运算量,明显的提升了系统性能。 本文论述数字下变频技术的一种FPGA 实现方法,用比较低的系统成本,实现比较高的谱分辨率的数字接收系统,完成对气象信号的有效处理。实际的系统选用48M H z 时钟对60MH z 的雷达中频信号采样,然后经过FPGA 的数字下变频及其滤波处理,得到信号的包络和相位信息。 1 欠采样技术 为了降低对ADC 器件的要求,对于低通、带通信号,可以用带通信号的采样方法,在低于奈奎斯特采样率时进行数模转换:只要采样率不低于两倍信号带宽f h -f l ,时域的采样就不会导致信号频谱的混叠,如公式(1)所示: 2f h N +1[f S [2f l N (1)其中,N 为自然数,且1[N [f l f h -f l 。84

大连理工大学 硕士学位论文 软件无线电接收机中可编程数字下变频器的研究与设计 姓名:李武翰 申请学位级别:硕士 专业:通信与信息系统 指导教师:刘军民 20040314

摘要 软件无线电的中心思想是构造一个具有开放性、标准化和模块化的通用硬件平台,将宽带A/D和D/A转换器尽可能靠近天线,用软件完成各种通信功能,以研制出高度灵活性和适应性的无线通信系统。A/D变换器制造技术的进步,其工作带宽覆盖到中频频段,并具有较高的采样频率和足够大的动态范围,从而使无线电接收机技术由基带数字化向中频数字化方向发展,因此,实现基于带通采样定理的宽带数字中频软件无线电接收机成为可能。 本文设计和实现了基于FPGA的可编程数字下变频器,用于宽带数字中频软件无线电接收机中,完成数字下变频、信道提取、数据抽取,采样率转换和信道整形滤波等功能。采用自上向下的模块化设计方法,将PDDC的功能划分为基本单元,实现这些功能模块并组成模块库。在具体应用时,优化配置各个模块来满足具体无线通信系统性能的要求。这样做比传统ASIC数字下变频器具有更好的可编程性和灵活性。 PDDC采用基于多相滤波数字正交变换的下变频结构,利用Cyclone系列FPGA中内嵌的可编程锁相环采样时钟合成器产生特定的采样频率,实现信道选择和数字下变频。用全字并行分布式(DA)算法实现时间校J下滤波器。将可编程抽取、插值器与多级积分梳状滤波器(cIc)相配合,实现高效数字抽取和插值模块。改进并实现了CIC通带补偿滤波器模块,用来减小多级CIC的通带误差所导致的信号失真。设计和实现多个半带滤波器抽取模块,组合成多级抽取器实现2‘倍抽耿。使用正则有符号数字量(CSD)表示法实现半带抽取滤波器模块。改进简化加法器图(RAG)算法用来实现平方根升余弦脉冲成形器等常系数FIR滤波器。设计和实现了多路时分复用转蜀型FIR滤波器作为信道整形滤波器,充分利用了FPGA的并行处理能力,提高了资源利用率。以上各模块用FPGA31:发工具进行了功能仿真和时序分析,形成软核,便于移植和重用,缩短相关项目设计周期。最后将本文设计的PDDC应用于GSM/EDGE/wCDMA多模数字中频接收机中,用ADS2002C进行系统仿真,满足系统性能要求。 关键词:数字下变频:数宇正交变换:多相滤波;FP6A:抽取和内插:FIR滤波器