基于DSP 的数据采集与处理系统的设计

张 菊,张淑娥

(华北电力大学电子与通信工程系,河北保定071000)

摘要:基于数字信号处理(DSP )的数据采集系统相对于基于单片机的数据采集系统更能够满足

电力系统在精确度和实时性方面的要求。文章自行设计了一个基于DSP 的数据采集与处理系统,对DSP 芯片T MS320LF2407和A /D 转换芯片ADS8364的特点做了介绍,重点阐述了ADS8364的硬件设计以及与DSP 的接口电路。此系统主要完成电力系统中模拟信号的精确采集,实时监测电力系统的运行状况,在故障时可向上位机报警,同时记录下实时运行数据。这种高效的数据采集与处理系统,可广泛地应用于各种智能仪表、自动化控制设备中,有着非常好的市场应用前景。

关键词:数字信号处理;ADS8364;数据采集

中图分类号:T N911.72

文献标识码:B 文章编号:1005-7641(2006)01-0070-04

收稿日期:2005-05-10;修回日期:2005-06-09

0 引言

在电力系统中,对三相电压、三相电流精确快

速地采集、计算和存储,是进行数字信号处理分析、电能质量分析、故障类型分析、故障位置分析等的基础。要完成这些功能,不仅要求CP U 的处理速度快,而且对A /D 的转换速度和精度也有一定的要求。传统的数据采集与处理多采用单片机实现。但单片机自身的结构特点限制了它的处理速度和精度,尤其在数字信号处理方面,大量的乘和累加计算会大大地影响系统的性能。所以随着数字信号处理(DSP,D igital Signal Pr ocessing )技术的出现,特别是近几年DSP 芯片的价格不断下降和其开发工具日臻成熟,人们越来越多地选择DSP 处理器取代单片机作为单片控制系统的核心,采用T MS320LF2407和ADS8364完成高速、高精度的数据采集。T MS320LF2407的单指令周期只有25ns,ADS8364是16位A /D 转换器,转换时间最少可达3.2μs,该系统在实时性和精度方面比较适合电力系统中高精度数据采集处理的需要。

1 基于D S P 的数据采集与处理系统设计

1.1 系统的主要功能

(1)采集计算三相电压、三相电流的值。(2)实时监测电力系统运行状况。

(3)以月为周期,记录电力系统运行不正常时

的值,包括各相电压越上限时间、各相电压越下限时间、各相电压缺相时间、各相电压越限值、各相电流过负荷时间、各相电流过负荷值、停电时间、停电次数等,并主动上报事故告警。其中,电压的上限、下限值和电流的过负荷值可修改。

(4)可通过RS -232标准串行口和上位机通信,数据格式和功能应符合电力系统的101规约;大量的数据传输则可采用US B 总线接口。

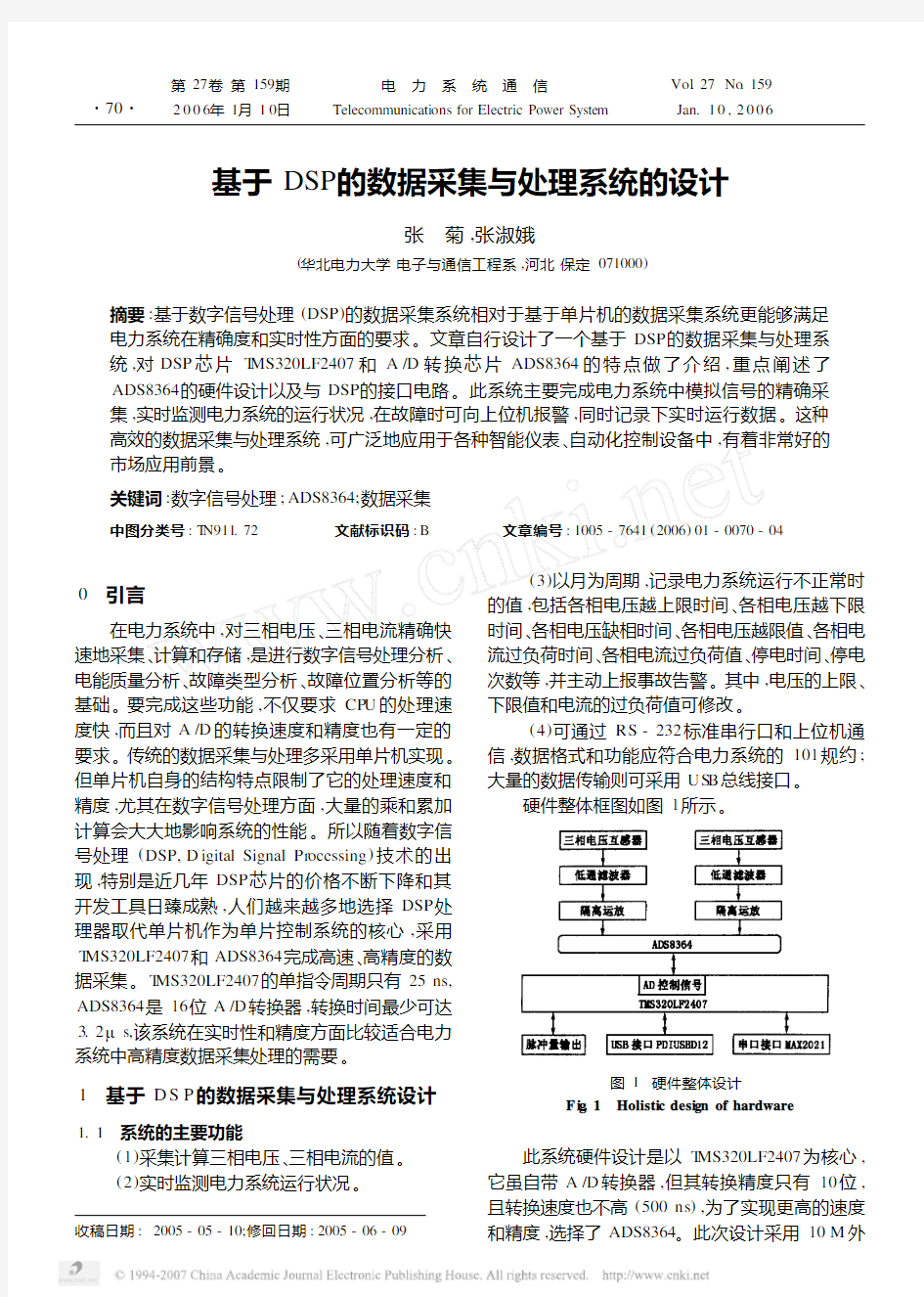

硬件整体框图如图1所示

。

图1 硬件整体设计

F i g .1 Holisti c desi gn of hardware

此系统硬件设计是以T MS320LF2407为核心,它虽自带A /D 转换器,但其转换精度只有10位,且转换速度也不高(500ns ),为了实现更高的速度和精度,选择了ADS8364。此次设计采用10M 外

?

07?第27卷第159期 电 力 系 统 通 信 Vol .27No .159

2006年1月10日 Telecommunicati ons for Electric Power Syste m Jan.10,200

6

部晶振,外扩了64k RAM 。预留了2个开关量的输出,以满足一定的控制功能。在模拟量输入前向通道中,分别将电压信号、电流信号输入电压互感器和电流互感器(互感器的输出均为-5~+5V ),再经过低通滤波器、运算放大器以及电平平移电路,输入到ADS8364(电压为0~+5V 。芯片MAX202和P D I U S BD12分别驱动RS -232标准通信和US B 总线接口。

1.2 T M S 320L F2407简介

T MS320LF240x 是DSP 控制器24x 系列的新

成员,是T MS320C2000T M

平台下的一种定点DSP 芯片。它集成了数字信号处理和电机运动的数字化控制功能,是高效、高精度的数字控制器。T MS320LF2407DSP 的特点是采用高性能静态C MOS 技术,使得供电电压降为3.3V ,减少了控制器的功耗;40M I/s 的执行速度使得指令周期缩短为25ns;16bit 地址总线和16bit 数据总线,可扩展的外部存储器总共192kbit 的空间(64kbit 程序存储器空间,64kbit 的数据存储器空间,64kbit I/O 寻址空间);片内有高达32kbit 字的F LASH 程序存储器,为多种用途的产品提供了经济的可编程解决方案,256kbit 字的引导ROM ,使在线编程更加方便;2个事件管理器模块EVA 和EVB ,每个均包括2个16bit 通用定时器和8个16bit 的脉宽调制(P WM )通道;40个可单独编程或复用的通用输入/输出引脚(GP I O )等。1.3AD S 8364简介

美国某公司的ADS8364,是一种高速、低功耗、双16bA /D 转换器,有6个模拟量输入通道。它由独立的5V AV DD 和DV DD 供电,转换结果通过内置的输出缓冲电路送出。此输出缓冲电路可由DV DD 驱动,或者通过独立的BV DD 驱动。BV DD 的范围较宽为2.7~5.5V,这使得存在多种电源环境时,可以灵活配置。它有6个完全相同的采样保持电路,分成A 、B 、C 3组,每一组都由1个HOLD 引脚控制。内置2.5V 的参考电压,可作为模拟量输入前向通道中电压极性转换和电平平移电路的基准。ADS8364可从外部引入最大5MHz 的时钟频率,此时采样时间是0.8μs,转换时间只有3.2μs,A /D 的最大采样率达250k,要达到此值,可在下一次转换开始时读取上一次转换的结果。

2 T M S 320LF2407与ADS 8364的接口设计

T MS320LF2407与ADS8364的接口如图2

所示。

图2 DSP 和AD 的接口

F i g .2 I n terface between of D SP and AD

(1)AD 缓冲区供电电压的选择

ADS8364的内部输出缓冲器供电电压BV DD 能

够十分灵活地配置,此次设计中,3.3V 电源同时供电给DSP 和ADS8364的内部输出缓冲器,所以二者接口无需电平转换,BV DD 直接和DV DD 相连。

(2)AD 片选信号的设置

DSP 的外部I/O 空间选通引脚I S,总保持为高电平,除非选通外部的I/O 空间,所以,将它和地址线A15一起选通A /D 的片选信号CS;读有效RE 直接和A /D 芯片的RD 相连。

(3)同步采样的控制

电力系统中,如果只要求计算模拟量的有效

值,而不要求计算相位,那么即使对三相电压和三相电流不能实现同时采样,但基本上也能达到测量精度要求。但在某些情况下,对“同步”的要求就比较苛刻,例如计算三相电压之间、三相电流之间或电压与电流之间的相位差时,就必须保证三相电压、三相电流是同时采样。为了达到此项要求,选择了具有6个输入通道的ADS8364。ADS8364的HOLDA 、HOLDB 、HOLDC 引脚是低脉冲触发有效,若它们同时被置低,则能对6个模拟量输入通道同时采样。

DSP 的复用引脚TI P WM /T1C MP /I O P B4用作T1C MP 功能,设置TI C MP 为低有效,即当通用定时器1计数值和预置的通用定时器1比较寄存器的值匹配时,产生T1C MP 信号,AD 的6个模拟量输入通道同时采样1次,同时,在软件中将通用计数器1清零,重新计数。

通用定时器1比较寄存器的值如下设置:以工频50Hz 为例,设1个周期采集64个点,则采样频

?

17? ?设计与开发? 张 菊,等 基于DSP

的数据采集与处理系统的设计

率为3.2kHz,远远低于AD的最大采样率。2次采样间隔为312.5μs。CP U时钟频率10M,周期为0.1μs,设置通用定时器1的预定标因子为1,初值为0,比较寄存器的值为3124,即通用定时器1计数至3124,即经过了312.5μs时,又一次采样开始,从而达到循环采样的目的。

(4)DSP的复用引脚X I N T1/I O P A2用作X I N T1功能,它由A/D的EOC引脚引起中断,在相应的中断服务子程序中,顺序读取AD的转换结果。

(5)ADS8364的数据通道的选择

ADS8364估值模块用4根地址线访问数据转换器,可选A2、A3、A4、A5或A12、A13、A14、A15,此设计选择A12、A13、A14、A15。其中,低三位地址线用来控制ADS8364的A0、A1、A2(不同的地址实现的功能如表1所示),最高位地址线可和I S 信号控制ADS8364的片选信号CS。此次设计六路通道循环采样转换,即应选择“CYCLE”模式, A0、A1、A2的值固定为“011”如图2所示,A1、A2连接供电电平,A1接地。所以没有利用A12、A13、A14的控制。

(6)AD复位信号的控制

DSP的复用引脚B I O/I O PC1用作I O PC1功能,控制A/D芯片的复位引脚RESET。方法是:系统软件初始化时,将I O PC1置高,待系统时钟稳定后,令其产生1个低脉冲,即对ADS8364可靠复位。之所以特地在系统初始化时利用软件使ADS8364复位,是因为这样做可以保证DSP从A/D 中读出的数据转换结果顺序依次是通道A0、A1、B0、B1、C0、C1,否则通道的顺序是随机的,无法存储数据。

表1 ADS8364EVM地址定义

Table1 Address def i n e of AD S8364EV M

地址功能

8000选择通道A0

9000选择通道A1

A000选择通道B0

B000选择通道B1

C000选择通道C0

D000选择通道C1

E000选择“CYC LE”模式

F000选择“F I F O”模式4 编程举例

下面是X I N T1中断服务子程序中读取AD转换结果的程序,采用C语言编写,在CCS2.12环境中调试通过。

先定义一些变量:

unsigned int ADC_result[6];/存转换结果/

v olatile int3ADC_address=(volatile int3) 0e000;/AD的读地址/

初始化定时器1:

v oid init_ti m er1()

{

3T1CNT=0x00;//Ti m er1的计数器清零

3T1CON=0x1002;//Ti m er1为连续增计数模式,预分频值为1,使用内部时钟,使能定时器比较操作,比较寄存器的值当计数器为零时重装载3T1C MP=0x0c34;//Ti m er1的比较寄存器的值根据3124us时延和预分频值确定

3I FR=3I FR|0x01;//清除I N T1中断标志3I M R=3I M R|0x01;//允许I N T1中断

3T1CON=3T1CON|0x40;//启动Ti m er1}

外部中断1中断服务子程序中读取转换结果的部分程序:

unsigned int I;

f or(i=0;i<6;i++)

{ADC_result[i]=3ADC_address;

}

这样,6个通道的转换结果就存在了数组ADC _result中,进而可做相应处理。ADS8364的工作时序如图3所示

。

图3 ADS8364波形图

F i g.3 W ave chart of AD S8364

?

2

7

? 电 力 系 统 通 信 2006,27(159

)

5 结束语

以上设计的电力信号采集与处理系统模拟量的计算精度为0.1级,达到了比较好的性能;能够和上位机通过R S -232标准通信,波特率可为1200、2400或9600。在此基础上,可进行各种参数,诸如有功功率、无功功率、功率因数以及谐波等的分析和计算,并传给上位机,同时,还可完成许多控制功能。这种高效的数据采集与处理系统可广泛应用于各种智能仪表、自动化控制设备、配电网

终端设备中,有着非常好的市场前景。

(S )参考文献:

[1] 郑力新,周凯汀,方瑞明,等.DSP 多路同步数据采集

板设计[J ].华侨大学学报(自然科学版),2004,25

(2):145-149.

[2] 苏清,吴顺君,李真芳,等.高性能DSP 与高速实时信

号处理[M ].西安:西安电子科技大学出版社,2002.

[3] 刘和平,王维俊,江渝,等.T M S320LF240x DSP C 语言

开发应用[M ].北京:北京航空航天大学出版社,2002.

[4] T o m Hendrick .I nterfacing the ADS 8364t o the T MS 320F2812

DSP,TI .S LAA163[R ].Texas I nstru ments I nc .,2002.12.[5] Tom Hendrick .Soft w are Contr ol of the ADS8364,TI .

S LAA155[R ].Texas I nstru ments I nc .,2002,8.张 菊(1975-),女,河北辛集人,硕士研究生,专业是通信与信息系统。

张淑娥(1964-),女,辽宁沈阳人,副教授,主要从事通信方面的教学和科研工作。

D esi gn of da t a acqu i r i n g and processi n g system ba sed on D SP

ZHAN G Ju,ZHAN G Shu 2e

(Depart m ent of Electr on and Communicati on Engineering ,North China Electric Po wer University,Baoding 071000,China )Abstract:The data acquiring syste m based on DSP can satisfy the de mands of higher accuracy and real ti m e in electric power system if compared with the syste m based on m icr ocontr oller .This paper intr oduces the design of data acquiring and p r ocessing syste m,dis 2cusses the characteristics of T M S320LF2407and ADS8364,and focuses on the hard ware design of the ADS8364and its interface with the DSP .This system mainly realizes the functi ons of accurate acquiring the signal in electric power syste m,monit oring its run 2ning situati on .W hen the electric power syste m breaks down the syste m can send out an alar m signal and recode the real 2ti m e run 2ning data .This data acquiring and p r ocessing syste m can be app lied t o vari ous intelligence instru ments and aut omatic contr ol equi p 2ments,and there is a very good market foregr ound .

Key words:D igital Signal Pr ocessing (DSP );ADS8364;data acquiring (上接第61页)

[2] Acti on 高级开发.[OB /DL ].htt p://hubdog .csdn .net/

Hubdog/T Acti on .ht m .

[3] 张国鸣,唐树才.网络管理使用技术[M ].北京:清华

大学出版社,2002.

王 会(1980-),女,陕西大荔人,硕士研究生,主要

研究方向为无线与移动通信、网络通信和GPS 技术。

王 忠(1964-),男,四川成都人,副教授,主要研究方向是GPS 、Galileo 理论及应用,无线与移动通信关键技术,网络通信理论与技术。

杜传利(1978-),男,山东德州人,硕士研究生,主要研究方向为无线与移动通信、网络通信和GPS 技术等。

D esi gn and i m plem en t a ti on of i n telli gen t publi c phone charge managem en t system

WAN G Hui,WAN G Zhong,DU Chuan 2li

(Dep t .of Communicati on Engineering Sichuan University,Chengdu 610065,China )

Abstract:By using Del phi object 2oriented s oft w are as the devel op ing t ool and installing the database S QL Server 2000at backgr ound

server,an intelligent public phone charge gate way syste m has been devel oped successfully .This syste m has the characteristics,such as clear constructi on,si m p le code,easy t o maintain,convenient t o upgrading and ex panding .A t p resent the syste m has passed debug 2ging and put int o using .The article f ocus t o intr oduce s o me key technol ogies which are used during syste m realizati on,including the classes that caused the syste m structure t o be clear,the Tlist that can be used t o maintain objects and the multithreading technique that can enhance syste m working efficiency .These technol ogies have fully manifested the characteristic of object 2oriented Del phi .Key words:class;thread;charge syste m;intelligent public phone

?

37? ?设计与开发? 张 菊,等 基于DSP

的数据采集与处理系统的设计

第六章Matlab/Dsp builder硬件模块设计 Matlab是国内强大的数学分析工具,广泛用于科学计算和工程计算,还可以进行复杂的数字信号处理系统的建模、参数估计及性能分析。Simulink是Matlab的一个组成部分,用于图形化建模仿真。DSP Builder是Altera公司推出的一个面向DSP开发的系统级工具,它构架在多个软件工具之上,并把系统级(算法级建模)和RTL级(硬件实现)两个设计领域的设计工具连接起来放在Matlab/Simulink平台上,而将QuartrsⅡ作为底层设计工具置于后台,从而最大程度地发挥了这三种工具的优势。DSP Builder作为Simulink中的一个工具箱,使得用FPGA设计DSP系统完全可以通过Simulink的图形化界面进行,只要简单地进行DSP Builder工具箱中的模块调用即可。Matlab/DSP Builder尤其适用于一些在Quartus Ⅱ上不方便完成或不能完成的设计项目(如涉及算法类及模拟信号处理与生产方面的系统处理)。DSP Builder还可以自动完成大部分的设计过程和仿真,直到把设计文件下载到FPGA 中。 DSP Builder提供了Quartus? II软件和MATLAB/Simulink工具之间的接口。其具有如下特性: 1.用于连接Mathwork的MATLAB(信号处理工具箱和滤波器设计工具箱),Simulink环境和Altera? 的Quartus II设计软件环境。 2.支持Altera 的DSP核,这些核均可以从Altera的网站上下载(例如:FIR Compiler、Reed-Solomon Compiler等等)。 3.可以利用Altera的DSP开发板来快速的实现设计的原型。 4.支持SignalTap? II逻辑分析仪(一种嵌入式的信号分析仪,它可以探测到DSP开发板上Altera器件内部的信号,并把数据引入到MATLAB的工作区以便于进行可视化的分析)。 5.包括了用户可以创建的定制的逻辑,用于配合SOPC Builder和Nios? II嵌入式处理器设计。 6.包括了PLL块,用于多时钟设计。 7.包括了状态机块。 8.针对DSP系统的算法和实现,支持统一的表示方法。 9.根据MATLAB和Simulink的测试矢量,可以自动生成VHDL测试激励或Quartus II 矢量文件(.vec)。 10.自动调用VHDL综合器和Quartus II编译器。 11.仿真可以设定为比特或周期精度。 12.提供多种的定点运算和逻辑操作,用于配合使用Simulink 软件。 13.支持多种Altera 的器件: Stratix、Stratix II 和 Stratix GX 器件; Cyclone 和 Cyclone II 器件; APEXII、APEX 20KC 和 APEX 20KE 器件; Mercury器件; ACEX? 1K 器件; FLEX? 10K 和 FLEX 6000 器件。 利用Matlab和DSP Builder进行模块设计也是SOPC技术的一个组成部分。这是由于利用Matlab/DSP Builder/QuartrsⅡ可完成纯硬件的DSP算法模型及实现,从而构成嵌入式系统外围接口的协处理模块,再进一步构成软件程序中的精简指令,DSP模块或其他功能模块可以成为单片FPGA电路系统中的一个组成部分,而且通过Matlab/DSP Builder,可以直接为Nios嵌入式处理器设计各类加速器,并以指令的形式加入到Nios的指令系统,从而成为

学号1049721203024 成绩 课程作业 DSP技术 题目:基于DSP2812定时器产生方波 学院(系):信息工程学院 专业班级:电子与通信工程124班 学生姓名:毛大龙 指导教师:孟哲 硬件□软件□ ppt□ 2012年 1 月 8 日

基于DSP2812定时器产生方波硬件设计 1.系统硬件设计内容 本次设计所设计的定时器(信号发生器)是采用TI公司生产的DSP芯片TMS320VC2812和D/A转换芯片TLC7528组成,产生稳定的方波。 我们主要是利用了数字信号处理器以及数模转换器两个部分,其中DSP芯片 TMS320VC2812是系统的核心处理器(控制器),TLC7528芯片是一个模数转换器,主要通过c2812芯片产生的时钟信号作为模数转换器的使能信号,TLC7528被驱动后,将系统产生的数字信号进行转化(数模转换),输出连续的模拟信号,即产生一定占空比的方波(初次我们设定的PWM波占空比为10%,产生的波形频率为1KHZ)最后通过示波器把模拟波形输出到示波器上,整个系统设计简单,清晰易懂。 2.系统设计思想 本系统是以TMS320VC2812这个DSP芯片为核心,通过DSP芯片进行控制和处理,从而产生稳定的方波(PWM)波形,通过D/A转换芯片实现把数字信号转换为模拟信号。整个硬件系统所要做的就是正确连接DSP芯片和D/A转换芯片,确保芯片正常工作,得到稳定的输出波形结果。 系统整体设计方案框图如下: 图1—1 系统整体硬件设计方案 3.系统硬件电路设计原理及框图 3.1系统硬件电路设计原理 整个硬件电路设计主要由中心处理器和模数转换器构成,其核心部分就是

5 DSP控制及硬件电路的设计 5.1 DSP控制 目前市面上流行的主控制器包括:51单片机系列、DSP系列和FPGA。在这中间:虽然51单片机有着成本低廉,体积小的优势;但因其计算能力弱,和外设较少的缺陷,无法满足本系统的需要。FPGA又称现场可编程门阵列,其时序脉冲准确,运算速度快,在需要进行大量重复运算的工程项目中得到了广泛应用。但FPGA以并行运算为主,并需要使用硬件描述语言(verilog 或VHDL)来实现电路设计,相比较单片机有很大不同,这造成开发难度较大,门槛较高。DSP是近几年得到快速发展的控制器,其外设丰富,运算速度快,能满足实时性要求较高的工业现场;尤其适用于控制算法复杂,计算量大的工程项目。 综合以上分析,本文矿用光伏供电系统选择DSP芯片 TMS320LF2407作为最终的控制芯片。TMS320LF2407芯片集成度高,运算速度快,外设丰富,价格适中,作为本设计的控制器,拥有其他芯片所不具备的优势。 5.1.1 TMS320LF2407的技术参数 (1)TMS320LF2407供电电压为3.3V,供电电压低,通态损耗小。最高工作频率40MHZ,指令周期短,指令周期为25ns,能够满足较大载波频率时的计算需求,具备实时控制能力。 (2)TMS320LF2407拥有丰富的存储器资源:包括32K字

程序闪存空间, 1.5K字的数据/程序随机存储器,544字的双口随 机存储器和2k字的单口RAM。除此之外,TMS320LF2407片内还集成有64K数据存储器空间以及64K程序存储器空间; 其I/O 寻址空间达64K,能有效满足使用需要; TMS320LF2407可用于扩展的外部存储器达到192K字。 (3)TMS320LF2407拥有两个事件管理器模块EV A和EVB。每个事件管理器模块上均集成有以下资源:两个16位通用定时器(通过倍频器可以达到很高的工作频率)和8个16位PWM 波生成通道; 为检测上升下降脉冲,片上集成有3个捕获单元。每个模块还可实现以下功能: 可编程的PWM死区控制功能,防止上下桥臂同接收触发信号,同时导通; 输出A、B、C三相对称和非对称触发信号;当接受低电平外部中断信号时,关闭PWM 通道片内光电编码器接口电路,停止发出触发信号; A/D转换功能。 (4)拥有10位模数转换器,最小转换时间为375ns,A/D转换器拥有独立和级连两种工作方式,使用事件管理器EV A、EVB 来实现触发。 (5)拥有16位串行外设接口模块(SPI),和串行通讯接口模块(SCI) (6)拥有5个外部中断资源,除复位中断外,还拥有两个电机驱动保护中断,和两个可屏蔽中断。 (7)除高性能模式外,电源管理还包括低功耗模式,在运算

目录 摘要...................................................... I 第1章绪论 ..................................................................... 错误!未定义书签。第2章总体设计 (1) 2.1系统要实现的功能 (1) 2.2系统的设计流程 (2) 1.2原理框图 (2) 第3章DSP最小系统电路设计.................................... 错误!未定义书签。 3.1电源电路设计 (2) 3.2复位电路设计 (3) 3.3时钟电路设计 (3) 3.4JTAG接口电路设计..................... 错误!未定义书签。 3.5DSP的串行接口电路设计 (4) 3.6存储器FLASH扩展设计 (4) 第4章软件设计 (5) 4.1仿真工作原理及测试步骤 (9) 4.2测试程序 (9) 4.3测试的注意事项 (10) 总结 ................................................................................... 错误!未定义书签。致谢 . (8) 参考文献 (8) 第1章绪论 DSP 有两种涵义,一种是Digital Signal Processing,指的是数字信号处理技术;一种是Digital Signal Processor,指的是数字信号处理器。两者是不可分割的,前者是理论上的技术,要通过后者变成实际产品,两者结合起来才成为解决某一实际问题和实现某一方案的手段。数字信号处理器是目前IT 领域中发展极为迅速的一类微处理器,其功能强大,应用范围相当广泛,能够完成实时的数字信号处理任务。DSP 的性能几乎决定了电子产品的性能。在人们生活当中,DSP可谓无处不在,例如手机,电视机,数码相机,MP3等等都有DSP的存在。DSP 已经成为通信、计算机和消费类电子产品等领域的基础器件。因此,只有理论的学习是不够的,设计一个DSP

2010 - 2011学年第 2 学期《DSP芯片的原理与开发应用》 题目:DSP硬件开发平台设计 班级: 学号: 姓名: 指导教师: 成绩:

基于DSP E1-16XS的硬件开发平台设计 引言 嵌入式系统硬件的核心是各种类型的嵌入式处理器,目前全世界嵌入式处理器的品种已经超过1000多种,流行体系结构有30多个系列,嵌入式处理器一般可以分为嵌入式微处理器、嵌入式微控制器、嵌入式DSP处理器和嵌入式片上系统。 与标准微处理器相比,嵌入式微处理器只保留了和嵌入式应用有关的功能,并且为了满足嵌入式应用的特殊要求,在工作温度、抗电磁干扰、可靠性等方面都做了各种增强。 DSP嵌入式系统是DSP系统嵌入到应用电子系统中的一种通用系统,这种系统既具有DSP器件在数据处理方面的优势,又具有应用目标所需要的技术特征,在许多嵌入式应用领域,既需要在数据处理方面具有独特的优势的DSP,也需要在智能控制方面技高一筹的微处理器(MCU);因此,将DSP与MCU融合在一起的双核平台,将成为DSP技术发展的一种新潮流。德国Hyperstone公司是真正把DSP 成功嵌入32位微处理器的厂商之一,尤其是它的E1-XS系列更是这方面的佼佼者。 1 E1-16XS微处理器结构概述 Hyperstone RISC/DSP架构框图如图1所示,Hyperstone内核是专为RISC和DSP功能的集成而设计的,但它不是两个不同内核在单个芯片上的简单组合,而是一个集成的内核和指令集。这一全集成的内核基于单处理器模式,带有单指令流。RISC和DSP单元间简单且高效的通信由1个96路的32位内部存储器实现,每个时钟周期内可以执行3条指令的操作,所以在100MHz的频率下可以达到300 MOPS这样优秀的性能。 Hyperstone E1-16XS是一款0.25μm CMOS工艺的微处理器,它结合了高性能的RISC微处理器和DSP处理器,利用简洁高效的指令,使嵌入式DSP处理器的实时性得以充分的发挥。该处理器主要具有如下的特点: 1、32位RISC/DSP处理器ALU、DSP单元和Load/Store单元并行处理,内部

- -- DSP最小系统电路设计 第1章绪论 DSP 有两种涵义,一种是Digital Signal Processing,指的是数字信号处理技术;一种是Digital Signal Processor,指的是数字信号处理器。两者是不可分割的,前者是理论上的技术,要通过后者变成实际产品,两者结合起来才成为解决某一实际问题和实现某一方案的手段。数字信号处理器是目前IT 领域中发展极为迅速的一类微处理器,其功能强大,应用范围相当广泛,能够完成实时的数字信号处理任务。DSP的性能几乎决定了电子产品的性能。在人们生活当中,DSP可谓无处不在,例如手机,电视机,数码相机,MP3等等都有DSP的存在。DSP 已经成为通信、计算机和消费类电子产品等领域的基础器件。因此,只有理论的学习是不够的,设计一个DSP最小系统,掌握这门重要技术,才能更深刻地理解和掌握DSP,为今后进行高精度、高性能的电子设计打下基础。 DSP 芯片是模拟信号变换成数字信号以后进行高速实时处理的专用微处理器,其处理速度比最快的CPU还快10-50 倍,具有处理速度高、功能强、性能价格比好以及速度功耗比高等特点,被广泛应用于具有实时处理要求的场合。 DSP 系统以DSP 芯片为基础,具有以下优点。 1.高速性 DSP 系统的运行速度较高,最新的DSP运行速度高达1000MIPS 以上。 2.编程方便 可编程DSP可使设计人员在开发过程中灵活方便的对软件进行修改和升级。 3.稳定性好 DSP 系统以数字处理为基础,受环境温度及噪声的影响比较小,可靠性高。 4.可重复性好 数字系统的性能基本上不受元器件参数性能的影响,便于测试、调试和大规模生产。 5.集成方便 DSP 系统中的数字部件有高度的规范性,便于大规模集成。 6.性价比高 常用的DSP价格在5美元以下。

绪论 DSP(数字信号处理器)是在模拟信号变换成数字信号以后进行高速实时信号处理的专用处理器,其处理速度比最快的CPU还快10~50倍。DSP具有可编程特性、运算速度快及接口灵活的特点,使得它在电子产品的研制中发挥着越来越大的作用。采用DSP器件来实现数字信号处理系统已经成为当今社会的发展趋势。 在DSP领域,美国TI(德州仪器)公司生产的TMS320家族DSP芯片以其独特的哈佛结构、硬件密集型方案以及灵活的指令系统,成为数字信号处理器产业中的领先者。其C5000系列是16位定点、速度为40M1PS~200MIPS、可编程、低功耗和高新能的DSP,在有线和无线通信、IP电话、便携式信息系统、手机、助听器等领域得到了广泛应用。 最小系统模块是使得DSP芯片能够工作的最精简模块。如何以最短的开发周期.开发出适于自己应用的高性能低成本的DSP最小系统模块,是进行DSP系统开发的第一步。最小系统模块设计包括硬件设计和软件设计。 本次设计是对TI公司生产的16位定点DSP芯片——TMS320VC5402进行最小系统模块硬件设计,它可以很方便地与外围模块组合成不同功能的应用系统。

1 DSP简介 1.1 DSP 的应用领域 在近 20 多年时间里,DSP 芯片的应用已经从军事、航空航天领域扩大到信号处理、通信、雷达、消费等许多领域。主要应用有信号处理、通信、语音、图形、图像、军事、仪器仪表、自动控制、医疗、家用电器等。 DSP 主要应用市场为3C 领域,占整个市场需求的 90%。数字蜂窝电话是 DSP 最为重要的应用领域之一。由于 DSP 具有强大的计算能力,使得移动通信的蜂窝电话重新崛起,并创造了一批诸如 GSM、CDMA 等全数字蜂窝电话网。在Modem 器件中,DSP 更是成效卓著,不仅大幅度提高了传输速率,且具有接收动态图像能力。另外,可编程多媒体 DSP 是 PC 领域的主流产品。以XDSL Modem为代表的高速通信技术与MPEG 图像技术相结合,使得高品位的音频和视频形式的计算机数据有可能实现实时交换。目前的硬盘空间相当大,这主要得益于CDSP(可定制 DSP)的巨大作用。预计在今后的 PC 机中,一个 DSP 即可完成全部所需的多媒体处理功能。DSP 也是消费类电子产品中的关键器件。由于 DSP的广泛应用,数字音响设备的更新换代周期变得非常短暂。用于图像处理的 DSP,一种用于 JPEG 标准的静态图像数据处理;另一种用于动态图像数据处理。 1.2 DSP的特点 DSP 芯片是模拟信号变换成数字信号以后进行高速实时处理的专用微处理器,其处理速度比最快的 CPU 还快 10-50 倍,具有处理速度高、功能强、性能价格比好以及速度功耗比高等特点,被广泛应用于具有实时处理要求的场合。 DSP 系统以 DSP 芯片为基础,具有以下优点。 1.高速性,DSP运行速度高达1000MIPS以上 2.编程方便,可编程DSP可使设计人员在开发过程中灵活方便的对软件进行修改和升级。

DSP课程设计 计算机与信息工程学院 通信工程产业班 李盛 一、基本DSP硬件系统设计 硬件任务设计概述 要求: 1、基本DSP硬件系统以TMS320C54x系列为核心处理器,包括最小系统、存 储器扩展、显示器、键盘、AD、DA等电路模块; 2、硬件设计画出主要芯片及电路模块之间的连接即可,重点考查电路模块方 案设计与系统地址分配; 3、设计方案以电路示意图为主,辅以必要的文字说明。 总体方案设计 本次硬件电路大体如下 TMS320C54x 模块电路原理图设计 1,电源模块 C54X数字信号处理器电源包括内核电源和外部接口电源,其外部接口电

源为3.3V,内部则根据型号不同而采用了不同的电压。由于C54X处理器大多应用于低功耗场合,因此电源电路的设计需要注意电源的转换效率和电路的复杂程度,而高效率的DC-DC转换电路就十分适合这种应用。 TPS54110能够提供1.5A的连续电流输出,其输出电压可调,低电压输出范围覆盖0.9~3.3V,能够较好地满足C54X处理器的供电要求,具体内容如下图: 2,时钟电路模块 任何工作都按时间顺序。用于产生时间的电路就是时钟电路。实时时钟电路DS1302是一种具有涓细电流充电能力的电路,主要特点是采用串行数据传输,可为掉电保护电源提供可编程的充电功能,并且可以关闭充电功能。采用普通32.768KHz晶振。 3,JTAG仿真模块 JTAG仿真器 4,复位电路模块 在系统上电过程中,如果电源电压还没有不稳定,这时DSP进入工作状态可能造成不可预知的后果,甚至造成硬件的损坏,因此有必要在系统中加入上电复位电路,上电复位电路的作用可以保证上电可靠,并在需要时实现手工复位。 5,数码管电路模块 一共12个引脚,8个段选。从上面左边第一排开始,按顺时针顺序依次往下遍历所有引脚。 6,SRAM:IS61LV6416模块 如图,电路SRAM中的借口与DSP芯片借口相连接构成电路系统。 硬件设计结果与分析 利用protel分别完成了电源电路,时钟电路,复位电路等外设电路的绘制,完成了最小系统的schematic原理图,并生成了PCB图,PCB板及3D效果图。 电路原理图

DSP系统的设计过程 总的来说,DSP系统的设计还没有非常好的正规设计方法。 DSP系统设计一般方法 第一步明确任务 必须根据应用系统的目标确定系统的性能指标、信号处理的要求,通常可用数据流程图、数学运算序列、正式的符号或自然语言来描述。 第二步算法仿真 一般来说,为了实现系统的最终目标,需要对输入的信号进行适当的处理,而处理方法的不同会导致不同的系统性能,要得到最佳的系统性能,就必须在这一步确定最佳的处理方法,即数字信号处理的算法(Algorithm),因此这一步也称算法模拟阶段。例如,语音压缩编码算法就是要在确定的压缩比条件下,获得最佳的合成语音。算法模拟所用的输入数据是实际信号经采集而获得的,通常以计算机文件的形式存储为数据文件。如语音压缩编码算法模拟时所用的语音信号就是实际采集而获得并存储为计算机文件形式的语音数据文件。有些算法模拟时所用的输入数据并不一定要是实际采集的信号数据,只要能够验证算法的可行性,输入假设的数据也是可以的。 第三步设计实时DSP系统 实时DSP系统的设计包括硬件设计和软件设计两个方面。硬件设计首先要根据系统运

算量的大小、对运算精度的要求、系统成本限制以及体积、功耗等要求选择合适的DSP芯片。然后设计DSP芯片的外围电路及其他电路。软件设计和编程主要根据系统要求和所选的DSP芯片编写相应的DSP汇编程序,若系统运算量不大且有高级语言编译器支持,也可用高级语言(如C语言)编程。由于现有的高级语言编译器的效率还比不上手工编写汇编语言的效率,因此在实际应用系统中常常采用高级语言和汇编语言的混合编程方法,即在算法运算量大的地方,用手工编写的方法编写汇编语言,而运算量不大的地方则采用高级语言。采用这种方法,既可缩短软件开发的周期,提高程序的可读性和可移植性,又能满足系统实时运算的要求。 DSP硬件和软件设计完成后,就需要进行硬件和软件的调试。软件的调试一般借助于DSP开发工具,如软件模拟器、DSP开发系统或仿真器等。调试DSP算法时一般采用比较实时结果与模拟结果的方法,如果实时程序和模拟程序的输入相同,则两者的输出应该一致。应用系统的其他软件可以根据实际情况进行调试。硬件调试一般采用硬件仿真器进行调试,如果没有相应的硬件仿真器,且硬件系统不是十分复杂,也可以借助于一般的工具进行调试。系统的软件和硬件分别调试完成后,就可以将软件脱离开发系统而直接在应用系统上运行。当然,DSP系统的开发,特别是软件开发是一个需要反复进行的过程,虽然通过算法模拟基本上可以知道实时系统的性能,但实际上模拟环境不可能做到与实时系统环境完全一致,而且将模拟算法移植到实时系统时必须考虑算法是否能够实时运行的问题。如果算法运算量太大不能在硬件上实时运行,则必须重新修改或简化算法。

5 DSP 控制及硬件电路的设计 5.1 DSP 控制 目前市面上流行的主控制器包括:51单片机系列、DSP 系列和FPGA 。在这中间:虽然51单片机有着成本低廉,体积小的优势;但因其计算能力弱,和外设较少的缺陷,无法满足本系统的需要。FPGA 又称现场可编程门阵列,其时序脉冲准确,运算速度快,在需要进行大量重复运算的工程项目中得到了广泛应用。但FPGA 以并行运算为主,并需要使用硬件描述语言(verilog 或VHDL )来实现电路设计,相比较单片机有很大不同,这造成开发难度较大,门槛较高。DSP 是近几年得到快速发展的控制器,其外设丰富,运算速度快,能满足实时性要求较高的工业现场;尤其适用于控制算法复杂,计算量大的工程项目。 综合以上分析,本文矿用光伏供电系统选择DSP 芯片 TMS320LF2407作为最终的控制芯片。TMS320LF2407芯片集成度高,运算速度快,外设丰富,价格适中,作为本设计的控制器,拥有其他芯片所不具备的优势。 5.1.1 TMS320LF2407的技术参数 (1)TMS320LF2407供电电压为3.3V ,供电电压低,通态损耗小。最高工作频率40MHZ ,指令周期短,指令周期为25ns ,能够满足较大载波频率时的计算需求,具备实时控制能力。 (2)TMS320LF2407拥有丰富的存储器资源:包括32K 字 程序闪存空间, 1.5K字的数据/程序随机存储器,544字的双口随机存储器和2k 字的单口RAM 。除此之外,TMS320LF2407片内还集成有64K 数据存储器空间以及 64K 程序存储器空间; 其I/O寻址空间达64K ,能有效满足使用需要; TMS320LF2407可用于扩展的外部存储器达到192K 字。

绪论 一个完整的DSP系统通常是由DSP芯片和其他相应的外围器件构成。DSP硬件系统主要包括电源电路、复位电路、时钟电路等。DSP的时钟电路用来为TMS320C54x芯片提供时钟信号,由一个内部振荡器和一个锁相环PLL组成,可通过晶振或外部的时钟驱动。以下我们将着重讨论DSP 硬件系统的基本设计中时钟电路的设计。 关键字TMS320C54x 时钟产生器软件可编程PLL

精品文档 目录 绪论................................................................................................. I 第一章时钟产生器. (1) 第二章软件可编程PLL (2) 第一节软件配置PLL介绍 (2) 一时钟模式介绍 (2) 二时钟模式设置 (2) 第二节程序 (6) 一倍频模式向倍频模式的切换 (6) 二倍频模式向分频模式的切换 (7) 三分频模式向倍频模式的切换 (8) 四分频模式向分频模式的切换 (9) 第三章心得体会 (10) 第四章参考文献 (11)

TMS320C54X X1X2\CLKIN 4 1 3 2 Vdd TSM320C54X X1X2\CLKIN C1C2 晶体 外部晶振

第二章软件可编程PLL 第一节软件配置PLL介绍 软件可编程PLL的特点是有高度的灵活性,它包括一个用来提供各种时钟乘数因子的时钟标定位、直接开放和禁止PLL的功能和一个PLL 锁存定时器,该锁存定时器可以延迟期间PLL时钟模式的切换直到所存操作完成为止。 一时钟模式介绍 带有内部的软件可编程PLL的期间可以设置为下面两种时钟模式:PLL模式:输入时钟(CLKIN)乘以31个可能的因子中的一个因子,这些因子取值范围为0.25~15,他们可以通过PLL电路获取。 DIV(分频器)模式:输入时钟(CLKIN)处以2或4.当用DIV模式时,所有的模拟部分,包括PLL电路,都被禁止以使功耗降到最小。 二时钟模式设置 复位操作之后,时钟操作模式立即由3个外部引脚CLKMD1,CLKMD2,CLKMD3的直来确定。3个CLKMD引脚所对应的模式如表1所示,复位之后,软件可编程PLL可以被变成设置为所需的模式。下列时钟模式引脚作何可以在复位时开放PLL:C5402中是CLKMD(3-1)=000b 110b.当这些时钟模式引脚被组合式,内部的PLL锁相定时器不再激活,因此,系统必须延迟释放复位以保证PLL锁存时间的延迟得以满足。