指令系统和汇编语言程序设计实验报告

姓名:XXX

班级:XXXXXXX

学号:000000

3.2 指令系统实验

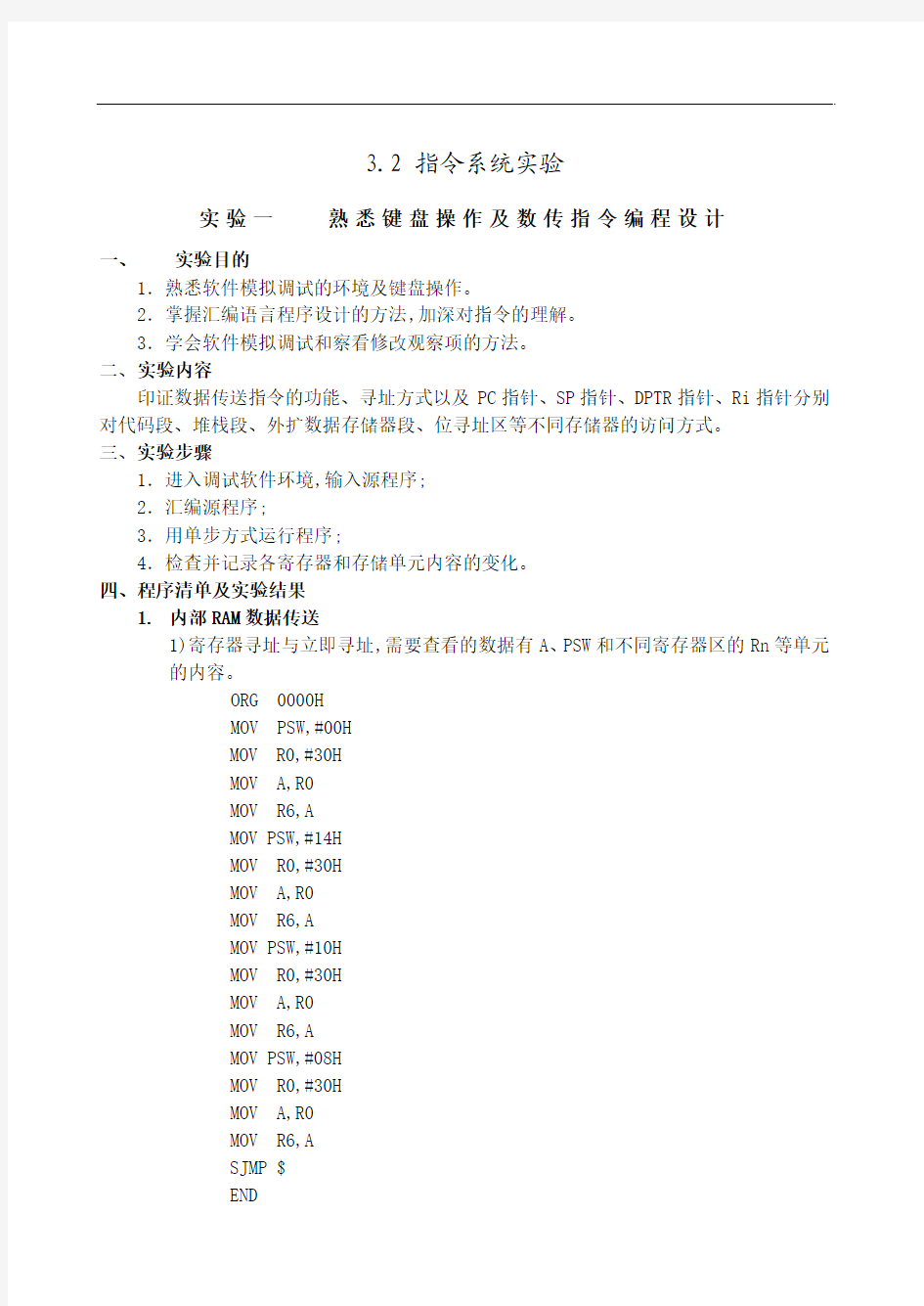

实验一熟悉键盘操作及数传指令编程设计

一、实验目的

1.熟悉软件模拟调试的环境及键盘操作。

2.掌握汇编语言程序设计的方法,加深对指令的理解。

3.学会软件模拟调试和察看修改观察项的方法。

二、实验内容

印证数据传送指令的功能、寻址方式以及PC指针、SP指针、DPTR指针、Ri指针分别对代码段、堆栈段、外扩数据存储器段、位寻址区等不同存储器的访问方式。

三、实验步骤

1.进入调试软件环境,输入源程序;

2.汇编源程序;

3.用单步方式运行程序;

4.检查并记录各寄存器和存储单元内容的变化。

四、程序清单及实验结果

1.内部RAM数据传送

1)寄存器寻址与立即寻址,需要查看的数据有A、PSW和不同寄存器区的Rn等单元

的内容。

ORG 0000H

MOV PSW,#00H

MOV R0,#30H

MOV A,R0

MOV R6,A

MOV PSW,#14H

MOV R0,#30H

MOV A,R0

MOV R6,A

MOV PSW,#10H

MOV R0,#30H

MOV A,R0

MOV R6,A

MOV PSW,#08H

MOV R0,#30H

MOV A,R0

MOV R6,A

SJMP $

数据记录:

2) 直接寻址,需查看30H、31H、32H、40H、ACC、PSW等单元的内容。 ORG 0100H

MOV 30H,#45H

MOV 31H,#46H

MOV 02H,31H

MOV 0E0H,30H

MOV 32H,ACC

MOV ACC,PSW

MOV 40H,ACC

SJMP $

END

数据记录:

3)寄存器间接寻址,需查看@R0、RO等的内容。

ORG 0200H

MOV R0,#30H

MOV @R0,#30H

SJMP $

END

数据记录:

2.外部数据传送

需要查看的数据有外部数据存储器单元2000H,外部程序存储器单元2001H。

ORG 0000H

MOV A,#89H

MOV DPTR,#2000H

MOVX @DPTR,A

INC DPTR

CLR A

MOVC A,@A+DPTR

SJMP $

ORG 2000H

DB 44H

DB 78H

DB 67H

END

数据记录:

3.堆栈操作

需要查看的数据有50H、51H、A及SP指针和堆栈区中数据随PUSH和POP指令执行后

1)可用于保护现场和恢复现场的程序

ORG 0000H

MOV SP,#5FH

MOV 50H,#3BH

MOV 51H,#2FH

MOV A,#12H

PUSH 50H

PUSH 51H

PUSH ACC

POP 0E0H

POP 51H

POP 50H

SJMP $

END

数据记录:

2)可用于数据交换的程序

ORG 0100H

MOV SP,#6FH

MOV 50H,#3BH

MOV 51H,#2FH

PUSH 50H

PUSH 51H

POP 50H

POP 51H

SJMP $

数据记录:

4.数据交换

记录每条指令运行后的结果,从而加深对各种不同的交换指令的理解。 1)SWAP指令

ORG 0000H

MOV A,#58H

SWAP A

MOV 40H,A

SJMP $

END

数据记录:

2) XCHD 指令

ORG 0030H

MOV A,#30H

MOV R0,#30H

MOV @R0,#09H

XCHD A,@R0

MOV 41H,A

SJMP $

END

数据记录:

ORG 0100H

MOV 50H,#1

MOV A,#89H

XCH A,50H

MOV R7,#3

XCH A,R7

XCH A,@R0

SJMP $

END

数据记录:

五、思考题

1、寄存器寻址与寄存器间接寻址有什么区别?

答:寄存器寻址所需操作数放在寄存器中,确定了寄存器就得到了操作数,存放操作数的寄存器地址内含或隐含在指令的操作码字节中;而寄存器间接寻址是将指令指定的寄存器内容作为操作数的地址,该地址所指定的单元内容作为被寻找的操作数。

2、PC指针与SP指针有什么区别?

答:PC指针是一个16位的程序地址寄存器,其内容是当前执行指令的下一条指令在程序内存中的地址,具有自动加1的功能,从而保证程序能够自动顺序执行,寻址范围达64KB,但是PC单元本身没有地址,是不可寻址的;而SP指针为堆栈指针,其内容是堆栈栈顶的存储单元地址,S可以初始化为不同的值,因此堆栈位

再减1。

3、DPTR指针与Ri(R0,R1)指针有什么区别?

答:数据指针DPTR为16位寄存器,存放16位地址,作为访问外部程序内存ROM、外部数据存储器RAM和扩展I/O接口时的地址;而Ri(i=0,1)可寻址片内RAM低128B(00H~7FH),与P2口配合使用,用Ri指示低8位地址(00H~0FFH),P2口输出高8位地址,可寻址片外数据存储器或I/O的64KB区域。

4、立即寻址与直接寻址有什么区别?

答:立即寻址中,操作数直接由指令给出,通常紧跟指令操作码之后的一个或两个字节就是所需的操作数;而直接寻址则直接给出操作数所在的单元地址或位地址。

5、同一个特殊功能寄存器不同表达形式。

答:书写时既可以使用寄存器符号,也可以使用寄存器单元地址,通常有四种表达形式。例如:Cy 可以表示为Cy/0D7H/PSW.7/0D0H.7,但A累加器比较特殊,有三种表示方法:A/ACC/0E0H。

6、三种不同的交换指令的区别是什么?

答:三种不同的交换指令分别是:整字节交换指令、低半字节交换指令、累加器高低半字节交换指令。整字节交换指令,XCH,把累加器A的内容与内部RAM及SFR 中的内容互相交换,影响P标志;低半字节交换指令,XCHD,累加器A低四位与片内RAM某单元低四位交换,高四位不变;累加器高低半字节交换指令,SWAP,将累加器A中的高四位与低四位内容交换,不影响标志位。

实验二数传指令程序设计

一、实验目的

1.掌握数据块的传送操作和算术运算指令的应用。

2.进一步掌握汇编语言设计和调试方法。

3.掌握观察窗口的使用方法。

4.学会给存储单元赋初值的方法。

二、实验内容

1、把内部RAM 40H~4FH置初值0A0H~0AFH;

2、而后把40H~4FH内容传送到外部RAM 9800H~980FH中;

3、再把 9800H~980FH内容传送到 50H~5FH中。

三、实验步骤

1.分别用单步和连续运行方式,调试上述程序;

2.在观察窗口中观察结果。

四、实验程序清单

数据块传送参考程序:

ORG 0000H

MAIN: MOV R0,#40H

MOV R2,#10H

MOV A,#0A0H

A1: MOV @R0, A

INC R0

INC A

DJNZ R2, A1

MOV R0, #40H

MOV DPTR, #9800H

MOV R2, #10H

A2: MOV A, @R0

MOVX @DPTR, A

INC R0

INC DPTR

DJNZ R2, A2

MOV R0, #50H

MOV DPTR, #9800H

MOV R2, #10H

A3: MOVX A, @DPTR

MOV @R0, A

INC DPTR

DJNZ R2, A3 SJMP $

END

数据记录:

五、思考题

1)若两个数据块都在外部数据存储器中,如何实现数据块的传送?

答:在外部数据存储器中的两个数据块不能直接传送数据,可将外部数据存储器中的数据块先送到片内,完成操作后再送回片外即可完成数据块的传送。

2)在调试程序时,若不用程序给40H~4FH赋初值,而用键盘在CPU DATA区给40H~4FH 单元预赋初值,如何做?

答:在输出窗口中对应的地址直接输入初值即可。

实验三算数运算指令编程设计

一、实验目的

1、掌握算术运算指令及其应用。

2、进一步掌握汇编语言设计和调试方法。

3、掌握观察窗口的使用方法。

4、学会给存储单元赋初值的方法。

二、实验内容

1、求两个无符号数求和及差;

2、求两个带符号数求和及差;

3、求两个压缩的BCD码数的和及差。

三、实验步骤

1.分别用单步和连续运行方式,调试上述各个程序;

2.在观察窗口中观察结果。

四、实验程序清单

1、计算下面各式中两个无符号数的和及差,观察CY,并记录运算结果,并求出结果的真值。

(1)计算200+200

(2)计算 36589+46542

(3)计算 100-200及200-100

(4)计算 36589-16542及16542-36589

1)加法的参考程序:

(1)计算两个单字节数的和的参考程序:

ORG 0000H

MAIN: MOV A,#200

ADD A,#200

SJMP $

END

数据记录:

实验分析:

Cy=1,表示加法有借位;ac=1,说明低四位向高四位有进位。所以计算结果为100H+90H=190H(即400)。结果正确。

(2)计算两个双字节数的和的参考程序:

ORG 0100H

MAIN: MOV A,#low(36589)

ADD A,# low(46542)

MOV 30H,A

MOV A,#HIGH (36589)

ADDC A,# HIGH (46542)

MOV 31H,A

MOV A,#0

ADDC A,#0

MOV 32H,A

SJMP $

END

数据记录:

实验分析:

计算得出的结果为0144BBH,ac、cy均为零,故为真值。0144BBH=83131.结果正确。

3)减法的参考程序

(1)两个单字节数的减法程序

ORG 0000H

MAIN: CLR C

MOV A,#100

SUBB A,#200

SJMP $

数据记录:

4)两个双字节数的减法程序

ORG 0100H

MAIN: CLR C

MOV A,#low(36589)

SUBB A,# low(16542)

MOV 30H,A

MOV A,#HIGH (36589)

SUBB A,# HIGH (16542)

MOV 31H,A

MOV A,#0

SUBB A,#0

MOV 32H,A

SJMP $

END

计算结果为4E4FH,因为ac、cy均为零,故为真值。4E4FH=20047。结果正确。

计算16542-36589 :

实验分析:

因cy=1,故有借位。所以计算结果为-(0FFFFFFH+1-0FFB1B1H)=-4E4FH=-20047。结果正确。

2、计算下面各式中两个带符号数的和及差,观察OV,并记录运算结果,并求出结果的真值。

(1)计算 56+78

数据记录:

实验分析:

Ov=1,溢出,结果无意义。

(2)计算 120+120

数据记录:

实验分析:

Ov=1,溢出,结果无意义。

(3)计算 -56-78

数据记录:

实验分析:

Ov=1,溢出,结果无意义。

(4)计算 -120-123

数据记录:

实验分析:

Ov=1,溢出,结果无意义。

3、BCD码运算,观察CY、AC,并记录运行结果,求出结果的真值。

1)计算 56+99

参考程序:

ORG 0000H

MAIN: MOV A,#56H

ADD A,#99H

DA A

MOV 30H,A

SJMP $

数据记录:

实验分析:

Cy=1,故有借位,所以计算结果为100+55=155,为真值。结果正确。

2)计算 56-99

参考程序:

ORG 0000H

MAIN: CLR C

MOV A,#9AH

SUBB A,#99H

ADD A,#56H

DA A

MOV 30H,A

CPL C

SJMP $

END

数据记录:

实验分析:

Cy=1,有借位,所以计算结果为57-100=-43,为真值。结果正确。

3)计算36826529+29541265

多字节十进制加法参考程序: Array ORG 0000H

MAIN: MOV R0, #30H

MOV R1, #20H

MOV 2FH,#04H

CLR C

DA1: MOV A,@R0

ADDC A, @R1

DA A

MOV @R1, A

INC R0

INC R1

DJNZ 2FH, DA1

MOV 7FH, C

SJMP $

END

数据记录:

实验分析:

思考题

1)如果求两个带符号数的和或差出现了溢出,如何将两个运算数扩大字节后再做一遍,再观察OV,记录结果,求出真值,计算结果还溢出吗?

答:不会溢出。

2)在多字节十进制加法程序,若两数的和存放到从40H开始的单元,如何修改程序?

答:利用循环。程序如下:

ORG 1000H

MAIN: MOV R0, #30H

MOV R1, #20H

MOV SP,#3FH

MOV 2FH,#04H

CLR C

DA1: MOV A,@R0

ADDC A, @R1

DA A

PUSH ACC

INC R0

INC R1

DJNZ 2FH, DA1

MOV 7FH, C

SJMP $

END

实验四 逻辑运算及位操作指令编程设计

一、 实验目的

(1) 熟悉字节逻辑运算指令功能。 (2) 熟悉位操作指令运算功能。

(3)从而更深入的掌握汇编语言程序设计。 (4)学会观察CPU 窗口中BIT 区的变化。 二、 实验内容

1. 字节逻辑运算程序

在片内RAM 的FIRST 和SECOND 单元中各有一符号数X 和Y,要求按下列条件算出Z,存入RESULT 单元中(设运算结果仍为8位数)。

FIRST EQU 30H

SECOND EQU 31H

RESULT EQU 32H

ORG 0000H

START:MOV R0,FIRST MOV A, R0

JB ACC.7, NEG MOV B, #2 DIV AB MOV A, B JZ TEMP1 MOV A,R0

ADD A, SECOND SJMP RES TEMP1: MOV A, R0 ANL A, SECOND SJMP RES NEG: CPL ACC.7

Z=

系统工程实验报告 学院:管工学院 班级:工业工程102班 姓名:管华同 学号:109094042

实验一:解释结构模型 一、实验目的: 熟悉EXCEL,掌握解释结构模型规范方法。 二、实验内容: 1.已知可达矩阵如下表1 12345678 111010000 201000000 311110000 401010000 501011000 601011111 701011011 800000001 2. EXCEL中对错误!未找到引用源。中的可达矩阵用实用方法建立其递阶结构模型。(1)对可达矩阵进行缩减,得到缩减矩阵 12345678 111010000 201000000 311110000 401010000 501011000 601011111 701011011 800000001 (2)按小到大给每行排序 1 2 3 4 5 6 7 8 每行的和 2 0 1 0 0 0 0 0 0 1 8 0 0 0 0 0 0 0 1 1 4 0 1 0 1 0 0 0 0 2 1 1 1 0 1 0 0 0 0 3 5 0 1 0 1 1 0 0 0 3 3 1 1 1 1 0 0 0 0 4 7 0 1 0 1 1 0 1 1 5 6 0 1 0 1 1 1 1 1 6

(3)调整行列构成对角单位矩阵 2 8 4 1 5 3 7 6 每行的和 2 1 0 0 0 0 0 0 0 1 8 0 1 0 0 0 0 0 0 1 4 1 0 1 0 0 0 0 0 2 1 1 0 1 1 0 0 0 0 3 5 1 0 1 0 1 0 0 0 3 3 1 0 1 1 0 1 0 0 4 7 1 1 1 0 1 0 1 0 5 6 1 1 1 0 1 0 1 1 6 (4)画出递阶结构有向图 28 4 15 37 6(4)递阶结构模型完成。第一级第五级第二级 第三级第四级

单片机原理及接口技术 实验报告 任课教师 班级 姓名 日期

实验一构建单片机最小系统和实验环境熟悉 一、单片机最小系统的组成原理图 二、单片机的工作原理: 1.运算器 运算器包括算术逻辑运算单元ALU、累加器ACC、寄存器B、暂存器TMP、程序状态字寄存器PSW、十进制调整电路等。它能实现数据的算术逻辑运算、位变量处理和数据传送操作。 (1)算术逻辑单元ALU ALU在控制器根据指令发出的内部信号控制下,对8位二进制数据进行加、减、乘、除运算和逻辑与、或、非、异或、清零等运算。它具有很强的判跳、转移、丰富的数据传送、提供存放中间结果以及常用数据寄存器的功能。MCS-51中位处理具有位处理功能,特别适

用于实时逻辑控制。 (2)累加器ACC 累加器ACC是8位寄存器,是最常用的专用寄存器,它既可存放操作数,又可存放运算的中间结果。MCS—51系列单片机中许多指令的操作数来自累加器ACC。累加器非常繁忙,在与外部存储器或I/O接口进行数据传送时,都要经过A来完成。 (3)寄存器B 寄存器B是8位寄存器,主要用于乘、除运算。乘法运算时,B中存放乘数,乘法操作后,高8位结果存于B寄存器中。除法运算时,B中存放除数,除法操作后,余数存于寄存器B中。寄存器B也可作为一般的寄存器用。 (4)程序状态字PSW 程序状态字是8位寄存器,用于指示程序运行状态信息。其中有些位是根据程序执行结果由硬件自动设置的,而有些位可由用户通过指令方法设定。PSW中各标志位名称及定义如下: CY():进(借)位标志位,也是位处理器的位累加器C。在加减运算中,若操作结果的最高位有进位或有借位时,CY由硬件自动置1,否则清“0”。在位操作中,CY作为位累加器C 使用,参于进行位传送、位与、位或等位操作。另外某些控制转移类指令也会影响CY位状态(第三章讨论)。 AC():辅助进(借)位标志位。在加减运算中,当操作结果的低四位向高四位进位或借位时此标志位由硬件自动置1,否则清“0”。 F0():用户标志位,由用户通过软件设定,决定程序的执行方式。 RS1(),RS0():寄存器组选择位。用于设定当前通用寄存器组的组,其对应关系如下:

译码器实验报告 一、实验目的 1、掌握中规模集成译码器的逻辑功能和使用方法 2、熟悉数码管的使用 二、实验原理 译码器是一个多输入、多输出的组合逻辑电路。它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。译码器在数字系统中有广泛的用途,不仅用于代码的转换、终端的数字显示,还用于数据分配,存贮器寻址和组合控制信号等。不同的功能可选用不同种类的译码器。 译码器可分为通用译码器和显示译码器两大类。前者又分为变量译码器和代码变换译码器。 变量译码器(又称二进制译码器),用以表示输入变量的状态,如2线-4线、3线-8线和4线-16线译码器。若有n个输入变量,则有2n个不同的组合状态,就有2n个输出端供其使用。而每一个输出所

代表的函数对应于n个输入变量的最小项。 三、实验设备与器件 1.+5V直流电源 2.单次脉冲源 3.逻辑电平开关 4.74LS138 四、实验内容及步骤 1.74LS138译码器逻辑功能测试 将译码器使能端STA、STB、STC与地址端A2、A1、A0分别接到逻辑电平开关输入口,八个输出端Y7…Y0依次连接在十六位逻辑电平显示上,拨动逻辑电平开关,逐项测试74LS138的逻辑功能。2.实验箱电源连接正确,电路自查确定无误后,电路验证还是不正确的情况下进行下面的排错检查:

1)检查芯片的电源和地的电平是否正确。 2)芯片的使能端连接的电平正确。 3)从逻辑电平开关输入信号是否正确。 4)从输出端按逻辑功能状态往前一步一步排查。 3.两片3线-8线译码器74LS138扩展为4线-16线译码器 用两片74LS138组合成一个四线-十六线译码器进行实验,并分析逻辑功能。

成都理工大学工程技术学院《过程控制系统课程设计实验报告》 名称:单容水箱液位过程控制 班级:2011级自动化过程控制方向 姓名: 学号:

目录 前言 一.过程控制概述 (2) 二.THJ-2型高级过程控制实验装置 (3) 三.系统组成与工作原理 (5) (一)外部组成 (5) (二)输入模块ICP-7033和ICP-7024模块 (5) (三)其它模块和功能 (8) 四.调试过程 (9) (一)P调节 (9) (二)PI调节 (10) (三)PID调节 (11) 五.心得体会 (13)

前言 现代高等教育对高校大学生的实际动手能力、创新能力以及专业技能等方面提出了很高的要求,工程实训中心的建设应紧紧围绕这一思想进行。 首先工程实训首先应面向学生主体群,建设一个有较宽适应面的基础训练基地。通过对基础训练设施的 集中投入,面向全校相关专业,形成一定的规模优势,建立科学规范的训练和管理方法,使训练对象获得机械、 电子基本生产过程和生产工艺的认识,并具备一定的实践动手能力。 其次,工程实训的内容应一定程度地体现技术发展的时代特征。为了适应现代化工业技术综合性和多学科交叉的特点,工程实训的内容应充分体现机与电结合、技术与非技术因素结合,贯穿计算机技术应用,以适应科学技术高速发展的要求。应以一定的专项投入,建设多层次的综合训练基地,使不同的训练对象在获得对现代工业生产方式认识的同时,熟悉综合技术内容,初步建立起“大工程”的意识,受到工业工程和环境保护方面的训练,并具备一定的实用技能。 第三,以创新训练计划为主线,依靠必要的软硬件环境,建设创新教育基地。以产品的设计、制造、控制乃至管理为载体,把对学生的创新意识和创新能力的培养,贯穿于问题的观测和判断、创造和评价、建模和设计、仿真和建造的整个过程中。

东南大学 《微机实验及课程设计》 实验报告 实验四(1)简单输入输出 一. 实验目的与内容 (一)实验目的 1)进一步掌握TPC实验装置的基本原理和组成结构; 2)掌握利用I/O指令单步调试检查硬件接口功能,学会利用示波器检测I/O指令执行时总线情况; 3)掌握简单并行输入输出接口的工作原理及使用方法,进一步熟悉掌握输入输出单元的功能

和使用。 (二)实验内容及要求 1、输出接口输出,根据8个发光二极管发光的情况验证编程从键盘输入一个字符或数字,将其ASCII码通过正确性。(输出端口实验必做) 2、用逻辑电平开关预置某个字母的ASCII码,编程输入这个ASCII码,并将其对应字母在屏幕上显示出来。(输入端口实验必做) 3、利用基本实验(1)中的输出锁存电路,设计L0~L7为流水灯,流水间隔时间由软件产生。(输出端口实验) 4、利用基本实验(2)中的输入电路,监测逻辑电平开关K0~K7的变换,当开关状态为全开时,在屏幕上显示提示信息并结束程序。(输入端口实验) 要求: 1、输入输出端口应该可以响应外设的连续变化。 2、输出按ESC键退出;输入按任意键退出。 3、内容3、4比做一题,选做一题 二. 实验基本原理 (一)基本原理 简单并行输出实验:八D触发器74LS273的八个输入端接数据总线D0~D7,从键盘输入一个字符或数字,通过2A8H~输出接口输出该字符或者数字代表的ASCII码,再通过8个发光二极管发光显示二进制数码,从而验证编程以及电路的正确性。 简单并行输入实验:八缓冲器74LS244的八个输出端接数据总线D0~D7,8个输入端分别接逻辑电平开关K0~K7,在逻辑电平开关上预置任意字符的ASCII码,编程将此ASCII码通过2A0H~输入,ASCII码对应字符显示在屏幕上,从而验证编程及电路的正确性。 (二)实验接线图

《计算机组成原理》 实验报告 实验室名称:S402 任课教师:邹洋 小组成员:王娜任芬 学号:2010212121 2010212119

实验一_HAMMING码 (2) 实验二_乘法器 (7) 实验三_时序部件 (16) 实验四_CPU__算术逻辑单元实验 (24) 实验五_CPU__指令译码器实验 (32) 实验六_CPU_微程序控制器实验1 (43) 实验七_八_CPU实验 (59)

1 编码实验:Hamming码 1.1、实验目的 1、对容错技术有初步了解,理解掌握海明码的原理 2、掌握海明码的编码以及校验方法 1.2、实验原理 海明码是由Richard Hamming于1950年提出的,目前是被广泛采用的很有效的校验编码。它的特点是只要增加少数几个校验位,就能检测出多位出错,并能自动纠错。 Hamming码的实现原理是在数据中加入几个校验位,将数据代码的码距比较均匀的拉大,并把数据的每一个二进制位分配在几个奇偶校验组中。当某一位出错后,就会引起有关的几个校验位的值发生变化。这不但可以发现出错,还能指出是哪一位出错,为进一步自动纠错提供了依据。 假设校验位的个数为r,则它能表示2r个信息,用其中的一个信息指出“没有错误”,其余的2r-1个信息指出错误发生在哪一位。然而错误也可能发生在校验位,因此只有k=2r-1-r个信息能用于纠正被传送数据的位数,也就是说要满足关系: 2r≥k+r+1 若要能检测与自动校正一位错,并能发现两位错,此时校验位的位数r和数据位的位数k应满足下述关系:2r-1≥k+r 按上述不等式,可计算出数据位k与校验位r的对应关系,如表1.1所示: 表1.1 数据位k与校验位r的对应关系 k值最小的r值 1~3 4 4~10 5 11~25 6 26~56 7 57~119 8 若海明码的最高位号为m,最低位号为1,即H m H m-1…H2H1,则此海明码的编码规律通常是 1)校验位与数据位之和为m,每个校验位P i在海明码中被分在位号为2i-1的位置上,其余各位为数据位,并按从低向高逐位依次排列的关系分配各数据位。 2)海明码的每一位码H i(包括数据位和校验位本身)由多个校验位校验,其关系是被校验的每一位位号等于校验它的各校验位的位号之和。 3)在增大合法码的码距时,所有码的码距应尽量均匀增大,以保证对所有码的检错能力平衡提高。 下面具体看一下对一个字节进行海明编码的实现过程。 只实现一位纠错两位检错,由前面的表可以看出,8位数据位需要5位校验位,可表示为H13H12…H2H1。 五个校验位P5~P1对应的海明码位号分别为H13、H8、H4、H2和H1。P5只能放在H13位

译码器、编码器及其应用 一、实验目的 (1) 掌握中规模集成译码器的逻辑功能和使用方法; (2) 熟悉掌握集成译码器和编码器的应用; (3) 掌握集成译码器的扩展方法。 二、实验设备 数字电路实验箱,74LS20,74LS138。 三、实验内容 (1) 74LS138译码器逻辑功能的测试。将74LS138输出??接数字实验箱LED 管,地址输入接实验箱开关,使能端接固定电平(或GND)。电路图如Figure 1所示: Figure 2 ??????????????时,任意拨动开关,观察LED显示状态,记录观察结果。 ??????????????时,按二进制顺序拨动开关,观察LED显示状态,并与功能表对照,记录观察结果。 用Multisim进行仿真,电路如Figure 3所示。将结果与上面实验结果对照。

Figure 4 (2) 利用3-8译码器74LS138和与非门74LS20实现函数: ?? 四输入与非门74LS20的管脚图如下: 对函数表达式进行化简: ?? ?? A ? ??????????? ???? 按Figure 5所示的电路连接。并用Multisim进行仿真,将结果对比。 Figure 6

(3) 用两片74LS138组成4-16线译码器。 因为要用两片3-8实现4-16译码器,输出端子数目刚好够用。 而输入端只有 A、、三个,故要另用使能端进行片选使两片138译码器 进行分时工作。而实验台上的小灯泡不够用,故只用一个灯泡,而用连接灯泡的导线测试?,在各端子上移动即可。在multisim中仿真电路连接如Figure 7所示(实验台上的电路没有接下面的两个8灯LED): Figure 8 四、实验结果 (1) 74LS138译码器逻辑功能的测试。 当输入 A时,应该是输出低电平,故应该第一个小灯亮。实际用实验台测试时,LE0灯显示如Figure 9所示。当输入 A时,应该是输出低电平,故理论上应该第二个小灯亮。实际用实验台测试时,LE0灯显示如Figure 6所示。 Figure 10

实验报告管理系统报告文件编码(008-TTIG-UTITD-GKBTT-PUUTI-WYTUI-8256)

软件项目设计报告 实验报告管理系统 所在班级12计卓 小组成员 江灵瞳201印海平201钱晨晨 学院名称信电工程学院 专业名称计算机科学与技术 指导教师胡局新 起止日期 2015年1月15日 目录

1 绪论 开发背景 实验教学是学生技能培养的重要环节之一,学生实验报告的质量在一定程度上反映了实验教学的质量,实验报告管理水平也反映了实验教学管理水平。目前,大部分学校所提交的实验报告大多还停留在以纸为介质的方式上,这将严重制约着实验教学的开展。首先,很多课程的实验结果在纸质实验报告中不能表现或不能完全表现,其次纸质实验报告的批改和分析也是实验授课老师的一个很重负担,如何提高学生实验报告的表象能力,提高教师批改实验报告的效率并及时发现和纠正实验报告中存在的问题是许多课程实验授课教师所面对的一个难题。 本次设计完成的工作 老师登录该系统可以上传、下载实验报告、查看学生做的实验报告并给学生打分、老师可以查看实验验课程、实验课程列表、查看实验提交情况等。 学生登录该系统可以上传、下载实验报告、查看实验课程和实验课程列表。 任务分工 组织结构:为了完成学生信息管理系统的项目开发,班级组成了一个项目团队,人员分工:为了明确项目团队中每个人的任务分工,现制定人员分工,如下表所示: 任务 我们三个人各自分工完成自己的模块内容,首先,江灵瞳构造整个系统的框架,然后印海平设计数据库,在我们一起先设计前台界面,之后我们就各自实现各自模块的功能。

2 系统分析 需求分析 1)实验课程设置,设置课程编号、课程名、时间、次数、老师编号、老师名、实验班级; 2)实验列表设置,设置实验编号、实验名、班级、学生学号、学生名、老师名、实验路径、提交状态、分数; 3)树型类别设置,设置编号、名字、路径、学生名、老师名、树的状态。 可行性分析 编写目的: 背景: 徐州工程学院是一所培养应用型人才的普通高等学院。为了完善管理学校实验报告太多没有地方保存了,经决定开发实验报告管理系统。 要求: 实验报告系统必须提供学生信息和教师信息的基础设置;提供强大的条件搜索功能个实验课程查询、实验列表出现等管理功能;可以分不同权限、不同用户对该系统进行操作。另外,该系统还必须保证数据的安全性、完整性和准确性。 目标: 实验报告管理系统的目标是实现学生的纸质的实验报告太多没有地方长期保存,这样用一个系统可以将一个课程所有学生的实验报告进行管理方便存放。 条件、假定和限制: 时间的限制,我们必须在两周的时间里完成项目,在这期间系统分析员需要整理好分析结果,分配各组员的任务,每天需要人员跟踪记录整理文档。程序开发人员须在5天的时间里进行系统设计、程序编码、系统测试、程序调试。期间,还包括一个双休日假期。 根据上面的分析,在技术上不会存在什么问题,因此项目延期的可能性很小。只要在分配的时间里都能顺利地完成任务,再加上团队的凝聚力齐心协力,相信在这两周内会获得一个满意的结果。 用例图 图用例图

系统工程仿真实验报告 姓名:_蒋智颖_ 学号:_110061047_ 成绩:___________ 实验一:基于VENSIM的系统动力学仿真 一、实验目的 VENSIM是一个建模工具,可以建立动态系统的概念化的,文档化的仿真、分析和优化模型。PLE(个人学习版)是VENSIM的缩减版,主要用来简单化学习动态系统,提供了一种简单富有弹性的方法从常规的循环或储存过程和流程图建立模型。本实验就是运用VENSIM进行系统动力学仿真,进一步加深对系统动力学仿真的理解。 二、实验软件 VENSIM PLE 三、原理 1、在VENSIM中建立系统动力学流图; 2、写出相应的DYNAMO方程; 3、仿真出系统中水准变量随时间的响应趋势; 四、实验内容及要求 某城市国营和集体服务网点的规模可用SD来研究。现给出描述该问题的DYNAMO方程及其变量说明。 L S·K=S·J+DT*NS·JK N S=90 R NS·KL=SD·K*P·K/(LENGTH-TIME·K) A SD·K=SE-SP·K C SE=2 A SP·K=SR·K/P·K A SR·K=SX+S·K C SX=60 L P·K=P·J+DT*NP·JK N P=100 R NP·KL=I*P·K C I=0.02 其中:LENGTH为仿真终止时间、TIME为当前仿真时刻,均为仿真控制变量;S为个体服务网点数(个)、NS为年新增个体服务网点数(个/年)、SD为实际千人均服务网点与期望差(个/千人)、SE为期望的千人均网点数、SP为的千人均网点数(个/千人)、SX为非个体服务网点数(个)、SR为该城市实际拥有的服务网点数(个)、P为城市人口数(千人)、NP为年新

河北大学计算机组成原理实验报告 实验项目指令译码器成绩 一、实验目的: (1)理解指令译码器的作用和重要性。 (2)学习设计指令译码器。 二、实验原理: 指令译码器是计算机控制器中最重要的部分。所谓组合逻辑控制器就是指指令译码电路是由组合逻辑实现的。 组合逻辑控制器又称硬连线控制器,是设计计算机的一种方法。这种控制器中的控制信号直接由各种类型的逻辑门和触发器等构成。这样,一旦控制部件构成后,除非重新设计和物理上对它重新连线,否则要想增加新的功能是不可能的。结构上这种缺陷使得硬连线控制器的设计和调试变得非常复杂而且代价很大。所以,硬连线控制器曾一度被微程序控制器所取代。但是随着新一代及其及VLSI技术的发展,这种控制器又得到了广泛重视,如RISC机广泛使用这种控制器。 图6-42是组合逻辑控制器的方框图。逻辑网络的输入信号来源有3个:①指令操作码译 码器的输出I n ;②来自时序发生器的节拍电位信号T k ;③来自执行部件的反馈信号B j 。逻辑网 络的输出信号就是微操作控制信号,用来对执行部件进行控制。

图6-42 组合逻辑控制器的结构方框图 组合逻辑控制器的基本原理可描述位:某一微操作控制信号C m 是指令操作码译码器的输出I n 、时序信号(节拍电位信号T k )和状态条件信号B j 的逻辑函数。即 C m =f(I n ,T k ,B j ) 用这种方法设计控制器,需要根据每条指令的要求,让节拍电位和时序脉冲有步骤地去控制机器的各有关部分,一步一步地执行指令所规定的微操作,从而在一个指令周期内完成一条指令所规定的全部操作。 三、实验步骤: (1)将试验台设置成FPGA-CPU 独立调试模式,REGSEL=0、CLKSEL=1、FDSEL=0。使用试验台上的单脉冲,即STEP_CLK 短路子短接,短路子RUN_CLK 断开。 (2)将设计在QuartusII 下输入,变异后下载到TEC-CA 上的FPGA 中。 (3)拨动试验台上的开关SD 5~SD 0,改变IR[15..12]、进位标志C 和结果为0标志Z ,观察指示灯R 10~R 0显示的控制信号,并填写表6-28。 四、实验现象及分析:

哈夫曼编码译码器实验报告(免费)

————————————————————————————————作者:————————————————————————————————日期:

问题解析与解题方法 问题分析: 设计一个哈夫曼编码、译码系统。对一个ASCII编码的文本文件中的字符进行哈夫曼编码,生成编码文件;反过来,可将编码文件译码还原为一个文本文件。 (1)从文件中读入任意一篇英文短文(文件为ASCII编码,扩展名为txt); (2)统计并输出不同字符在文章中出现的频率(空格、换行、标点等也按字符处理);(3)根据字符频率构造哈夫曼树,并给出每个字符的哈夫曼编码; (4)将文本文件利用哈夫曼树进行编码,存储成压缩文件(编码文件后缀名.huf)(5)用哈夫曼编码来存储文件,并和输入文本文件大小进行比较,计算文件压缩率;(6)进行译码,将huf文件译码为ASCII编码的txt文件,与原txt文件进行比较。 根据上述过程可以知道该编码译码器的关键在于字符统计和哈夫曼树的创建以及解码。 哈夫曼树的理论创建过程如下: 一、构成初始集合 对给定的n个权值{W1,W2,W3,...,Wi,...,Wn}构成n棵二叉树的初始集合 F={T1,T2,T3,...,Ti,...,Tn},其中每棵二叉树Ti中只有一个权值为Wi的根结 点,它的左右子树均为空。 二、选取左右子树 在F中选取两棵根结点权值最小的树作为新构造的二叉树的左右子树,新二 叉树的根结点的权值为其左右子树的根结点的权值之和。 三、删除左右子树 从F中删除这两棵树,并把这棵新的二叉树同样以升序排列加入到集合F中。 四、重复二和三两步, 重复二和三两步,直到集合F中只有一棵二叉树为止。 因此,有如下分析: 1.我们需要一个功能函数对ASCII码的初始化并需要一个数组来保存它们; 2.定义代表森林的数组,在创建哈夫曼树的过程当中保存被选中的字符,即给定报文 中出现的字符,模拟哈夫曼树选取和删除左右子树的过程; 3.自底而上地创建哈夫曼树,保存根的地址和每个叶节点的地址,即字符的地址,然 后自底而上检索,首尾对换调整为哈夫曼树实现哈弗曼编码; 4.从哈弗曼编码文件当中读入字符,根据当前字符为0或者1的状况访问左子树或者 右孩子,实现解码; 5.使用文件读写操作哈夫曼编码和解码结果的写入; 解题方法: 结构体、数组、类的定义: 1.定义结构体类型的signode 作为哈夫曼树的节点,定义结构体类型的hufnode 作为

《工程系统建模与仿真》实验报告 姓名XXXXXXX 学号XXXXXXX 班级XXXXXXX 专业XXXXXXX 报告提交日期XXXXXXX

实验一 扭摆法测定物体的转动惯量 一、 实验名称 扭摆法测定物体的转动惯量 二、 同组成员 学号 姓名 XXXXXX XXX XXXXXX XXX XXXXXX XXX XXXXXX XXX XXXXXX XXX XXXXXX XXX XXXXXX XXX XXXXXX XXX XXXXXX XXX 三、 实验器材 1) 转动惯量测试仪 2) 数字式电子台秤 3) 游标卡尺 4) 扭摆及几种有规则的待测转动惯量的物体:金属载物圆盘、塑料圆柱体、 木球、验证转动惯量平行轴定理用的金属细杆,杆上有两块可以自由移动的金属滑块。 四、 实验原理 转动惯量的测量,一般都是使刚体以一定形式运动,通过表征这种运动特征的物理量与转动惯量的关系,进行转换测量。本实验使物体作扭转摆动,由于摆动周期及其它参数的测定计算出物体的转动惯量。 扭摆的构造如图 1-1所示,在垂直轴1上装有一根薄片状的螺旋弹簧2,用以产生恢复力矩。在轴的上方可以装上各种待测物体。垂直轴与支座间装有轴承,以降低摩擦力矩。3为水平仪,用来调整系统平衡。 将物体在水平面内转过一定角度θ后,在弹簧的恢复力矩作用下物体就开始绕垂直轴作周期往返扭转运动。 根据虎克定律,弹簧受扭转而产生的恢复力矩M 与所转过的角度θ成正 比,即:M=-Kθ (1) 上式中,K 为弹簧的扭转常数。 由转动定律M =Iβ得:β=M /I (2) 令ω2=K /I ,忽略轴承的摩擦阻力矩,由式(1)、(2)得: 2 22 d K dt I θβθωθ= =-=- 图 1-1 上述方程表示扭摆运动具有角简谐振动的特性,角加速度与角位移成正比, 且方向相反。此方程的解为:θ=Acos (ωt +?)。 式中,A 为谐振动的角振幅,φ为初相位角,ω为角速度,此谐振动的周期

学生实验报告 实验名称用Verilog HDL语句实现74LS181的功能 实验日期2013 年10月19号 学号 姓名 班级计算机科学与技术一班 一、实验目的与要求 1、了解运算器的组成结构; 2、掌握算术逻辑运算器的工作原理; 3、掌握简单运算器的数据传送通道 4、掌握用Verilog HDL实现简单运算器的设计 二、实验原理 74LS181的逻辑功能表 图中,S0到S3是四个控制端,用于选择进行何种运算。M用于控制ALU进行算术

运算还是逻辑运算。 当M=0时,M 对进位信号没有任何影响,Fi 值与操作数Ai ,Bi 以及地位向本位进位Cn+1有关,所以M=0时进行算术运算。操作数用补码表示,“加”只算术加,运算时考虑进位;“+”指逻辑加,不考虑进位;减法运算时,减法取反码运算后用加法器实现,结果输出为A 减B 减1在最末位产生一个强迫进位(加1),以得到A 减B 的结果。 当M=1时,封锁了各位的进位输出Cn+i=0,因此各位的运算结果Fi 仅与操作数Ai ,Bi 有关,此时进行逻辑运算。 三、实验内容与步骤 1.根据书85面的逻辑功能表编写Verilog HDL 语句,编译,仿真等步骤。 2.按照模式一电路图结构图设置对应的引脚参数。确认无误后,配置文件下载。 CLOCK9CLOCK5CLOCK2 CLOCK0 SPEAKER 扬声器 NO.1 PIO11-PIO8PIO15-PIO12PIO48 PIO49D15 D16HEX HEX PIO32 PIO33 PIO34 PIO35 PIO36 PIO37 PIO38 PIO39 D1D2D3D4D5D6D7D8实验电路结构图 译码器 译码器 译码器 译码器 FPGA/CPLD 目标芯片1 2 3 4 5 6 7 8 PIO3-PIO0 PIO7-PIO4HEX HEX 键1 键2 键3 键4 键5 键6 键7 键8 PIO39-PIO32PIO31-PIO28 PIO27-PIO24PIO23-PIO20PIO19-PIO16 3.连接试验箱,开通电源,进行验证。 五、实验环境与设备 实验软件:Quartus ii 软件 实验设备:实验室试验箱 六、实验代码设计(含符号说明) module NS74181(A,B,F,S,CN,CO,M); //端口名 input[3:0] A,B; input[3:0] S; input M,CN; output CO; output[3:0] F; reg[3:0] F; reg[3:0] ta,tb; //用ta,tb 代替~A 和~B reg CO; //进位 always @(S) begin ta=~A; tb=~B; case(S) 'b0000: begin

实验三译码器及其应用 一、实验目的 (1) 掌握中规模集成译码器的逻辑功能和使用方法; (2) 熟悉掌握集成译码器的应用; (3) 掌握集成译码器的扩展方法。 二、实验设备 数字电路实验箱,电脑一台,74LS20,74LS138。 三、实验内容 (1)利用3-8译码器74LS138和与非门74LS20实现函数: 四输入与非门74LS20的管脚图如下: 对函数表达式进行化简: 按Figure 1所示的电路连接。并用Multisim进行仿真,将结果对比。

Figure 1 (2) 用两片74LS138组成4-16线译码器。 因为要用两片3-8实现4-16译码器,输出端子数目刚好够用。 导线测试,在各端子上移动即可。在multisim中仿真电路连接如Figure 2所示(实 验台上的电路没有接下面的两个8灯LED): Figure 2 四、实验结果 (1) 利用3-8译码器74LS138和与非门74LS20实现函数。

输入,由可知,小灯应该亮。测试结果如Figure 1所示。输入,分析知小灯应该灭,测试结果如Figure 2所示。输入 ,分析知小灯应该亮,测试结果如Figure 3所示。 Figure 4 Figure 5

Figure 6 同理测试,得到结果列为下面的真值表: A B C Y 0 0 0 1 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 0 1 1 0 0 1 1 1 1 与所要实现的逻辑功能相一致。 (2) 用两片74LS138组成4-16线译码器。 进行测试,得到的结果列为真值表如下: G1 A B C 1 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 0 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 0 0 0 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 0 0 1 0 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1

《系统工程》实验报告 姓名:**** 班级:**** 学号:**** 指导老师:**** 2014年12 月4 日

实验三 简单库存模型 一、 实验目的 1、 熟悉STELLA 软件的基本操作 2、 加深对系统动力学主要要素和基本思想的理解 3、 学会利用STELLA 软件建立一阶反馈系统模型、仿真运行及结果分析 二、 实验要求 1、简单库存模型各变量及其因果关系图如下图: 2、各变量之间的关系可用如下方程表示: LI?K=I ?J+DT*R1?JK NI=1000 RR1?KL=DK/Z AD?K=Y-I ?K CZ=5 CY=6000 3、要求利用STELLA 建立上述库存模型的流图,仿真计算并分析结果 三、实验步骤 1、确定水准变量、速率变量、辅助变量、常量及水准变量初值; 2、熟悉STELLA 软件操作指导,建立模型的四个基本构造块为:栈(stock )、流(flow )、转换器(converter)、连接器(connector ),设置仿真参数(采用默认值); 2、根据因果关系图连接流; 3、确定水准方程、速率方程、辅助方程、赋初值方程和常量方程; 库存量 库存 差额 订货量 + (—) R1 D I — + 期望库存Y

4、建立模型仿真结果分析所需的数据模块; 5、仿真及结果分析 实验内容: 1.确定水准变量、速率变量、辅助变量、常量及水准变量初值; 2.建立四个基本块,根据关系图连接,如下图 3.确定水准方程、速率方程、辅助方程、赋初值方程和常量方程,并且运行仿真得输出特性示意图,如下图.

4.仿真得出数据随时间变化的精确流程,如下图

《嵌入式操作系统》实验报告 班级计算机 学号 姓名 指导教师庄旭菲

内蒙古工业大学信息工程学院计算机系 2018年6月 实验一 Linux内核移植与编译实验 1. 实验目的 了解 Linux 内核相关知识与内核结构 了解 Linux 内核在 ARM 设备上移植的基本步骤和方法 掌握 Linux 内核裁剪与定制的基本方法 2. 实验内容 分析 Linux 内核的基本结构,了解 Linux 内核在 ARM 设备上移植的一些基本步骤及常识。 学习 Linux 内核裁剪定制的基本配置方法,利用 UP-Magic210 型设备配套 Linux 内核进行自定义功能(如helloworld 显示)的添加,并重新编译内核源码,生成内核压缩文件 zImage,下载到 UP-Magic210 型设备中测试。 3. 实验步骤 实验目录:/UP-Magic210/SRC/kernel/编译内核:在宿主机端为UP-Magic210 设备的Linux 内核编写简单的测试驱动(内核)程序并修改内核目录中相关文件,添加对测试驱动程序的支持。 (1)、使用 vim 编辑器手动编写实验代码

内如如下: #include

PL/0 语言编译器分析实验 一、实验目的 通过阅读与解析一个实际编译器(PL/0语言编译器)的源代码,加深对编译阶段(包括词法分析、语法分析、语义分析、中间代码生成等)和编译系统软件结构的理解,并达到提高学生学习兴趣的目的。 二、实验要求 (1)要求掌握基本的程序设计技巧(C语言)和阅读较大规模程序源代码的能力; (2)理解并掌握编译过程的逻辑阶段及各逻辑阶段的功能; (3)要求能把握整个系统(PL/0语言编译器)的体系结构,各功能模块的功能,各模块之间的接口; (4)要求能总结出实现编译过程各逻辑阶段功能采用的具体算法与技 三、实验报告 pl/0语言是pascal语言的一个子集,我们这里分析的pl/0的编译程序包括了对pl/0语言源程序进行分析处理、编译生成类pcode代码,并在虚拟机上解释运行生成的类pcode代码的功能。 pl/0语言编译程序采用以语法分析为核心、一遍扫描的编译方法。词法分析和代码生成作为独立的子程序供语法分析程序调用。语法分析的同时,提供了出错报告和出错恢复的功能。在源程序没有错误编译通过的情况下,调用类pcode 解释程序解释执行生成的类pcode代码。 词法分析子程序分析: 词法分析子程序名为getsym,功能是从源程序中读出一个单词符号(token),把它的信息放入全局变量sym、id和num中,语法分析器需要单词时,直接从这三个变量中获得。(注意!语法分析器每次用完这三个变量的值就立即调用getsym 子程序获取新的单词供下一次使用。而不是在需要新单词时才调用getsym过程。)getsym过程通过反复调用getch子过程从源程序过获取字符,并把它们拼成单词。getch过程中使用了行缓冲区技术以提高程序运行效率。 词法分析器的分析过程: 调用getsym时,它通过getch过程从源程序中获得一个字符。如果这个字符是字母,则继续获取字符或数字,最终可以拼成一个单词,查保留字表,如果查到为保留字,则把sym变量赋成相应的保留字类型值;如果没有查到,则这个单词应是一个用户自定义的标识符(可能是变量名、常量名或是过程的名字),把sym 置为ident,把这个单词存入id变量。查保留字表时使用了二分法查找以提高效率。如果getch获得的字符是数字,则继续用getch获取数字,并把它们拼成一个整数,然后把sym置为number,并把拼成的数值放入num变量。如果识别出其它合

数电实验报告 实验三译码器及其应用 一、实验目的 1、掌握译码器的测试方法。 2、了解中规模集成译码器的功能,管脚分布,掌握其逻辑功能。 3、掌握用译码器构成组合电路的方法。 4、学习译码器的扩展。 二、实验仪器 1、数字逻辑电路实验板 1块 2、74HC138 3-8线译码器 2片 3、74HC20 双4输入与非门 1片 三、实验原理 1、中规模集成译码器74HC138 74HC138是集成3线-8线译码器,在数字系统中应用比较广泛。图3-1是其引脚排列。 其中 A2 、A1 、A0 为地址输入端, 0Y~ 7Y为译码输出端,S1、2S、3S为使能端。74HC138真值表如下: 74HC138引脚图为:

74HC138工作原理为:当S1=1,S2+S3=0时,电路完成译码功能,输出低电平有效。其中: 2、译码器应用 因为74HC138 三-八线译码器的输出包括了三变量数字信号的全部八种组合,每一个输 出端表示一个最小项,因此可以利用八条输出线组合构成三变量的任意组合电路。 四、实验内容 1、译码器74HC138 逻辑功能测试 (1)控制端功能测试 测试电路如图:

按上表所示条件输入开关状态。观察并记录译码器输出状态。 LED指示灯亮为0,灯不亮为1。 (2)逻辑功能测试 将译码器使能端S1、2S、3S及地址端A2、A1、A0 分别接至逻辑电平开关输出口,八个 输出端Y7 Y0依次连接在逻辑电平显示器的八个输入口上,拨动逻辑电平开关,按下表逐项测试74HC138的逻辑功能。 2、用74HC138实现逻辑函数 Y=AB+BC+CA 如果设A2=A,A1=B,A0=C,则函数Y的逻辑图如上所示。用74HC138和74HC20各一块在实验箱上连接下图线路。并将测试结果下面的记录表中。

简易计算机系统综合设计设计报告 班级姓名学号 一、设计目的 连贯运用《数字逻辑》所学到的知识,熟练掌握EDA工具的使用方法,为学习好后续《计算机原理》课程做铺垫。 二、设计内容 ①按给定的数据格式和指令系统,使用EDA工具设计一台用硬连线逻辑控制的简易计算机系统; ②要求灵活运用各方面知识,使得所设计的计算机系统具有较佳的性能; ③对所做设计的性能指标进行分析,整理出设计报告。 三、详细设计 3.1设计的整体架构 控制信号

3.2各模块的具体实现 1.指令计数器(zhiling_PC) 元件: 输入端口:CLK,RESET,EN; 输出端口:PC[3..0]; CLK:时钟信号; RESET:复位信号; EN:计数器控制信号,为1的时候加一; PC[3..0]:地址输出信号; 代码:

波形图: 总共有九条指令,指令计数器从0000到1000;功能: 实现指令地址的输出; 2.存储器(RAM) 元件: 输入端口:PC[3..0],CLK; 输出端口:zhiling[7..0]; CLK:时钟信号; PC[3..0]:指令地址信号; zhiling[7..0]:指令输出信号; 代码:

波形图: 功能: 根据输入的地址输出相应的指令; 3.指令译码器(zlymq) 元件: 输入端口:zhiling[7..0]; 输出端口:R1[1..0],R2[1..0],M[3..0];zhiling[7..0]:指令信号; R1:目标寄存器地址; R2:源寄存器地址; M[3..0]:指令所代表的操作编号; 代码:

波形图:

功能: 实现指令的操作译码,同时提取出目标寄存器和源寄存器的地址; 4.算术逻辑运算器(ALU) 元件: 输入端口:EN_ALU,a[7..0],b[7..0],M[3..0]; 输出端口:c[7..0],z; EN_ALU:运算器的使能端; a[7..0]:目标寄存器R1的值; b[7..0]:源寄存器R2的值; M[3..0]:指令所代表的操作编号; c[7..0]:运算结果; z:运算完成的信号; 代码:

译码器实验报告 译码器(decoder)是一类多输入多输出组合逻辑电路器件,其可以分为:变量译码和显示译码两类。变量译码器一般是一种较少输入变为较多输出的器件,常见的有n线-2^n线译码和8421BCD 码译码两类;显示译码器用来将二进制数转换成对应的七段码,一般其可分为驱动LED和驱动LCD两类。 译码器是一种具有“翻译”功能的逻辑电路,这种电路能将输入二进制代码的各种状态,按照其原意翻译成对应的输出信号。有一些译码器设有一个和多个使能控制输入端,又成为片选端,用来控制允许译码或禁止译码。 在图1中,74138是一种3线—8线译码器,三个输入端CBA共有8种状态组合(000—111),可译出8个输出信号Y0—Y7。这种译码器设有三个使能输入端,当G2A与G2B均为0,且G1为1时,译码器处于工作状态,输出低电平。当译码器被禁止时,输出高电平。 图2时检测74ls138译码器时间波形的电路,使用的虚拟仪器为数字信号发生器和逻辑分析仪。数字信号发生器在一个周期内按顺序送出两组000—111的方波信号。

图3表明如何将两片3线—8线译码器连接成4线—16线译码器。其中第二片74138的使能端G1和第一片的使能端G2A接成D输入端。当D=0时,第一片74138工作,对0000—0111的输入信号进行译码输出。当D=1时,第二片74138工作,对1000—1111的输入信号进行译码输出。 在图4中,7442为二—十进制译码器,具有4个输入端和10个输出端。输入信号采用8421BCD码,二进制数0000—1001与十进制数0—9对应。当输入超过这个范围是无效,10个输出端均为高电平。7442电路没有使能端,因此只要输入在规定范围内,就会有一个输出端为低电平。 图5位BCD—七段显示译码器电路,LED数码管将显示与BCD码对应的十进制数0—9。因为显示译码器电路输出高电平,所以应该采用共阴极LED数码管。 编码与译码的过程刚好相反。通过编码器可对一个有效输入信号生成一组二进制代码。有的编码器设有使能端,用来控制允许编码或禁止编码。 优先编码器的功能是允许同时在几个输入端有输入信号,编码器按输入信号排定的优先顺序,只对同时输入的几个信号中优先权最