CD4511引脚图及功能

CD4511是一个用于驱动共阴极 LED (数码管)

显示器的 BCD 码—七段码译码器,特点如下:

具有BCD转换、消隐和锁存控制、七段译码及

驱动功能的CMOS电路能提供较大的拉电流。可

直接驱动LED显示器。

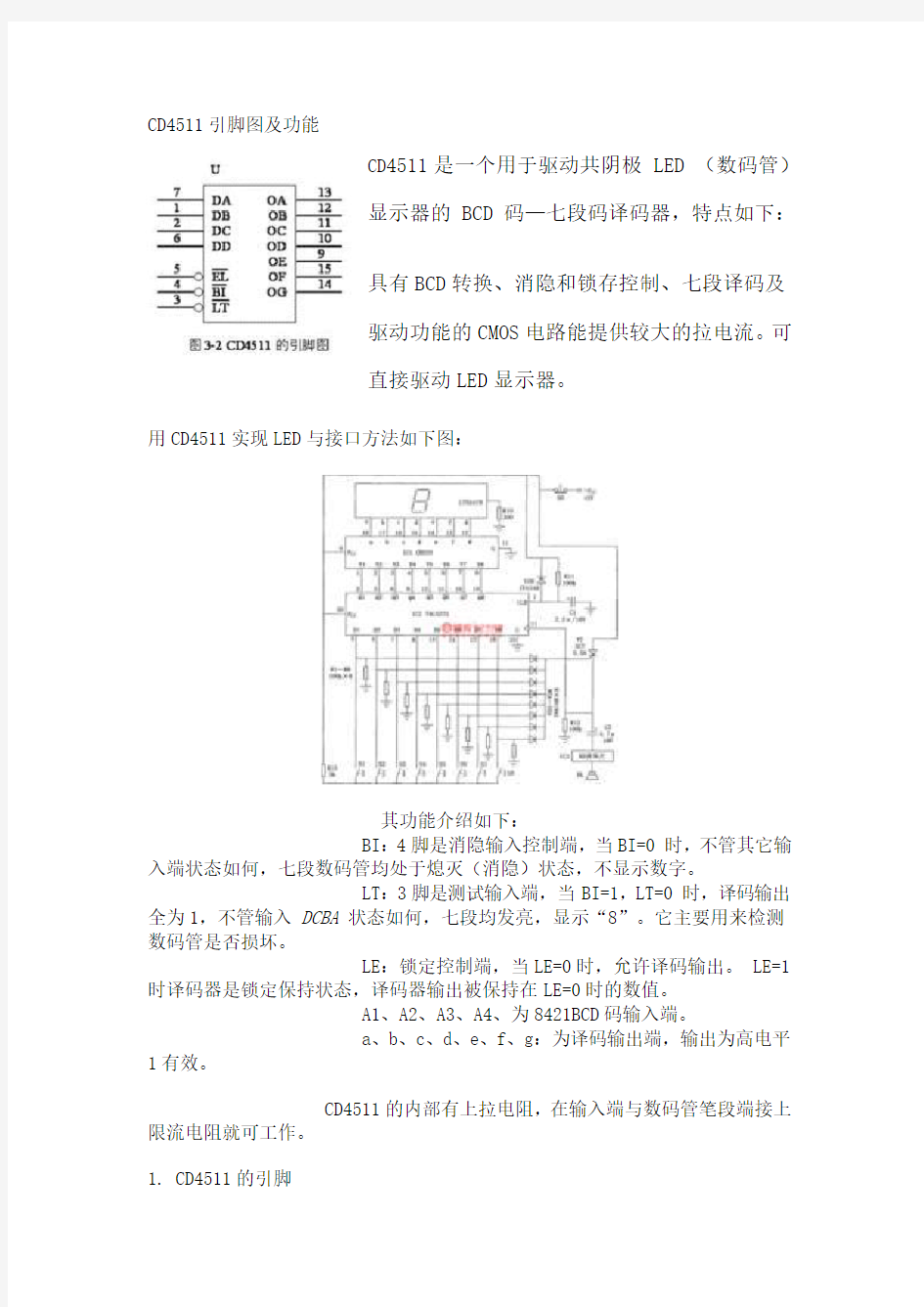

用CD4511实现LED与接口方法如下图:

其功能介绍如下:

BI:4脚是消隐输入控制端,当BI=0 时,不管其它输入端状态如何,七段数码管均处于熄灭(消隐)状态,不显示数字。

LT:3脚是测试输入端,当BI=1,LT=0 时,译码输出全为1,不管输入DCBA 状态如何,七段均发亮,显示“8”。它主要用来检测数码管是否损坏。

LE:锁定控制端,当LE=0时,允许译码输出。 LE=1时译码器是锁定保持状态,译码器输出被保持在LE=0时的数值。

A1、A2、A3、A4、为8421BCD码输入端。

a、b、c、d、e、f、g:为译码输出端,输出为高电平1有效。

CD4511的内部有上拉电阻,在输入端与数码管笔段端接上限流电阻就可工作。

1. CD4511的引脚

CD4511具有锁存、译码、消隐功能,通常以反相器作输出级,通常用以驱动LED。

其引脚图如3-2所示。

各引脚的名称:其中7、1、2、6分别表示A、B、C、D;5、4、3分别表示LE、BI、LT;13、12、11、10、9、15、14分别表示 a、b、c、d、e、f、g。左边的引脚表示输入,右边表示输出,还有两个引脚8、16分别表示的是VDD、VSS。

2. CD4511的工作原理

1.CD4511的工作真值表如表3-2

2.锁存功能

译码器的锁存电路由传输门和反相器组成,传输门的导通或截止由控制端LE的电平状态。

当LE为“0”电平导通,TG2截止;当LE为“1”电平时,TG1截止,TG2导通,此时有锁存作用。如图3-3

(3)译码

CD4511译码用两级或非门担任,为了简化线路,先用二输入端与非门对输入数据B、C进行组合,得出、、、四项,然后将输入的数据A、D一起用或

非门译码。

(4)消隐

BI为消隐功能端,该端施加某一电平后,迫使B端输出为低电平,字形消隐。消隐控制电路如图3-4所示。

消隐输出J的电平为

J= =(C+B)D+BI

如不考虑消隐BI项,便得J=(B+C)D

据上式,当输入BCD代码从1010---1111时,J端都为“1”电平,从而使显示器中的字形消隐。

表3-2 CD 4511的真值表

CD4518/CC4518是二、十进制(8421编码)同步加计数器,内含两个单元的加计数器,其功能表如真值表所示。每单个单元有两个时钟输入端CLK和EN,可用时钟脉冲的上升沿或下降沿触发。由表可知,若用ENABLE信号下降沿触发,触发信号由EN端输入,CLK端置“0”;若用CL℃K信号上升沿触发,触发信号由CL℃K端输入,ENABLE端置“1”。RESET端是清零端,RESET端置“1”时,计数器各端输出端Q1~Q4均为“0”,只有RESET端置“0”时,CD4518才开始计数。

CD4518采用并行进位方式,只要输入一个时钟脉冲,计数单元Q1翻转一次;当Q1为1,Q4为0时,每输入一个时钟脉冲,计数单元Q2翻转一次;当Q1=Q2=1时,每输入一个时钟脉冲Q3翻转一次;当Q1=Q2=Q3=1或Q1=Q4=1时,每输入一个时钟脉冲Q4翻转一次。这样从初始状态(“0”态)开始计数,每输入10个时钟脉冲,计数单元便自动恢复到“0”态。若将第一个加计数器的输出端Q4A作为第二个加计数器的输入端ENB的时钟脉冲信号,便可组成两位8421编码计数器,依次下去可以进行多位串行计数。

CD4520/CC4520为二进制加计数器,由两个相同的内同步4级计数器构成。计数器级为D

型触发器,具有内部可交换CP和EN线,用于在时钟上升沿或下降沿加计数。在单个单元运算中,EN输入保持高电平,且在CP上升沿进位。CR线为高电平时,计数器清零。计数器在脉动模式可级联,通过将Q3连接至下—计数器的EN输入端可实现级联,同时后者的CP输入保持低电平。

引脚功能:

CD4518 CD4520 引脚图

CD4518逻辑图

CD4520逻辑图

真值表功能:

CD4518 CD4520时序图

典型应用电路:

纹波串联4个计数器正极性边缘触发

同步串联二进制计数器负边缘触发

功能图极限参数:

op07的功能介绍:Op07芯片是一种低噪声,非斩波稳零的双极性运算放大器集成电路。由于OP07具有非常低的输入失调电压(对于OP07A最大为25μV),所以OP07在很多应用场合不需要额外的调零措施。OP07同时具有输入偏置电流低(OP07A为±2nA)和开环增益高(对于OP07A为300V/mV)的特点,这种低失调、高开环增益的特性使得OP07特别适用于高增益的测量设备和放大传感器的微弱信号等方面。 特点: 超低偏移:150μV最大。 低输入偏置电流:1.8nA 。 低失调电压漂移:0.5μV/℃。 超稳定,时间:2μV/month最大 高电源电压范围:±3V至±22V 图1 OP07外型图片 图2 OP07 管脚图 OP07芯片引脚功能说明: 1和8为偏置平衡(调零端),2为反向输入端,3为正向输入端,4接地,5空脚6为输出,7接电源+ 图3 OP07内部

电路图 ABSOLUTE MAXIMUM RATINGS 最大额定值 Sy mb ol 符号Parameter参数 Value 数值 Unit 单位 VC C Supply Voltage 电源电压±22 V Vid Differential Input Voltage差分输入电 压 ±30 V Vi Input Voltage 输入电压±22 V Top er Operating Temperature 工作温度 -40 to +105 ℃ Tst g Storage T emperature 贮藏温度 -65 to +150 ℃ 电气特性 虚拟通道连接= ± 15V ,Tamb = 25 ℃(除非另有说明) Sy mb Parameter 参数及测试条件最小典最 Uni t

2016/2/10 笔记一:分配引脚的四种方法:(Quartus II 13.0sp1 (64-bit)) 1、常规方法,利用Pin Planner命令,适用于引脚使用比较少的工程,简洁方便; 2、使用.csv文件进行引脚分配: 步骤一:利用记事本新建一个.csv的格式文件,内容格式如图下图所示,然后保存; 步骤二:选择菜单栏Assignments-->Import Assignment,添加刚才生成的文件路径;

步骤三:点击OK,引脚分配完成。 注意:.csv文件保存路径不要有中文,建议保存在工程文件夹下。 3、使用.qsf文件进行引脚分配: 步骤一:在Quartus II中打开.qsf文件(系统默认生成.qsf文件,默认保存在该工程文件夹下) 步骤二:添加以下格式内容,格式如下图所示; 步骤三:点击保存,引脚分配完成。 4、使用.tcl文件进行引脚分配: 步骤一:生成.tcl文件,选择菜单栏Project-->Generate Tcl File For Project,点击OK,默认保存路径为该工程文件夹; 步骤二:添加以下格式内容,格式和.qsf文件格式一致; 步骤三:选择菜单栏Tool-->Tcl Scripts,选择生成的.tcl文件,点击Run,引脚分配完成。

说明:在实际的应用过程中,我们应该根据工程的子模块个数和引脚的使用多少来选择合适的引脚分配方式,笔者总结了以下几条:(不喜勿喷,还望多多赐教) 1、工程中使用的引脚数为个位数时,并且特别少,建议使用常规方法,利用Pin Planner 命令进行引脚分配; 2、工程中只有一个子模块时,如果引脚众多,尤其使用到数码管显示时,建议使用.tcl 文件进行引脚分配; 如图所示,.tcl文件中标识符和变量名已经给出,只需要输入对应引脚,比较方便。在多子模块的情况下,.tcl文件中没有给出标识符和变量名,这点需要注意。 3、多个子模块,使用引脚众多的情况下,利用.tcl文件、.csv文件和.qsf文件进行引脚分配大同小异,不过个人更喜欢利用.csv文件进行引脚分配,因为格式相对简单。

Quartus II中FPGA管脚的分配策略 编写:*** 校核: 审核: 二〇一年月日

目录 目录..........................................................................................I QUARTUS II中FPGA管脚分配策略.. (1) 1.FPGA管脚介绍 (1) 1.1.电源管脚 (1) 1.2.配置管脚 (2) 1.3.普通I/O管脚 (2) 1.4.时钟管脚 (2) 2.FPGA管脚分配方法 (3) 2.1.P IN P LANNER方式 (3) 2.2.I MPORT A SSIGNMENTS方式 (4) 2.3.T CL S CRIPTS方式 (6) 2.4.项目组统一使用方式 (9) 3.编写FPGA管脚分配文件 (10) 3.1.查看PDF格式的原理图 (10) 3.2.查看P RJ PCB格式的原理图 (11) 4.保存FPGA管脚分配文件 (12) 4.1.T CL格式或CSV格式 (12) 4.2.QSF格式 (12) 4.3.项目组统一使用格式 (12) 附录管脚类型说明 (13)

Quartus II中FPGA管脚分配策略 1. FPGA管脚介绍 FPGA的管脚从使用对象来说可分为两大类:专用管脚和用户自定义管脚。一般情况下,专用管脚大概占FPGA管脚数的20% ~ 30%,剩下的70% ~ 80%为用户自定义管脚。从功能上来说可分为电源管脚、配置管脚、时钟管脚、普通I/O管脚等。 下面以Altera公司的Cyclone IV E系列芯片EP4CE30F23C8为例,如图1所示,芯片总共包含484个芯片管脚。图中不同颜色的区域代表不同的Bank,整个芯片主要分为8个Bank,FPGA的各个管脚分布在不同的Bank中。 其中,三角形标记的管脚为电源管脚,正三角表示VCC,倒三角表示GND,三角内部的O表示I/O管脚电源,I表示内核电源。 圆形标记的管脚为普通用户I/O管脚,可以由用户随意使用。 正方形标记且内部有时钟沿符号的管脚为全局时钟管脚。 五边形标记的管脚为配置管脚。 图1 Wire Bond 1.1. 电源管脚 FPGA通常需要两个电压才能运行,一个是内核电压,另一个是I/O电压。每个电压通过独立的电源管脚来提供。内核电压是用来给FPGA内部的逻辑门和触发器供电。随着FPGA的发展,内核电压从5V、3.3V、2.5V、1.8V到1.5V ,变得越来越低。I/O电压用来给各个Bank供电,每个Bank 都有独立的I/O电压输入。一般情况下,内核电压会比I/O电压低。

在Quartus II中分配管脚的两种常用方法. 示范程序 seg7_test.v 此例化文件共需要17个管脚。接下来我和大家一起讨论使用QII分配管脚的两种常用方法。 方法一:Import Assignments 步骤1:使用记事本或类似软件新建一个txt文件(或csv文件),按如下格式编写管脚分配内容(不同的开发版,其内容也不同,本文以我使用的艾米电子2C8开发版为范例)。注意:To和Location两个关键字中间有一个半角逗号。

图1 pin.txt 步骤2:在QII软件中,选择“Assignments ——Import Assignments”。如图所示,导入xxx.txt文件即可。 图2 导入pin.txt 步骤3:在QII软件中,选择“Assignments ——Pin”标签(或者点击按钮),打开Pin Planner,验证管脚是否分配正确。

图3 验证管脚是否分配正确 方法二:source xxx.tcl 步骤1:在QII软件中,使用“Assignments ——Remove Assignments”标签,移除管脚分配内容,以确保此次操作,分配的管脚没有因为覆盖而出现错误的情况。

图4 Remove Assignments 注:在未执行任何管脚分配操作新工程中,可跳过步骤1。 步骤2:使用记事本或类似软件新建一个tcl文件,按如下格式编写管脚分配内容(不同的开发版,其内容也不同,本文以我使用的艾米电子2C8开发版为范例)。 注意关键字set_location_assignment和-to的用法。

图5 pin.tcl 步骤3:执行pin.tcl 方法1:在QII软件中,使用“View ——Utility Windows ——Tcl Console”标签,打开Quartus II Tcl Console。执行语句: 图6 source pin.tcl 方法2:在QII软件中,使用“Tools ——Tcl Scripts …”标签,打开Tcl Scripts。

FPGA管脚分配需要考虑的因素 在芯片的研发环节,FPGA验证是其中的重要的组成部分,如何有效的利用FPGA的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从研发的时间段上来考虑这种方法往往是不可取的,RTL 验证与验证板设计必须是同步进行的,在验证代码出来时验证的单板也必须设计完毕,也就是管脚的分配也必须在设计代码出来之前完成。所以,管脚的分配更多的将是依赖人,而非工具,这个时候就更需要考虑各方面的因素。 综合起来主要考虑以下的几个方面: 1、FPGA所承载逻辑的信号流向。 IC验证中所选用的FPGA一般逻辑容量都非常大,外部的管脚数量也相当的丰富,这个时候就必须考虑到PCB设计时的布线的难度,如果管脚的分配不合理,那么有可能在PCB设计时出现大量的交叉的信号线,这给布线带来很大的困难,甚至走不通,或者是即便是布线走通了,也有可能由于外部的延时过大而不满足时序方面的要求。所以在管脚分配前对FPGA工作的环境要相当的熟悉,要对其中的信号来自哪里去向何方非常的清楚,这就按照连线最短的原则将对应的信号分配到与外部器件连线最近的BANK中,2、掌握FPGA内部BANK的分配的情况。 现在FPGA内部都分成几个区域,每个区域中可用的I/O管脚数量各不相同。在IC验证中都是采用了ALTERA 与XILINX系列的FPGA ,这两个厂商的FPGA中内部BANK 的分配有一定的差异,这可以在设计中查阅相关的手册。下面与ALTERA中Stratix II 系列的FPGA内部BANK的分配为例来进行说明。 图中详细说明了FPGA内部BANK的分配情况和每个BANK中所支持的I/O标准。根

莈螃莃莈虿肁膆op07的功能介绍:Op07芯片是一种低噪声,非斩波稳零的双极性运算放大器集成电路。由于OP07具有非常低的输入失调电压(对于OP07A最大为25μV),所以OP07在很多应用场合不需要额外的调零措施。OP07同时具有输入偏置电流低(OP07A为±2nA)和开环增益高(对于OP07A为300V/mV)的特点,这种低失调、高开环增益的特性使得OP07特别适用于高增益的测量设备和放大传感器的微弱信号等方面。 袃膅薈蒁膁螄蒈特点: 蚃蚈罿莀薆蚈膀超低偏移:150μV最大。 低输入偏置电流:1.8nA 。 低失调电压漂移:0.5μV/℃。 超稳定,时间:2μV/month最大 高电源电压范围:±3V至±22V 袈螀薀肃螈螇肂图1 OP07外型图片 芈蚀袅羈蕿节蒄图2 OP07 管脚图 膄蒃膇莁蒂芆肇OP07芯片引脚功能说明: 1和8为偏置平衡(调零端),2为反向输入端,3为正向输入端,4接地,5空脚6为输出,7接电源+

芅芇衿薂袄膇肀图3 OP07内部电路图 蒇蚀螁蚆莇蚈莄ABSOLUTE MAXIMUM RATINGS 最大额定值 芈羁膃薇 葿蒃螂 Sy mb ol 符号肁羅螆芁蚃薄蚇Parameter参数 薃袆蝿袃莆螆肀 Value 数值 Unit 单位 VC C Supply Voltage 电源电压±22 V Vid Differential Input Voltage差分输入电 压 ±30 V Vi Input Voltage 输入电压±22 V Top er Operating Temperature 工作温度 -40 to +105 ℃ Tst g Storage T emperature 贮藏温度 -65 to +150 ℃ 电气特性

第二种:建立TCL文件进行管脚分配。这种方法比较灵活,是比较常用的。 这种方法具有分配灵活,方便快捷,可重用性等多方面优点。方法如下: 选择Projects菜单项,并选择Generate tcl file for project选项,系统会为你自动生成相应文件,然后你只要向其中添加你的分配内容就可以了。还有一种方法就是直接用new ,新建一个TCL文件即可,具体不再细讲。 下面是我分配的内容一部分,可供大家参考。 set_global_assignment -name FAMILY Cyclone set_global_assignment -name DEVICE EP1C3T144C8 set_global_assignment -name ORIGINAL_QUARTUS_VERSION 8.0 set_global_assignment -name PROJECT_CREATION_TIME_DATE "19:14:58 JANUARY 06, 2009" set_global_assignment -name LAST_QUARTUS_VERSION 8.0 set_global_assignment -name USE_GENERATED_PHYSICAL_CONSTRAINTS OFF -section_id eda_palace set_global_assignment -name DEVICE_FILTER_PACKAGE "ANY QFP" set_global_assignment -name LL_ROOT_REGION ON -section_id "Root Region" set_global_assignment -name LL_MEMBER_STATE LOCKED -section_id "Root Region" set_global_assignment -name DEVICE_FILTER_PIN_COUNT 144 set_global_assignment -name DEVICE_FILTER_SPEED_GRADE 8 set_global_assignment -name FITTER_EFFORT "STANDARD FIT" set_global_assignment -name BDF_FILE topDesign.bdf set_global_assignment -name QIP_FILE nios.qip set_global_assignment -name QIP_FILE altpll0.qip

OP07C中文资料 篇一:op07管脚、原理及其应用电路中文资料 一、Op07芯片是一种低噪声,非斩波稳零的单运算放大器集成电路。由于OP07具有非常低的输入失调电压(对于OP07A最大为25μV),所以OP07在很多应用场合不需要额外的调零措施。OP07同时具有输入偏置电流低(OP07A为±2nA)和开环增益高(对于OP07A 为300V/mV)的特点,这种低失调、高开环增益的特性使得OP07特别适用于高增益的测量设备和放大传感器的微弱信号等方面。 二、OP07特点: 超低偏移: 150μV最大。 低输入偏置电流:。 低失调电压漂移:μV/℃。 超稳定,时间: 2μV/month最大 高电源电压范围:±3V至±22V 三、OP07内部结构原理图 四、OP07芯片引脚功能说明: 1和8为偏置平衡(调零端),2为反向输入端,3为正向输入端,4接地,5空脚 6为输出,7接电源 + ABSOLUTE MAXIMUM RATINGS 最大额定值 五、OP07典型应用电路

图4 输入失调电压调零电路 图5 典型的偏置电压试验电路 图6 老化电路 图7 典型的低频噪声放大电路 图8 高速综合放大器 图9 选择偏移零电路 图10 调整精度放大器 图11高稳定性的热电偶放大器 图12 精密绝对值电路 篇二:OP07中文 op07 的功能介绍:Op07芯片是一种低噪声,非斩波稳零的双极性运算放大器集成电路。由于OP07具有非常低的输入失调电压(对于OP07A最大为25μV),所以OP07在很多应用场合不需要额外的调零措施。OP07同时具有输入偏置电流低(OP07A为±2nA)和开环增益高(对于OP07A为300V/mV)的特点,这种低失调、高开环增益的特性使得OP07特别适用于高增益的测量设备和放大传感器的微弱信号等方面。特点: 超低偏移: 150μV最大。低输入偏置电流:。低失调电压漂移:μV/℃。超稳定,时间: 2μV/month最大高电源电压范围:±3V至±22V 工作电源电压范围是±3V~±18V;OP07完全可以用单电源供电,

op07中文资料 时间:2009-05-16 07:42:22 来源:资料室作者: op07的功能介绍:Op07芯片是一种低噪声,非斩波稳零的双极性运算放大器集成电路。由于OP07具有非常低的输入失调电压(对于OP07A最大为25μV),所以OP07在很多应用场合不需要额外的调零措施。OP07同时具有输入偏置电流低(OP07A为±2nA)和开环增益高(对于OP07A 为300V/mV)的特点,这种低失调、高开环增益的特性使得OP07特别适用于高增益的测量设备和放大传感器的微弱信号等方面。 特点: 超低偏移:150μV最大。 低输入偏置电流:1.8nA 。 低失调电压漂移:0.5μV/℃。 超稳定,时间:2μV/month最大 高电源电压范围:±3V至±22V 工作电源电压范围是±3V~±18V;OP07完全可以用单电源供电,你说的+5V,-5V绝对没有问题,用单+5V也可以供电,但是线性区间太小,单电源供电,模拟地在1/2 VCC. 建议电源最好>8V,否则线性区实在太小,放大倍数无法做大,一不小心,就充顶饱和了。我一直用+12V,-12V双电源供电。 图1 OP07外型图片

图2 OP07 管脚图 OP07芯片引脚功能说明: 1和8为偏置平衡(调零端),2为反向输入端,3为正向输入端,4接地,5空脚6为输出,7接电源+ 图3 OP07内部电路图 ABSOLUTE MAXIMUM RATINGS 最大额定值 Sym Parameter参数Value数值Unit 单位bol 符号

VCC Supply Voltage 电源电压±22V Vid Differential Input Voltage差分输入电压±30V Vi Input Voltage 输入电压±22V Tope r Operating Temperature 工作温度 -40 to +105 ℃ Tstg Storage Temperature 贮藏温度-65 to +150 ℃ 电气特性 虚拟通道连接= ± 15V ,T amb = 25 ℃(除非另有说明)Sym bol 符号Parameter 参数及测试条件最小 典 型 最 大 Unit 单位 Vio Input Offset Voltage 输入失调电压0℃≤T amb ≤ +70℃ - 60 1 5 2 5 μV Long Term Input Offset Voltage Stability-(note 1) 长期输入偏置电压的稳定性 -0.42 μV/M o DVio Input Offset Voltage Drift 输入失调电压漂移-0.51. 8 μV/ ℃ Iio Input Offset Current输入失调电流0℃≤T amb≤ +70℃-0.86 8 nA DIio Input Offset Current Drift 输入失调电流漂移-155 pA/ ℃ Iib Input Bias Current输入偏置电流0℃≤T amb ≤ +70℃-1.8 7 9 nA DIib Input Bias Current Drift 输入偏置电流漂移-155 pA/ ℃ Ro Open Loop Output Resistance 开环输出电阻-60-ΩRid Differential Input Resistance 差分输入电阻-33-MΩRic Common Mode Input Resistance 共模输入电阻-12-GΩ

小時不識月Stupid & Hungry 时常记记,以防忘记!FPGA相关事宜,请在新浪微博@COM张一同讨论。。。[原创].在Quartus II中分配管脚的两种常用方法 示范程序 seg7_test.v 此例化文件共需要17个管脚。接下来我和大家一起讨论使用QII分配管脚的两种常用方法。方法一:Import Assignments

步骤1:使用记事本或类似软件新建一个txt文件(或csv文件),按如下格式编写管脚分配内容(不同的开发版,其内容也不同,本文以我使用的艾米电子2C8开发版为范例)。 注意:To和Location两个关键字中间有一个半角逗号。 图1 pin.txt 步骤2:在QII软件中,选择“Assignments ——Import Assignments”。如图所示,导入xxx.txt文件即可。 图2 导入pin.txt

步骤3:在QII软件中,选择“Assignments ——Pin”标签(或者点击按钮),打开Pin Planner,验证管脚是否分配正确。 图3 验证管脚是否分配正确 方法二:source xxx.tcl 步骤1:在QII软件中,使用“Assignments ——Remove Assignments”标签,移除管脚分配内容,以确保此次操作,分配的管脚没有因为覆盖而出现错误的情况。

图4 Remove Assignments 注:在未执行任何管脚分配操作新工程中,可跳过步骤1。 步骤2:使用记事本或类似软件新建一个tcl文件,按如下格式编写管脚分配内容(不同的开发版,其内容也不同,本文以我使用的艾米电子2C8开发版为范例)。 注意关键字set_location_assignment和-to的用法。

Quartus II中FPGA管脚分配策略Quartus II中FPGA管脚的分配策略 编写:*** 校核: 审核: 二〇一年月日

目录 目录 目录..........................................................................................I QUARTUS II中FPGA管脚分配策略.. (1) 1.FPGA管脚介绍 (1) 1.1.电源管脚 (1) 1.2.配置管脚 (2) 1.3.普通I/O管脚 (2) 1.4.时钟管脚 (2) 2.FPGA管脚分配方法 (3) 2.1.P IN P LANNER方式 (3) 2.2.I MPORT A SSIGNMENTS方式 (3) 2.3.T CL S CRIPTS方式 (6) 2.4.项目组统一使用方式 (8) 3.编写FPGA管脚分配文件 (9) 3.1.查看PDF格式的原理图 (9) 3.2.查看P RJ PCB格式的原理图 (10) 4.保存FPGA管脚分配文件 (11) 4.1.T CL格式或CSV格式 (11) 4.2.QSF格式 (11) 4.3.项目组统一使用格式 (11) 附录管脚类型说明 (12)

Quartus II中FPGA管脚分配策略 1.FPGA管脚介绍 FPGA的管脚从使用对象来说可分为两大类:专用管脚和用户自定义管脚。一般情况下,专用管脚大概占FPGA管脚数的20% ~ 30%,剩下的70% ~ 80%为用户自定义管脚。从功能上来说可分为电源管脚、配置管脚、时钟管脚、普通I/O管脚等。 下面以Altera公司的Cyclone IV E系列芯片EP4CE30F23C8为例,如图1所示,芯片总共包含484个芯片管脚。图中不同颜色的区域代表不同的Bank,整个芯片主要分为8个Bank,FPGA的各个管脚分布在不同的Bank中。 其中,三角形标记的管脚为电源管脚,正三角表示VCC,倒三角表示GND,三角内部的O表示I/O管脚电源,I表示内核电源。 圆形标记的管脚为普通用户I/O管脚,可以由用户随意使用。 正方形标记且内部有时钟沿符号的管脚为全局时钟管脚。 五边形标记的管脚为配置管脚。 图1 Wire Bond 1.1.电源管脚 FPGA通常需要两个电压才能运行,一个是内核电压,另一个是I/O电压。每个电压通过独立的电源管脚来提供。内核电压是用来给FPGA内部的逻辑门和触发器供电。随着FPGA的发展,内核电压从5V、3.3V、2.5V、1.8V到1.5V ,变得越来越低。I/O电压用来给各个Bank供电,每个Bank都有独立的I/O电压输入。一般情况下,内核电压会比I/O电压低。

op07中文资料 op07的功能介绍:Op07芯片是一种低噪声,非斩波稳零的双极性运算放大器集成电路。由于OP07具有非常低的输入失调电压(对于OP07A最大为25μV),所以OP07在很多应用场合不需要额外的调零措施。OP07同时具有输入偏置电流低(OP07A为±2nA)和开环增益高(对于OP07A 为300V/mV)的特点,这种低失调、高开环增益的特性使得OP07特别适用于高增益的测量设备和放大传感器的微弱信号等方面。 特点: 超低偏移:150μV最大。 低输入偏置电流: 1.8nA 。 低失调电压漂移:0.5μV/℃。 超稳定,时间:2μV/month最大 高电源电压范围:±3V至±22V 工作电源电压范围是±3V~±18V;OP07完全可以用单电源供电,你说的+5V,-5V绝对没有问题,用单+5V也可以供电,但是线性区间太小,单电源供电,模拟地在1/2 VCC. 建议电源最好>8V,否则线性区实在太小,放大倍数无法做大,一不小心,就充顶饱和了。我一直用+12V,-12V双电源供电。 图1 OP07外型图片

图2 OP07 管脚图 OP07芯片引脚功能说明: 1和8为偏置平衡(调零端),2为反向输入端,3为正向输入端,4接地,5空脚6为输出,7接电源+ 图3 OP07内部电路图 ABSOLUTE MAXIMUM RATINGS 最大额定值 Sym bol Parameter参数Value数值Unit 单位符号

VCC Supply Voltage 电源电压±22V Vid Differential Input Voltage差分输入电压±30V Vi Input Voltage 输入电压±22V Tope r Operating Temperature 工作温度 -40 to +105 ℃ Tstg Storage Tem perature 贮藏温度-65 to +150 ℃ 电气特性 虚拟通道连接= ± 15V ,Tam b = 25 ℃(除非另有说明)Sy mb ol 符号Parameter 参数及测试条件 最 小 典型最大 Uni t 单 位 Vio Input Offset Voltage 输入失调电压0℃ ≤ Tam b ≤ +70℃ - 60 150 250μV Long Term Input Offset Voltage Stability-(note 1) 长期输入偏置电压的 稳定性 -0.42 μV/ Mo DVi o Input Offset Voltage Drift 输入失调电 压漂移 -0.5 1.8 μV/ ℃ Iio Input Offset Current输入失调电流 0℃≤Tamb≤ +70℃ -0.8 6 8nA DIio Input Offset Current Drift 输入失调电 流漂移 -1550 pA/ ℃ Iib Input Bias Current输入偏置电流 0℃≤Tamb ≤ +70℃ - 1.8 7 9 nA DIib Input Bias Current Drift 输入偏置电流 漂移 -1550 pA/ ℃ Ro Open Loop Output Resistance 开环输 出电阻 -60-Ω Rid Differential Input Resistance 差分输 入电阻 -33-MΩ Ric Common Mode Input Resistance 共 模输入电阻 -120-GΩ

op07中文资料数据手册 时间:2009-05-16 07:42:22 来源:资料室作者: op07的功能介绍:Op07芯片是一种低噪声,非斩波稳零的双极性运算放大器集成电路。由于OP07具有非常低的输入失调电压(对于OP07A最大为25μV),所以OP07在很多应用场合不需要额外的调零措施。OP07同时具有输入偏置电流低(OP07A为±2nA)和开环增益高(对于OP07A 为300V/mV)的特点,这种低失调、高开环增益的特性使得OP07特别适用于高增益的测量设备和放大传感器的微弱信号等方面。 特点: 超低偏移:150μV最大。 低输入偏置电流:1.8nA 。 低失调电压漂移:0.5μV/℃。 超稳定,时间:2μV/month最大 高电源电压范围:±3V至±22V 工作电源电压范围是±3V~±18V;OP07完全可以用单电源供电,你说的+5V,-5V绝对没有问题,用单+5V也可以供电,但是线性区间太小,单电源供电,模拟地在1/2 VCC. 建议电源最好>8V,否则线性区实在太小,放大倍数无法做大,一不小心,就充顶饱和了。我一直用+12V,-12V双电源供电。 图1 OP07外型图片

图2 OP07 管脚图 OP07芯片引脚功能说明: 1和8为偏置平衡(调零端),2为反向输入端,3为正向输入端,4接地,5空脚6为输出,7接电源+ 图3 OP07内部电路图 ABSOLUTE MAXIMUM RATINGS 最大额定值 Sym Parameter参数Value数值Unit 单位bol 符号

VCC Supply Voltage 电源电压±22V Vid Differential Input Voltage差分输入电压±30V Vi Input Voltage 输入电压±22V Tope r Operating Temperature 工作温度 -40 to +105 ℃ Tstg Storage Temperature 贮藏温度-65 to +150 ℃ 电气特性 虚拟通道连接= ± 15V ,T amb = 25 ℃(除非另有说明)Sym bol 符号Parameter 参数及测试条件最小 典 型 最 大 Unit 单位 Vio Input Offset Voltage 输入失调电压0℃≤T amb ≤ +70℃ - 60 1 5 2 5 μV Long Term Input Offset Voltage Stability-(note 1) 长期输入偏置电压的稳定性 -0.42 μV/M o DVio Input Offset Voltage Drift 输入失调电压漂移-0.51. 8 μV/ ℃ Iio Input Offset Current输入失调电流0℃≤T amb≤ +70℃-0.86 8 nA DIio Input Offset Current Drift 输入失调电流漂移-155 pA/ ℃ Iib Input Bias Current输入偏置电流0℃≤T amb ≤ +70℃-1.8 7 9 nA DIib Input Bias Current Drift 输入偏置电流漂移-155 pA/ ℃ Ro Open Loop Output Resistance 开环输出电阻-60-ΩRid Differential Input Resistance 差分输入电阻-33-MΩRic Common Mode Input Resistance 共模输入电阻-12-GΩ

二、管脚分配方法 FPGA 的管脚分配,除了在QII软件中,选择“Assignments ->Pin”标签(或者点击按钮),打开Pin Planner,分配管脚外,还有以下2种方法。 方法一:Import Assignments 步骤1: 使用记事本或类似软件新建一个txt文件(或csv文件),按如下格式编写管脚分配内容(不同的开发版,其内容也不同,本文以我使用的DIY_DE2开发板为范例)。【这种方式格式最为简单】 注意:To和Location两个关键字中间有一个半角逗 号。 图1 pin.txt 步骤2: 在QII软件中,选择“Assignments -> Import Assignments”。如图所示,导入xxx.txt或者xxx.csv文件即可

图2 导入pin.txt 步骤3: 在QII软件中,选择“Assignments -> Pin”标签(或者点击按钮),打开Pin Planner,验证管脚是否分配正确。

图3 验证管脚是否分配正确 方法二:导入source xxx.tcl文件 步骤1: 在QII软件中,使用“Assignments -> Remove Assignments”标签,移除管脚分配内容,以确保此次操作,分配的管脚没有因为覆盖而出现错误的情况。

图4 Remove Assignments 注:在未执行任何管脚分配操作新工程中,可跳过步骤1。 步骤2: 使用记事本或类似软件新建一个tcl文件,按如下格式编写管脚分配内容(不同的开发版,其内容也不同,本文以我使用的DIY_DE2开发板为范例)。 注意关键字set_location_assignment和-to的用法。

六附录表DE2平台的引脚分配表 表6- 1 SDRAM pin assignments Signal Name FPGA Pin No. Description DRAM_ADDR[0] PIN_T6 SDRAM Address[0] DRAM_ADDR[1] PIN_V4 SDRAM Address[1] DRAM_ADDR[2] PIN_V3 SDRAM Address[2] DRAM_ADDR[3] PIN_W2 SDRAM Address[3] DRAM_ADDR[4] PIN_W1 SDRAM Address[4] DRAM_ADDR[5] PIN_U6 SDRAM Address[5] DRAM_ADDR[6] PIN_U7 SDRAM Address[6] DRAM_ADDR[7] PIN_U5 SDRAM Address[7] DRAM_ADDR[8] PIN_W4 SDRAM Address[8] DRAM_ADDR[9] PIN_W3 SDRAM Address[9] DRAM_ADDR[10] PIN_Y1 SDRAM Address[10] DRAM_ADDR[11] PIN_V5 SDRAM Address[11] DRAM_DQ[0] PIN_V6 SDRAM Data[0] DRAM_DQ[1] PIN_AA2 SDRAM Data[1] DRAM_DQ[2] PIN_AA1 SDRAM Data[2] DRAM_DQ[3] PIN_Y3 SDRAM Data[3] DRAM_DQ[4] PIN_Y4 SDRAM Data[4] DRAM_DQ[5] PIN_R8 SDRAM Data[5] DRAM_DQ[6] PIN_T8 SDRAM Data[6] DRAM_DQ[7] PIN_V7 SDRAM Data[7] DRAM_DQ[8] PIN_W6 SDRAM Data[8] DRAM_DQ[9] PIN_AB2 SDRAM Data[9] DRAM_DQ[10] PIN_AB1 SDRAM Data[10] DRAM_DQ[11] PIN_AA4 SDRAM Data[11] DRAM_DQ[12] PIN_AA3 SDRAM Data[12] DRAM_DQ[13] PIN_AC2 SDRAM Data[13] DRAM_DQ[14] PIN_AC1 SDRAM Data[14] DRAM_DQ[15] PIN_AA5 SDRAM Data[15] DRAM_BA_0 PIN_AE2 SDRAM BankAddress[0] DRAM_BA_1 PIN_AE3 SDRAM BankAddress[1] DRAM_LDQM PIN_AD2 SDRAM Low-byte DataMask DRAM_UDQM PIN_Y5 SDRAM High-byte DataMask DRAM_RAS_N PIN_AB4 SDRAM RowAddressStrobe DRAM_CAS_N PIN_AB3 SDRAM Column AddressStrobe DRAM_CKE PIN_AA6 SDRAM Clock Enable DRAM_CLK PIN_AA7 SDRAM Clock DRAM_WE_N PIN_AD3 SDRAM WriteEnable

详解Arduino Uno开发板的引脚分配图及定义(重 要且基础) 首先开发板实物图如下: 在本篇文章中,我们将详细介绍Arduino开发板的硬件电路部分,具体来说,就是介绍Arduino Uno开发板的引脚分配图及定义。Arduino Uno微控制器采用的是Atmel 的ATmega328。Arduino Uno开发板的引脚分配图包含14个数字引脚、6个模拟输入、电源插孔、USB连接和ICSP插头。引脚的复用功能提供了更多的不同选项,例如驱动电机、LED、读取传感器等。在这篇文章中,我们将介绍Arduino Uno引脚的功能。 Arduino Uno引脚分配图

Arduino Uno引脚分配- 电源 Arduino Uno开发板可以使用三种方式供电: ●直流电源插孔-可以使用电源插孔为Arduino开发板供电。电源插孔通常连接到一个适配器。开发板的供电范围可以是5-20V,但制造商建议将其保持在7-12V之间。高于12V时,稳压芯片可能会过热,低于7V可能会供电不足。 ●VIN引脚- 该引脚用于使用外部电源为Arduino Uno开发板供电。电压应控制在上述提到的范围内。 ●USB电缆- 连接到计算机时,提供500mA/5V电压。

在电源插孔的正极与VIN引脚之间链接有一个极性保护的二极管,额定电流为1安培。您使用的电源决定了可用于电路的功率。例如,使用USB为电路供电时,电流最大限制在500mA。考虑到该电源也用于为MCU、外围设备、板载稳压器和与其连接的组件供电。当通过电源插座或VIN为电路供电时,可用的最大电流取决于Arduino开发板上的5V和3.3V稳压器。 ●5v和3v3 根据制造商的数据手册,它们提供稳压的5V和3.3v,向外部组件供电。 ●GND 在Arduino Uno引脚分配图中,可以看到有5个GND引脚,它们都是互连的。 GND引脚用于闭合电路回路,并在整个电路中提供一个公共逻辑参考电平。务必确保所有的GND(Arduino、外设和组件)相互连接并且有共同点。 ●RESET - 复位Arduino开发板。

O P07资料

OP07中文资料 op07的功能介绍: 高精度单片运算放大器 OP07是一种高精度单片运算放大器,具有很低的输入失调电压和漂移。OP07的优良特性使它特别适合作前级器,放大微弱信号。使用OP07一般不用考虑调零和频率问题就能满足要求。 主要特点: ◆低输入失调电压:75uV(最大) ◆低失调电压温漂:1.3uV/℃(最大) ◆低失调电压时漂:1.5uV/月(最大) ◆低噪声:0.6uV P-P(最大) ◆宽输入电压范围:±14V ◆宽电源电压范围:3V~18V Op07芯片是一种低噪声,非斩波稳零的双极性运算放大器集成电路。由于OP07具有非常低的输入失调电压OP07A最大为25μV),所以OP07在很多应用场合不需要额外的调零措施。OP07同时具有输入偏置电流低(OP07A为和开环增益高(对于OP07A为300V/mV)的特点,这种低失调、高开环增益的特性使得OP07特别适用于高增益的测量放大传感器的微弱信号等方面。 特点: 超低偏移:150μV最大。 低输入偏置电流: 1.8nA 。 低失调电压漂移:0.5μV/℃ 。 超稳定,时间:2μV/month最大 高电源电压范围:±3V至±22V

图1 OP07外型图片 2 OP07 管脚图 OP07芯片引脚功能说明: 1和8为偏置平衡(调零端),2为反向输入端,3为正向输入端,4接地,5空脚 6为输出,7接电源+

图3 OP0路图 ABSOLUTE MAXIMUM RATINGS 最大额定值 Symbol 符号Parameter参数Value数值 Unit 单位 VCC Supply Voltage 电源电压±22 V Vid Differential Input Voltage差分输入电压±30 V Vi Input Voltage 输入电压±22 V Toper Operating Temperature 工作温度-40 to +105 ℃ Tstg Storage Temperature 贮藏温度-65 to +150 ℃ 电气特性 虚拟通道连接= ± 15V ,Tamb = 25 ℃(除非另有说明) Symbol 符号Parameter 参数及测试条件最小典型最大 Unit 单位 Vio Input Offset Voltage 输入失调电压0℃ ≤ Tamb ≤ +70℃ -60 150 250 μV Long Term Input Offset Voltage Stability-(note 1) 长期输 入偏置电压的稳定性 -0.4 2 μV/Mo

OP07中文资料 op07的功能介绍: 高精度单片运算放大器 OP07是一种高精度单片运算放大器,具有很低的输入失调电压和漂移。OP07的优良特性使它特别适合作前级放大器,放大微弱信号。使用OP07一般不用考虑调零和频率问题就能满足要求。 主要特点: ◆低输入失调电压:75uV(最大) ◆低失调电压温漂:1.3uV/℃(最大) ◆低失调电压时漂:1.5uV/月(最大) ◆低噪声:0.6uV P-P(最大) ◆宽输入电压范围:±14V ◆宽电源电压范围:3V~18V Op07芯片是一种低噪声,非斩波稳零的双极性运算放大器集成电路。由于OP07具有非常低的输入失调电压(对于OP07A最大为25μV),所以OP07在很多应用场合不需要额外的调零措施。OP07同时具有输入偏置电流低(OP07A为±2nA)和开环增益高(对于OP07A为300V/mV)的特点,这种低失调、高开环增益的特性使得OP07特别适用于高增益的测量设备和放大传感器的微弱信号等方面。 特点: 超低偏移:150μV最大。 低输入偏置电流: 1.8nA 。 低失调电压漂移:0.5μV/℃ 。 超稳定,时间:2μV/month最大 高电源电压范围:±3V至±22V

图1 OP07外型图片 图2 OP07 管脚图 OP07芯片引脚功能说明: 1和8为偏置平衡(调零端),2为反向输入端,3为正向输入端,4接地,5空脚 6为输出,7接电源+

图3 OP07内部电路图 ABSOLUTE MAXIMUM RATINGS 最大额定值 Symbol 符号 Parameter参数Value数值VCC Supply Voltage 电源电压±22 Vid Differential Input Voltage差分输入电压±30 Vi Input Voltage 输入电压±22 Toper Operating Temperature 工作温度-40 to +105 Tstg Storage Temperature 贮藏温度-65 to +150 电气特性 虚拟通道连接= ± 15V ,Tamb = 25 ℃(除非另有说明) Symbol 符号 Parameter 参数及测试条件最小典型最 Vio Input Offset Voltage 输入失调电压0℃ ≤ Tamb ≤ +70℃ -60 15 25