广东技术师范学院《数字电子技术》试卷及答案

一、填空题(每空1分,共20分)

1. 有一数码10010011,作为自然二进制数时,它相当于十进制数( 147 ),作为8421BCD 码时,它相当于十进制数( 93 )。

2.三态门电路的输出有高电平、低电平和( 高阻 )3种状态。

3.TTL 与非门多余的输入端应接( 高电平或悬空 )。

4.TTL 集成JK 触发器正常工作时,其d R 和d S 端应接( 高 )电平。 5. 已知某函数??

? ?

?+??? ?

?++=D C AB D C A B F ,该函数的反函数F =

( D C B A D C A B ++ )。

6. 如果对键盘上108个符号进行二进制编码,则至少要(7)位二进制数码。

7. 典型的TTL 与非门电路使用的电路为电源电压为( 5 )V ,其输出高电平为( 3.6 )V ,输出低电平为( 0.35 )V , CMOS 电路的电源电压为( 3—18 ) V 。

8.74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A 2A 1A 0=110时,输出 01234567Y Y Y Y Y Y Y Y 应为( 10111111 )。

9.将一个包含有32768个基本存储单元的存储电路设计16位为一个字节的ROM 。该ROM 有( 11 )根地址线,有( 16 )根数据读出线。

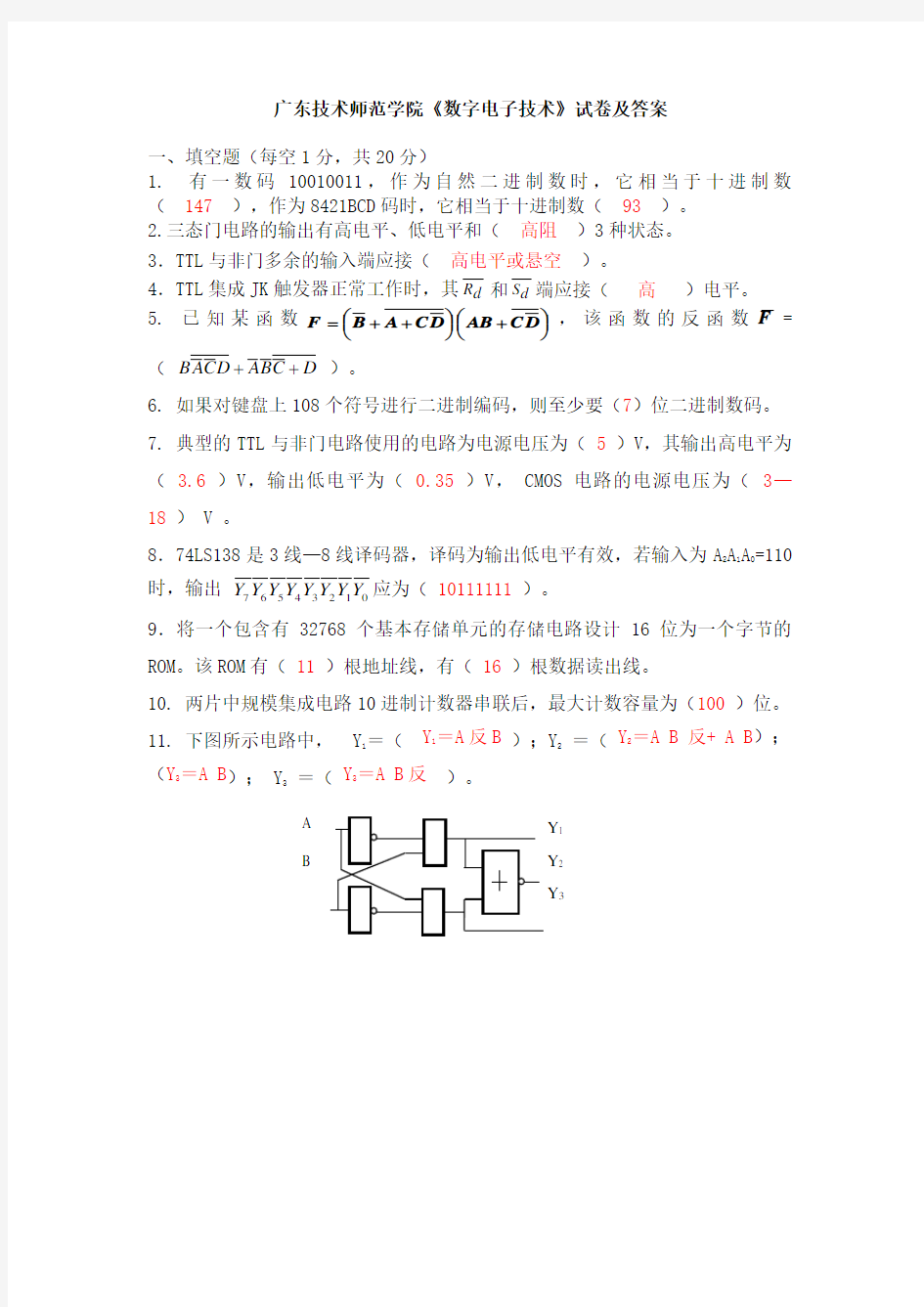

10. 两片中规模集成电路10进制计数器串联后,最大计数容量为(100 )位。 11. 下图所示电路中, Y 1=( Y 1=A 反B );Y 2 =( Y 2=A B 反+ A B ); (Y 3=A B ); Y

Y 3=A B 反

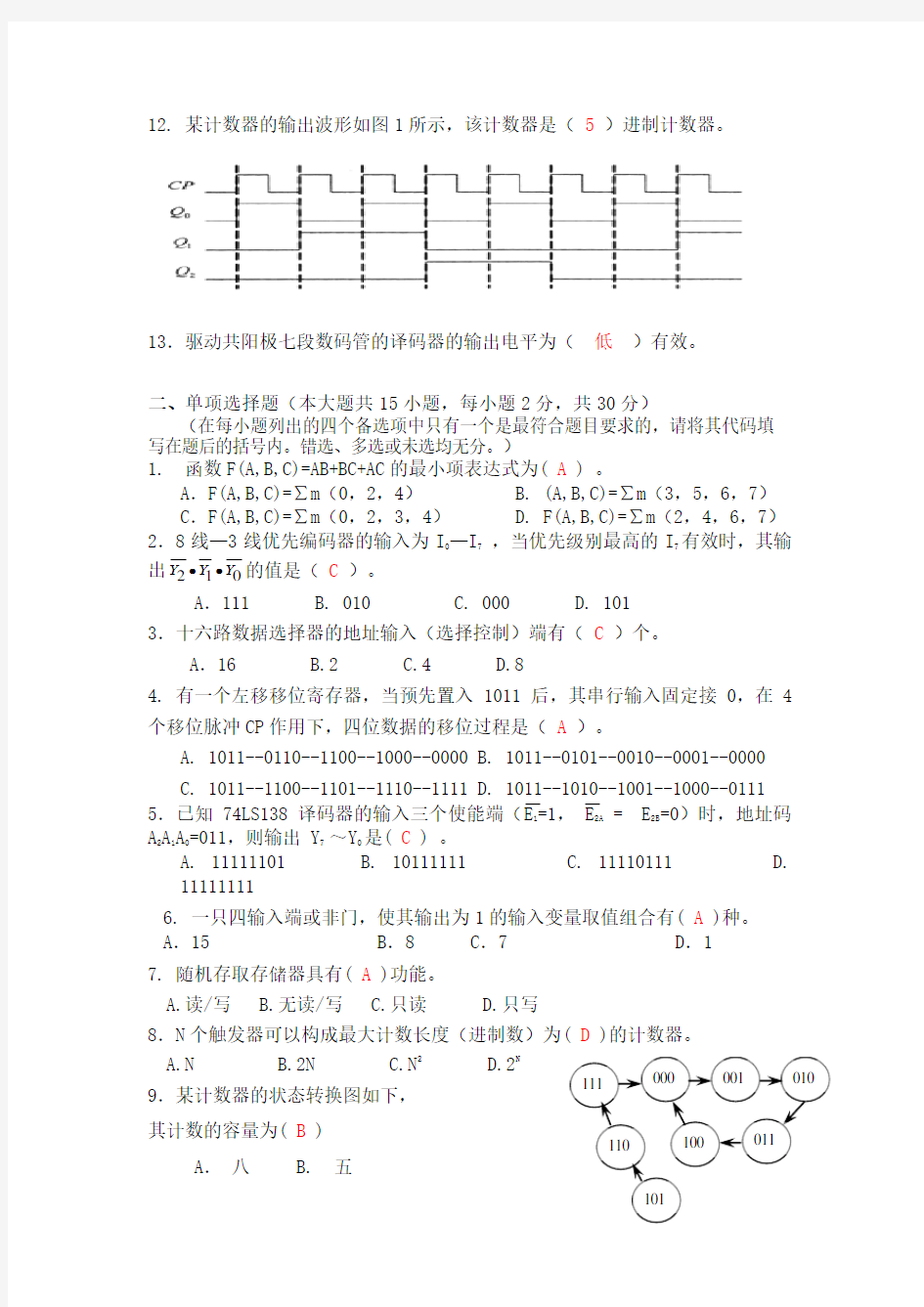

12. 某计数器的输出波形如图1所示,该计数器是( 5 )进制计数器。

13.驱动共阳极七段数码管的译码器的输出电平为( 低 )有效。

二、单项选择题(本大题共15小题,每小题2分,共30分)

(在每小题列出的四个备选项中只有一个是最符合题目要求的,请将其代码填写在题后的括号内。错选、多选或未选均无分。)

1. 函数F(A,B,C)=AB+BC+AC 的最小项表达式为( A ) 。

A .F(A,B,C)=∑m (0,2,4) B. (A,B,C)=∑m (3,5,6,7) C .F(A,B,C)=∑m (0,2,3,4) D. F(A,B,C)=∑m (2,4,6,7) 2.8线—3线优先编码器的输入为I 0—I 7 ,当优先级别最高的I 7有效时,其输出012Y Y Y ??的值是( C )。

A .111 B. 010 C. 000 D. 101 3.十六路数据选择器的地址输入(选择控制)端有( C )个。

A .16 B.2 C.4 D.8

4. 有一个左移移位寄存器,当预先置入1011后,其串行输入固定接0,在4个移位脉冲CP 作用下,四位数据的移位过程是( A )。

A. 1011--0110--1100--1000--0000

B. 1011--0101--0010--0001--0000

C. 1011--1100--1101--1110--1111

D. 1011--1010--1001--1000--0111 5.已知74LS138译码器的输入三个使能端(E 1=1, E 2A = E 2B =0)时,地址码A 2A 1A 0=011,则输出 Y 7 ~Y 0是( C ) 。

A. 11111101

B. 10111111

C. 11110111

D. 11111111

6. 一只四输入端或非门,使其输出为1的输入变量取值组合有( A )种。 A .15 B .8 C .7 D .1

7. 随机存取存储器具有( A )功能。

A.读/写

B.无读/写

C.只读

D.只写

8.N 个触发器可以构成最大计数长度(进制数)为( D )的计数器。 A.N B.2N C.N 2 D.2N 9.某计数器的状态转换图如下, 其计数的容量为( B )

A . 八 B. 五

C. 四

D. 三

10.已知某触发的特性表如下(A、B为触发器的输入)其输出信号的逻辑表达式为( C )。

A. C. n

n Q

+ D. Q n+1= B

n

1

=

Q+

B

Q

A

11.有一个4位的D/A转换器,设它的满刻度输出电压为10V,当输入

数字量为1101时,输出电压为(A)。

A. 8.125V B.4V C. 6.25V D.9.375V

12.函数F=AB+BC,使F=1的输入ABC组合为( D )

A.ABC=000 B.ABC=010

C.ABC=101 D.ABC=110

13.已知某电路的真值表如下,该电路的逻辑表达式为( C )。

A.C

Y= B. AB C

Y+

= D.C

AB

Y= C.C

=

Y+

C

B

14.四个触发器组成的环行计数器最多有( D )个有效状态。

A.4

B. 6

C. 8

D. 16

三、判断说明题(本大题共2小题,每小题5分,共10分)

(判断下列各题正误,正确的在题后括号内打“√”,错误的打“×”。)

1、逻辑变量的取值,1比0大。(×)

2、D/A转换器的位数越多,能够分辨的最小输出电压变化量就越小(√)。3.八路数据分配器的地址输入(选择控制)端有8个。(×)

4、因为逻辑表达式A+B+AB=A+B成立,所以AB=0成立。(×)

5、利用反馈归零法获得N进制计数器时,若为异步置零方式,则状态S N只是短暂的过渡状态,不能稳定而是立刻变为0状态。(√)

6.在时间和幅度上都断续变化的信号是数字信号,语音信号不是数字信号。(√)

7.约束项就是逻辑函数中不允许出现的变量取值组合,用卡诺图化简时,可将约束项当作1,也可当作 0。(√)

8.时序电路不含有记忆功能的器件。(×)

9.计数器除了能对输入脉冲进行计数,还能作为分频器用。(√)

10.优先编码器只对同时输入的信号中的优先级别最高的一个信号编码.(√)

四、综合题(共30分)

1.对下列Z 函数要求:(1)列出真值表;(2)用卡诺图化简;(3)画出化简后的逻辑图。(8分)

Z=C B A C B A B A ??+??+

BC=0

(1)真值表 (2分) (2)卡诺图化简(2分)

(3) 表达式(2分)

逻辑图(2分)

Z=C B A B A ++=A ⊕B+C BC=0

2.试用3线—8线译码器74LS138和门电路实现下列函数。(8分)

Z (A 、B 、C )=AB+A C

“1Z

解:Z (A 、B 、C )=AB +

A C =A

B (

C +C )+A C (B +B )

=ABC +AB C +A BC +A B C = m 1+ m 3+ m 6+ m 7

=7 6 3 1 m m m m ???

3.74LS161是同步4位二进制加法计数器,其逻辑功能表如下,试分析下列电路是几进制计数器,并画出其状态图。(8分)

74LS161逻辑功能表

CP

“1”

4.触发器电路如下图所示,试根据CP及输入波形画出输出端Q

1、Q

2

的波

形。设各触发器的初始状态均为“0”(6分)。

一、填空题:(每空3分,共15分)

1.逻辑函数有四种表示方法,它们分别是(真值表)、(逻辑图)、(逻辑表达式)和(卡诺图)。

2.将2004个“1”异或起来得到的结果是(0 )。

3.由555定时器构成的三种电路中,(施密特触发器)和(单稳态触发器)是脉冲的整形电路。

4.TTL器件输入脚悬空相当于输入(高)电平。

5.基本逻辑运算有: (与)、(或)和(非)运算。

6.采用四位比较器对两个四位数比较时,先比较(最高)位。

7.触发器按动作特点可分为基本型、(同步型)、(主从型)和边沿型;8.如果要把一宽脉冲变换为窄脉冲应采用(积分型单稳态)触发器。9.目前我们所学的双极型集成电路和单极型集成电路的典型电路分别是(TTL )电路和( CMOS )电路。

10.施密特触发器有(两)个稳定状态.,多谐振荡器有(0 )个稳定状态。

11.数字系统按组成方式可分为功能扩展电路、功能综合电路两种;

12.两二进制数相加时,不考虑低位的进位信号是(半)加器。

13.不仅考虑两个本位(低位)相加,而且还考虑来自 低位进位 相加的运算电路,称为全加器。

14.时序逻辑电路的输出不仅和_该时刻输入变量的取值_有关,而且还与_该时刻电路所处的状态_有关。

15.计数器按CP 脉冲的输入方式可分为_同步计数器_和_异步计数器_。 16.触发器根据逻辑功能的不同,可分为_RS 触发器 、_T 触发器_、_JK 触发器_、_T ˊ触发器_、_D 触发器_等。

17.根据不同需要,在集成计数器芯片的基础上,通过采用_反馈归零法 、_预置数法_、_进位输出置最小数法_等方法可以实现任意进制的技术器。 18.4. 一个 JK 触发器有 两 个稳态,它可存储 一 位二进制数。

19.若将一个正弦波电压信号转换成同一频率的矩形波,应采用 多谐振荡器 电路 。

20. 把JK 触发器改成T 触发器的方法是 J=K=T 。

21.N 个触发器组成的计数器最多可以组成 2n 进制的计数器。 22.基本RS 触发器的约束条件是 RS=0 。

23.对于JK 触发器,若K J =,则可完成 T 触发器的逻辑功能;若K J =,则可完成 D 触发器的逻辑功能。

二.数制转换(5分):

1、(11.001)2=(3.2)16=(3.125)10

2、(8F.FF )16=(10001111.11111111)2=(143.996093)10

3、(25.7)10=(11001.1011)2=(19.B )16

4、(+1011B )原码=(01011)反码=(01011)补码

5、(-101010B )原码=(1010101)反码=(1010101)补码 1、 化简等式

Y ABC ABC ABC =++ C B AC B A Y ++=

D C A C B A B A D C Y ++⊕=)(,给定约束条件为:AB+CD=0

2 用卡诺图化简函数为最简单的与或式(画图)。

(0,2,8,10)

Y m =∑ 化简得 Y AC AD =+

1.试画出下列触发器的输出波形 (设触发器的初态为0)。 (12分)

1.

2.

3.

2.已知输入信号X,Y,Z的波形如图3所示,试画出

+

F?

XYZ

+

+

?

=的波形。

X

Y

Z

X

X

YZ

Y

Z

图3 波形图

1、分析如图所示组合逻辑电路的功能。

2.试分析如图3所示的组合逻辑电路。 (15分)

1). 写出输出逻辑表达式; 2). 化为最简与或式; 3). 列出真值表; 4). 说明逻辑功能。

3. 七、分析如下时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图。(20分)

图4

C

4.74161组成的电路如题37图所示,分析电路,并回答以下问题

(1)画出电路的状态转换图(Q

3Q

2

Q

1

Q

);

(2)说出电路的功能。(74161的功能见表)

题37图

六.设计题:(30分)

1.要求用与非门设计一个三人表决用的组合逻辑电路图,只要有2票或3票同意,表决就通过(要求有真值表等)。

2. 试用JK触发器和门电路设计一个十三进制的计数器, 并检查设计的电路能否自启动。(14分)

七.(10分)试说明如图 5所示的用555 定时器构成的电路功能,求出U T+ 、U T- 和ΔU T ,并画出其输出波形。(10分)

图5

数字电路笔试汇总 2、什么是同步逻辑和异步逻辑?(汉王笔试) 同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。 電路設計可分類為同步電路和非同步電路設計。同步電路利用時鐘脈衝使其子系統同步運作,而非同 步電路不使用時鐘脈衝做同步,其子系統是使用特殊的“開始”和“完成”信號使之同步。由於非同步電 路具有下列優點--無時鐘歪斜問題、低電源消耗、平均效能而非最差效能、模組性、可組合和可複用性-- 因此近年來對非同步電路研究增加快速,論文發表數以倍增,而Intel Pentium 4處理器設計,也開始採用 非同步電路設計。 异步电路主要是组合逻辑电路,用于产生地址译码器、FIFO或RAM的读写控制信号脉冲,其逻 辑输出与任何时钟信号都没有关系,译码输出产生的毛刺通常是可以监控的。同步电路是由时序电路(寄存 器和各种触发器)和组合逻辑电路构成的电路,其所有操作都是在严格的时钟控制下完成的。这些时序电路 共享同一个时钟CLK,而所有的状态变化都是在时钟的上升沿(或下降沿)完成的。 3、什么是"线与"逻辑,要实现它,在硬件特性上有什么具体要求?(汉王笔试) 线与逻辑是两个输出信号相连可以实现与的功能。在硬件上,要用oc门来实现(漏极或者集电极开路),由于不用oc门可能使灌电流过大,而烧坏逻辑门,同时在输出端口应加一个上拉电阻。(线或则是下拉电阻) 4、什么是Setup 和Holdup时间?(汉王笔试) 解释setup和hold time violation,画图说明,并说明解决办法。(威盛VIA 2003.11.06 上海笔试试题) Setup/hold time 是测试芯片对输入信号和时钟信号之间的时间要求。建立时间是指触发器的时钟信 号上升沿到来以前,数据稳定不变的时间。输入信号应提前时钟上升沿(如上升沿有效)T时间到达芯片,这个T就是建立时间-Setup time.如不满足setup time,这个数据就不能被这一时钟打入触发器,只有在下 一个时钟上升沿,数据才能被打入触发器。保持时间是指触发器的时钟信号上升沿到来以后,数据稳定不 变的时间。如果hold time不够,数据同样不能被打入触发器。 建立时间(Setup Time)和保持时间(Hold time)。建立时间是指在时钟边沿前,数据信号需要保持不 变的时间。保持时间是指时钟跳变边沿后数据信号需要保持不变的时间。如果不满足建立和保持时间的话,那么DFF将不能正确地采样到数据,将会出现

数字电子技术基础期末考试试卷 1.时序逻辑电路一般由和两分组成。 2.十进制数(56)10转换为二进制数为和十六进制数为。 3.串行进位加法器的缺点是,想速度高时应采用加法器。 4.多谐振荡器是一种波形电路,它没有稳态,只有两个。 5.用6个D 触发器设计一个计数器,则该计数器的最大模值M=。 123(1(24.T ,图1 5 时,6.D 触发器 的Q 和Q1的表达式,并画出其波形。 图 D=Q n+1=Q 1= 7.已知电路如图4所示,试写出: ①驱动方程; ②状态方程; ③输出方程; ④状态表;

⑤电路功能。图4 1.设计一个三变量偶检验逻辑电路。当三变量A 、B 、C 输入组合中的“1”的个数为偶数时F=1,否则F=0。选用8选1数选器或门电路实现该逻辑电路。 要求: (1)列出该电路F(A,B,C)的真值表和表达式; (2ABCF 2求: (1(21.3.4.产生5.32 10分,共 70分) 1.解: 2.证明:左边 3.解: (1)化简该 函数为最简与或式: 解: F 3()43A B C D E A B C D E AB AC A D E =++++--------------=?+++--------------=++-------------分 分 分 ()()33()(1)22BC D B C AD B BC D BAD CAD BC BC BC D BA CA =++++--------------=++++--------------=++++-----------------------分 分分分

填对卡诺图圈对卡诺图-----------2分 由卡诺图可得: F A B A C D A C D B C B D =++++------------------------------2分 (2)画出用两级与非门实现的最简与或式电路图: 则可得电路图如下:------------------------------------------------2分 4.T 1=0.7T=0.7f= T 1=q= 1T T 5.6. 方程: n n n Q Q K Q 0 0000=+ 1111110(n n n n Q J Q K Q Q X +=+=⊕(2分) ③输出方程:n n Q Q Y 01=-----------------------------------------(1分) ④状态表:--------------------------------------------------------------------(3分) ⑤从状态表可得:为受X 控制的可逆4进制值计数器。-----------------------------(2分) 1.解:(1)依题意得真值表如下:--------------------------3分 0102J J Q ⊕(分)

数字电子技术基础第二次实验报告 一、题目代码以及波形分析 1. 设计一款可综合的2选1多路选择器 ①编写模块源码 module multiplexer(x1,x2,s,f); input x1,x2,s; output f; assign f=(~s&x1)|(s&x2); endmodule ②测试模块 `timescale 1ns/1ps module tb_multiplexer; reg x1_test; reg x2_test; reg s_test; wire f_test; initial s_test=0;

always #80 s_test=~s_test; initial begin x1_test=0; x2_test=0; #20 x1_test=1; x2_test=0; #20 x1_test=0; x2_test=1; #20 x1_test=1; x2_test=1; #20 x1_test=0; x2_test=0;

#20 x1_test=1; x2_test=0; #20 x1_test=0; x2_test=1; #20 x1_test=1; x2_test=1; end multiplexer UUT_multiplexer(.x1(x1_test),.x2(x2_test),.s(s_test),.f(f_test)); endmodule ③仿真后的波形截图

④对波形的分析 本例目的是令s为控制信号,实现二选一多路选择器。分析波形图可以知道,s为0时,f 输出x1信号;s为1时,f输出x2信号。所以实现了目标功能。 2. 设计一款可综合的2-4译码器 ①编写模块源码 module dec2to4(W,En,Y); input [1:0]W; input En; output reg [0:3]Y; always@(W,En) case({En,W}) 3'b100:Y=4'b1000; 3'b101:Y=4'b0100; 3'b110:Y=4'b0010;

湖南工学院教案用纸 实验1基本门电路逻辑功能测试(验证性实验) 一、实验目的 1?熟悉基本门电路图形符号与功能; 2?掌握门电路的使用与功能测试方法; 3?熟悉实验室数字电路实验设备的结构、功能与使用。 二、实验设备与器材 双列直插集成电路插座,逻辑电平开关,LED发光显示器,74LS00, 74LS20 , 74LS86,导 线 三、实验电路与说明 门电路是最简单、最基本的数字集成电路,也是构成任何复杂组合电路和时序电路的基本单 元。常见基本集门电路包括与门、或门、与非门、非门、异或门、同或门等,它们相应的图形符号与逻辑功能参见教材P.176, Fig.6.1。根据器件工艺,基本门电路有TTL门电路和CMOS门电路之分。TTL门电路工作速度快,不易损坏,CMOS门电路输出幅度大,集成 度高,抗干扰能力强。 1.74LS00 —四2输入与非门功能与引脚: 2. 74LS20 —双4输入与非门功能与引脚: 3. 74LS86 —四2输入异或门功能与引脚: 四、实验内容与步骤 1.74LS00功能测试: ①74LS00插入IC插座;②输入接逻辑电平开关;③输出接LED显示器;④接电源;⑤拔

动开关进行测试,结果记入自拟表格。 湖南工学院教案用纸

2. 74LS20功能测试: 实验过程与74LS00功能测试类似。 3. 74LS86功能测试: 实验过程与74LS00功能测试类似。 4. 用74LS00构成半加器并测试其功能: ①根据半加器功能:S A B , C AB,用74LS00设计一个半加器电路; ②根据所设计电路进行实验接线; ③电路输入接逻辑电平开关,输出接LED显示器; ④通电源测试半加器功能,结果记入自拟表格。 5. 用74LS86和74LS00构成半加器并测试其功能: 实验过程与以上半加器功能测试类似。 五、实验报告要求 1. 内容必须包括实验名称、目的要求、实验电路及设计步骤、实验结果记录与分析、实验总结与体会等。2?在报告中回答以下思考题: ①如何判断逻辑门电路功能是否正常? ②如何处理与非门的多余输入端? 实验2组合逻辑电路的设计与调试(设计性综合实验) 一、实验目的 1?熟悉编码器、译码器、数据选择器等MSI的功能与使用; 2?进一步掌握组合电路的设计与测试方法; 3?学会用MSI实现简单逻辑函数。 二、实验设备与器材

数字电子技术基础试卷试题答案汇总 一、 填空题(每空1分,共20分) 1、逻辑代数中3种基本运算是(与运算、或运算、非运算) 2、逻辑代数中三个基本运算规则 (代入规则、反演规则、对偶规则) 3、逻辑函数的化简有 公式法 , 卡诺图 两种方法。 4、A+B+C= A ’B ’C ’ 。 5、TTL 与非门的u I ≤U OFF 时,与非门 关闭 ,输出 高电平 ,u I ≥U ON 时,与非门 导通 ,输出 低电平 。 6、组合逻辑电路没有 记忆 功能。 7、竞争冒险的判断方法 代数方法 , 卡诺图法 。 8、触发器它2 稳态,主从RS 触发器的特性方程Q ’’=S+RQ ’ SR=0 , 主从JK 触发器的特性方Q ’’=JQ ’+K ’Q ,D 触发器的特性方程 Q ’’=D 。 二、 选择题(每题1分,共10分) 1、相同为“0”不同为“1”它的逻辑关系是 ( C ) A 、或逻辑 B 、与逻辑 C 、异或逻辑 2、Y (A ,B ,C ,)=∑m (0,1,2,3)逻辑函数的化简式 ( C ) A 、Y=AB+BC+ABC B 、Y=A+B C 、Y=A (A) 3、 A 、Y=A B B 、Y 处于悬浮状态 C 、Y=B A + 4、下列图中的逻辑关系正确的是 ( A ) A.Y=B A + B.Y=B A + C.Y=AB 5、下列说确的是 ( A ) A 、主从JK 触发器没有空翻现象 B 、JK 之间有约束 C 、主从JK 触发器的特性方程是CP 上升沿有效。 6、下列说确的是 ( C ) A 、同步触发器没有空翻现象 B 、同步触发器能用于组成计数器、移位寄存器。 C 、同步触发器不能用于组成计数器、移位寄存器。 7、下列说法是正确的是 ( A ) A 、异步计数器的计数脉冲只加到部分触发器上 B 、异步计数器的计数脉冲同时加到所有触发器上 C 、异步计数器不需要计数脉冲的控制

专业: 班级: 学号: 姓名: 指导教师: 电气学院

实验一集成门电路逻辑功能测试 一、实验目的 1. 验证常用集成门电路的逻辑功能; 2. 熟悉各种门电路的逻辑符号; 3. 熟悉TTL集成电路的特点,使用规则和使用方法。 二、实验设备及器件 1. 数字电路实验箱 2. 万用表 3. 74LS00四2输入与非门1片74LS86四2输入异或门1片 74LS11三3输入与门1片74LS32四2输入或门1片 74LS04反相器1片 三、实验原理 集成逻辑门电路是最简单,最基本的数字集成元件,目前已有种类齐全集成门电路。TTL集成电路由于工作速度高,输出幅度大,种类多,不宜损坏等特点而得到广泛使用,特别对学生进行实验论证,选用TTL电路较合适,因此这里使用了74LS系列的TTL成路,它的电源电压为5V+10%,逻辑高电平“1”时>2.4V,低电平“0”时<0.4V。实验使用的集成电路都采用的是双列直插式封装形式,其管脚的识别方法为:将集成块的正面(印有集成电路型号标记面)对着使用者,集成电路上的标识凹口左,左下角第一脚为1脚,按逆时针方向顺序排布其管脚。 四、实验内容 ㈠根据接线图连接,测试各门电路逻辑功能 1. 利用Multisim画出以74LS11为测试器件的与门逻辑功能仿真图如下

按表1—1要求用开关改变输入端A,B,C的状态,借助指示灯观测各相应输出端F的状态,当电平指示灯亮时记为1,灭时记为0,把测试结果填入表1—1中。 表1-1 74LS11逻辑功能表 输入状态输出状态 A B C Y 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 悬空 1 1 1 悬空0 0 0 2. 利用Multisim画出以74LS32为测试器件的或门逻辑功能仿真图如下

《数字电子技术基础实验》 实验报告 学院: 学号: 姓名: 专业: 实验时间: 实验地点: 2016年12月

Figure 5.51n位移位寄存器 一、实验目的及要求 编写testbench 验证Figure 5.51源代码功能,实现n位移位寄存器。 了解并熟悉移位寄存器的工作原理功能; 熟悉n位移位寄存器的逻辑功能。 所需功能:实现所需功能需要R,Clock,L,w,Q,5个变量,其中参数n 设为缺省值16,以定义触发器的个数。 当时钟信号Clock从0变为1时刻,正边沿触发器做出响应: 当L=0时,对输出结果Q进行向右移位,将w的值赋给Q的 最高位,实现移位; 当L=1时,将输入R的值寄存在Q中; 所需EDA工具及要求: Modelsim: 1、在Modelsim中建立工程,编写Figure 5.51模块的源码; 2、编写Figure 5.51的测试模块源码,对Figure 5.51进行仿真、测 试,观察仿真波形图并进行分析等; Synplify Pro: 1、使用Synplify Pro对Figure 5.51进行综合,得到RTL View、 Technology View、综合报表等,进行观察、分析等; 二、实验内容与步骤 1、在Modelsim中建立工程,编写Figure 5.51模块的源码; 本题实现的是一个n位移位寄存器,触发器对时钟信号Clock敏感,为正边沿敏感型。L实现对Q的控制,若L=1,则将R寄存到Q中;若L=0,则对Q向右移位。 如下图是一个4位移位寄存器 图表说明了该四位移位寄存器的移位过程

module shiftn (R, L, w, Clock, Q); parameter n = 16; input [n-1:0] R; input L, w, Clock; output reg [n-1:0] Q; integer k; always @(posedge Clock) if (L) Q <= R; else begin for (k = 0; k < n-1; k = k+1) Q[k] <= Q[k+1]; Q[n-1] <= w; end endmodule 这是可用于表示任意位宽的移位寄存器的代码,其中参数n设为缺省值16,以定义触发器的个数。R和Q的位宽用n定义,描述移位操作的else 分支语句用for循环语句实现,可适用于由任意多个触发器组成的移位操作。 2、编写Figure 5.51的测试模块源码,对Figure 5.51进行仿真、测试,观察仿真波形图并进行分析等; `timescale 1ns/1ns module shiftn_tb;

数字电子技术实验 简要讲义 适用专业:电气专业 编写人:于云华、何进 中国石油大学胜利学院机械与控制工程学院 2015.3

目录 实验一:基本仪器熟悉使用和基本逻辑门电路功能测试 (3) 实验二:小规模组合逻辑电路设计 (4) 实验三:中规模组合逻辑电路设计 (5) 实验四:触发器的功能测试及其应用 (7) 实验五:计数器的功能测试及其应用 (8) 实验六:计数、译码与显示综合电路的设计 (9)

实验一:基本仪器熟悉使用和常用门电路逻辑功能测试 (建议实验学时:2学时) 一、实验目的: 1、熟悉实验仪器与设备,学会识别常用数字集成芯片的引脚分配; 2、掌握门电路的逻辑功能测试方法; 3、掌握简单组合逻辑电路的设计。 二、实验内容: 1、测试常用数字集成逻辑芯片的逻辑功能:74LS00,74LS02,74LS04,74LS08,74LS20,74LS32,74LS86等(预习时查出每个芯片的逻辑功能、内部结构以及管脚分配)。 2、采用两输入端与非门74LS00实现以下逻辑功能: ① F=ABC ② F=ABC③ F=A+B ④ F=A B+A B 三、实验步骤:(学生根据自己实验情况简要总结步骤和内容)主要包括: 1、实验电路设计原理图;如:实现F=A+B的电路原理图: 2、实验真值表; 3、实验测试结果记录。如: 输入输出 A B F3 00灭

四、实验总结: (学生根据自己实验情况,简要总结实验中遇到的问题及其解决办法)注:本实验室提供的数字集成芯片有: 74LS00, 74LS02,74LS04,74LS08,74LS20,74LS32,74LS74,74LS90,74LS112, 74LS138,74LS153, 74LS161 实验二:小规模组合逻辑电路设计 (建议实验学时:3学时) 一、实验目的: 1、学习使用基本门电路设计、实现小规模组合逻辑电路。 2、学会测试、调试小规模组合逻辑电路的输入、输出逻辑关系。 二、实验内容: 1、用最少的门电路设计三输入变量的奇偶校验电路:当三个输入端有奇数个1时,输出为高,否则为低。(预习时画出电路原理图,注明所用芯片型号) 2、用最少的门电路实现1位二进制全加器电路。(预习时画出电路原理图,注明所用芯片型号) 3、用门电路实现“判断输入者与受血者的血型符合规定的电路”,测试其功能。要求如下:人类由四种基本血型:A、B、AB、O 型。输血者与受血者的血型必须符合下述原则: O型血可以输给任意血型的人,但O型血的人只能接受O型血; AB型血只能输给AB型血的人,但AB血型的人能够接受所有血型的血; A 型血能给A型与AB型血的人;但A型血的人能够接受A型与O型血; B型血能给B型与AB型血的人,而B型血的人能够接受B型与O型血。 试设计一个检验输血者与受血者血型是否符合上述规定的逻辑电路,如果符合规定电路,输出高电平(提示:电路只需要四个输入端,它们组成一组二进制数码,每组数码代表一对输血与受血的血型对)。 约定“00”代表“O”型 “01”代表“A”型 “10”代表“B”型 “11”代表“AB”型(预习时画出电路原理图,注明所用芯片型号) 三、实验步骤:(学生根据自己实验情况简要总结步骤和内容),与实验一说明类似。

数字电子技术基础—试题—解答

三、逻辑函数化简(每题5分,共10分) 1、用代数法化简为最简与或式 Y= A + 1、Y=A+B 2、用卡诺图法化简为最简或与式 Y= + C +A D, 约束条件:A C + A CD+AB=0 2、用卡诺图圈0的方法可得:Y=(+D)(A+ )(+ ) 四、分析下列电路。(每题6分,共12分) 1、写出如图4所示电路的真值表及最简逻辑表达式。 图 4 1、该电路为三变量判一致电路,当三个变量都相同时输出为1,否则输出为0。 2、写出如图5所示电路的最简逻辑表达式。 2、 B =1,Y = A , B =0 Y 呈高阻态。

五、判断如图 6所示电路的逻辑功能。若已知 u B =-20V,设二极管为理想二极管,试根据 u A 输入波形,画出 u 0 的输出波形(8分) t 图 6 五、 u 0 = u A · u B ,输出波形 u 0 如图 10所示: 图 10 六、用如图 7所示的8选1数据选择器CT74LS151实现下列函数。(8分) Y(A,B,C,D)=Σm(1,5,6,7,9,11,12,13,14) 图 7 答: 七、用 4位二进制计数集成芯片CT74LS161采用两种方法实现模值为10的计数器,要求画出接线图和全状态转换图。(CT74LS161如图8所示,其LD端为同步置数端,CR为异步复位端)。(10分) 图 8 七、接线如图 12所示:

三、将下列函数化简为最简与或表达式(本题 10分) 1. (代数法) 2、F 2 ( A,B,C,D)=∑m (0,1,2,4,5,9)+∑d (7,8,10,11,12,13)(卡诺图法) 三、 1. 2. 四、分析如图 16所示电路,写出其真值表和最简表达式。(10分) 四、 1. 2. , , , 五、试设计一个码检验电路,当输入的四位二进制数 A、B、C、D为8421BCD码时,输出Y为1,否则Y为0。(要求写出设计步骤并画电路图)(10分) 五、 六、分析如图17所示电路的功能,写出驱动方程、状态方程,写出状态表或状态转换图,说明电路的类型,并判别是同步还是异步电路?(10分) 六、同步六进制计数器,状态转换图见图 20。 图 20

. 数字电子技术基础期末考试试卷 一、填空题 1. 时序逻辑电路一般由 和 两分组成。 2. 十进制数(56)10转换为二进制数为 和十六进制数为 。 3. 串行进位加法器的缺点是 ,想速度高时应采用 加法器。 4. 多谐振荡器是一种波形 电路,它没有稳态,只有两个 。 5. 用6个D 触发器设计一个计数器,则该计数器的最大模值M= 。 二、化简、证明、分析综合题: 1.写出函数F (A,B,C,D) =A B C D E ++++的反函数。 2.证明逻辑函数式相等:()()BC D D B C AD B B D ++++=+ 3.已知逻辑函数F= ∑(3,5,8,9,10,12)+∑d(0,1,2) (1)化简该函数为最简与或式: (2)画出用两级与非门实现的最简与或式电路图: 4.555定时器构成的多谐振动器图1所示,已知R 1=1K Ω,R 2=8.2K Ω,C=0.1μF 。试求脉冲宽度 T ,振荡频率f 和占空比q 。 ………………………密……………………封…………………………装…………………订………………………线……………………… 系别 专业(班级) 姓名 学号

图1 5.某地址译码电路如图2所示,当输入地址变量A7-A0的状态分别为什么状态 时,1Y 、6Y 分别才为低电平(被译中)。 图2 6.触发器电路就输入信号的波形如图3所示,试分别写出D 触发器的Q 和Q1的表达式,并画出其波形。 图3 ………………封…………………………装…………………订………………………线………………………

D= Q n+1= Q1= 7. 已知电路如图4所示,试写出: ①驱动方程; ②状态方程; ③输出方程; ④状态表; ⑤电路功能。图4 三、设计题:(每10分,共20分) 1.设计一个三变量偶检验逻辑电路。当三变量A、B、C输入组合中的“1”的个数为偶数时F=1,否则F=0。选用8选1数选器或门电路实现该逻辑电路。要求: (1)列出该电路F(A,B,C)的真值表和表达式; (2)画出逻辑电路图。 2.试用74161、3-8译码器和少量门电路,实现图5所示波形VO1、VO2,其中CP为输入波形。要求: (1)列出计数器状态与V01、V02的真值表;

数字电子技术实验指导书 (韶关学院自动化专业用) 自动化系 2014年1月10日 实验室:信工405

数字电子技术实验必读本实验指导书是根据本科教学大纲安排的,共计14学时。第一个实验为基础性实验,第二和第七个实验为设计性实验,其余为综合性实验。本实验采取一人一组,实验以班级为单位统一安排。 1.学生在每次实验前应认真预习,用自己的语言简要的写明实验目的、实验原理,编写预习报告,了解实验内容、仪器性能、使用方法以及注意事项等,同时画好必要的记录表格,以备实验时作原始记录。教师要检查学生的预习情况,未预习者不得进行实验。 2.学生上实验课不得迟到,对迟到者,教师可酌情停止其实验。 3.非本次实验用的仪器设备,未经老师许可不得任意动用。 4.实验时应听从教师指导。实验线路应简洁合理,线路接好后应反复检查,确认无误时才接通电源。 5.数据记录 记录实验的原始数据,实验期间当场提交。拒绝抄袭。 6.实验结束时,不要立即拆线,应先对实验记录进行仔细查阅,看看有无遗漏和错误,再提请指导教师查阅同意,然后才能拆线。 7.实验结束后,须将导线、仪器设备等整理好,恢复原位,并将原始数据填入正式表格中,经指导教师签名后,才能离开实验室。

目录实验1 TTL基本逻辑门功能测试 实验2 组合逻辑电路的设计 实验3 译码器及其应用 实验4 数码管显示电路及应用 实验5 数据选择器及其应用 实验6 同步时序逻辑电路分析 实验7 计数器及其应用

实验1 TTL基本逻辑门功能测试 一、实验目的 1、熟悉数字电路试验箱各部分电路的基本功能和使用方法 2、熟悉TTL集成逻辑门电路实验芯片的外形和引脚排列 3、掌握实验芯片门电路的逻辑功能 二、实验设备及材料 数字逻辑电路实验箱,集成芯片74LS00(四2输入与非门)、74LS04(六反相器)、74LS08(四2输入与门)、74LS10(三3输入与非门)、74LS20(二4输入与非门)和导线若干。 三、实验原理 1、数字电路基本逻辑单元的工作原理 数字电路工作过程是数字信号,而数字信号是一种在时间和数量上不连续的信号。 (1)反映事物逻辑关系的变量称为逻辑变量,通常用“0”和“1”两个基本符号表示两个对立的离散状态,反映电路上的高电平和低电平,称为二值信息。(2)数字电路中的二极管有导通和截止两种对立工作状态。三极管有饱和、截止两种对立的工作状态。它们都工作在开、关状态,分别用“1”和“0”来表示导通和断开的情况。 (3)在数字电路中,以逻辑代数作为数学工具,采用逻辑分析和设计的方法来研究电路输入状态和输出状态之间的逻辑关系,而不必关心具体的大小。 2、TTL集成与非门电路的逻辑功能的测试 TTL集成与非门是数字电路中广泛使用的一种逻辑门。实验采用二4输入与非门74LS20芯片,其内部有2个互相独立的与非门,每个与非门有4个输入端和1个输出端。74LS20芯片引脚排列和逻辑符号如图2-1所示。

数字电子技术试卷(1) 一.填空(16) 1.十进制数123的二进制数是 1111011 ;十六进制数是 7B 。 2.100001100001是8421BCD 码,其十进制为 861 。 3.逻辑代数的三种基本运算是 与 , 或 和 非 。 4.三态门的工作状态是 0 , 1 , 高阻 。 5.描述触发器逻辑功能的方法有 真值表,逻辑图,逻辑表达式,卡诺图,波形图 。 6.施密特触发器的主要应用是 波形的整形 。 7.设4位D/A 转换器的满度输出电压位30伏,则输入数字量为1010时的输出模拟电压为 。 8.实现A/D 转换的主要方法有 , , 。 二.判断题(10) 1.BCD 码即8421码 ( 错 ) 2.八位二进制数可以表示256种不同状态。 ( 对 ) 3.TTL 与非门与CMOS 与非门的逻辑功能不一样。 ( ) 4.多个三态门的输出端相连于一总线上,使用时须只让一个三态门传送信号,其他门处于高阻状态。 (对 ) 5.计数器可作分频器。 ( 对 ) 三.化简逻辑函数(14) 1.用公式法化简- - +++=A D DCE BD B A Y ,化为最简与或表达式。 解;D B A Y +=- 2.用卡诺图化简∑∑= m d D C B A Y ),,,,()+,,,, (84210107653),,,(,化为最简与或表达式。 四.电路如图1所示,要求写出输出函数表达式,并说出其逻辑功能。(15) 解;C B A Y ⊕⊕=, C B A AB C )(1++=,全加器,Y 为和,1C 为进位。 五.触发器电路如图2(a ),(b )所示,⑴写出触发器的次态方程; ⑵对应给定波形画出Q 端波形(设初态Q =0)(15) 解;(1)AQ Q Q n +=- +1 ,(2)、A Q n =+1 六.试用触发器和门电路设计一个同步的五进制计数器。(15) 七.用集成电路定时器555所构成的自激多谐振荡器电路如图3所示,试画出V O ,V C 的工作波形,并求出振荡频率。(15)

数字电子技术基础考题 一、填空题:(每空3分,共15分) 1.逻辑函数有四种表示方法,它们分别是(真值表)、(逻辑图)、(逻辑表达式)和(卡诺图)。 2.将2004个“1”异或起来得到的结果是(0 )。 3.由555定时器构成的三种电路中,()和()是脉冲的整形电路。4.TTL器件输入脚悬空相当于输入(高)电平。 5.基本逻辑运算有: (and )、(not )和(or )运算。 6.采用四位比较器对两个四位数比较时,先比较(最高)位。 7.触发器按动作特点可分为基本型、(同步型)、(主从型)和边沿型;8.如果要把一宽脉冲变换为窄脉冲应采用(积分型单稳态)触发器 9.目前我们所学的双极型集成电路和单极型集成电路的典型电路分别是(TTL )电路和(CMOS )电路。 10.施密特触发器有(2)个稳定状态.,多谐振荡器有(0 )个稳定状态。 11.数字系统按组成方式可分为功能扩展电路、功能综合电路两种;12.两二进制数相加时,不考虑低位的进位信号是(半)加器。 13.不仅考虑两个_______本位_____相加,而且还考虑来自___低位进位____相加的运算电路,称为全加器。 14.时序逻辑电路的输出不仅和___该时刻输入变量的取值______有关,而且还与_电路原来的状态_______有关。 15.计数器按CP脉冲的输入方式可分为__同步计数器和____异步计数器_。 16.触发器根据逻辑功能的不同,可分为_____rs______、______jk_____、___t________、___d________、___________等。 17.根据不同需要,在集成计数器芯片的基础上,通过采用__反馈归零法_________、__预置数法_________、__进位输出置最小数法__等方法可以实现任意进制的技术器。 18.4. 一个JK 触发器有 2 个稳态,它可存储 1 位二进制数。 19.若将一个正弦波电压信号转换成同一频率的矩形波,应采用多谐振荡器电路。20.把JK触发器改成T触发器的方法是 j=k=t 。 21.N个触发器组成的计数器最多可以组成2n 进制的计数器。 22.基本RS触发器的约束条件是rs=0 。

《数字电子技术》实验报告 实验序号:01 实验项目名称:门电路逻辑功能及测试 学号姓名专业、班级 实验地点物联网实验室指导教师时间2016.9.19 一、实验目的 1. 熟悉门电路的逻辑功能、逻辑表达式、逻辑符号、等效逻辑图。 2. 掌握数字电路实验箱及示波器的使用方法。 3、学会检测基本门电路的方法。 二、实验仪器及材料 1、仪器设备:双踪示波器、数字万用表、数字电路实验箱 2. 器件: 74LS00 二输入端四与非门2片 74LS20 四输入端双与非门1片 74LS86 二输入端四异或门1片 三、预习要求 1. 预习门电路相应的逻辑表达式。 2. 熟悉所用集成电路的引脚排列及用途。 四、实验内容及步骤 实验前按数字电路实验箱使用说明书先检查电源是否正常,然后选择实验用的集成块芯片插入实验箱中对应的IC座,按自己设计的实验接线图接好连线。注意集成块芯片不能插反。线接好后经实验指导教师检查无误方可通电实验。实验中

1.与非门电路逻辑功能的测试 (1)选用双四输入与非门74LS20一片,插入数字电路实验箱中对应的IC座,按图1.1接线、输入端1、2、4、5、分别接到K1~K4的逻辑开关输出插口,输出端接电平显 图 1.1 示发光二极管D1~D4任意一个。 (2)将逻辑开关按表1.1的状态,分别测输出电压及逻辑状态。 表1.1 输入输出 1(k1) 2(k2) 4(k3) 5(k4) Y 电压值(v) H H H H 0 0 L H H H 1 1 L L H H 1 1 L L L H 1 1 L L L L 1 1 2. 异或门逻辑功能的测试

图 1.2 (1)选二输入四异或门电路74LS86,按图1.2接线,输入端1、2、4、5接逻辑开关(K1~K4),输出端A、B、Y接电平显示发光二极管。 (2)将逻辑开关按表1.2的状态,将结果填入表中。 表1.2 输入输出 1(K1) 2(K2) 4(K35(K4) A B Y 电压(V) L H H H H L L L H H H H L L L H H L L L L L H H 1 1 1 1 1 1 1 1

实验一组合逻辑电路设计与分析 1.实验目的 (1)学会组合逻辑电路的特点; (2)利用逻辑转换仪对组合逻辑电路进行分析与设计。 2.实验原理 组合逻辑电路是一种重要的数字逻辑电路:特点是任何时刻的输出仅仅取决于同一时刻输入信号的取值组合。根据电路确定功能,是分析组合逻辑电路的过程,一般按图1-1所示步骤进行分析。 图1-1 组合逻辑电路的分析步骤 根据要求求解电路,是设计组合逻辑电路的过程,一般按图1-2所示步骤进 行设计。 图1-2 组合逻辑电路的设计步骤 3.实验电路及步骤 (1)利用逻辑转换仪对已知逻辑电路进行分析。 a.按图1-3所示连接电路。 b.在逻辑转换仪面板上单击由逻辑电路转换为真值表的按钮和由真值表导出 简化表达式后,得到如图1-4所示结果。观察真值表,我们发现:当四个输入变量A,B,C,D中1的个数为奇数时,输出为0,而当四个输入变量A,B,C,D 中1的个数为偶数时,输出为1。因此这是一个四位输入信号的奇偶校验电路。

(2)根据要求利用逻辑转换仪进行逻辑电路的设计。 a.问题提出:有一火灾报警系统,设有烟感、温感和紫外线三种类型不同的火 灾探测器。为了防止误报警,只有当其中有两种或两种以上的探测器发出火灾探测信号时,报警系统才产生报警控制信号,试设计报警控制信号的电路。 b.在逻辑转换仪面板上根据下列分析出真值表如图1-5所示:由于探测器发出 的火灾探测信号也只有两种可能,一种是高电平(1),表示有火灾报警;一种是低电平(0),表示正常无火灾报警。因此,令A、B、C分别表示烟感、温感、紫外线三种探测器的探测输出信号,为报警控制电路的输入、令F 为报警控制电路的输出。 图1-4 经分析得到的真值表和表达式

一、单项选择题(每小题1分,共15分) 在下列每小题的四个备选答案中选出一个正确的答案,并将其字母标号填入题干的括号内。 1.一位十六进制数可以用多少位二进制数来表示?( C ) A . 1 B . 2 C . 4 D . 16 2.以下电路中常用于总线应用的是( A ) A.T S L 门 B.O C 门 C. 漏极开路门 D.C M O S 与非门 3.以下表达式中符合逻辑运算法则的是( D ) A.C ·C =C 2 B.1+1=10 C.0<1 D.A +1=1 4.T 触发器的功能是( D ) A . 翻转、置“0” B. 保持、置“1” C. 置“1”、置“0” D. 翻转、保持 5. 存储8位二进制信息要多少个触发器(D ) A.2 B.3 C.4 D.8 6.多谐振荡器可产生的波形是( B ) A.正弦波 B.矩形脉冲 C.三角波 D.锯齿波 7.一个16选一的数据选择器,其地址输入(选择控制输入)端的个 数是( C ) A.1 B.2 C.4 D.16 8.引起组合逻辑电路中竟争与冒险的原因是( C ) A.逻辑关系错; B.干扰信号; C.电路延时; D.电源不稳定。 9.同步计数器和异步计数器比较,同步计数器的最显著优点是( A ) A.工作速度高 B.触发器利用率高 C.电路简单 D.不受时钟C P 控制 10.N 个触发器可以构成能寄存多少位二进制数码的寄存器?( B ) A.N -1 B.N C.N +1 D.2N 11.若用J K 触发器来实现特性方程AB Q A Q n 1n +=+,则J K 端的方程应为 ( B ) A.J =A B ,K =B A B.J =A B ,K =B A C.J =B A +,K =A B D.J =B A ,K =A B 12.一个无符号10位数字输入的D A C ,其输出电平的级数是( C ) A.4 B.10 C.1024 D.100 13.要构成容量为4K ×8的RAM ,需要多少片容量为256×4的RAM ?( D ) A.2 B.4 C.8 D.32 14.随机存取存储器R A M 中的内容,当电源断掉后又接通,则存储器中的内容将如何变换?( C ) A.全部改变 B.全部为1 C.不确定 D.保持不变 15.用555定时器构成单稳态触发器,其输出的脉宽为( B ) A.0.7RC ; B.1.1RC ; C.1.4RC ; D.1.8RC ;

数字电子技术基础1 一.1.(15分) 试根据图示输入信号波形分别画出各电路相应的输出信号波形L1、L2、L3、L4、和L5。设各触发器初态为“0”。 二.(15分) 已知由八选一数据选择器组成的逻辑电路如下所示。试按步骤分析该电路在M1、M2取不同值时(M1、M2取值情况如下表所示)输出F的逻辑表达式。 八选一数据选择器输出端逻辑表达式为:Y=Σm i D i,其中m i是S2S1S0最小项。 三.(8分) 试按步骤设计一个组合逻辑电路,实现语句“A>B”,A、B均为两位二进制数,即A (A1、A0),B(B1、B0)。要求用三个3输入端与门和一个或门实现。 四.(12分) 试按步骤用74LS138和门电路产生如下多输出逻辑函数。 74LS138逻辑表达式和逻辑符号如下所示。 五.(15分) 已知同步计数器的时序波形如下图所示。试用维持-阻塞型D触发器实现该计数器。要求按步骤设计。 六.(18分) 按步骤完成下列两题 1.分析图5-1所示电路的逻辑功能:写出驱动方程,列出状态转换表,画出完全状态转换图和时序波形,说明电路能否自启动。 2.分析图5-2所示的计数器在M=0和M=1时各为几进制计数器,并画出状态转换图。 图5-1

图5-2 七. 八.(10分) 电路下如图所示,按要求完成下列问题。 1.指出虚线框T1中所示电路名称. 2.对应画出V C 、V 01、A 、B 、C 的波形。并计算出V 01波形的周期T=?。 数字电子技术基础2 一.(20分)电路如图所示,晶体管的β=100,Vbe=0.7v 。 (1)求电路的静态工作点; (2) 画出微变等效电路图, 求Au 、r i 和r o ; (3)若电容Ce 开路,则将引起电路的哪些动态参数发生变化?并定性说明变化趋势. 二.(15分)求图示电路中a U 、b U 、b U 、c U 及L I 。 三.(8分)逻辑单元电路符号和具有“0”、“1”逻辑电平输入信号X 1如下图所示,试分别画出各单元电路相应的电压输出信号波形Y 1、Y 2、Y 3。设各触发器初始状态为“0”态。 四.(8分)判断下面电路中的极间交流反馈的极性(要求在图上标出瞬时极性符号)。如为负反馈,则进一步指明反馈的组态。 (a ) (b )

数字电子技术试卷试题答案汇总(完整版)

数字电子技术基础试卷试题答案汇总 一、 填空题(每空1分,共20分) 1、逻辑代数中3种基本运算是 , , 。 2、逻辑代数中三个基本运算规 则 , , 。 3、逻辑函数的化简有 , 两种方法。 4、A+B+C= 。 5、TTL 与非门的u I ≤U OFF 时,与非门 ,输出 ,u I ≥U ON 时,与 非门 ,输出 。 6、组合逻辑电路没有 功能。 7、竞争冒险的判断方法 , 。 8、触发器它有 稳态。主从RS 触发器的特性方 程 , 主从JK 触发器的特性方程 ,D 触发器的特性方 程 。 二、 选择题(每题1分,共10分) 1、相同为“0”不同为“1”它的逻辑关系是 ( ) A 、或逻辑 B 、与逻辑 C 、异或逻辑 2、Y (A ,B ,C ,)=∑m (0,1,2,3)逻辑函数的化简式 ( ) A 、Y=AB+BC+ABC B 、Y=A+B C 、Y=A 3、 A 、Y=A B B 、Y 处于悬浮状态 C 、Y=B A + 4、下列图中的逻辑关系正确的是 ( ) A.Y=B A + B.Y=B A + C.Y=AB 5、下列说法正确的是 ( ) A 、主从JK 触发器没有空翻现象 B 、JK 之间有约束 C 、主从JK 触发器的特性方程是CP 上升沿有效。 6、下列说法正确的是 ( ) A 、同步触发器没有空翻现象 B 、同步触发器能用于组成计数器、移位寄存器。 C 、同步触发器不能用于组成计数器、移位寄存器。 7、下列说法是正确的是 ( ) A 、异步计数器的计数脉冲只加到部分触发器上 B 、异步计数器的计数脉冲 同时加到所有触发器上 C 、异步计数器不需要计数脉冲的控制 8、下列说法是正确的是 ( )

数字电子技术基础试题(一) 一、填空题 : (每空1分,共10分) 1. (30.25) 10 = ( ) 2 = ( ) 16 。 2 . 逻辑函数L = + A+ B+ C +D = 。 3 . 三态门输出的三种状态分别为:、和。 4 . 主从型JK触发器的特性方程= 。 5 . 用4个触发器可以存储位二进制数。 6 . 存储容量为4K×8位的RAM存储器,其地址线为条、数据线为条。 二、选择题: (选择一个正确的答案填入括号内,每题3分,共30分 ) 1.设下图中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:()图。 2.下列几种TTL电路中,输出端可实现线与功能的电路是()。 A、或非门 B、与非门 C、异或门 D、OC门 3.对CMOS与非门电路,其多余输入端正确的处理方法是()。

A、通过大电阻接地(>1.5KΩ) B、悬空 C、通过小电阻接地(<1KΩ) D、通过电阻接V CC 4.图2所示电路为由555定时器构成的()。 A、施密特触发器 B、多谐振荡器 C、单稳态触发器 D、T触发器 5.请判断以下哪个电路不是时序逻辑电路()。 A、计数器 B、寄存器 C、译码器 D、触发器 6.下列几种A/D转换器中,转换速度最快的是()。 A、并行A/D转换器 B、计数型A/D转换器 C、逐次渐进型A/D转换器 B、 D、双积分A/D转换器 7.某电路的输入波形 u I 和输出波形 u O 如下图所示,则该电路为()。 A、施密特触发器 B、反相器 C、单稳态触发器 D、JK触发器 8.要将方波脉冲的周期扩展10倍,可采用()。 A、10级施密特触发器 B、10位二进制计数器 C、十进制计数器 B、D、10位D/A转换器 9、已知逻辑函数与其相等的函数为()。 A、 B、 C、 D、 10、一个数据选择器的地址输入端有3个时,最多可以有()个数据信号输出。 A、4 B、6 C、8 D、16 三、逻辑函数化简(每题5分,共10分) 1、用代数法化简为最简与或式