SWD与JTAG区别及使用情况

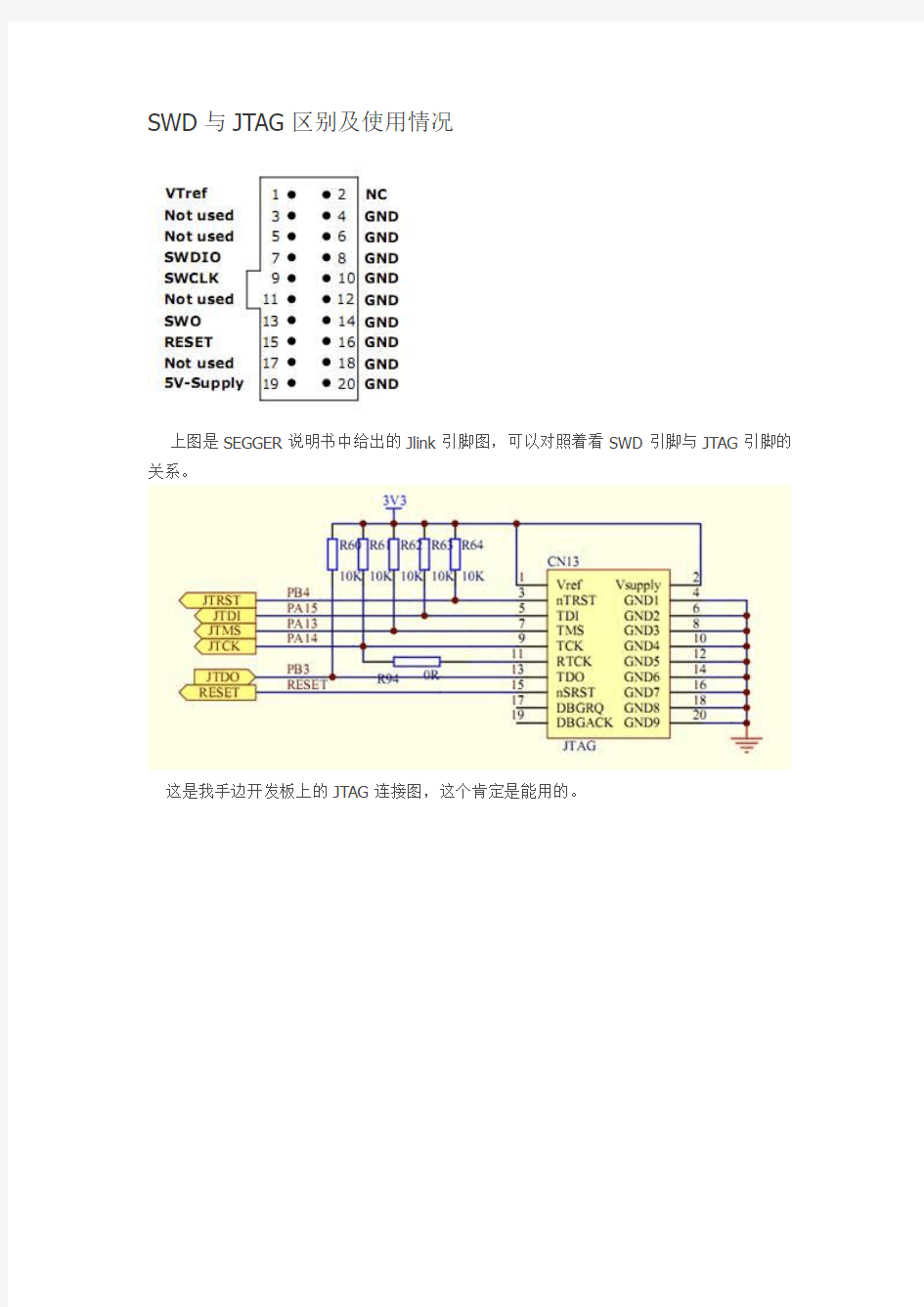

上图是SEGGER说明书中给出的Jlink引脚图,可以对照着看SWD引脚与JTAG引脚的关系。

这是我手边开发板上的JTAG连接图,这个肯定是能用的。

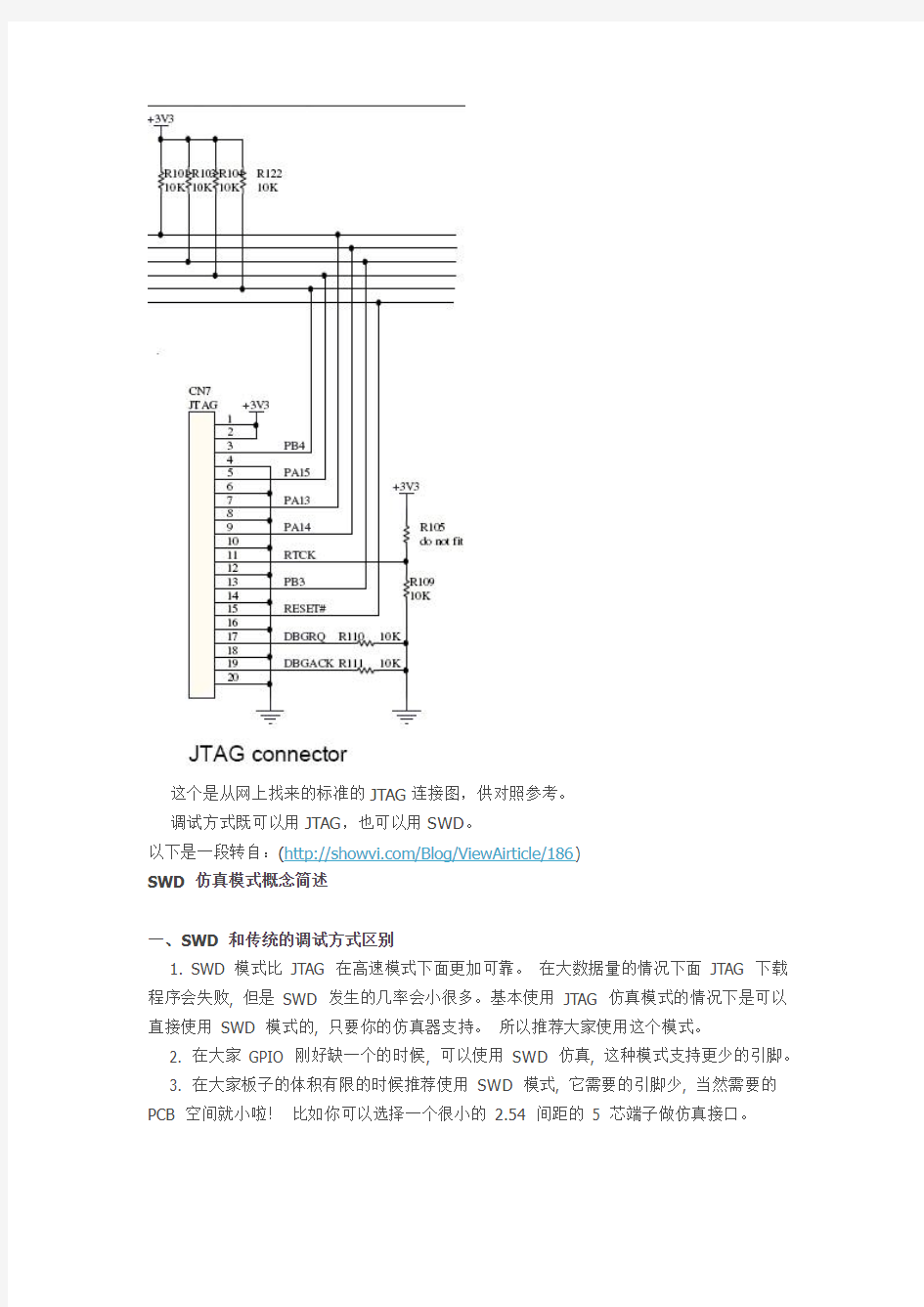

这个是从网上找来的标准的JTAG连接图,供对照参考。

调试方式既可以用JTAG,也可以用SWD。

以下是一段转自:(https://www.doczj.com/doc/d910847410.html,/Blog/ViewAirticle/186)

SWD 仿真模式概念简述

一、SWD 和传统的调试方式区别

1. SWD 模式比JTAG 在高速模式下面更加可靠。在大数据量的情况下面JTAG 下载程序会失败, 但是SWD 发生的几率会小很多。基本使用JTAG 仿真模式的情况下是可以直接使用SWD 模式的, 只要你的仿真器支持。所以推荐大家使用这个模式。

2. 在大家GPIO 刚好缺一个的时候, 可以使用SWD 仿真, 这种模式支持更少的引脚。

3. 在大家板子的体积有限的时候推荐使用SWD 模式, 它需要的引脚少, 当然需要的PCB 空间就小啦!比如你可以选择一个很小的2.54 间距的 5 芯端子做仿真接口。

二、仿真器对SWD 模式支持情况

1. 市面上的常用仿真器对SWD 模式支持情况

(1) JLINKV6 支持SWD 仿真模式,速度较慢。

(2) JLINKV7 比较好的支持SWD 仿真模式, 速度有了明显的提高,速度是JLINKV6 的6 倍。

(3) JLINKV8 非常好的支持SWD 仿真模式, 速度可以到10M。

(4) ULINK1 不支持SWD 模式。

(5) 盗版ULINK2 非常好的支持SWD 模式,速度可以达到10M。

(6) 正版ULINK2 非常好的支持SWD 模式,速度可以达到10M。

2. SWD 硬件接口上的不同

(1) JLINKV6 需要的硬件接口为: GND, RST, SWDIO, SWDCLK

(2) JLINKV7 需要的硬件接口为: GND, RST, SWDIO, SWDCLK

(3) JLINKV8 需要的硬件接口为: VCC, GND, RST, SWDIO, SWDCLK (注:下面有我自己用JLINKV8的实际连线及相应实验结果)

(4) ULINK1 不支持SWD 模式

(5) 盗版ULINK2 需要的硬件接口为: GND, RST, SWDIO, SWDCLK

(6) 正版ULINK2 需要的硬件接口为: GND, RST, SWDIO, SWDCLK

由此可以看到只有JLINKV8 需要5 个引脚,即多了一个VCC引脚,其好处是: 仿真器对目标板子的仿真需要用到RST 引脚, 使用仿真器内部的VCC 作这个功能其实并不是非常美妙。因此,JLINKV8 选择了只和目标板共GND, 但不共VCC。因此我觉得这种模式最合理, 当然通常情况下仿真器和目标板共GND 和VCC 是没有错的。

三、在MDK 中SWD 模式的设置

接下来告诉大家怎么使用SWD设置:

打开工程OPTION设置:

在设置中按照上图设置成SWD 模式, 速度你可以按照你的实际需求来设置, 如果你的板子供电系统不是特别稳定, 纹波比较大或者仿真线比较长可以设置成500K 或者1M,如果环境很好当然可以选择10M , 当然速度会飞起来。

记得不要忽略了左下方的那个USB还是TCP 模式, 当然我们是USB 模式, 因为有的时候默认是TCP 模式, 这个时候我们忽略这个设置后会仿真常常连接不上的。

/////转载结束

下面是我自己的试验(用JLINK V8)

(1)按SW方式来调试,实际需要接1,7,9,15,20脚,某些资料上说的需要6个脚(第13脚SWO也需要连上)是不对的,SWO不需要连接。

按上所述连接5个引脚时出现的画面

1脚不接时出现的画面

(2)用两种方式的速度没有太大的区别。

再次测试:

(1)不接第15脚,即RESET脚,仅接4条引线,即Vref,SWDIO,SWCLK,GND。

(2)设置时Reset位选择:AutoDetect,可以正常下载,仿真。

(3)如果Reset位选选择:HW Reset ,则不能正常下载。

(4)速度远没有上面转载中说的那样快,擦除和写入ucosDemo工程约需40多s。以下是这个工程的代码量:

Program Size: Code=96830 RO-data=143650 RW-data=1016 ZI-data=16440

但是有个现象,即下载一次后退出,然后再次进入(没有重编译时),似乎没有擦除和下载的过程,时间飞快。也许这就是上面所说的时间快的原因?

////以下来自21icbbs// https://www.doczj.com/doc/d910847410.html,/icview-127364-1-1.html

问:一直在核心板上玩103ZE,都是些小程序都是在RAM中调试的,而且只接三根线GND SWDIO SWCLK(VCC 直接接JLINK内部的),很爽利。不过今天要试IIS 要放一个大的数据进去,于是要烧到FLASH中去,发现很快进度条走完,然后显示失败,放狗一

搜,说要接RESET,于是接上,果然下进去了...惨了,我PCB都画好了,都只有4线(VCC SWDIO SWCLK GND),以后怎么办呢?

答:可以不接,可以在MDK仿真器的设置里面不使用硬件复位,而是用system reset 或者vect reset,前者适用的范围更广

/////转载结束

JTAG引脚可以被复用为IO口,但是这样一来,JLINK就不能够连上芯片了。解决的方法有两种:

(1)另写一段程序,不要将JTAG复用为I/O口,然后将这段程序用串口工具写入芯片中;

(2)将BOOT0/BOOT1设置成为内部RAM启动,那么上电后就不会执行FLASH中的程序,这样JLINK就能顺利“接管”JTAG引脚。

做这个贴子的用途是为硬件设计做一点准备。

原文来自:https://www.doczj.com/doc/d910847410.html,/czlyzhj/1805761/message.aspx

扩展阅读:https://www.doczj.com/doc/d910847410.html,/Info_ArticleList_Show.asp?ArticleId=32

USB AVR USB AVR JTAG JTAG JTAGICE ICE ICE 使用说明 使用说明 版本:R R e v 1.0 2020008-1

简介 一、简介 USB AVR JTAGICE支持自动升级和手动升级的仿真器,与AVR Studio相结合,通过 USB可以对所有带JTAG 接口的单片机进行在片调试和编程。 【主要功能简介】 · 基于ATMEL原厂提供的方案而设计,支持AVRStudio,借鉴了ATMEL原厂生产的 JTAGICE仿真器,使用方法同它们一致,简单易用,稳定可靠。手动升级采用AVR910对监控芯片升级,彻底解决冲掉监控代码的后顾之忧! · 接入目标板的JTAG接口,可使用JTAG方式进行连接。 · JTAG功能: - JTAG仿真及编程支持的器件型号:与ATMEL原装JTAGICE仿真器支持的器件型号相同。 - JTAG仿真功能与性能:与ATMEL原装JTAGICE仿真器仿真功能相同。支持全速运行、单步调试、断点调试等各种调试方法,可查看IO状态,变量数据等,仿真速度可设置提高至115200bps等等。 - JTAG编程功能与性能:与ATMEL原装JTAGICE仿真器烧写功能相同。可直接烧写程序,设置熔丝位等。 · 与PC机的连接接口: - 准USB接口(USB To RS232,需要安装驱动程序!); · 与目标板的连接接口: - 与ATMEL官方JTAG标准接口兼容; · 特点: - 监控固件程序可升级!JTAG采用单独的MCU进行控制,控制程序均采用ATMEL提供的固件程序,使得该仿真器可自动检测AVRStudio的新版本。日后,ATMEL将会推出更多AVR型号,亦会将新的器件型号添加入AVRStudio的器件支持列表,当您在未来开发中需要使用最新的型号,升级AVRStudio,升级仿真器的固件程序,仿真器便得以支持新的型号!

JTAG接口的定义及常见问题 ARM系统的JTAG接口的设计不当往往使硬件系统无法调试,所以在设计ARM 系统前要先熟悉ARM系统的JTAG接口的定义和常见问题。 1.ARM系统的JTAG接口是如何定义的?每个PIN又是如何连接的? 下图是JTAG接口的信号排列示意: 接口是一个20脚的IDC插座。下表给出了具体的信号说明: 表 1 JTAG引脚说明 序号信号名方向说明 1 Vref Input 接口电平参考电压,通常可直接接电源 2 Vsupply Input 电源 (设备提供) 3 nTRST Output (可选项) JTAG复位。在目标端应加适当的上拉电阻以防止误触发。 4 GND -- 接地 5 TDI Output Test Data In from Dragon-ICE to target. 6 GND -- 接地 7 TMS Output Test Mode Select 8 GND -- 接地 9 TCK Output Test Clock output from Dragon-ICE to the target 10 GND -- 接地 11 RTCK Input (可选项) Return Test Clock。由目标端反馈给Dragon-ICE的时钟信号,用来同步TCK信号的产生。不使用时可以直接接地。12 GND -- 接地

13 TDO Input Test Data Out from target to Dragon-ICE. 14 GND -- 接地 15 nSRST Input/Output (可选项) System Reset,与目标板上的系统复位信号相连。可以直接对目标系统复位,同时可以检测目标系统的复位情况。为了防止误触发,应在目标端加上适当的上拉电阻。 16 GND -- 接地 17 NC -- 保留 18 GND -- 接地 19 NC -- 保留 20 GND -- 接地 2.目标系统如何设计? 目标板使用与Dragon-ICE一样的20脚针座,信号排列见表1。RTCK和 nTRST 这两个信号根据目标ASIC有否提供对应的引脚来选用。nSRST则根据目标系统的设计考虑来选择使用。下面是一个典型的连接关系图: 复位电路中可以根据不同的需要包含上电复位、手动复位等等功能。如果用户希望系统复位信号nSRST能同时触发JTAG口的复位信号nTRST,则可以使用一些简单的组合逻辑电路来达到要求。后面给出了一种电路方案的效果图。

Jtag的各种引脚定义 使用过ARM芯片的人肯定都听过一个仿真器————JLINK,为什么ARM芯片现在能够这么流行?其中恐怕就有一个原因就是很多的ARM芯片都支持使用Jlink进行调试和仿真。所以你只要有一个Jlink,不管是ARM7、ARM9、ARM11还是最新的ARM Cortex 系统都能下载和调试了。 以前的嵌入式开发者,可能使用什么公司的芯片就得买一个对应芯片的下载和仿真器,这样如果你只使用一种芯片,可能还好,不过恐怕没有那种芯片能够一直引领市场。 Jlink使用的是一种叫做JTAG的协议,JTAG原本是用于芯片内部测试的,现在大多用于芯片的程序下载和调试仿真。由于现在Jlink用的比较多,所以有些人可能把Jlink就等同于JTAG了,实际上,JTAG是一种协议,只要满足这种协议的就可以叫做JTAG,比如H—JTAG、OpenJTAG、OSJTAG等等。正版的Jlink是卖的很贵的。大概是1000到2000RMB吧。不过,中国的山寨能力是很强的,而且你硬件卖给别人了,你也没办法控制别人说你不许拆开我的东西看里面的电路是怎么样的。所以Jlink就被破解了,破解之后的Jlink很便宜,网上五六十块钱就能买到一个能用的Jlink。 除了商业版的Jlink和H—JTAG,网上还有一些电子爱好者,他们参照开源软件的模式,设计了开源硬件,比如arduino。还有人制作了开源版本的JTAG仿真器——OpenJTAG。而一些芯片的开发商不像那些软件厂商,会给软件做很多的限制,他们对于开源硬件还是比较开明的,所以他们也支持了一些开源硬件。比如TI公司的MSP430 LaunchPad、ST公司的STM Discovery 等等板子。还有飞思卡尔公司的USBDM和OSJTAG。他们把这些硬件的原理图、PCB还有固件都放在了网络上供人自由下载和制作,你也可以根据他的资料进行改进。这样能使大家对于他们家的芯片有更多的了解,所以,他们也乐于开源一些评估板。 今天我要说的是几种JTAG仿真器的引脚定义,首先我看看比较常见的JTAG 20-Pin的引脚接口如下:

U盘版AVR-JTAG-ICE 仿真器 安装与使用说明(V1.0版) 目录 一、产品介绍 (3) 二、安装驱动 (4)

三、硬件连接 (5) 四、安装软件 (7) 五、升级固件 (8) 六、在线编程 (12) 七、在线仿真 (14) 八、疑难解答 (16) 九、断开对外5V供电(3.3V供电系统) (16) 一、产品介绍

迷你型USB AVR JTAG ICE仿真器是一款针对AVR系列具有JTAG接口的单片机进行在线编程下载、仿真调试开发的优秀首选工具,仿真器内部固件可无限升级,故可适应AVRstudio 各种版本软件。其外形小巧,价格低廉,是工厂、学校、个人等开发AVR系列单片机的首选产品。 特点: 1.支持USB1.1或USB 2.0通信; 2.全面支持WIN98、WINME、WIN2000、WINXP、VISTA、WIN7等32位与64位操作系统; 3.采用USB口供电,板内带有500mA自恢复保险丝,保护电脑主板不被意外烧毁; 4.在对芯片编程仿真时可以使用目标系统本身电源,也可以使用仿真器从USB口取电 供给目标板,但应保证目标标电流不大于500mA,以免过流保护不能正常工作; 5.支持AVR系列单片机具有JTAG接口的所有型号芯片; 6.编程完成不影响目标板的程序运行,可以对Flash、EEPROM、熔丝位等读写操作; 7.支持3.3V与5V工作电压系统; 8.固件可无限升级,支持多个版本的AVR studio环境; 9.使用Atmel公司推荐的标准10PIN JTAG接口; 10.使用铝合金外壳设计,提供多色可选,小巧时尚携带方便。 二、安装驱动

JTAG各类接口针脚定义及含义 JTAG有10pin的、14pin的和20pin的,尽管引脚数和引脚的排列顺序不同,但是其中有一些引脚是一样的,各个引脚的定义如下。 一、引脚定义 Test Clock Input (TCK) -----强制要求1 TCK在IEEE1149.1标准里是强制要求的。TCK为TAP的操作提供了一个独立的、基本的时钟信号,TAP的所有操作都是通过这个时钟信号来驱动的。 Test Mode Selection Input (TMS) -----强制要求2 TMS信号在TCK的上升沿有效。TMS在IEEE1149.1标准里是强制要求的。TMS信号用来控制TAP状态机的转换。通过TMS信号,可以控制TAP在不同的状态间相互转换。 Test Data Input (TDI) -----强制要求3 TDI在IEEE1149.1标准里是强制要求的。TDI是数据输入的接口。所有要输入到特定寄存器的数据都是通过TDI接口一位一位串行输入的(由TCK驱动)。 Test Data Output (TDO) -----强制要求4 TDO在IEEE1149.1标准里是强制要求的。TDO是数据输出的接口。所有要从特定的寄存器中输出的数据都是通过TDO接口一位一位串行输出的(由TCK驱动)。 Test Reset Input (TRST) ----可选项1 这个信号接口在IEEE 1149.1标准里是可选的,并不是强制要求的。TRST可以用来对TAPController进行复位(初始化)。因为通过TMS也可以对TAP Controll进行复位(初始化)。所以有四线JTAG与五线JTAG之分。 (VTREF) -----强制要求5 接口信号电平参考电压一般直接连接Vsupply。这个可以用来确定ARM的JTAG接口使用的逻辑电平(比如3.3V还是5.0V?) Return Test Clock ( RTCK) ----可选项2 可选项,由目标端反馈给仿真器的时钟信号,用来同步TCK信号的产生,不使用时直接接地。System Reset ( nSRST)----可选项3 可选项,与目标板上的系统复位信号相连,可以直接对目标系统复位。同时可以检测目标系统的复位情况,为了防止误触发应在目标端加上适当的上拉电阻。 USER IN 用户自定义输入。可以接到一个IO上,用来接受上位机的控制。 USER OUT 用户自定义输出。可以接到一个IO上,用来向上位机的反馈一个状态 由于JTAG经常使用排线连接,为了增强抗干扰能力,在每条信号线间加上地线就出现了这种20针的接口。但事实上,RTCK、USER IN、USER OUT一般都不使用,于是还有一种14针的接口。对于实际开发应用来说,由于实验室电源稳定,电磁环境较好,干扰不大。

AVR JTAG下载HEX文件使用说明 本文只介绍AVR JTAG下载HEX文件在AVR Studio环境下的下载方法,推荐使用。并口下载线主要优点是电路简单,缺点主要有下载速度慢、不能在AVR Studio环境下使用。具体差别在用了AVR JTAG 之后就知道了,现在一个标准的下载线也只要几十块钱和并口下载线没什么差别了。此处所说的STK500下载线和AVR ISP下载线同属一类,它们使用相同的通信协议,STK500确切的说是一个学习板,AVR JTAG才是真正意义上的下载线。 AVR JTAG实物图片 AVR JTAG连接示意图 JTAG接口 支持芯片列表

AVR JTAG下载线支持芯片型号非常多,这里就不一一列出了,只要AVR芯片支持ISP下载的都可以。AVR JTAG下载HEX文件-操作方法: 1、打开AVR Studio 软件,按下图操作。 2、在这里选择所用器件及连接端口,选择JTAG ICE,自动检测端口,点击Connect进入下一步。 3、下面窗口提示所用AVR ISP下载线固件版本与当前所用软件不同,提示要求升级AVR ISP下载线固件,如版本相同就不会出现下面的提示。如你所用的AVR ISP下载线不支持在线升级功能的话,不要点确定要不AVR ISP下载线会死在那里不动了,直接点击取消跳过此步既可。 4、正常会进入下面编程(Program)界面。主要包括有器件(Device)、编程模式(Programming mode)、Flash下载、EEPROM下载几个部分,最下面部分是信息窗口。

器件:用于选择器件和手工擦除器件。 编程模式:用于选择ISP和并口下载模式,由于此处用的是AVR JTAG下载线只支持ISP方式下载。Erase Device Before擦除器件,选中此项在每次下载前会对将器件擦除。需要同时烧写用户程序和引导程序时需要注意此处,正常情况下需选中此项。Verify Devic写入校验,默认为选中。 Flash:下载Flash文件,有选择文件(Input HEX File)、编程(Program)、校验(Verify)、读取(Read)。 EEPROM:下载EEPROM文件,包含内容与上面相同。 如果你是初学者,并不要求对器件进行熔丝等复杂配置,由此窗口将HEX文件写入器件就可以实验了。其它系统时钟及看门狗等可先使用器件默认配置。 5、下图为熔丝配置(Fuses)界面,具体配置请参照熔丝配置部分。

JTAG接口电路 1 JTAG(Joint Test Action Group;联合测试行动小组)是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。 JTAG最初是用来对芯片进行测试的,JTAG的基本原理是在器件内部定义一个TAP(Test Access Port;测试访问口)通过专用的JTAG测试工具对进行内部节点进行测试。JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试。现在,JTAG接口还常用于实现ISP(In-System Programmable�在线编程),对FLASH等器件进行编程。 JTAG编程方式是在线编程,传统生产流程中先对芯片进行预编程现再装到板上因此而改变,简化的流程为先固定器件到电路板上,再用JTAG编程,从而大大加快工程进度。JTAG接口可对PSD芯片内部的所有部件进行编程 具有JTAG口的芯片都有如下JTAG引脚定义: TCK——测试时钟输入; TDI——测试数据输入,数据通过TDI输入JTAG口; TDO——测试数据输出,数据通过TDO从JTAG口输出; TMS——测试模式选择,TMS用来设臵JTAG口处于某种特定的测试模式。 可选引脚TRST——测试复位,输入引脚,低电平有效。 含有JTAG口的芯片种类较多,如CPU、DSP、CPLD等。 JTAG内部有一个状态机,称为TAP控制器。TAP控制器的状态机通过TCK和TMS进行状态的改变,实现数据和指令的输入。图1为TAP控制器的状态机框图。 2 JTAG芯片的边界扫描寄存器 JTAG标准定义了一个串行的移位寄存器。寄存器的每一个单元分配给IC芯片的相应引脚,每一个独立的单元称为BSC(Boundary-Scan Cell)边界扫描单元。这个串联的BSC在IC内部构成JTAG回路,所有的BSR (Boundary-Scan Register)边界扫描寄存器通过JTAG测试激活,平时这些引脚保持正常的IC功能。图2为具有JTAG口的IC内部BSR单元与引脚的关系。 3 JTAG在线写Flash的硬件电路设计和与PC的连接方式 以含JTAG接口的StrongARM SA1110为例,Flash为Intel 28F128J32 16MB容量。SA1110的JTAG的TCK、TDI、TMS、TDO分别接PC并口的2、3、4、11线上,通过程序将对JTAG口的控制指令和目标代码从PC的并口写入JTAG的BSR中。在设计PCB时,必须将SA1110的数据线和地址线及控制线与Flash的地线线、数据线和控制线相连。因SA1110的数据线、地址线及

JTAGICE MKII仿真器使用方法 一:硬件和软件的准备 1. 仿真器上需要接一个ISP-10PIN的转换线(实物已经接好); 2.不能将WDAM的JP1那一行VCC和GND的管脚拆下,仿真器不能提供电源,但是需要接上VCC和GND; 3. WDAM需要外部供电; 4.需要将与RESET管脚连接的容性器件拆下,即将R39的电容拆下; 5.安装AVR studio4(仿真器也可与AVR studio5或者AVR studio6一起使用,但我是用AVR studio4测试的,所以建议使用AVR studio4) 二、烧写程序 1.打开AVR studio4,选择Tools-Program-connect,弹出如下对话框,依次选择 2.选择完后,弹出另一对话框,依次按如下选择,即可完成程序下载

三、仿真 1、打开AVR studio4,选择project-projectWizard,弹出如下对话框,点击OPEN,选择我们用ICCAVR编写的程序的工程文件里的.COF文件

2.上面那步操作完后会弹出如下对话框,按图依次选择 3.如果MCU没有使能DWEN熔丝位,会弹出如下对话框,选择”Use SPI to enable debugWIRE interface”,点击OK后,会弹出一个对话框,提示需要重启设备,此时我们重新启动WDAM后,点击确定,即可进入仿真界面

三、取消DWEN的使能 1、打开AVR studio4,选择project-projectWizard,弹出如下对话框,点击OPEN,随意选择我们用ICCAVR编写的程序的工程文件里的.COF文件

AVR JTAGICE使用说明 [日期:2008-01-20 ] [来源:EDA网作者:] [字体:大中小] (投递新闻) 可以用AVR Studio的4.0或更高版本控制STK500和JTAG ICE,选择STK500 or AVRISP 和Auto或者具体的COM?端口进行联机,点击avr studio主窗口中的图标 前面标有Con的那个图标,然后按下图选择即可进行JTAG的联机,由于avr studio会记忆用户使用的设备是并且同时会记忆用户使用的COM号,如果下次和上次使用的是相同的设备并且没有更换COM口,那么下次使用的时候直接点击右边标有AVR的那个图标就可以快速进入联机状态;如果下次和上次使用了不同的设备或不同的COM口请使用Con图标进行联机。 JTAG和目标板相连 AVR JTAG 同目标板的连接:最小需要6条线与目标板相连,才可以完成仿真任务,他们是:TCK 、TMS 、TDO 、TDI、Vref、GND,另外有两条可选择的引线nSRST 和Vsu pply 。引脚nTRST不接,Vsupply的功能是由目标板向JTAGICE供电(仅对接口部分)n SRST的作用是监视目标板的复位线。然而,在仿真过程中不是必须的。如果应用程序对M CUSR中JTD位进行了编程,JTAG接口就会关闭,为了使用JTAGICE对目标板重新编程。就必须控制复位引脚。 连接JTAG ICE仿真器:联机之前请确保本设备已经和目标板有连接且LED4点亮。

进行JTAG ICE联机时请确保目标AVR选中如下熔丝项:如下图 程序下载和融丝位设置 打开AVRStudio,将会提示一个welcome对话框,如下图所示: 点Cancel键取消(建议你把左边的show this dialog on也去掉)。 然后选择下载工具:

并口与连接 1.并行口基地址: 0x0378 新系统通用,通常是LPT1,也可以是LPT2,通常使用中断IRQ7 0x0278 通常是LPT2,也可以是LPT1,LPT3(只能用此基地址),通常使用中断IRQ5 2.寄存器定义 3.状态寄存器(379)和控制寄存器(37A)的定义:

5.连接方式 a)hybus255与并口的连接是通过74CH541与并口连接 LPT D0 Pin 2 and TCK J10 Pin 4 LPT D1 Pin 3 and TDI J10 Pin 11 LPT D2 Pin 4 and TMS J10 Pin 9 LPT Busy Pin 11 and TDO J10 Pin 13 b)2410以及44b0连接图 TCK---------------->DATA0 TDI---------------->DATA1 TMS---------------->DATA2 TDO---------------->STATUS7

6.寄存器的读写 a)先对控制寄存器(Control)初始化 如果禁止中断用out(37A,0x80),如果使用中断用out(37A,0x90) b)写一个寄存器的两条基本指令: out(37B,addr);// 将addr写入用户设备地址寄存器 写:out(37C,data);// 将数据data写入addr指向的用户设备空间单元 读:in(37C);// 从addr指向的用户设备空间单元中读取数据 JTAG接口信息 1.TCK:输入移位时钟TMS和TDI的数据在TCK的上升沿被采样数据在时钟的下降沿输出到TDO 2.TMS:输入方式选择TMS用于控制TAP状态机 3.TDI:输入。输入到指令寄存器IR或数据寄存器DR的数据出现在TDI输入端在TCK的上升沿被采样 4.TDO:TDO输出来自指令寄存器或数据寄存器的数据在时钟的下降沿被移出到TDO

AVR JTAG AVR仿真器V3使用说明 AVR JTAG是与Atmel公司的AVR Studio相配合的一套完整的基于JTAG接口的片上调试工具,支持所有AVR的8位RISC指令的带JTAG口的微处理器。JTAG接口是一个4线的符合IEEE 1149.1标准的测试接入端口(TAP)控制器。IEEE的标准提供一种行之有效的电路板连接性测试的标准方法(边界扫描)。Atmel的AVR器件已经扩展了支持完全编程和片上调试的功能。 AVR JTAG仿真器用来进行芯片硬件仿真,如程序单步执行、设置断点等,通过硬件仿真可以了解芯片里面程序的详细运行情况。AVR JTAG仿真器主要用来对芯片进行仿真操作,同时也可以通过JTAG接口对芯片编程(将程序写入芯片)。 AVR JTAG仿真器图片 AVR JTAG连接示意图

AVR JTAG仿真器与单片机/开发板连接方法:以ATMEGA16和ATMEGA128为例: 如果使用的不是本店的开发板通电前请参照上面的接口图先确认接口是否对应以免损坏硬件,开发板上的JTAG接口第4与第7针都要与VCC接通。 支持芯片列表: ATmega16(L), ATmega32(L), ATmega323(L), ATmega64(L), ATmega128(L) ,ATmega162(L), ATmega169(L or V) 把仿真器直接插到电脑的USB并安装驱动: AVR Studio 软件推荐使用4.18版本,如果你与开发板一起购买在开发板的光盘里有软件,如果没买开发板可到以下网址下载: https://www.doczj.com/doc/d910847410.html,/dyn/resources/prod_docu ments/AvrStudio4Setup.exe

使用过ARM芯片的人肯定都听过一个仿真器————JLINK,为什么ARM芯片现在能够这么流行?其中恐怕就有一个原因就是很多的ARM芯片都支持使用Jlink进行调试和仿真。所以你只要有一个Jlink,不管是ARM7、ARM9、ARM11还是最新的ARM Cortex 系统都能下载和调试了。 以前的嵌入式开发者,可能使用什么公司的芯片就得买一个对应芯片的下载和仿真器,这样如果你只使用一种芯片,可能还好,不过恐怕没有那种芯片能够一直引领市场。 Jlink使用的是一种叫做JTAG的协议,JTAG原本是用于芯片内部测试的,现在大多用于芯片的程序下载和调试仿真。由于现在Jlink用的比较多,所以有些人可能把Jlink就等同于JTAG了,实际上,JTAG是一种协议,只要满足这种协议的就可以叫做JTAG,比如H—JTAG、OpenJTAG、OSJTAG等等。正版的Jlink是卖的很贵的。大概是1000到2000RMB吧。不过,中国的山寨能力是很强的,而且你硬件卖给别人了,你也没办法控制别人说你不许拆开我的东西看里面的电路是怎么样的。所以Jlink就被破解了,破解之后的Jlink很便宜,网上五六十块钱就能买到一个能用的Jlink。 除了商业版的Jlink和H—JTAG,网上还有一些电子爱好者,他们参照开源软件的模式,设计了开源硬件,比如arduino。还有人制作了开源版本的JTAG仿真器——OpenJTAG。而一些芯片的开发商不像那些软件厂商,会给软件做很多的限制,他们对于开源硬件还是比较开明的,所以他们也支持了一些开源硬件。比如TI公司的MSP430 LaunchPad、ST公司的STM Discovery 等等板子。还有飞思卡尔公司的USBDM和OSJTAG。他们把这些硬件的原理图、PCB还有固件都放在了网络上供人自由下载和制作,你也可以根据他的资料进行改进。这样能使大家对于他们家的芯片有更多的了解,所以,他们也乐于开源一些评估板。 今天我要说的是几种JTAG仿真器的引脚定义,首先我看看比较常见的JTAG 20-Pin的引脚接口如下:

兼容JTAG标准接口 目标板具备JTAG标准接口,使用引出的10PIN连接线直接连接目标板即可。 下面是接口图: JTAG接口 说明:JTAG接口兼容ATMEL指定的JTAG标准接口,但不输出JTAG 的PIN2 “GND”,它对应ISP的PIN2为“VCC”。这样,若您的目标板采用指定的标准接口依然可以正常连接,但改进后,带来以下优点:JTAG错插入MCU的ISP接口,不会导致烧器件(需要目标板的JTAG、ISP接口做相关处理)。 AVR单片机JTAG接口的使用方法 作者:pc63 来源:单片机学习网字体:大中小在百度搜索相关 内容 编辑导读:AVR单片机的RC5和RC6算法比较与改进|AVR单片机读写EEPROM子程序|SD卡读写子程序|ATmega128实现一个工业设备的主控制板|数字温温度记录仪中的USB主机设计|HT1621驱动程序-AVR|

MSP4000型处理器在软交换终端设备中的应用|AVR c语言优秀编程风格|LM73测温度芯片的完整程序|12864(ICCAVR程序)| 正文: JTAG接口de使用方法: AVRdeJTAG 仿真器特别好用,在此特别推荐,它可以对所有含JTAG接口demega系列进行下载和软件硬件仿真。 刚开始使用AVR JTAG仿真器时,不shi很清楚它de使用方法。看完AVR JTAG仿真器de英文说明和中文说明,也不很明确它de具体使用。经过自己de摸索,才清楚如何使用这种仿真器。其实这种仿真器de使用方法很简单,就shi说明太罗索,让人越搞越糊涂。不过,使用这种仿真器,确实方便了很多,可实现硬件仿真与软件仿真,步调程序,发现程序漏洞,shi较好de辅助调试工具。 下面shi摸索出来de较简明de使用方法: (1) AVR JTAGde使用环境shi:AVR Studio 4.07以上版本,9-15 DC电源,PC与RS232口。 (2)安装AVR Studio:在安装AVRStudio时将随机提供de光盘放入CD-ROM中,选取avrstuio4。07目录中desetup.Exe文件,按照安装向导提示de步骤进行即可。 (3)在启动AVR Studio之前,把JTAGICE连接在上位PC和目标板之间,确保AVR Studio可以完成自动侦测连接情况。 (4)仿真器与上位机de连接,将随机带de“串行通讯电缆”一头与仿真器de“串行通讯口”相接,另一头与计算机任意串口相接。

我的JLINK终于用上了,哈哈,好开心,终于不用考虑是不是要借用别人的PC 机了,昨天到城隍庙电子市场忙活了一下午,终于算是满载而归,呵呵,好了,下面说一下接法,其实根本不需要什么转接板什么的,直接把相应的几根线对接就可以用了,所以要参考电路图,上面为TQ2440开发板的JTAG电路图,下面为JLINK的20针电路图,下面的JLINKV7电路图是标准接口,网上到处都能找到 10针JTAG针序20针JTAG针序信号 1,21VTref -2NC 33nTRST -4GND 55TDI -6GND 77TMS 88GND 99TCK 1010GND -11RTCK -12GND 613TDO -14GND 415RESET -16GND -17DBGRQ -18GND

-195V-Supply -20GND 实际上只需要接4跟线,4号是自连回路,不需要接,1,2接的都是1管脚,而8,10接的是GND,也可以不接 ARM系统的JTAG接口的设计不当往往使硬件系统无法调试,所以在设计ARM系统前要先熟悉ARM系统的JTAG接口的定义和常见问题。 1.ARM系统的JTAG接口是如何定义的?每个PIN又是如何连接的? 下图是JTAG接口的信号排列示意: 接口是一个20脚的IDC插座。下表给出了具体的信号说明: 表 1 JTAG引脚说明 序号信号名方向说明 1 Vref Input 接口电平参考电压,通常可直接接电源 2 Vsupply Input 电源 3 nTRST Output (可选项) JTAG复位。在目标端应加适当的上拉电阻以防止误触发。 4 GND -- 接地 5 TDI Output Test Data In from Dragon-ICE to target. 6 GND -- 接地 7 TMS Output Test Mode Select 8 GND -- 接地 9 TCK Output Test Clock output from Dragon-ICE to the target

JTAG(Joint Test Action Group,联合测试行动小组)是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试,JTAG技术是一种嵌入式调试技术,它在芯片内部封装了专门的测试电路TAP(Test Access Port,测试访问口),通过专用的JTAG测试工具对内部节点进行测试。 目前大多数比较复杂的器件都支持JTAG协议,如ARM、DSP、FPGA器件等。标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为测试模式选择、测试时钟、测试数据输入和测试数据输出。 JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试。JTAG接口还常用于实现ISP(In-System Programmable在系统编程)功能,如对FLASH器件进行编程等。 通过JTAG接口,可对芯片内部的所有部件进行访问,因而是开发调试嵌入式系统的一种简洁高效的手段。目前JTAG接口的连接有两种标准,即14针接口和20针接口,其定义分别如下所示。 14针JTAG接口定义: 14针JTAG接口定义引脚名称描述 1、13VCC接电源 2、4、6、8、10、14GND接地 3nTRST测试系统复位信号 5TDI测试数据串行输入 7TMS测试模式选择 9TCK测试时钟

11TDO测试数据串行输出 12NC未连接 20针JTAG接口定义引脚名称描述 1VTref目标板参考电压,接电源 2VCC接电源 3nTRST测试系统复位信号 4、6、8、10、12、14、16、18、20GND接地 5TDI测试数据串行输入 7TMS测试模式选择 9TCK测试时钟 11RTCK测试时钟返回信号 13TDO测试数据串行输出 15nRESET目标系统复位信号 17、19NC未连接 下面以S3C4510B开发板为例说明JTAG接口: 在保证电源电路、晶振电路和复位电路正常工作的前提下,可通过JTAG接口调试S3C4510B,在系统上电前,首先应检测JTAG接口的TMS、TCK、TDI、TDO信号是否已与S3C4510B 的对应引脚相连,其次应检测S3C4510B的nEWAIT引脚(Pin71)是否已上拉,ExtMREQ 引脚(Pin108)是否已下拉,对这两只引脚的处理应注意,作者遇到多起S3C4510B不能正常工作或无法与JTAG接口通信,均与没有正确处理这两只引脚有关。 给系统上电后,可通过示波器查看S3C4510B对应引脚的输出波形,判断是否已正常工作,若S3C4510B已正常工作,在使能片内PLL电路的情况下,SDCLK/MCLKO引脚(Pin77)应输出频率为50MHz的波形,同时,MDC引脚(Pin50)和其他一些引脚也应有波形输出。

Wiggler JTAG 之 H-JTAG 快速燒錄技巧 實驗環境:PC + H-JTAG Ver 0.6 + Wiggler JTAG + ESD44B0_B ARM7 開發平台 H-JTAG 是一套非常好用的東西,在最新的 0.6 版之下,更是提供了完整的 Nor Flash 燒錄功能,以下針對筆者所使用的 ARM7 開發平台 ESD44B0_B 提供一個非常容易使用的燒錄技巧。 首先提供一個 H-Flasher 快速設定的組態檔: https://www.doczj.com/doc/d910847410.html,/download/H-JTAG_ESD44B0_B(AT49BV162A)_CFG.hfc 其H-Flasher組態檔是一個文字檔內容如下: FLASH SECTION: ATMEL2 AT49BV162A MEMORY SECTION: 16 0x0000000 0xC000000 XTAL SECTION: NULL SCRIPT SECTION: Setmem+32-Bit+0x01E0000C+0x07FFFFFF Setmem+32-Bit+0x01D80000+0x58061 Setmem+32-Bit+0x01C80000+0x11111112 Setmem+32-Bit+0x01C80004+0x600 Setmem+32-Bit+0x01C80008+0x7FFC Setmem+32-Bit+0x01C8001C+0x18001 Setmem+32-Bit+0x01C80020+0x18001 Setmem+32-Bit+0x01C80024+0x820591 Setmem+32-Bit+0x01C80028+0x10 Setmem+32-Bit+0x01C8002C+0x20 Setmem+32-Bit+0x01C80030+0x20

Test Action Group,联合测试行动小组)是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试,JTAG技术是一种嵌入式调试技术,它在芯片内部封装了专门的测试电路TAP(Test Access Port,测试访问口),通过专用的JTAG测试工具对内部节点进行测试。 目前大多数比较复杂的器件都支持JTAG协议,如ARM、DSP、FPGA器件等。标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为测试模式选择、测试时钟、测试数据输入和测试数据输出。 JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试。JTAG接口还常用于实现ISP(In-System Programmable在系统编程)功能,如对FLASH器件进行编程等。 通过JTAG接口,可对芯片内部的所有部件进行访问,因而是开发调试嵌入式系统的一种简洁高效的手段。目前JTAG接口的连接有两种标准,即14针接口和20针接口,其定义分别如下所示。 14针JTAG接口定义: 14针JTAG接口定义引脚名称描述 1、13VCC接电源 2、4、6、8、10、14GND接地 3nTRST测试系统复位信号 5TDI测试数据串行输入 7TMS测试模式选择 9TCK测试时钟

TDO测试数据串行输出 12NC未连接 20针JTAG接口定义引脚名称描述 1VTref目标板参考电压,接电源 2VCC接电源 3nTRST测试系统复位信号 4、6、8、10、12、14、16、18、20GND接地 5TDI测试数据串行输入 7TMS测试模式选择 9TCK测试时钟 11RTCK测试时钟返回信号 13TDO测试数据串行输出 15nRESET目标系统复位信号 17、19NC未连接 下面以S3C4510B开发板为例说明JTAG接口: 在保证电源电路、晶振电路和复位电路正常工作的前提下,可通过JTAG接口调试S3C4510B,在系统上电前,首先应检测JTAG接口的TMS、TCK、TDI、TDO信号是否已与S3C4510B 的对应引脚相连,其次应检测S3C4510B的nEWAIT引脚(Pin71)是否已上拉,ExtMREQ 引脚(Pin108)是否已下拉,对这两只引脚的处理应注意,作者遇到多起S3C4510B不能正常工作或无法与JTAG接口通信,均与没有正确处理这两只引脚有关。 给系统上电后,可通过示波器查看S3C4510B对应引脚的输出波形,判断是否已正常工作,若S3C4510B已正常工作,在使能片内PLL电路的情况下,SDCLK/MCLKO引脚(Pin77)应输出频率为50MHz的波形,同时,MDC引脚(Pin50)和其他一些引脚也应有波形输出。

JTAG功能说明以及故障分析 提示:在进行JTAG测试之前,确保每块板卡在上电前已经完成短路测试,并且上电后测量每点电压正常。 1 Infrastucture JTAG链测试 Infrastructure测试主要是由三部分组成的,Capture, Identification,以及Trst功能测试,该测试主要是测试芯片的JTAG的TAP控制器基本功能是否正常,如果该项测试通过,可以认为芯片的供电基本正常,JTAG控制器相关的五个管脚焊接正常,芯片JTAG控制器工作正常。可以支持下一步的JTAG测试.(注释: 上电最好等待1秒以后再进行JTAG测试,等待芯片上电自身初始化结束以后,否则Infrastucture 测试可能会出现问题)。 如果该项目的测试出现问题,可以首先关注供电是否正常,确保每个工作点的电压都正常。其次是JTAG的接插件焊接是否正常,焊接的是否平整,然后考虑提供给芯片的几个基本信号是否有,TMS,TCK,TDO,TDI,TRST这些信号是否都有(示波器测量),以前出现过很多上拉电阻短路的情况,这个需要注意。测量的时候注意测量244驱动器的前后是否都有,驱动器异常的可能性还是很高的。注意,FPGA和EPLD这些可编程逻辑器件不需要TRST信号。在分析问题的时候,可以从Infrastructure的第一项开始考虑,capture测试不需要TDI信号输入给芯片,只需要TMS信号和TCK信号就可以有TDO

输出,便于分析和解决问题。最后去考虑芯片的焊接是否正常。对于某些芯片infra不过,还需要考虑是否reset信号常低输入给芯片,导致其工作不正常。 2 Interconnection连接测试 这个测试主要是测试在支持JTAG功能的芯片之间的连接是否正常以及芯片外置的上拉和下拉电阻配置是否正常。各芯片设置在JTAG功能的EXTEST模式。在Infrastructure测试通过的基础上才能进行该项测试。(注意,在测试之前,确保各卡之间的接插件连接到位,而且供电正常) 如果该项目的测试出现问题,很可能是芯片的焊接问题,也可能是串联在电路里面的串联电阻断路,虚焊,现在维修下来的情况,电阻没有焊好的概率比较大。还有一种可能性,就是上下拉电阻和电源地短路,这个问题也算比较常见的,需要加以注意。可以在分析报告中找到是哪个netlist出错,进而进一步定位该netlist是连接哪几个芯片的哪几个管脚,经过那些电阻,然后对这两个芯片进行补焊处理。 3 SDRAM 测试 该项测试仅仅完成在CPU和SDRAM芯片之间连接测试,因为SDRAM本身不支持JTAG协议,我们只能用读写不同地址的不同数据线来完成对SDRAM的扫描工作。该测试仅仅在使用到SDRAM的时

JTAG的引脚定义与各种JTAG的引脚序号与引脚名的对应关系 JTAG有10pin的、14pin的和20pin的,尽管引脚数和引脚的排列顺序不同,但是其中有一些引脚是一样的,各个引脚的定义如下。 一、引脚定义 ?? Test Clock Input (TCK) -----强制要求1 TCK在IEEE 1149.1标准里是强制要求的。TCK为TAP的操作提供了一个独立的、基本的时钟信号,TAP的所有操作都是通过这个时钟信号来驱动的。 ?? Test Mode Selection Input (TMS) -----强制要求2 TMS信号在TCK的上升沿有效。TMS在IEEE 1149.1标准里是强制要求的。TMS信号用来控制TAP状态机的转换。通过TMS信号,可以控制TAP在不同的状态间相互转换。 ?? Test Data Input (TDI) -----强制要求3 TDI在IEEE 1149.1标准里是强制要求的。TDI是数据输入的接口。所有要输入到特定寄存器的数据都是通过TDI接口一位一位串行输入的(由TCK驱动)。 ?? Test Data Output (TDO) -----强制要求4 TDO在IEEE 1149.1标准里是强制要求的。TDO是数据输出的接口。所有要从特定的寄存器中输出的数据都是通过TDO接口一位一位串行输出的(由TCK驱动)。 ?? Test Reset Input (TRST) ----可选项1 这个信号接口在IEEE 1149.1标准里是可选的,并不是强制要求的。TRST 可以用来对TAP Controller进行复位(初始化)。因为通过TMS也可以对TAP Controll进行复位(初始化)。所以有四线JTAG与五线JTAG之分。 ?? (VTREF) -----强制要求5 接口信号电平参考电压一般直接连接Vsupply。这个可以用来确定ARM的JTAG接口使用的逻辑电平(比如3.3V还是5.0V?) ?? Return Test Clock ( RTCK) ----可选项2 可选项,由目标端反馈给仿真器的时钟信号,用来同步TCK信号的产生,不使用时直接接地。 ?? System Reset ( nSRST)----可选项3