ALLEGRO约束规则设置介绍

目录:

第一部分:差分对的约束设置 (1)

第二部分:非差分信号约束设置 (8)

第三部分:区域约束设置 (11)

第四部分:XNet等长设置 (12)

本文所有操作与设置均在Allegro PCB editor 15.5环境中进行。

第一部分:差分对的约束设置

下面我们将通过对LVDS差分对信号的约束设置分步骤的讲解各个设置过程,其约束条件如

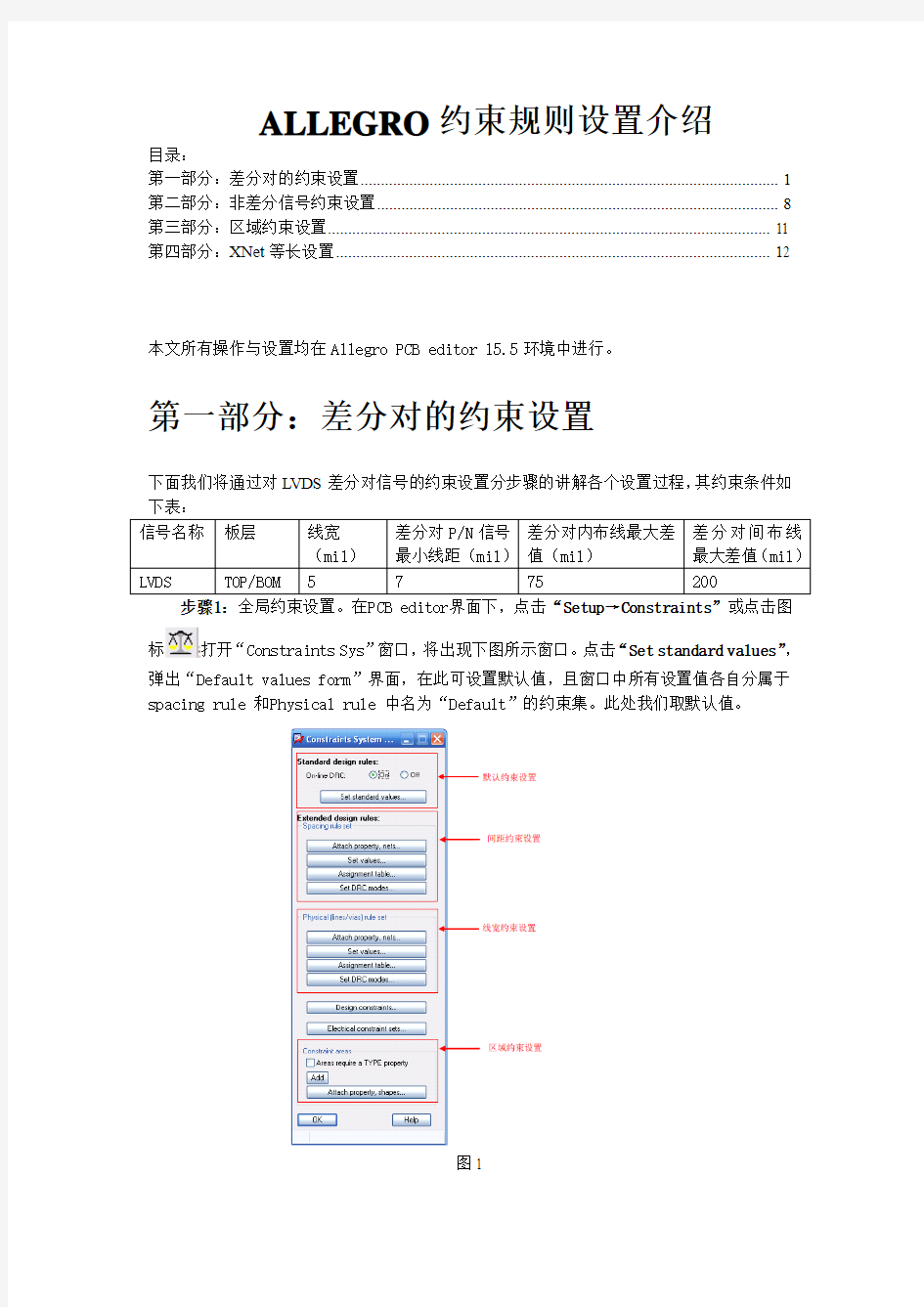

步骤1:全局约束设置。在PCB editor界面下,点击“Setup→Constraints”或点击图

标打开“Constraints Sys”窗口,将出现下图所示窗口。点击“Set standard values”,弹出“Default values form”界面,在此可设置默认值,且窗口中所有设置值各自分属于spacing rule 和Physical rule 中名为“Default”的约束集。此处我们取默认值。

图1

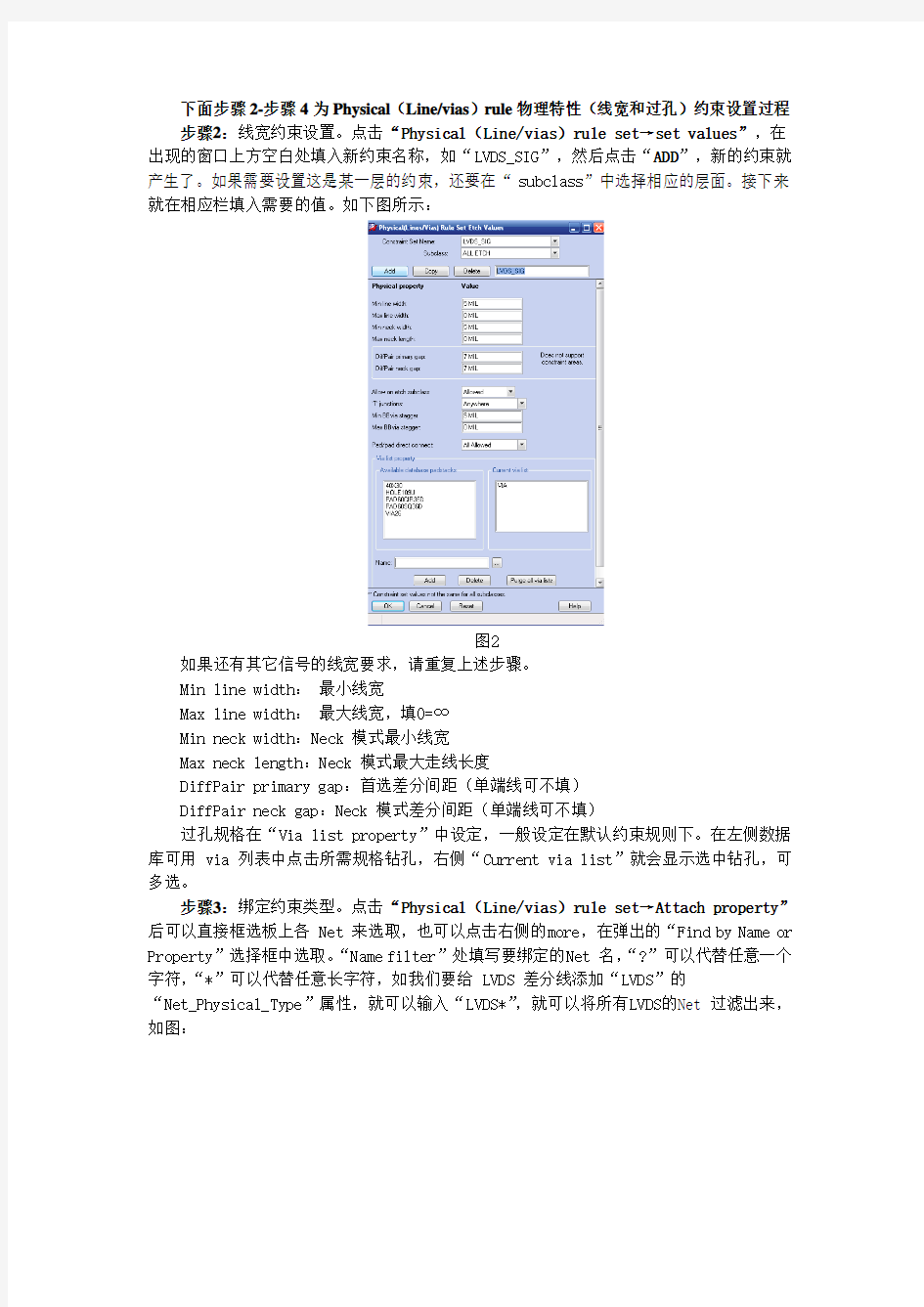

下面步骤2-步骤4为Physical(Line/vias)rule物理特性(线宽和过孔)约束设置过程步骤2:线宽约束设置。点击“Physical(Line/vias)rule set→set values”,在出现的窗口上方空白处填入新约束名称,如“LVDS_SIG”,然后点击“ADD”,新的约束就产生了。如果需要设置这是某一层的约束,还要在“subclass”中选择相应的层面。接下来就在相应栏填入需要的值。如下图所示:

图2

如果还有其它信号的线宽要求,请重复上述步骤。

Min line width:最小线宽

Max line width:最大线宽,填0=∞

Min neck width:Neck 模式最小线宽

Max neck length:Neck 模式最大走线长度

DiffPair primary gap:首选差分间距(单端线可不填)

DiffPair neck gap:Neck 模式差分间距(单端线可不填)

过孔规格在“Via list property”中设定,一般设定在默认约束规则下。在左侧数据库可用 via 列表中点击所需规格钻孔,右侧“Current via list”就会显示选中钻孔,可多选。

步骤3:绑定约束类型。点击“Physical(Line/vias)rule set→Attach property”后可以直接框选板上各 Net 来选取,也可以点击右侧的more,在弹出的“Find by Name or Property”选择框中选取。“Name filter”处填写要绑定的Net 名,“?”可以代替任意一个字符,“*”可以代替任意长字符,如我们要给 LVDS 差分线添加“LVDS”的

“Net_Physical_Type”属性,就可以输入“LVDS*”,就可以将所有LVDS的Net 过滤出来,如图:

图3

点击“All”选定net,点击“Apply”,出现“Edit Property”窗后,在左侧下拉选项中选择约束类型“Net_Physical_Type”,然后在右侧相应内容后填入约束名称“LVDS”,点击“Apply”,这样就完成了约束类型绑定,如图:

图4

图5

步骤4:约束规则分配。点击“Physical(Line/vias)rule set→Assignment table”出现约束规则分配列表,分配不同情形下适用怎样的规则。Physical rule的约束分配列表如下:

图6

第一列“Net Physical Property”:在步骤3“Attach property”中绑定的约束类型第二列“Area Property ”:约束绑定区域,在第三部分介绍。

第三列“Physical Constraint Set”:在步骤2“Set values”中设置的约束特征值关于约束绑定区域我们以后再说,那么这三行的意思就是:

绑定约束“NO_Type”的信号在“NO_Type”区域内应用Physical 约束“DEFAULT”

绑定约束“LVDS”的信号在“NO_Type”区域内应用Physical 约束“LVDS_SIG”

下面步骤5-步骤7为“Spacing rule”间距约束设置过程

步骤5:点击“Spacing rule→Set values”设置约束特征值。由于LVDS差分对要求线间距为7mil,所以我们在窗口上方空白处填入新约束名称“SPACE_7”,然后点击“ADD”,新的约束就产生了,在对应的各个距离内填上相应的数值即可。如下图所示:

图7

步骤6:点击“Spacing rule →Attach property”绑定约束类型。Spacing rule 的绑定约束类型的操作和Physical rule 设置基本相同。选取 LVDS 信号绑定约束类型“LVDS_SPACE”,如图:

图8

图9

步骤7:点击“Spacing rule →Assignment table”进行约束规则分配。

Spacing rule 的约束分配列表如下:

图10

上图中三行的意思是(关于约束绑定区域第三部分会有介绍):

绑定Spacing 约束“No_Type”的信号和绑定Spacing 约束“No_Type”的信号在“No_Type”区域内应用Spacing 约束“DEFAULT”

绑定Spacing 约束“LVDS_SPACE”的信号和绑定Spacing 约束“No_Type”的信号在“No_Type”区域内应用Spacing 约束“SPACE_7”

绑定Spacing 约束“LVDS_SPACE”的信号和绑定Spacing 约束“LVDS_SPACE”的信号在“No_Type”区域内应用Spacing约束“SPACE_7”

下面步骤8到步骤10为差分对等长约束设置过程

步骤8:差分对配对。点击“setup→electrical constraint spreadsheet…”或点击,打开Allegro constraint manager 窗口。选择“net →Routing→Differential Pair”,选中LVDS_A0_P和LVDS_A0_N右击,在弹出的菜单中选择“create→differential pair”,如下图所示。点击后会弹出“create differential pair”界面,在此界面就可以依次对所有差分对配对。

图11

图12

步骤9:建立ECSet。在左边工作窗体选择区选择“Electrical Constraint Set→Routing →Differential Pair”。在你的brd文件名(此处为unnamed)上右击→Create→Electrical CSet,在弹出的对话框中输入约束名,这里起名为“LVDS_LENGTH”,并在图示位置填入允许的长度差值75mil。

图13

如果需要对LVDS信号布线总长度设置约束,则在左边工作窗体选择区选择“Electrical Constraint Set→Routing→Total Etch Length”。在此我们可以看到刚才新建的约束“LVDS_LENGTH”,在其后面的“Minimum Etch Length”和“Maximum Etch Length”中添加布线长度的最小和最大值,如图。

图14

步骤10:为差分对绑定ECSet。打开“Net → Routing → Differential Pair”,在右侧可以看到已经配对的差分线,在“Electrical Cset References…”下单击,在弹出的对话框中选择刚才设置好的约束“LVDS_LENGTH”。也可以一次填多对,按住左键拖曳选择多个,右键菜单选“Change…”。这样就给差分线添加了长度约束“LVDS_LENGTH”。如图:

图15

同理,在“Net → Routing → Total Etch Length → Electrical Cset References…”下添加“LVDS_LENGTH”约束。

设置好后就可以布线了。

在最上面的字段名称上及项目名、Net 名上,按下鼠标右键可以展开下拉菜单,其中的“Sort”可以将对象重新排序,“Analyze”可以立即执行分析,分析后各种颜色的图示如下,也就是常说的红绿灯。

Pass –分析的结果符合设定值。

Fail –分析的结果不符合设定值。

Analysis error –无法执行分析。

Directly set –字段的设定值是由使用者直接输入的

图16

提示:没有红绿灯的,请打开Setup→User Preferences…,展开左边Etch项,右边

allegro_dynam_timing 选择on 即可。下面的一项allegro_dynam_timing_fixedpos是设置

红绿灯位置锁定还是跟着光标跑的。设置好后,还要在“constraint manager”窗口中,点

击“anslysis→analysis modes”,在弹出的界面中打开相应的 DRC 检查项即可,如下图

图17

第二部分:非差分信号约束设置

非差分信号的约束设置与差分信号的约束设置大致过程相同。

步骤1:全局约束设置。设置过程同“第一部分:差分对约束设置/步骤1”,取默认值即可。

下面步骤2-步骤4为Physical(Line/vias)rule物理特性(线宽和过孔)约束设置过程步骤2:线宽约束设置。设置过程同“第一部分:差分对约束设置/步骤2”。此处线宽约束命名为“VGA_SIG”。如下图所示:

图18

步骤3:绑定约束类型。设置过程同“第一部分:差分对约束设置/步骤3”。此处

“Net_Physical_Type”命名为“VGA”。如图:

图19

步骤4:约束规则分配。设置过程同“第一部分:差分对约束设置/步骤4”。

图20

下面步骤5-步骤7为“Spacing rule”间距约束设置过程

步骤5:设置约束特征值。设置过程同“第一部分:差分对约束设置/步骤5”。VGA 信号间距要求20mil,因此此处约束命名为“SPACE_20”。如下图所示:

图21

步骤6:绑定约束类型。设置过程同“第一部分:差分对约束设置/步骤6”。选取 VGA 信号绑定约束类型“VGA_SPACE”,如图:

图22

步骤7:约束规则分配。设置过程同“第一部分:差分对约束设置/步骤7”。

图23

步骤8:等长约束设置。点击“setup→electrical constraint spreadsheet…”或点击,打开Allegro constraint manager 窗口。在左边工作窗体选择区选择“NET→Routing→Relative PropagationDelay”。在主窗体利用Ctrl、Shift 键,将 VGA_BLUE/VGA_GREEN/VGA_RED三根线全部选定,“右击→Create→Match”,在弹出的对话框中填入组名“VGA_RGB”。这样就将这 3 根线加入到了一个group 中。在Relative Delay下的Delte:Toleranc处填入长度约束200mil。如图,

图24

填入时可以直接输入数字,不用输入单位。可以在“VGA_RED”对应的输入框“右击→set as target”指定其中某根net为target。如果需要对VGA的信号进行布线总长度约束设置,则在左边工作窗体选择区选择“Electrical Constraint Set→Routing→Total Etch Length”。

在此新建约束“VGA_LENGTH”(新建过程参考“第一部分:差分线约束设置/步骤9”),在其后面的“Minimum Etch Length”和“Maximum Etch Length”中添加布线长度的最小和最大值。

设定完以上约束就可以绕等长了,在右侧的Length上右击→Analyze,可以看到每根Net 的长度,当每个字段都以绿色显示时,就说明它们满足设置的长度约束了,如图:

图25

第三部分:区域约束设置

在PCB的布线过程中有些区域过于严格的约束是不可能达到的,比如在第二部分中的VGA 信号,在连接器管脚上是不可能达到20mil间距的。这时一个解决办法就是把这些地方划为一个Area,然后给它加上Net_Physical_Type和Net_Spacing_Type属性。针对这些Area ,设定合适的、比较宽松的约束值。如果不设置,也就是没有区域约束的地方,就是“No-Type”。

具体做法是在第一和第二部分的约束设置后,布线开始前,增加以下步骤:

1、参考“第一部分/步骤2和步骤5”在“Set values”中各添加Physical 和Spacing 的约束值“VGA_CONN_AREA”,填上相对比较宽松的、合理的值。

2、在“Constraint areas”中选Add,(注意这时的绘图层为constraint area),选择好画shape 的工具,在工作区绘制shape。如图:

图26

3、点击“Attach property,shapes”选刚才画的shape,绑定约束Net_Physical_Type 和Net_Spacing_Type。绑定后shape属性如图:

图27

图28

增加上述约束区域后,我们就可以开始布线了。在区域之外我们执行的是前面设置的约束条件VGA_SIG和VGA_SPACE,当进入此区域后,则执行VGA_CONN_AREA的约束条件。

第四部分:XNet等长设置

我们把连续的几段由无源元件(如电阻,电容或电感)连接的net 合称为一段Xnet。前面说的方法只能对Net 设置等长,既差分对的每根线、group中的每根线,操作的对象都是Net。而下面这种情况中要求Net1A + Net1B = Net2A + Net2B,那我们如何设置呢?

图29

步骤如下:

1、在Allegro PCB editor中点击菜单“Analyze→SI/EMI Sim→Model…”,在弹出来的提示界面中直接点击“Yes”即可,然后出现下面的Model设置窗体:

图30

2、直接在“DevType Value/Refdes”中选择要设定Model 的器件或直接在板子上点选要设置Model的器件。如果所选器件是电阻、电容、电感之类的双引脚元件,那么直接点“Auto Setup”,出现下图所示内容,然后点击“OK”即可。如果是多引脚器件则请参考相应工具

书,此处暂不做介绍。

图31

3、点击“setup/electrical constraint spreadsheet…”或点击,进入约束管理器Constraint Manager 的“Net→Routing→Relative Propagation Delay”,在右边就会显示整块板子所有的Net 或Xnet。建立需要等长的Pin Pair,在需要建立Pin Pair 的Xnet 上右击→Create

→Pin Pair:

图32

4、选择起始Pin 和结束Pin:

图33

这一步的目的是指定一个XNet 等长时计算长度的起始Pin 和结束Pin。如上图中,SIG_A1长度值就是J2.11-R1.1和R1.2-J3.11的长度和。

设好Pin Pair 之后,就可以用设置一般的Net 等长的方法来设置XNet 的等长,不同的只是将XNet 的Pin Pair 选定添加到一个等长组里。如图:

图34

图35

5、在新建组“SIG_XNET”的Relative Delay/Delte:Toleranc处填入长度约束20mil。如下图:

图36

至此,XNET的约束就设置好了,下面可以布线了。

差分对的约束设置 第一步,差分对的设置 差分对的设置有很多方法,下面介绍两种最常用的方法。 1.点击菜单Logic→Assign Differential Pair... 弹出以下对话框。 点击你想要创建差分对的Net1和Net2,填入差分的名字,点击Add后就成功创建了差分对。 点击Auto Generate按钮后,弹出以下对话框:

在第一个输入框填入Net的主要名字后,在下面的框中填入差分线的标志如N,P。点击Generate即可自动产生差分对。 2.在约束管理器中设置差分对。 在DSN上点击右键,在菜单中选择Create→Differential Pair。即可弹出下面的对话框。

和上一种方法的设置差不多,这里就不再叙述了。 第二步差分对约束规则的设置 差分对各项约束可以在约束管理器中的 Electric→Net→routing→Differential Pair中直接在各差分对上填入各项约束数值就可生效,但更好的方法是创建约束规则后赋给各个差分对。 在DSN上点击右键,在菜单中选择Create→Electrical CSet后,弹出下面的对话框; 输入规则名后点Ok,在Electric→constraimt set→outing→Differential Pair中可以看到新规则。 在表格中输入各项数值即可完成新规则的设置。如图所示 差分对约束参数主要有以下几个:

1coupling paramaters 主要包括了 Primary Gap 差分对最优先线间距(边到边间距)。 Primary Width 差分对最优先线宽。 Neck Gap 差分对Neck模式下的线间距(边到边间距),用于差分对走线在布线密集区域时切换到Neck值。 Neck Width差分对Neck模式下的线宽,用于差分对走线在布线密集区域时切换到Neck值。如图所示 设置数值时在表格中右键菜单中选择change,会出现以下各层数值表格,可以在每一层上设置不同的数值。 需要注意的是在物理(physical)约束中同样可以设置差分规则,但是电气规则约束在布线时更优先,同时电气规则可以设置更多的约束,推荐在电气规则中设置差分走线的约束。 2 Min Line Specing 差分对最小间距,一定要小于或等于"Primary gap"与(-)tolerance的数值,并且也要小于或等于"Neck gap"与(-)tolerance的数值。对于不符合约束的差分对,会显示“DS”的DRC错误提示。

Allegro? Constraint Manager User Guide 1 Welcome to Constraint Manager Topics in this chapter include The Allegro? Constraint Manager Information Set on page 12 What is Allegro? Constraint Manager?on page 13 Accessing Constraint Manager on page 17 Domains, Workbooks, Worksheets, and Cells on page 21 Constraint Manager’s User Interface Controls on page 33 Enhancements Done in 16.3 The Allegro? Constraint Manager Information Set The Allegro? Constraint Manager information set consists of online books accessible from Cadence Help in both HTML and PDF formats. All documentation is accessible from Constraint Manager’s help menu. Refer to . . .for this level of information Allegro?Constraint Manager User Guide (this book) This book is for users who want to know how to use Constraint Manager in the design flow. This book complements the information in the Allegro? Constraint Manager Reference.

在PCB设计过程中,需要通过设置各种规则,以满足各种信号的阻抗。比如,常用的高速差分线,我们常控的100欧姆,那么到底走多宽的线以及差分线之间的间距到底是多少,才能满足设计要求的100欧姆阻抗呢?本文就对Allegro 种的基本规则设置做一个详细的讲解。 注:本文是基于Allegro 15 版本的。对于16版本不适用。 首先需要打开规则管理器,可通过以下三种方式打开: 一、点击工具栏上的图标。 二、点击菜单Setup->Constraints 三、在命令栏内输入"cns" 并回车 打开的规则管理器如下:

在最上面一栏有一个On-line DRC,这是对画板过程中不停检测是否违反规则,并可产生DRC。一般我们都默认开启。可以实时查看产生的DRC 错误,并加以修正。 接下来的Spacing rule set 是对走线的线间距设置。比如对于时钟线、复位线、及高速查分线。我们可以再这里面加一规则,使其离其它信号线尽可能的远。 Physical(lines/vias)rule set 是针对各种物理规则设置,比如线宽,不同信号线的过孔等。例如我们可通过电源网络的设置,使其默认线宽比普通信号走线更粗,已满足走线的载流能力。 现针对一个时钟及电源,分别设置间距规则和物理规则。 首先筛选网络,对于需要设置线间距规则的网络赋上Net_Spacing_Type 属性、而对于需要设置线宽规则的网络赋上Net_Physical_type 。而对于即要线间距和线宽规则约束的

网络,可将Net_Spacing_Type 及Net_Physical_type 属性同时赋上。 本例针对的时钟网络,只需要对其赋上Net_Spacing_Type ,方法如下: 点击菜单Edit->Properties 然后在右侧Find 一栏中选择Nets 。如下图所示: 如果你知道PCB上网络名,那么你可以直接在PCB上选择一个网络。假如你并不知道到底哪个网络是时钟,那么你可以选择Find下面的More

Allegro 16.3约束规则设置 约束管理器是一个交叉的平台,以工作簿和工作表的形式在 Cadence PCB设计流程中用于管理所有工具的高速电子约束。可以使用约束管理器和SigXplorer Expert 开发电路的拓扑并得出电子约束,可以包含定制约束、定制测量和定制激励。 所谓约束就是用户定义的限制条件,当在板上走线和放置元件时会遵守这些约束。电子约束(ECSets)就是限制PCB 上与电行为有关的对象,比如可以设置某个网络最大传输延迟为2ns。 以下图为一约束设置窗口。 一、说明 先解释一下约束的类型以及约束中用到的简写名词,如下图所示:

1、NCIs(NET CLASS) 由众多nets或者buses、differential pairs、Xnet所组成的类,可对其赋予相似的约束。如下图所示。 2、NCC(Net Class-Class) 一般用在约束组与组之间的间距的时候使用,如下图。 3、DPr(Differential Pairs)差分对 一组差分对一般由两条Xnet或者net以差分走线的方式组成,如下图。差分对的形成有两种方式:一是由模型指定的差分对,再者就是由用户自己定义的差分对。 ?模型定义的差分对:可以在器件信号模型中指定差分对,可以使用PCB Design,PCB SI,SigXplores 来将模型指定给相应的元件。 ?用户定义的差分对:可以在约束管理器中 Net 一级的对象中创建差分对,可以灵活的更改差分对命名和更改差分对成员,但是没有模型指定差分对的精确性。 以下是设置差分对规则时,需要赋予约束的项。

针对以上约束中用到的一些约束点进行解释说明:

---------------------------------------------------------------范文最新推荐------------------------------------------------------ 约束理论的管理方法与作用 约束理论(TOC)是由以色列物理学家埃利?格特拉特(EliGoldratt)博士于20世纪80年代中期在他的最优生产技术(OPT)基础上创立和发展起来的。TOC在OPT的基础上已发展为:(1)使瓶颈产能最大化,从而使系统有效产出最大化的生产管理技术;(2)系统地解决问题的一套思维流程;(3)辨识系统核心问题并持续提升系统限制的管理哲学。TOC认为任何系统至少存在着一个约束,如果这个约束决定一个企业或组织达成目标的速率,则必须从克服该约束着手,才能以更快速的步伐在短时间内显著地提高系统的产出。TOC给出了管理改善的起点和路径,使得企业避免了不必要的弯路。因此,TOC对企业优化管理具有方法论上的意义。一、约束理论(TOC)(一)约束理论的基本原则(1)平衡物流,而不是平衡能力。所谓物流平衡就是使各个工序都与瓶颈机床同步,以求生产周期最短、在制品最少。(2)非瓶颈资源的利用程度不是由它们自己的潜力决定的,而是由系统的约束决定的。约束资源制约着系统的产出能力,而非约束资源的充分利用不仅不能提高有效产出,而且会使库存和运行费增加。(3)资源的“利用”和“活力”不是同义词。“利用”是指资源应该利用的程度,“活力”是指资源能够利用的程度。(4)瓶颈上一小时的损失,则是整个系统一个小时的损失。(5)非瓶颈获得的一个小时是毫无意义的。非瓶颈资源利用率的提高,可能会造成系统物流的不平衡或库存的增加,并不能提高系统的整体效率。(6)瓶颈控制了库存和产销率。(7)转运批量可以不等 1 / 9

Spacing规则(约束) Rex dlutarm@https://www.doczj.com/doc/dd8682664.html, 2009-07-02 Allegro 16.0以后版本的约束规则设置较之前有很大改变,对于用惯了15.x的人 来说,很多不习惯新的约束管理器。和在对待女人的态度上,恰相反。80后说90后脑残,15.7说16.2脑残,Xp说Vista脑残。Vista确实很脑残。新事物取代旧事物是自然界发展的客观规律。 说明: 1本文只介绍了Spacing约束的设置,因为Physical规则通常来说都设置的非常简单。掌握了Spacing规则Physical规则对你来说一定是小Case。另外,Physical 规则的设置也写的话,一定显得都是在重复Spacing的设置; 2文中所有的规则(约束),如不特殊说明默认情况下均指Spacing规则(约束);3对于Electrical的约束,是另一种约束,本文不作讨论。 约束的设置方式: 1直接的:Net中写数值, 2 间接的:创建Constraint Set,然后Assign给Net; 这两种都很常用,后者管理方便。在Physical和Spacing设置中用后者比较好,但是在Electrical中,我看到很多很多的人会混合使用。 使用第二种约束设置方式的约束设置步骤: 1约束的对象 2约束的内容 3给对象分配内容 1

这3个步骤默默的引导着所有间接约束的设置。基本约束 预备 先理解: Net class 2

Net class-class Region Region-class Region-class-class Bus …… 现在不理解,想跳过去。没关系,你早晚都要理解的。 最简单和稍微复杂一点的约束: 最简单的就是default的约束,稍微复杂一点的就是修改了一点默认的约束。 再复杂一些的约束: 你可能会想让不断变化的CLK(我们不考虑是不是差分)和其他的线离的远一些。 在Constraint Set中Create规则并设置规则的内容: Creat & Set之后 3

Allegro PCB设计中的约束管理 本章主要介绍一下约束管理器的使用,约束管理器贯穿于原理图设计、PCB 设计、仿真分析设计,这里主要讲述在PCB Editor中如何使用约束管理器来对信号进行约束设置。 一、约束管理器概述 约束管理器是贯穿于整个PCB设计平台的一个对信号约束的工具,在整个项目的开发过程中,起着桥梁的作用。我们可以在原理图设计阶段在约束管理器中设定约束来指导PCB设计;也可以在使用仿真分析工具仿真后,将仿真分析的拓扑添加到约束管理器中从而来驱动布局、布线。 约束管理器是以表格形式为基础的工作表形式,所以其操作简单、运用灵活。它将印制电路板所有的网名以表格形式显示,不仅使设计者对网名一目了然且更加方便地对信号设定不同的规则。对不同的规则如相对长度规则、总长度规则、曼哈顿长度规则等分了不同的栏显示以方便大家的规则设定。 二、约束管理器 1、约束管理器的启动 在Allegro PCB Design中,选择菜单命令Setup/Electrical Constraint Speadsheet或者单击Setup工具栏中的按钮,打开约束管理器,如图10_1所示。 10_1 2、约束管理器界面概述

1)菜单栏 约束管理器的菜单栏包括:File、Edit、Objects、Column、View、Analyze、Audit、Tools、Window及Help。 2)Electrical Constraint Set栏 此栏主要是对电气规则来设定约束,包括:Signal Intergrity(信号完整性设置规则)、Timing(时序规则设置)、Routing(布线设置)、All Constraint(所有的约束管理)。 3)Net栏 Net栏主要对指定的网络来设置不同的约束规则,包括Signal Intergrity(信号完整性设置规则)、Timing(时序规则设置)、Routing(布线设置)、Custom Measeurement(用户添加规则管理)、General Properties(通用属性设置)。 4)设计规则约束设置 包括:Electrical(电气规则)、Spacing(间距规则设置)、Physical(物理规则设置)、Design(设计规则设置)。 三、线的约束设置 约束管理器可以设定的规则很多,但是真正常用的是Net栏中Routing中的各项对布线的约束设置。包括:Wiring(线路设置)、Impedance(阻抗设置)、Min/Max Propagation Delays(最大或最小传输延时设置)、Total Etch Length(总长度设置)、Differential Pair(差分对的设置)和Relative Propagation Delay(相对传输延时设置)。 1、创建Bus 在设定约束的时候,可以对单独的网络进行设置,也可以对一个Bus进行设置。对于在原理图设计的时候没有设计总线形式的网络,也可以在约束管理器中创建一个Bus。方法如下:1、在约束管理器Net栏中选择Routing/Wiring,展开所有的网络列表;2、选中要创建Bus的网络名,单击鼠标右键,在弹出的菜单中选择Create/Bus,如图10_2所示;3、在弹出的对话框中输入创建的Bus名,如图10_3所示;4、点击“Ok”完成Bus的创建,此Bus会在约束管理器中即时显示。 注意:对一个Bus内的信号线,其布线拓扑应基本一致,否则,在设定约束后,布线的时候会引起匹配不当。

Cadence allegro菜单解释——file 已有 320 次阅读2009-8-16 19:17|个人分类:|关键词:Cadence allegro file 菜单解释 每一款软件几乎都有File菜单,接下来详细解释一下allegro与其他软件不同的菜单。 new 新建PCB文件,点new菜单进入对话框后,drawing type里面包含有9个选项,一般我们如果设计PCB就选择默认第一个board即可。 如果我们要建封装库选package symbol即可,其他7个选项一般很少用,大家可以理解字面意思就可以知道什么意思了。 open 打开你所要设计的 PCB文件,或者封装库文件。 recent designs 打开你所设计的PCB文件,一般是指近期所设计的或者打开过的PCB文件。 save 保存 save as 另存为,重命名。 import import 菜单包含许多项,下面详细解释一下我们经常用到的命令。 logic 导入网表,详细介绍在allegro基础教程连载已经有介绍,在此不再详细介绍。 artwork 导入从其他PCB文件导出的.art的文件。一般很少用词命令。 命令IPF和stream 很少用,略。 DXF 导入结构要素图或者其他DXF的文件。 导入方法如下: 点import/DXF后,在弹出的对话框选择,在DXF file里选择你要导入的DXF的路径,DXF units 选择MM,然后勾选use default text table和incremental addition,其他默认即可。再点edit/view layers弹出对话框,勾选select all,DXF layer filter 选择all,即为导入所有层的信息,然后在下面的class里选择board geometry,subclass选择assembly_notes,因为一般导入结构要素图都是导入这一层,然后点ok,进入了点import/DXF后弹出的对话框,然后点import即可将结构要素图导入。 IDF IFF Router PCAD 这四个命令也很少用,略。 PADS 一般建库的时候导入焊盘。 sub-drawing 命令功能非常强大,也是我们在PCB设计中经常用的命令,如果能够非常合理的应用sub-drawing命令会提高我们设计PCB的效率。

Allegro16.6约束规则设置详解 前言:本文主要讲解Allegro16.6约束管理器的使用,从基本约束规则到高级约束规则的设置。 目录: 一、基本约束规则设置 1、线间距设置 2、线宽设置 3、设置过孔 4、区域约束规则设置 5、设置阻抗 6、设置走线的长度范围 7、设置等长 7.1、不过电阻的NET等长 7.2、过电阻的XNET等长 7.3、T型等长 8、设置通用属性 9、差分规则设置 9.1、创建差分对 9.2、设置差分约束 10、Pin Delay

二、高级约束规则设置 11、单个网络长度约束 12、a+b类长度约束 13、a+b-c类长度约束 14、a+b-c在最大和最小传播延迟中的应用

1、线间距设置 (1)、设置默认间距规则 点击CM图标,如下图所示,打开约束管理器。 单击Spacing,再点击All Layers,如下图所示。右边有一个DEFAULT就是默认规则,我们可以修改其值。

按住Shift键,点击第一个和最后一个即可选中所示,然后输入一个值,这样就都修改了,如下图所示 (2)、定义特殊的间距约束 点选Default按鼠标右键,执行Create-Spacing CSet

加入新规则。取一个有意义点的名字,如下图所示,单击OK。 其值是从默认规则拷贝的,先修改其值。 按住Shift键选中所有,输入12,回车。 然后为所需要设置的网络分配规则 单击左边的Net-All Layers,在右边工作簿中,为GND网络设置12MIL_SPACE规则,在Referenced Spacing CSet下选中12MIL_SPACE,如下图所示

约束管理器分册 第一章约束管理器介绍 约束管理器是一个交叉的平台,以工作簿和工作表的形式在Cadence PCB设计流程中用于管理所有工具的高速电子约束。约束管理器让你定义、查看和校验从原理图到分析到PCB设计实现的设计流程中每一步的约束。可以使用约束管理器和SigXplorer Expert开发电路的拓扑并得出电子约束,可以包含定制约束、定制测量和定制激励。 本培训教材描述的主要是怎样在约束管理器中提取约束,并且约束如何与原理图和PCB的属性同步。本教材的内容是约束管理器、Concept HDL和PCB Design的紧密集成的集锦。 所谓约束就是用户定义的限制条件,当在板上走线和放置元件时会遵守这些约束。电子约束(ECSets)就是限制PCB上与电行为有关的对象,比如可以设置某个网络最大传输延迟为2ns。 教材主要内容如下: ?第1章~第7章主要关于原理图约束管理器使用: 在约束管理器中提取ECs(电子约束); 在原理图和约束管理器中执行ECO; 在Concept和PCB Design中传递ECs。 这部分面向Concept HDL的约束管理器的初学者,但是要熟悉Concept HDL 和PCB Design。此教材不讨论Concept HDL和PCB Design不同模式和属性的细节,但是会详细地讨论约束管理器过程。为了快速理解约束管理器的主要

特点,可以看看Concept HDL的多媒体教材。请见Help –Learning Concept HDL–Demos in Concept HDL。将练习文件project.zip解压缩到一个空的路径\design。确认设置环境变量CONCEPT_INST_DIR到Cadence 安装路径(一般安装时设置好了)。 第8章~第12章主要关于PCB约束管理器使用,但是省略了与原理图相同的部分。 本培训教材附两个练习文件:project.zip和golderboard.rar。 1.1 约束管理器简介 约束即用户定义的附加到网络或者管脚对上的要求,电子约束管理着网络和管脚对的行为。可以使用约束管理器来提取和管理电子约束。Cadence推荐使用约束管理器来提取约束,因为约束管理器有下列特性: 提供工作表为基础的用户接口,允许快速的提取、修改、删除约束。 支持语法检查 支持约束继承,高层的约束可以被继承,低层的约束可以覆盖高层约束。 可以定义电子约束集。 创建约束报告。 约束管理器在流程中的位置和作用请见下图:

前言:本文主要讲解Allegro16.6约束管理器的使用,从基本约束规则到高级约束规则的设置。 目录: 一、基本约束规则设置 1、线间距设置 2、线宽设置 3、设置过孔 4、区域约束规则设置 5、设置阻抗 6、设置走线的长度范围 置详解(图文并茂) 则设约束规.616o r g Alle (为了不侵犯别人的成果,所以在这里做了特殊说明,以示敬意)首先感谢詹书庭编写这篇文章,为我们学习交流Cadence allegro 苦用心! 俗话说的好,社会在发展,技术在进步,技术的进步在于不断的学习交流和实践。所以为了方便大家学习交流,为大家提供一个良好 QQ )! 学习交流 Cadence allegro 请加QQ 群: 一起来学AllegRo 【2】.群号: 331730476 .以下是正文 这篇文章写得很好,操作步骤详细,截图一目了然,通俗易懂,唯一的缺点就是部分截图不是很清晰,我对个别图片做了调整和替 换,不易替换的不清晰图片,仔细看下也能明白其中的意思。 此文章由丹心静居整理---2014.10.13 加入。对原文作者表示歉意的交流平台,在这里留下我们的群原文作者的群拒绝任何人 (QQ 软件提供了丰富的知识和方法。请大家认真学习,不要辜负作者的良 2014-10-13 第 1 页,共 83 页

二、高级约束规则设置 11、单个网络长度约束 12、a+b 类长度约束 13、a+b-c 类长度约束 14、a+b-c 在最大和最小传播延迟中的应用 y a l e D n i P 、10约束分差设置、.29分对差创建、.19设置则分规差、 9属性用置通设、 8等长型T 、.37等长NET X 阻的过电、.27等长NET 阻的电不过、.17置等长 设、 7

约束规则设置 约束管理器是一个交叉的平台,以工作簿和工作表的形式在 Cadence PCB设计流程中用于管理所有工具的高速电子约束。可以使用约束管理器和SigXplorer Expert 开发电路的拓扑并得出电子约束,可以包含定制约束、定制测量和定制激励。 所谓约束就是用户定义的限制条件,当在板上走线和放置元件时会遵守这些约束。电子约束(ECSets)就是限制PCB 上与电行为有关的对象,比如可以设置某个网络最大传输延迟为2ns。 以下图为一约束设置窗口。 一、说明 先解释一下约束的类型以及约束中用到的简写名词,如下图所示:

由众多nets或者buses、differential pairs、Xnet所组成的类,可对其赋予相似的约束。如下图所示。 2、NCC(Net Class-Class) 一般用在约束组与组之间的间距的时候使用,如下图。 3、DPr(Differential Pairs)差分对 一组差分对一般由两条Xnet或者net以差分走线的方式组成,如下图。差分对的形成有两种方式:一是由模型指定的差分对,再者就是由用户自己定义的差分对。 ?模型定义的差分对:可以在器件信号模型中指定差分对,可以使用PCB Design,PCB SI,SigXplores 来将模型 指定给相应的元件。

?用户定义的差分对:可以在约束管理器中 Net 一级的对象中创建差分对,可以灵活的更改差分对命名和更改差分对成员,但是没有模型指定差分对的精确性。 以下是设置差分对规则时,需要赋予约束的项。

针对以上约束中用到的一些约束点进行解释说明: 差分对的worksheets包含5个主要的约束目录: (1)Pin Delay 此值指一对网络之间管脚封装上的延迟,单位是时间ns 或者长度mil。 (2) 不耦合长度(Uncoupled Length) 不耦合长度约束是用来限制差分对的一对网络之间的不匹配长度。若“gather control”设置为ignore,则实际不不耦合长度不包括两个驱动和接收之间的耦合带之外的长度。若“gather control”设置为“include”,包含出芯片的这段不耦合长度。当不耦合(即在差分对刚刚从芯片出来的走线通常是不耦合的,不耦合有一定的长度)长度超过“max”时产生冲突。 (3)相位偏差(Static Phase Tolerance) 相位偏差约束确保差分对成员在转换时是同相和同步的。实际的数值(actual value)从长度上或者时间上反应了差分对成员之间的差值,当差值超出 tolerance 值时,就会有冲突。 (4)最小线间距(Min Line Spacing) 最小线间距约束指差分对之间的最小距离,如果小于设定的最小值则报错。添加的最小线间距约束值必须小于或者等于Primary Gap减去(-)Tolerance,并且也要小于或者等于Neck Gap减去(-)Tolerance。 (5)耦合参数(Coupling Parameters) 这里面包括6个部分需要设置。1、Primary gap :设置的是差分对之间的边到边理想间距,(+/-)tolerance 值是允许Diff Pairs的偏差值,如果间距偏差在范围内,差分对被认为是耦合的;2、Primary width:差分对成员的理想宽度;3、Neck gap:约束的是最小允许的边到边的差分间距,当在密集区域走线时,可能切换到neck模式,最小可允许的gap 包括Neck Gap 减去(-)Tolerance,当差分对间距小于ECSet 指定给差分对网络的Min neck width 规则值时,Neck Gap 覆盖任何Primary Gap 值,确保 Neck gap 不要低于任何Min line spaing 值,如果设置了(-)tolerance 值,不需要定义Neck gap ,因为已经说明了需要的Neck gap。;4、Neck width:最小可允许的差分对宽度,当在比较密集的区域走线的时,可能需要切换到neck模式;5、(+)Tolerance;6、(-)Tolerance。 使用差分计算器可以完成综合线宽和线距的计算以获得特殊的差分阻抗。在约束管理器中右键点击Primary Gap,

allegro 目录 第一章约束管理器介绍 (4) 1.1 约束管理器简介 (4) 1.2 约束管理器界面简介 (8) 1.2.1worksheet selector (8) 1.2.2用户接口 (9) 1.2.3View选项 (9) 1.3 启动约束管理器 (11) 第2章OBJECTS介绍 (12) 2.1 P IN-P AIRS (13) 2.1.1Pin-Pair规则 (14) 2.2 N ETS和X NETS (14) 2.3 B USES (15) 2.4 M ATCH G ROUPS (15) 2.4.1如何确定target pin pair (16) 2.4.2相对/匹配的群组规则 (16) 2.5 D IFF P AIRS (16) 2.5.1差分对工作表 (17) 2.5.2差分计算器(Differential Calculator)的使用方法 (19) 2.5.3差分对规则 (19) 2.6 D ESIGNS AND S YSTEMS (20) 第3章设置网络的走线约束 (21) 3.1.1设置网络的最大最小传输延迟 (21) 3.1.2设置网络相对传输延迟 (24) 3.1.3设置差分对约束 (26) 3.1.4查看网络规范格式和物理格式 (28) 第4章设置网络的时序和信号完整性约束 (30) 4.1 设置时序约束 (30) 4.2 设置信号完整性约束 (32) 4.2.1设置电气属性约束 (32)

0 第一章约束管理器介绍 2 4.2.2设置反射属性约束 (33) 第5章电子约束创建和应用 (35) 5.1 创建ECS ET (35) 5.2 指定ECS ET给网络 (40) 5.3 不考虑ECS ET的缺省约束值 (41) 5.4 在原理图中查看ECS ET (41) 第6章ECOS实现 (43) 6.1 在原理图中增加网络 (43) 6.2 在原理图中修改约束 (45) 6.3 在约束管理器中修改约束 (46) 6.4 在约束管理器中删除约束 (46) 6.5 在原理图中重新命名网络 (47) 第7章在原理图和PCB之间同步约束 (50) 7.1 从原理图中输出约束 (50) 7.2 在PCB D ESIGN中查看和添加约束 (50) 7.3 在原理图中导入并查看约束 (51) 7.4 在PCB和原理图之间同步约束的两种模式 (52) 7.4.1用原理图中的约束重写PCB中的约束 (53) 7.4.2在原理图中导入PCB中变更的约束 (56) 第8章约束分析 (58) 8.1 查看工作表单元格和对象 (58) 8.2 定制约束、定制测量和定制激励 (59) 8.2.1定制约束 (59) 8.2.1.1 用户定义的属性 (59) 8.2.1.2 约束的定制测量 (59) 第9章SCHEDULING NETS (61) 9.1 S CHEDULING N ETS (61) 9.2 S CHEDULING N ETS-R EVISITED (65) 第10章相对传输延迟 (68)

A llegro中的约束规则设置 Allegrophan 刚好五个字

修订记录 日期版本描述作者2008-12V1.0初版,学完的总结。适用于Cadence15.5版本。Allegrophan 2009-09-08V1.1小改,修改部分措辞Allegrophan 2009-10-14V1.2小改,更正、修改几个错漏之处。添加一些说明性文字。 感谢群里的佳猪、梦姑娘等朋友的指正! Allegrophan

目录 一:Physical(Line/vias)rule物理特性(线宽和过孔)约束设置: (4) 1)“Set values”设置约束特征值 (5) 2)“Attach property”绑定约束 (6) 3)“Assignment table”约束规则分配 (8) 二“Spacing rule”间距约束设置 (9) 1)“Set values”设置约束特征值 (9) 2)“Attach property”绑定约束 (10) 3)“Assignment table”约束规则分配 (11) 三Constraint areas区域约束设置 (12) 四Allegro中走线长度的设置 (13) 1)差分线等长设置 (13) 2)一组Net等长 (16) 3)XNet等长 (17)

线宽、线距、区域的约束主要在“Constraints Sys ”中设置,点击“Setup/Constraints ”或点击图标打开“Constraints Sys ”窗口,如下: “Constraints Sys ”窗口分两个级别,第一级别有两类:Standard design rules 和Exte Extended nded design rules 。Standard design rules 仅有一级分类,点击“Set standard values ”设置默认约束值,如下:

Allegro16.3约束设置 Allegro16.3约束设置差分对的约束设置第一步,差分对的设置差分对的设置有很多方法,下面介绍两种最常用的方法。1.点击菜单Logic→Assign Differential Pair... 弹出以下对话框。点击你想要创建差分对的Net1和Net2,填入差分的名字,点击Add后就成功创建了差分对。点击Auto Generate按钮后,弹出以下对话框:在第一个输入框填入Net的主要名字后,在下面的框中填入差分线的标志如N,P。点击Generate即可自动产生差分对。2.在约束管理器中设置差分对。在DSN上点击右键,在菜单中选择 Create→Differential Pair。即可弹出下面的对话框。和上一种方法的设置差不多,这里就不再叙述了。第二步差分对约束规则的设置差分对各项约束可以在约束管理器中的Electric→Net→routing→Differential Pair中直接在各差分对 上填入各项约束数值就可生效,但更好的方法是创建约束规则后赋给各个差分对。在DSN上点击右键,在菜单中选择Create→Electrical CSet后,弹出下面的对话框;输入规则名后点Ok,在Electric→constraimt set→outing→Differential Pair中可以看到新规则。在表格中输入各项数值即可完成新规则的设置。如图所示差分对约束参数主要有以下几个: 1coupling paramaters 主要包括了Primary Gap 差分对最

优先线间距(边到边间距)。Primary Width 差分对最优先线宽。Neck Gap 差分对Neck模式下的线间距(边到边间距),用于差分对走线在布线密集区域时切换到Neck值。Neck Width差分对Neck模式下的线宽,用于差分对走线在布线 密集区域时切换到Neck值。如图所示设置数值时在表格中右键菜单中选择change,会出现以下各层数值表格,可以 在每一层上设置不同的数值。需要注意的是在物理(physical)约束中同样可以设置差分规则,但是电气规则约束在布线时更优先,同时电气规则可以设置更多的约束,推荐在电气规则中设置差分走线的约束。2 Min Line Specing 差分对最小间距,一定要小于或等于"Primary gap"与(-)tolerance的数值,并且也要小于或等于"Neck gap"与(-)tolerance的 数值。对于不符合约束的差分对,会显示“DS”的DRC错误 提示。3 Dynamic Phase:动态相位检查,在16.3版本新加 入的功能。对差分对路径中每个转角之间造成的路径差异进行检查。如在整个差分对网络中,正向与反向之间的走线差距不能超过“x mils”。如果整个路径中的某一个位置,发生了两个信号之间相位偏移超过了规定的“x mils”,这个误差必须在“y mils”范围内补偿回来。如下图x=20,y=600.设定约束 时tolerance填入x值,max length填入y值。对于不符合 约束的走线的路径会以高亮显现,并且显示DY错误。4 Static Phase Tolerance 这个约束设置了两根差分线之间的差值,

C o n s t r a i n t M a n a g e r 约束规则基本设置 Revised by Petrel at 2021

约束规则的设置 孙海峰在PCB设计中规则设置是必不可少的,它也可以被称为DRC检查规则,用来确定电路板的走线规则是否符合设计要求。在AllegroPCB的电路板设计过程中,设计约束规则主要包括时序规则、走线规则、间距规则、信号完整性规则等以及物理规则等设置。 首先,需要认识一下,AllegroPCB的约束管理器: 在PCB设计界面中,执行Setup/Constraints/ConstraintManager命令,弹出AllegroConstraintManager对话框,如下图。 在约束管理器中,设计者可以对电路板的电气规则、物理规则、间距规则等设计规则进行设置定义。约束规则可以按板层、网络或者区域进行设置。 约束管理器是Cadence系统提供的专用规则设置系统,主要有菜单栏、工具栏、工作表选择区、工作状态报告栏四部分,在工作表中选择一个对象,然后右击,在弹出的命令菜单中,可以进行任意操作。 工作表选择区内可以选择电气规则、物理规则、间距规则等规则设置。在对应Net文件夹内,可以创建指定网络的对象分组,如:系统、设计、总线、差分对、扩展网络(XNet)、网络、相对或匹配群组,也可以创建基于相关属性的电气规则(ECSet)、物理规则(PCSet)、间距规则(SCSet)等。 约束管理器的约束对象分为引脚对、总线和匹配群组,她们相互之间存在优先级差异,即底层对象会集成顶层对象指定约束,为底层对象指定的约束优先高于上层继承的约束,对象层次的优先级为系统、设计、总线、差分对、扩展网络、相对或匹配群组、引脚对。 一、电气规则设置 在约束管理器中,选择Electrical选项卡,其中可以为设计或网络来设置时序规则、信号完整性规则、布线的电气规则(延时、差分对)等,执行Objects/Create/ElectricalCSet命令可新建电气规则。

目录 第一章约束管理器介绍 (4) 1.1约束管理器简介 (4) 1.2约束管理器界面简介 (8) 1.2.1worksheet selector (8) 1.2.2用户接口 (9) 1.2.3View选项 (9) 1.3启动约束管理器 (11) 第2章OBJECTS介绍 (12) 2.1P IN-P AIRS (13) 2.1.1Pin-Pair规则 (14) 2.2N ETS和X NETS (14) 2.3B USES (15) 2.4M ATCH G ROUPS (15) 2.4.1如何确定target pin pair (16) 2.4.2相对/匹配的群组规则 (16) 2.5D IFF P AIRS (16) 2.5.1差分对工作表 (17) 2.5.2差分计算器(Differential Calculator)的使用方法 (19) 2.5.3差分对规则 (19) 2.6D ESIGNS AND S YSTEMS (20) 第3章设置网络的走线约束 (21) 3.1.1设置网络的最大最小传输延迟 (21) 3.1.2设置网络相对传输延迟 (24) 3.1.3设置差分对约束 (26) 3.1.4查看网络规范格式和物理格式 (28) 第4章设置网络的时序和信号完整性约束 (30) 4.1设置时序约束 (30) 4.2设置信号完整性约束 (32) 4.2.1设置电气属性约束 (32)

4.2.2设置反射属性约束 (33) 第5章电子约束创建和应用 (35) 5.1创建ECS ET (35) 5.2指定ECS ET给网络 (40) 5.3不考虑ECS ET的缺省约束值 (41) 5.4在原理图中查看ECS ET (41) 第6章ECOS实现 (43) 6.1在原理图中增加网络 (43) 6.2在原理图中修改约束 (45) 6.3在约束管理器中修改约束 (46) 6.4在约束管理器中删除约束 (46) 6.5在原理图中重新命名网络 (47) 第7章在原理图和PCB之间同步约束 (50) 7.1从原理图中输出约束 (50) 7.2在PCB D ESIGN中查看和添加约束 (50) 7.3在原理图中导入并查看约束 (51) 7.4在PCB和原理图之间同步约束的两种模式 (52) 7.4.1用原理图中的约束重写PCB中的约束 (53) 7.4.2在原理图中导入PCB中变更的约束 (56) 第8章约束分析 (58) 8.1查看工作表单元格和对象 (58) 8.2定制约束、定制测量和定制激励 (59) 8.2.1定制约束 (59) 8.2.1.1 用户定义的属性 (59) 8.2.1.2 约束的定制测量 (59) 第9章SCHEDULING NETS (61) 9.1S CHEDULING N ETS (61) 9.2S CHEDULING N ETS-R EVISITED (65) 第10章相对传输延迟 (68)

ALLEGRO16.3 约束设置 一. 普通单端线的线宽设置 该约束定义为PCS,即physical constraint set,选中physical-->physical constraint set-->all layers,对右边的功能名字点击右键,creat-->physical cset即可创建pcs约束,如下图所示,我的工程名字是newcore。 如果需要对每层设置不同的线宽的话,只要把default展开,修改需要单独设置的层的线宽即可。上图中设置最小线宽为4mil,最大为40mil,在走线的时候,默认走的是最小线宽4mil,NECK下的线宽用于NECK MODE下的线宽,一般在bga下面走线的时候有时候两个管脚间距过小,需要使用neck mode,走线时,鼠标右键,选择neck mode即进入neck模式。 如果需要设置某些线的默认线宽不是4mil的话,比如设置默认电源、地的默认线宽不是4mil,那么可以创建一个PCS,适用于电源和地信号,默认线宽为10mil,如下图 设置好后,在physical-->net中对GND信号使用PCS_POWER规则,如下图 二. 普通单端线的线距设置 该约束定义为SCS,即spacing constraint set,选中spacing-->spacing constraint set-->all layers,对右边的功能名字点击右键,creat-->physical cset即可创建pcs约束,如下图所示。

default是3w间距设置,SCS_5W是5w间距设置,3w或5w都是line to line或者line to shape的,因为line to line和line to shape的平行距离可能较大。而line to hole、line to via、line to pin之类的最小间距仅是非常小的一段,所以这些间距的值可以是很小的,设置5即可。 如果需要设置某些线对其它线的线间距为5w的话,只要在net-->all layers中对该线应用scs_5w规则即可,如下图,对DDR的时钟线应用了5w规则,注意到这里的DDR_CK0是差分线对,5w规则应用于该差分线对与其他线之间的间距,而不是差分线内两线之间的间距: 三. 差分线线宽、内线距的设置 这里的内间距指的是差分对内两线的间距 在physical-->physical constraint set-->all layers中,有differential pair的一些设置,但是我应用时这些设置都是无效的,如下图所示,我还不清楚这些设置是做什么用的。 我知道的有效的差分线线宽、内间距的设置是在electrical-->electrical constraint set-->routing-->differential pari中是实现的,我的设置如下图: uncoupled length:一般不需要设置,没有用single trace mode去调节差分线的话,uncoupled length只在引脚附近出现,手动调一下该段uncoupled length即可。 Min line spacing:内间距最小线距,若实际走线内间距小于这个值,DRC就会出错。 Primary Gap:默认内间距 Primary width:默认线宽 Neck Gap: neck mode模式下默认内间距 Neck Width:neck mode 模式下默认线宽 四. 差分线外间距的设置