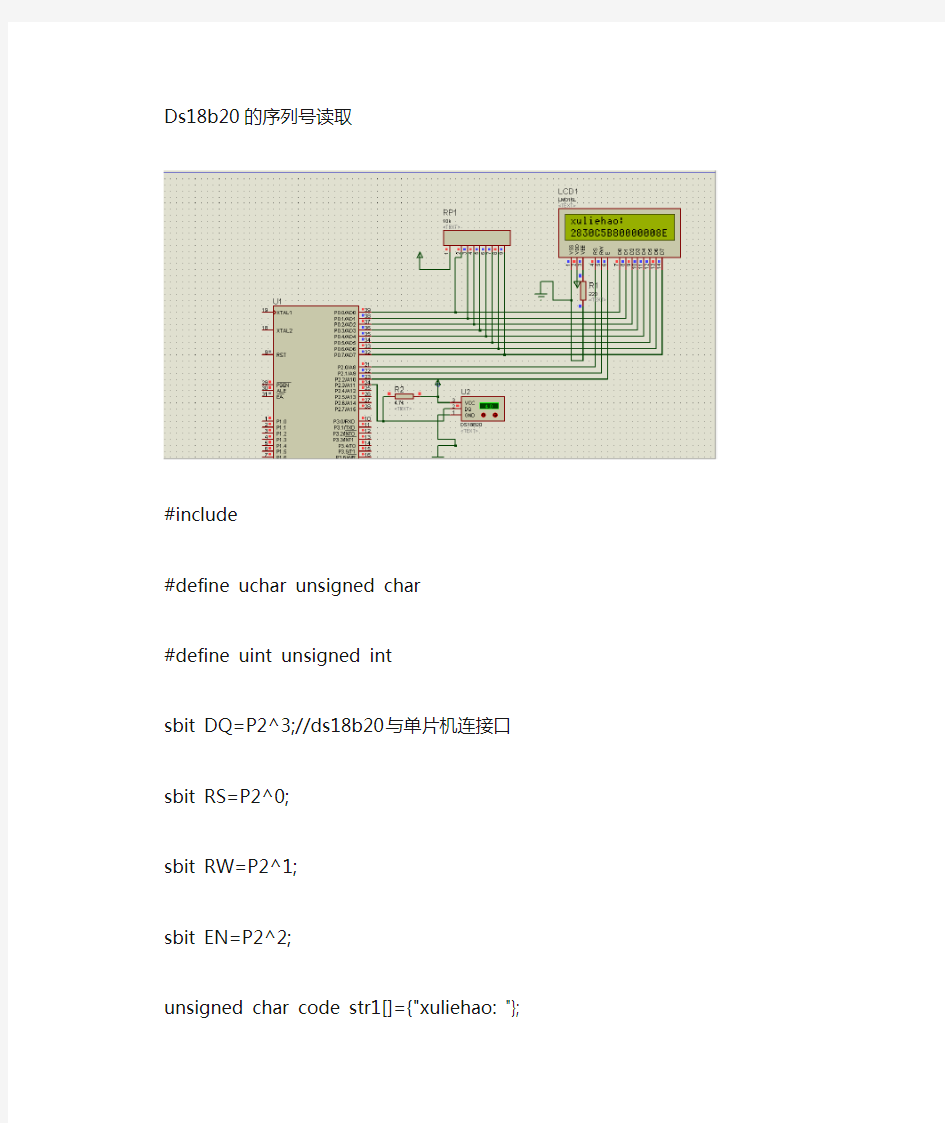

Ds18b20的序列号读取

#include

#define uchar unsigned char

#define uint unsigned int

sbit DQ=P2^3;//ds18b20与单片机连接口

sbit RS=P2^0;

sbit RW=P2^1;

sbit EN=P2^2;

unsigned char code str1[]={"xuliehao: "};

unsigned char code str2[]={" "};

uchar data disdata[5];

uint tvalue;//温度值

uchar tflag;//温度正负标志

/*************************lcd1602程序**************************/ void delay1ms(unsigned int ms)//延时1毫秒(不够精确的){unsigned int i,j;

for(i=0;i for(j=0;j<100;j++); } void wr_com(unsigned char com)//写指令// { delay1ms(1); RS=0; RW=0; EN=0; P0=com; delay1ms(1); EN=1; delay1ms(1); EN=0; } void wr_dat(unsigned char dat)//写数据// { delay1ms(1);; RS=1; RW=0; EN=0; P0=dat; delay1ms(1); EN=1; delay1ms(1); EN=0; } void lcd_init()//初始化设置// {delay1ms(15); wr_com(0x38);delay1ms(5); wr_com(0x0c); wr_com(0x06); } init_play()//初始化显示 { int i; lcd_init(); wr_com(0x80); for(i=0;i<15;i++) wr_dat(str1[i]); wr_com(0xc0); } /****************************ds1820程序***************************************/ void delay_18B20(unsigned int i)//延时1微秒 { while(i--); } void ds1820rst()/*ds1820复位*/ { unsigned char x=0; DQ = 1; //DQ复位 delay_18B20(4); //延时 DQ = 0; //DQ拉低 delay_18B20(100); //精确延时大于480us DQ = 1; //拉高 delay_18B20(40); } uchar ds1820rd()/*读数据*/ { unsigned char i=0; unsigned char dat = 0; for (i=8;i>0;i--) { DQ = 0; //给脉冲信号 dat>>=1; DQ = 1; //给脉冲信号 if(DQ) dat|=0x80; delay_18B20(10);//延时106us } return(dat); } void ds1820wr(uchar wdata)/*写数据*/ {unsigned char i=0; for (i=8; i>0; i--) { DQ = 0; DQ = wdata&0x01; delay_18B20(10);//延时106us DQ = 1; wdata>>=1; } } read_temp()/*读取温度值并转换*/ {uchar a,b; ds1820rst(); ds1820wr(0xcc);//*跳过读序列号*/ ds1820wr(0x44);//*启动温度转换*/ ds1820rst(); ds1820wr(0xcc);//*跳过读序列号*/ ds1820wr(0xbe);//*读取温度*/ a=ds1820rd(); b=ds1820rd(); tvalue=b; tvalue<<=8; tvalue=tvalue|a; if(tvalue<0x0fff) tflag=0; else {tvalue=~tvalue+1; tflag=1; } tvalue=tvalue*(0.625);//温度值扩大10倍,精确到1位小数 return(tvalue); } /*******************************************************************/ /********************主程序***********************************/ void main() { uchar a; int i; init_play();//初始化显示 ds1820rst(); ds1820wr(0x33); wr_com(0xc0); for(i=0;i<8;i++) {a=ds1820rd(); if(a/16>9) wr_dat(a/16+0x37); else wr_dat(a/16+0x30); if(a%16>9) wr_dat(a%16+0x37); else wr_dat(a%16+0x30);} while(1); } 时序分析基础与时钟约束实例(1) 文中实例配套SF-CY3开发套件。更多内容请参考《SF-CY3 FPGA套件开发指南》。 何谓静态时序分析(STA,Static Timing Analysis)? 首先,设计者应该对FPGA内部的工作方式有一些认识。FPGA的内部结构其实就好比一块PCB板,FPGA的逻辑阵列就好比PCB板上的一些分立元器件。PCB通过导线将具有相关电气特性的信号相连接,FPGA也需要通过内部连线将相关的逻辑节点导通。PCB板上的信号通过任何一个元器件都会产生一定的延时,FPGA的信号通过逻辑门传输也会产生延时。PCB的信号走线有延时,FPGA的信号走线也有延时。这就带来了一系列问题,一个信号从FPGA的一端输入,经过一定的逻辑处理后从FPGA的另一端输出,这期间会产生多大的延时呢?有多个总线信号从FPGA的一端输入,这条总线的各个信号经过逻辑处理后从FPGA 的另一端输出,这条总线的各个信号的延时一致吗?之所以关心这些问题,是因为过长的延时或者一条总线多个信号传输时间的不一致,不仅会影响FPGA本身的性能,而且也会给FPGA之外的电路或者系统带来诸多问题。 言归正传吧,之所以引进静态时序分析的理论也正是基于上述的一些思考。它可以简单的定义为:设计者提出一些特定的时序要求(或者说是添加特定的时序约束),套用特定的时序模型,针对特定的电路进行分析。分析的最终结果当然是要求系统时序满足设计者提出的要求。 下面举一个最简单的例子来说明时序分析的基本概念。假设信号需要从输入到输出在FPGA内部经过一些逻辑延时和路径延时。系统要求这个信号在FPGA内部的延时不能超过15ns,而开发工具在执行过程中找到了如图所示的一些可能的布局布线方式。那么,怎样的布局布线能够达到系统的要求呢?仔细分析一番,发现所有路径的延时可能为14ns、15ns、16ns、17ns、18ns,有两条路径能够满足要求,那么最后的布局布线就会选择满足要求的两条路径之一。 静态时序分析的前提就是设计者先提出要求,然后时序分析工具才会根据特定的时序模型进行分析,即有约束才会有分析。若设计者不添加时序约束,那么时序分析就无从谈起。特权同学常常碰见一些初学者在遇到问题时不问青红皂白就认为是时序问题,实际上只有在添加了时序约束后,系统的时序问题才有可能暴露出来。 下面我们再来看一个例子,我们假设有4个输入信号,经过FPGA内部一些逻辑处理后输出。FPGA内部的布线资源有快有慢之分,好比国道和高速公路。通过高速通道所需要的路径延时假设为3ns-7ns,但只有两条可用;而通过慢速通道的路径延时则>10ns。 (1)先将数据线置高电平“1”。 (2)延时(该时间要求的不是很严格,但是尽可能的短一点) (3)数据线拉到低电平“0”。 (4)延时750微秒(该时间的时间范围可以从480到960微秒)。 (5)数据线拉到高电平“1”。 (6)延时等待(如果初始化成功则在15到60毫秒时间之内产生一个由DS18B20所返回的低电平“0”。据该状态可以来确定它的存在,但是应注意不能无限的进行等待,不然会使程序进入死循环,所以要进行超时控制)。 (7)若CPU读到了数据线上的低电平“0”后,还要做延时,其延时的时间从发出的高电平算起(第(5)步的时间算起)最少要480微秒。 (8)将数据线再次拉高到高电平“1”后结束。 (1)数据线先置低电平“0”。 (2)延时确定的时间为15微秒。 (3)按从低位到高位的顺序发送字节(一次只发送一位)。 (4)延时时间为45微秒。 (5)将数据线拉到高电平。 (6)重复上(1)到(6)的操作直到所有的字节全部发送完为止。(7)最后将数据线拉高。 DS18B20的写操作时序图如图 DS18B20的读操作 (1)将数据线拉高“1”。 (2)延时2微秒。 (3)将数据线拉低“0”。 (4)延时15微秒。 (5)将数据线拉高“1”。 (6)延时15微秒。 (7)读数据线的状态得到1个状态位,并进行数据处理。 (8)延时30微秒。DS18B20的读操作时序图如图所示。 DS18B20的Protues仿真图 源程序代码: #include "reg51.h" #include "intrins.h" // 此头文件中有空操作语句NOP 几个微秒的延时可以用NOP 语句,但本人没用NOP,直接用了I++来延时 #define uchar unsigned char #define uint unsigned int uchar code table[]={0x30,0x31,0x32,0x33,0x34,0x35,0x36,0x37, 0x38,0x39}; sbit ds18b20_io=P2^0; //单片机与DS18B20的连接口 sbit lcdrs=P2^6; //1602与单片机的接口 sbit lcden=P2^7; 文献综述是"一种在分析、比较、整理、归纳一定时空范围内有关特 定课题研究的全部或大部情报的基础上,简明的类述其中的最重要部分,并标引出处的情报研究报告"。文献综述的定义包含三个基本要素:首先,文献综述反映原始文献有一定的时间和空间范围,它反映一定时期内或是某一时期一定空间范围的原始文献的内容。其次,文献综述集中反映一批相关文献的内容。其它二次文献如题录、索引、文摘、提要等一条只能揭示一篇原始文献的外表信息或内容信息,且各条目之间没有联系,而综述一篇可集中一批相关文献,且将这批文献作为一个有机整体予以揭示,信息含量比二次文献多得多。第三,文献综述是信息分析的高级产物。书目、索引等是对原始文献的外表特征进行客观描述,不涉及文献内容,编写人员不需了解原始文献的内容,也不需具备相关学科的基础知识;提要、文摘是对原始文献的 内容作简要介绍和评价,编写人员需要具有相关学科的一些基础知识,以识别和评价原始文献;文献综述则要求编写人员对综述的主题有深 入的了解,全面、系统、准确、客观地概述某一主题的内容。运用分析、比较、整理、归纳等方法对一定范围的文献进行深度加工,对于读者具有深度的引导功能,是创造性的研究活动。 文献综述的类型可以从不同的角度对文献综述进行划分,最常见的方法是根据文献综述反映内容深度的不同即信息含量的不同划分按照文献综述信息含量的不同,可将文献综述分为叙述性综述、评论性综述和专题研究报告三类。 叙述性综述是围绕某一问题或专题,广泛搜集相关的文献资料,对其内容进行分析、整理和综合,并以精炼、概括的语言对有关的理论、观点、数据、方法、发展概况等作综合、客观的描述的信息分析产品。叙述性综述最主要特点是客观,即必须客观地介绍和描述原始文献中的各种观点和方法。一般不提出撰写者的评论、褒贬,只是系统地罗列。叙述性综述的特点使得读者可以在短时间内,花费较少的精力了解到本学科、专业或课题中的各种观点、方法、理论、数据,把握全局,获取资料。 评论性综述是在对某一问题或专题进行综合描述的基础上,从纵向或横向上作对比、分析和评论,提出作者自己的观点和见解,明确取舍的一种信息分析报告。评论性综述的主要特点是分析和评价,因此有人也将其称为分析性综述。评论性综述在综述各种观点、理论或方法的同时,还要对每种意见、每类数据、每种技术做出分析和评价,表明撰写者自己的看法,提出最终的评论结果。可以启发思路,引导读者寻找新的研究方向。 专题研究报告是就某一专题,一般是涉及国家经济、科研发展方向的重大课题,进行反映与评价,并提出发展对策、趋势预测。"是一种现实性、政策性和针对性很强的情报分析研究成果"。其最显著的特点是预测性,它在对各类事实或数据、理论分别介绍描述后,进行论证、预测的推演,最后提出对今后发展目标和方向的预测及规划。专题研究报告对于科研部门确定研究重点和学科发展方向,领导部门制定各项决策,有效实施管理起着参考和依据的作用。这一类综述主 ASIC时序约束、时序分析 2009-11-13 22:13 A 时序约束的概念和基本策略 时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移约束(IPAD到FFS、FFS到OPAD)以及静态路径约束(IPA 综合布线工具调整映射和布局布线过程,使设计达到时序要求。例如用OFFSET_IN_BEFORE约束可以告诉综合布线工具输入信号在以根据这个约束调整与IPAD相连的Logic Circuitry的综合实现过程,使结果满足FFS的建立时间要求。 附加时序约束的一般策略是先附加全局约束,然后对快速和慢速例外路径附加专门约束。附加全局约束时,首先定义设计的所有分组附加周期约束,然后对FPGA/CPLD输入输出PAD附加偏移约束、对全组合逻辑的PAD TO PAD路径附加约束。附加专门约束时速例外路径和多周期路径,以及其他特殊路径。 B 附加约束的基本作用 1. 提高设计的工作频率 对很多数字电路设计来说,提高工作频率非常重要,因为高工作频率意味着高处理能力。通过附加约束可以控制逻辑的综时,从而提高工作频率。 2. 获得正确的时序分析报告 几乎所有的FPGA设计平台都包含静态时序分析工具,利用这类工具可以获得映射或布局布线后的时序分析报告,从而对束作为判断时序是否满足设计要求的标准,因此要求设计者正确输入约束,以便静态时序分析工具输出正确的时序分析 3. 指定FPGA/CPLD引脚位置与电气标准 FPGA/CPLD的可编程特性使电路板设计加工和FPGA/CPLD设计可以同时进行,而不必等FPGA/CPLD引脚位置完全确定,从成后,设计者要根据电路板的走线对FPGA/CPLD加上引脚位置约束,使FPGA/CPLD与电路板正确连接。另外通过约束还特性。为了满足日新月异的通信发展,Xilinx新型FPGA/CPLD可以通过IO引脚约束设置支持诸如 AGP、BLVDS、CTT、G LVPECL、LVDSEXT、LVTTL、 PCI、PCIX、SSTL、ULVDS等丰富的IO接口标准。另外通过区域约束还能在FPGA上规划各个成模块化设计等。 C 周期(PERIOD)的含义 周期的含义是时序中最简单也是最重要的含义,其它很多时序概念会因为软件商不同略有差异,而周期的概念确是最通用的,周期面要讲到的其它时序约束都是建立在周期约束的基础上的,很多其它时序公式,可以用周期公式推导。周期约束是一个基本时序和具根据PERIOD约束检查时钟域内所有同步元件的时序是否满足要求。PERIOD约束会自动处理寄存器时钟端的反相问题,如果相迟将被默认限制为PERIOD约束值的一半。如下图所示, 图1 周期的定义 时钟的最小周期为: TCLK = TCKO +TLOGIC +TNET +TSETUP -TCLK_SKEW TCLK_SKEW =TCD2 -TCD1 【时间简“识”】 说明:本文摘自于经管之家(原人大经济论坛) 作者:胖胖小龟宝。原版请到经管之家(原人大经济论坛) 查看。 1.带你看看时间序列的简史 现在前面的话—— 时间序列作为一门统计学,经济学相结合的学科,在我们论坛,特别是五区计量经济学中是热门讨论话题。本月楼主推出新的系列专题——时间简“识”,旨在对时间序列方面进行知识扫盲(扫盲,仅仅扫盲而已……),同时也想借此吸引一些专业人士能够协助讨论和帮助大家解疑答惑。 在统计学的必修课里,时间序列估计是遭吐槽的重点科目了,其理论性强,虽然应用领域十分广泛,但往往在实际操作中会遇到很多“令人发指”的问题。所以本帖就从基础开始,为大家絮叨絮叨那些关于“时间”的故事! Long long ago,有多long?估计大概7000年前吧,古埃及人把尼罗河涨落的情况逐天记录下来,这一记录也就被我们称作所谓的时间序列。记录这个河流涨落有什么意义?当时的人们并不是随手一记,而是对这个时间序列进行了长期的观察。结果,他们发现尼罗河的涨落非常有规律。掌握了尼罗河泛滥的规律,这帮助了古埃及对农耕和居所有了规划,使农业迅速发展,从而创建了埃及灿烂的史前文明。 好~~从上面那个故事我们看到了 1、时间序列的定义——按照时间的顺序把随机事件变化发展的过程记录下来就构成了一个时间序列。 2、时间序列分析的定义——对时间序列进行观察、研究,找寻它变化发展的规律,预测它将来的走势就是时间序列分析。 既然有了序列,那怎么拿来分析呢? 时间序列分析方法分为描述性时序分析和统计时序分析。 1、描述性时序分析——通过直观的数据比较或绘图观测,寻找序列中蕴含的发展规律,这种分析方法就称为描述性时序分析 ?描述性时序分析方法具有操作简单、直观有效的特点,它通常是人们进行统计时序分析的第一步。 在进行FPGA的设计时,经常会需要在综合、实现的阶段添加约束,以便能够控制综合、实现过程,使设计满足我们需要的运行速度、引脚位置等要求。通常的做法是设计编写约束文件并导入到综合实现工具,在进行FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。 一、周期约束 周期约束是Xilinx FPGA 时序约束中最常见的约束方式。它附加在时钟网线上,时序分析工具会根据周期约束来检查时钟域内所有同步元件的时序是否满足需求。周期约束会自动的寄存器时钟端的反相。如果相邻的两个元件的时钟相位是相反的,那么它们之间的延迟将被默认的限制成周期约束的一半。 在进行周期约束之前,必须对电路的时钟周期明了,这样才不会出现约束过松或者过紧的现象。一般情况下,设计电路所能达到的最高运行频率取决于同步元件本身的Setup Time 和Hold Time,以及同步元件之间的逻辑和布线延迟。周期约束一般是使用下面的约束方法: 1、period_item PERIOD=period {HIGH|LOW} [high_or low_item] 其中,period_item可以是NET或TIMEGRP,分别代表时钟线名称net name或元件分组名称group-name。用NET表示PERIOD约束作用到名为“net name”的时钟网线所驱动的同步元件上,用TIMEGRP表示PERIOD约束作用到TIMEGRP所定义的分组(包括FFS、LATCH和RAM等同步元件)上。period是目标时钟周期,单位可以是ps、ns、μS和ms 等。HIGH|LOW指出时钟周期中的第1个脉冲是高电平还是低电平,high or low time为HIGH LOW指定的脉冲的持续时间,默认单位是ns。如果没有该参数,时钟占空比是50%。例如,NET SYS_CLK PERIOD=10 ns HIGH 4ns 2、NET“clock net name”TNM_NET=“timing group name”; TIMESPEC“TSidentifier”=PERIOD “TNM reference”period {HIGH | LOW} [high or low item]INPUT_JITTER value; 很多时候为了能够定义比较复杂的派生关系的时钟周期,就要使用该方法。其中TIMESPEC在时序约束中作为一个标识符表示本约束为时序规范;TSidentifier包括字母TS和一个标识符identifier共同作为一个TS属性;TNM reference指定了时序约束是附加在哪一个组上,一般情况下加在TNM_NET定义的分组上。HIGH | LOW 指的是时钟的初始相位表明第一个时钟是上升沿还是下降沿;high or low item 表示的是时钟占空比,即就是high或者low的时间,默认为1:1, INPUT_JITTER 表示的是时钟的抖动时间,时钟会在这个时间范围内抖动,默认单元为ps。比如周期约束: NET "ex_clk200m_p" TNM_NET = TNM_clk200_p; TIMESPEC "TS_clk200_p" = PERIOD "TNM_clk200_p" 5.000 ns HIGH 50 %; 建立一个TNM_clk200_p的时序分组,包括时钟网络ex_clk200m_p驱动的所有同步 最近天气热了,想要是做个能显示温度的小设备就好了, 于是想到DIY 个电子温度计, 网上找了很多资料,结合自己的材料,设计了这个用单片机控制的实时电子温度计。 作为单 片机小虾的我做这个用了 2天时间,当然是下班后,做工不行见谅了。 主要元件用到了单片机 STC89C54RD+ , DB18B20温度传感器,4为共阳数码管, PNPS8550三极管等。 先上原理图: 洞洞板布局图: 然后就是实物图了: 函8D P3 iW 、 E E FJ T I RF D51*BZ0渥度澈码管显示 F7 Dl'AI>D li'A£> I 2、心 PDRM, 杖心P0WAD7 Pl I^TO 洋心EI^AJ D FLSAH 附上源程序:程序是别人写的,我只是自己 修改了下,先谢谢原程序者的无私奉献。 #include"reg52.h” #define uchar unsigned char #define uint unsigned int sbit DQ=P3A 4; 〃温度数据口 sbit wx1=P2A0; sbit wx2=P2A1; sbit wx3=P2A2; sbit wx4=P2A3; unsigned int temp, temp1,temp2, xs; //位选1 //位选2 //位选3 //位选4 uchar code table[]={0xc0,0xf9,0xa4,0xb0,0x99, 0x92,0x82,0xf8,0x80,0x90,0x88,0x83,0xc6}; /****** 延时程序 *******/ void delay1(unsigned int m) { unsigned int i,j; for(i=m;i>0;i--) for(j=110;j>0;j--); } void delay(unsigned int m) { while(m--); } /***********ds18b20 uchar ReadOneChar() { unsigned char i=0; unsigned char dat = 0; for (i=8;i>0;i--) { 读一个字节 **************/ void Init_DS18B20() { unsigned char x=0; DQ = 1; //DQ 复位 delay(8); 〃稍做延时 DQ = 0; 〃单片机将 ds18b20通信端口 DQ 拉低 delay(80); //精确延时大于480us DQ = 1; delay(4); x=DQ; delay(20); } 〃拉高总线 //稍做延时后如果x=0则初始化成功 x=1 则初始化失败 〃共阳数码管 〃温度延时程序 一、毕业设计(论文)内容及研究意义(价值) 1.1 研究内容 时间序列分析是一种动态数据处理的统计方法。该方法基于随机过程理论和数理统计学方法,研究随机数据序列所遵从的统计规律,以用于解决实际问题。它包括一般统计分析(如自相关分析,谱分析等),统计模型的建立与推断,以及关于时间序列的最优预测、控制与滤波等内容。时间序列是按时间顺序排列的一组数字序列。而时间序列分析就是利用这组数列,应用数理统计方法加以处理,以预测未来事物的发展。它的基本原理:一是承认事物发展的延续性。应用过去数据,就能推测事物的发展趋势。二是考虑到事物发展的随机性。任何事物发展都可能受偶然因素影响,为此要利用统计分析中加权平均法对历史数据进行处理。 随着招生改革的深化,高校招生生源之争在所难免。通过时间序列分析的基本方法:回归分析法、指数加权平滑法、移动平均法来分析某高校招生部门提供的2005~2010年度各省、直辖市新生入学报到率的历史数据,应用基于时间序列分析法的新生入学报到率预测模型预测2011年14个省、直辖市新生入学报到率,然后与2011年高校新生入学报到率的实际情况进行比较,验证该模型的合理性和可信性。 1.2 研究意义 通过科学、准确地对新生入学报到率的预测,使学校招生总体规划与国民经济发展规划和社会发展相适应,招生部门也可科学地规划各省、直辖市的招生指标。如在学校每年各招生指标不变的前提下,对预测入学率较高的省份放较多的招生指标,相反入学率较低的则适当减少招生指标。因此,新生入学报到率的预测是招生部门每年编制各省、直辖市招生计划的重要依据,而预测方法又是科学预测入学率的重要手段。通常学校招生部门编制下一年的招生计划的原则是在保证不突破学校总的招生计划前提下提高入学报到率,以最高的全校入学率来完成学校每年的招生任务。而本次论文主要是为了研究和验证时间序列分析在高校新生入学报到率预测过程中可用性,为高校招生时制定合理的招生计划提供帮助。 18B20温度传感器应用解析 温度传感器的种类众多,在应用与高精度、高可靠性的场合时DALLAS(达拉斯)公司生产的DS18B20温度传感器当仁不让。超小的体积,超低的硬件开消,抗干扰能力强,精度高,附加功能强,使得DS18B20更受欢迎。对于我们普通的电子爱好者来说,DS18B20的优势更是我们学习单片机技术和开发温度相关的小产品的不二选择。了解其工作原理和应用可以拓宽您对单片机开发的思路。 DS18B20的主要特征: ?? 全数字温度转换及输出。 ?? 先进的单总线数据通信。 ?? 最高12位分辨率,精度可达土0.5摄氏度。 ?? 12位分辨率时的最大工作周期为750毫秒。 ?? 可选择寄生工作方式。 ?? 检测温度范围为–55°C ~+125°C (–67°F ~+257°F) ?? 内置EEPROM,限温报警功能。 ?? 64位光刻ROM,内置产品序列号,方便多机挂接。 ?? 多样封装形式,适应不同硬件系统。 DS18B20芯片封装结构: DS18B20引脚功能: ·GND 电压地·DQ 单数据总线·VDD 电源电压·NC 空引脚 DS18B20工作原理及应用: DS18B20的温度检测与数字数据输出全集成于一个芯片之上,从而抗干扰力更强。其一个工作周期可分为两个部分,即温度检测和数据处理。在讲解其工作流程之前我们有必要了解18B20的内部存储器资源。18B20共有三种形态的存储器资源,它们分别是: ROM 只读存储器,用于存放DS18B20ID编码,其前8位是单线系列编码(DS18B20的编码是19H),后面48位是芯片唯一的序列号,最后8位是以上56的位的CRC码(冗余校验)。数据在出产时设置不由用户更改。DS18B20共64位ROM。RAM 数据暂存器,用于内部计算和数据存取,数据在掉电后丢失,DS18B20共9个字节RAM,每个字节为8位。第1、2个字节是温度转换后的数据值信息,第3、4个字节是用户EEPROM(常用于温度报警值储存)的镜像。在上电复位时其值将被刷新。第5个字节则是用户第3个EEPROM的镜像。第6、7、8个字节为计数寄存器,是为了让用户得到更高的温度分辨率而设计的,同样也是内部温度转换、计算的暂存单元。第9个字节为前8个字节的CRC码。EEPROM 非易失性记忆体,用于存放长期需要保存的数据,上下限温度报警值和校验数据,DS18B20共3位EEPROM,并在RAM都存在镜像,以方便用户操作。 RAM及EEPROM结构图: 图2 我们在每一次读温度之前都必须进行复杂的且精准时序的处理,因为DS18B20的硬件简单结果就会导致软件的巨大开消,也是尽力减少有形资产转化为无形资产的投入,是一种较好的节约之道。 控制器对18B20操作流程: 1,复位:首先我们必须对DS18B20芯片进行复位,复位就是由控制器(单片机)给DS18B20单总线至少480uS的低电平信号。当18B20接到此复位信号后则会在15~60uS后回发一个芯片的存在脉冲。 2,存在脉冲:在复位电平结束之后,控制器应该将数据单总线拉高,以便于在15~60uS后接收存在脉冲,存在脉冲为一个60~240uS的低电平信号。至此,通信双方已经达成了基本的协议,接下来将会是控制器与18B20间的数据通信。如果复位低电平的时间不足或是单总线的电路断路都不会接到存在脉冲,在设计时要注意意外情况的处理。 XILINX时序约束使用指南笔记 第一章 时序约束介绍 第二章 时序约束方法 第三章 时序约束原则 第四章 在XST中指定时序约束 第五章 在Synplify中指定时序约束方法 第六章 时序约束分析 第一章 时序约束介绍 基本的时序约束包括: “PERIOD Constraints” “OFFSET Constraints” “FROM:TO(Multi‐Cycle)约束” 第二章 时序约束方法 1,简介: 2,基本的约束方法 根据覆盖的路径不同,时序要求变成一些不同的全局约束。 最普通的路径类型包括: 1,输入路径 2,同步元件到同步元件路径 3,指定路径 4,输出路径 XILINX的时序约束与每一种全局约束类型都有关。最有效的方法就是一开始就指定全局约束然后再加上指定路径的约束。在很多案例中,只要全局约束就可满足需求。 FPGA器件执行工具都是由指定的时序要求驱动的。如果时序约束过头的话,就会导致内存使用增加,工具运行时间增加。更重要的是,过约束还会导致性能下降。因此,推荐使用实际设计要求的约束值。 3,输入时序约束 输入时序约束包括2种 “系统同步输入” “源同步输入” 输入时钟约束覆盖了输入数据的FPGA外部引脚到获取此数据的寄存器之间的路径。输入时钟约束经常用”OFFSET IN”约束。指定输入时钟要求的最好方法,取决于接口的类型(源/系统同步)和接口是SDR还是DDR。 OFFSET IN定义了数据和在FPGA引脚抓取此数据的时钟沿之间的关系。在分析OFFSET IN 约束时,时序分析工具自动将影响时钟和数据延迟的因素考虑进去。这些因素包括: 时钟的频率和相位转换 时钟的不确定 数据延迟调整 除了自动调整,还可以在与接口时钟相关的”PERIOD”约束中另外增加时钟不确定。 关于增加”INPUT_JITTER”的更多信息,参见第三章的”PERIOD Constraints”。 “OFFSET IN”与单输入时钟有关,默认情况下,OFFSET IN约束覆盖了从输入pad到内部同步元件之间的所有路径。用于抓取那些从pad输入的数据的同步元件由指定的OFFSET IN 时钟触发。应用OFFSET IN约束被称为”global”方法。这是指定输入时序的最有效的方法。 系统同步输入 在体统同步接口中,发送和抓取数据共用一个系统时钟。板上的布线延迟和时钟倾斜限制了接口的工作频率。更低的频率也会导致系统同步输入接口典型的采用SDR应用。 系统同步SDR应用例子,见图2‐1。系统同步SDR应用中,在时钟上升沿从源器件发送 用Quartus II Timequest Timing Analyzer进行时序分析:实例讲解 (一) (2012-06-21 10:25:54) 转载▼ 标签: 杂谈 一,概述 用Altera的话来讲,timequest timing analyzer是一个功能强大的,ASIC-style的时序分析工具。采用工业标准--SDC(synopsys design contraints)--的约束、分析和报告方法来验证你的设计是否满足时序设计的要求。在用户的角度,从我使用TimeQuest的经验看,它与IC设计中经常用到的比如prime time,time craft等STA软件是比较类似的。用过prime time或time craft的朋友是非常容易上手的。 在这一系列的文章里,我将会拿一个DAC7512控制器的verilog设计作为例子,详细讲解如何使用TimeQuest进行时序设计和分析。 二,TimeQuest的基本操作流程 做为altera FPGA开发流程中的一个组成部分,TimeQuest执行从验证约束到时序仿真的所有工作。Altera推荐使用下面的流程来完成TimeQuest 的操作。 1. 建立项目并加入相关设计文件 不管做什么事情,都需要有一个目标或者说对象。我们用TimeQuest 做时序分析,当然也需要一个对象,这个对象实际上就是我们的设计。所以首先是要建立一个Quartus II的项目,并把所有需要的设计文件都加入到项目中去。需要注意的一点是,这里的设计文件,不仅仅包含逻辑设计相关的文件,也包含已经存在的时序约束文件,当然,需要以synopsys Design Constraints(.sdc)的格式存在的。 2. 对项目进行预编译(initial compilation) 项目建立以后,如果从来没有对项目进行过编译的话,就需要对项目进行预编译。这里的预编译是对应于全编译(full compilation)来讲的,我们可以理解为预编译是对项目进行部分的编译,而全编译是对项目进行完整的编译。做预编译的目的是为了生成一个initial design database, 文献综述 摘要:通过对数据一系列处理,运用三阶自回归AR(3)模型拟合gps坐标时间序列,由于gps坐标时间序列数据之间的相关关系,且历史数据对未来的发展有一定影响,并对未来的电力增长进行预测。理论准备:拿到一个观测值序列之后,首先要判断它的平稳性,通过平稳性检验,序列可分为平稳序列和非平稳序列两大类。如果序列值彼此之间没有任何向关性,那就意味着该序列是一个没有任何记忆的序列,过去的行为对将来的发展没有丝毫影响,这种序列我们称之为纯随机序列,从统计分析的角度而言,纯随机序列式没有任何分析价值的序列。如果序列平稳,通过数据计算进行模型拟合,并利用过去行为对将来的发展预测,这是我们所期望得到的结果。可采用下面的流程操作。 关键字:gps坐标时间序列时间序列分析数据预测 一、前言 GPS坐标时间序列分析原来是“概率论与数理统计”领域当中的一个重要分支,其中有国际著名的学术杂志“时间序列分析”。由于在过去的二十几年当中,时间序列分析方法在经济学的定量分析当中获得了空前的成功应用,因此所出现的“时间序列计量经济学”已经成为了“实证宏观经济学”的同意语或者代名词。由此可见,作为宏观经济研究,甚至已经涉及到微观经济分析,时间序列分析方法是十分重要的。 时间序列分析方法之所以在经济学的实证研究中如此重要,其主要原因是经济数据大多具有时间属性,都可以按照时间顺序构成时间序列,而时间序列分析正是分析这些时间序列数据动态属性和动态相关性的有力工具。从一些典型的研究案例中可以看出,时间序列分析方法在揭示经济变量及其相关性方法取得了重要进展。 目前关于时间序列分析的教科书和专著很多。仅就时间序列本身而言的理论性论著也很多,例如本课程主要参考的Hamilton的“时间序列分析”,以及Box 和Jankins的经典性论著“时间序列分析”;近年来出现了两本专门针对经济学和金融学所编写的时间序列专著,这也是本课程主要参考的教材。另外需要注意的是,随着平稳性时间序列方法的成熟和解决问题所受到的局限性的暴露,目前研究非平稳时间序列的论著也正在出现,其中带有结构性特征的非平稳时间序列分析方法更是受到了广泛重视。 二、本实验采用2000-01~2004-11月gps坐标时间序列数据做时间序列分析模型,数据如下: 2000.1 5.4% 2001.9 8.8% 2003.5 13.4% 2000.2 15.3% 2001.10 8.5% 2003.6 13.1% 2000.3 7.1% 2001.11 7.4% 2003.7 15.2% 2000.4 6.9% 2001.12 9.6% 2003.8 15.5% 2000.5 12.8% 2002.1 15.4% 2003.9 15.5% 2000.6 12.5% 2002.2 -3.2% 2003.10 14.8% 2000.7 13.5% 2002.3 6.2% 2003.11 15.6% 2000.8 10.6% 2002.4 10.6% 2003.12 13.4% 51单片机操作DS18B20汇编源程序 推荐 ; FLAG1:标志位,为"1"时表示检测到DS18B20 ; DQ:DS18B20的数据总线接脚 ; TEMPER_NUM:保存读出的温度数据 ; 本程序仅适合单个DS18B20和51单片机的连接,晶振为12MHZ左右TEMPER_LEQU36H TEMPER_HEQU35H DQBITP1.7 ; DS18B20初始化程序 ;//*****************************************// INIT_1820: SETBDQ NOP CLRDQ MOVR0,#06BH TSR1: DJNZR0,TSR1; 延时 SETBDQ MOVR0,#25H TSR2: JNBDQ,TSR3 DJNZR0,TSR2 LJMPTSR4; 延时 TSR3: SETBFLAG1; 置标志位,表示DS1820存在 LJMPTSR5 TSR4: CLRFLAG1; 清标志位,表示DS1820不存在 LJMPTSR7 TSR5: MOVR0,#06BH TSR6: DJNZR0,TSR6; 延时 TSR7: SETBDQ RET ;//*****************************************// ; 重新写DS18B20暂存存储器设定值 ;//*****************************************// RE_CONFIG: JBFLAG1,RE_CONFIG1; 若DS18B20存在,转RE_CONFIG1 RET RE_CONFIG1: MOVA,#0CCH; 发SKIP ROM命令 LCALLWRITE_1820 MOVA,#4EH; 发写暂存存储器命令 LCALLWRITE_1820 MOVA,#00H; TH(报警上限)中写入00H LCALLWRITE_1820 MOVA,#00H; TL(报警下限)中写入00H LCALLWRITE_1820 MOVA,#1FH; 选择9位温度分辨率 LCALLWRITE_1820 RET ;//*****************************************// ; 读出转换后的温度值 ;//*****************************************// GET_TEMPER: SETBDQ; 定时入口 LCALLINIT_1820 JBFLAG1,TSS2 RET; 若DS18B20不存在则返回 TSS2: MOVA,#0CCH; 跳过ROM匹配 LCALLWRITE_1820 MOVA,#44H; 发出温度转换命令 LCALLWRITE_1820 LCALLINIT_1820 MOVA,#0CCH; 跳过ROM匹配 LCALLWRITE_1820 MOVA,#0BEH; 发出读温度命令 LCALLWRITE_1820 LCALLREAD_1820 MOVTEMPER_NUM,A; 将读出的温度数据保存 RET ;//*****************************************// ; 读DS18B20的程序,从DS18B20中读出一个字节的数据 时间研究在企业中的应用 1国内外文献综述 1.1关于时间研究的缘起 “时间研究”概念,最早由国外学者泰勒提出,泰勒当时提出时间研究的主要目的是改进企业关于相关工序的操作方法,制定科学合理的劳动定额,规范标准,制定标准,实行多劳多得分配方式,通过制定基本标准提高企业生产效率,降低企业生产经营成本。实践证明,由于泰勒的时间研究,企业的生产效率大大提高,造就了企业和员工双赢的局面。后来,在泰勒研究的基础上,吉尔布雷斯夫妇加以创造,对时间研究进行了升华,提出了“动作研究”概念,动作研究,顾名思义,就是对工人的操作动作进行有科学根据的分解,确定为完成工序,工人最基本、必不可少的动作要素,在此基础上,进行科学分析,通过实践,通过测量,找出最省时、最省力、最省工、效率最高的操作动作与操作顺序,根据研究结果,制定企业操作工序,规范操作动作,促进企业生产效率的提高。后人将二者的研究不断升华,不断拓展,形成了一门时间研究学说,对企业的生产造成了深远的影响,促进了现代企业生产方式的变革,造就了企业的高速发展。后人往往将两人的研究合称为“动作时间研究”。 1.2国外文献综述 随着科学技术的进步,企业生产效率逐步提高。但是关于企业生产效率的提高问题,慢慢走向了死胡同,科学技术发展已达到一定水平,单靠科学技术已不能很好促进企业生产效率的提高。企业生产效率提高问题得到国内外相关学者的普遍关注,在此背景下,国外学者首先将思维延伸到非科学技术手段上去,开展了很多理论探索。时间研究,应运而生。 国外关于时间研究方面的探索,可以追溯到20世纪末、21世纪初。时至今日,其研究已经硕果累累,研究团队不断增多,涉及领域不断扩大,研究成果遍地开花,构建了多层次、多视角、多范围的研究体系,学者不断深化理论研究,不断充实实证研究,相关定量研究方法层出不穷,研究成果十分惊人,促进了企业的生产。总结起来,国外关于时间研究方面的实证探索,主要可归纳为两方面,一是时间定额制定方法方面,二是时间模型方面。 1.2.1时间定额制定方法方面 关于时间研究定额制定方法方面,其代表人物主要有Nakayama与Furukawa。Nakayama (2002)提出利用工人工作成就,通过使用商数法这一实证研究方法,来制定相关企业的标准时间,这一方法可以反映企业员工对时序,以及对时序的动态评估方面的个体差异。Furukawa等(2006),通过研制一种装置,评估工时定额,这种装置可以利用存储的一些数据评估工时定额,这些数据包括测试资料表数据,以及技能水平表数据等。 1.2.2时间模型方面 关于时间模型方面的研究,其代表人物主要有Liu与Turkey。Liu等(2005)在研究船舶相关中间产品的标准工时时,使用了简单的线性回归模型、复杂的线性回归模型以及人工神经网络模型等三种模型,来比较可靠准确地估计相关产品的工时,取得了突破性成果。Turkey (2009)以锻造业为例,通过人工神经网络模型,构建不同于以往任何时候的工时测定模型,通过完全覆盖以往数据,可以比较准确地估计类似产品的标准工时。 1.3国内文献综述 我国关于时间研究的探索,起步比较晚,大概起始于21世纪初,而且当时仅仅是介绍相关理论,很少涉及实证研究,实践意义不是很大。我国关于时间研究的探索,取得阶段性成果是在最近十年,主要是因为经过21世纪初不少学者将时间研究理论引进到国内,引起了国内很多学者的重视,而我国企业在经过了几十年的高速发展后,也在这时遇到了瓶颈,亟待通过提高生产效率,促进企业的发展。所以,关于时间研究的探索,有了理论诉求,又 第一部分:DS18B20的封装和管脚定义 首先,我们来认识一下DS18B20这款芯片的外观和针脚定义,DS18B20芯片的常见封装为TO-92,也就是普通直插三极管的样子,当然也可以找到以SO(DS18B20Z)和μSOP(DS18B20U)形式封装的产品,下面为DS18B20各种封装的图示及引脚图。 了解了这些该芯片的封装形式,下面就要说到各个管脚的定义了,如下表即 为该芯片的管脚定义: 上面的表中提到了一个“奇怪”的词——“寄生电源”,那我有必要说明一下了,DS18B20芯片可以工作在“寄生电源模式”下,该模式允许DS18B20工作在无外部电源状态,当总线为高电平时,寄生电源由单总线通过VDD 引脚,此时DS18B20可以从总线“窃取”能量,并将“偷来”的能量储存到寄生电源储能电容(Cpp)中,当总线为低电平时释放能量供给器件工作使用。所以,当DS18B20工作在寄生电源模式时,VDD引脚必须接地。 第二部分:DS18B20的多种电路连接方式 如下面的两张图片所示,分别为外部供电模式下单只和多只DS18B20测温系统的典型电路连接图。 (1)外部供电模式下的单只DS18B20芯片的连接图 (2)外部供电模式下的多只DS18B20芯片的连接图 这里需要说明的是,DS18B20芯片通过达拉斯公司的单总线协议依靠一个单线端口通讯,当全部器件经由一个三态端口或者漏极开路端口与总线连接时,控制线需要连接一个弱上拉电阻。在多只DS18B20连接时,每个DS18B20都拥有一个全球唯一的64位序列号,在这个总线系统中,微处理器依靠每个器件独有的64位片序列号辨认总线上的器件和记录总线上的器件地址,从而允许多只DS18B20同时连接在一条单线总线上,因此,可以很轻松地利用一个微处理器去控制很多分布在不同区域的DS18B20,这一特性在环境控制、探测建 第1章FPGA中IO口时序分析 作者:屋檐下的龙卷风 博客地址:https://www.doczj.com/doc/dc3081828.html,/linjie-swust/ 日期:2012.3.1 1.1 概述 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。 1.2 FPGA整体概念 由于IO口时序约束分析是针对于电路板整个系统进行时序分析,所以FPGA需要作为一个整体分析,其中包括FPGA的建立时间、保持时间以及传输延时。传统的建立时间、保持时间以及传输延时都是针对寄存器形式的分析。但是针对整个系统FPGA的建立时间保持时间可以简化。 图1.1 FPGA整体时序图 如图1.1所示,为分解的FPGA内部寄存器的性能参数: (1) Tdin为从FPGA的IO口到FPGA内部寄存器输入端的延时; (2) Tclk为从FPGA的IO口到FPGA内部寄存器时钟端的延时; (3) Tus/Th为FPGA内部寄存器的建立时间和保持时间; (4) Tco为FPGA内部寄存器传输时间; (5) Tout为从FPGA寄存器输出到IO口输出的延时; 对于整个FPGA系统分析,可以重新定义这些参数:FPGA建立时间可以定义为:(1) FPGA建立时间:FTsu = Tdin + Tsu – Tclk; (2) FPGA保持时间:FTh = Th + Tclk; (3) FPGA数据传输时间:FTco = Tclk + Tco + Tout; 由上分析当FPGA成为一个系统后即可进行IO时序分析了。FPGA模型变为如图1.2所示。 最近天气热了,想要是做个能显示温度的小设备就好了,于是想到DIY个电子温度计,网上找了很多资料,结合自己的材料,设计了这个用单片机控制的实时电子温度计。作为单片机小虾的我做这个用了2天时间,当然是下班后,做工不行见谅了。 主要元件用到了单片机STC89C54RD+,DB18B20温度传感器,4为共阳数码管,PNPS8550三极管等。 先上原理图: 洞洞板布局图: 然后就是实物图了: 附上源程序:程序是别人写的,我只是自己修改了下,先谢谢原程序者的无私奉献。#include"reg52.h" #define uchar unsigned char #define uint unsigned int sbit DQ=P3^4; //温度数据口 sbit wx1=P2^0; //位选1 sbit wx2=P2^1; //位选2 sbit wx3=P2^2; //位选3 sbit wx4=P2^3; //位选4 unsigned int temp, temp1,temp2, xs; uchar code table[]={0xc0,0xf9,0xa4,0xb0,0x99, //共阳数码管0x92,0x82,0xf8,0x80,0x90,0x88,0x83,0xc6}; /******延时程序*******/ void delay1(unsigned int m) { unsigned int i,j; for(i=m;i>0;i--) for(j=110;j>0;j--); } void delay(unsigned int m) //温度延时程序 { while(m--); } void Init_DS18B20() { unsigned char x=0; DQ = 1; //DQ复位ds18b20通信端口 delay(8); //稍做延时 DQ = 0; //单片机将DQ拉低 delay(80); //精确延时大于480us DQ = 1; //拉高总线 delay(4); x=DQ; //稍做延时后如果x=0则初始化成功x=1则初始化失败delay(20); } /***********ds18b20读一个字节**************/ uchar ReadOneChar() { unsigned char i=0; unsigned char dat = 0; for (i=8;i>0;i--) {时序分析基础与时钟约束实例1

DS18B20温度检测程序

文献综述的类型

ASIC时序约束、时序分析

时间序列分析——最经典的

时序约束

DS18B20单片机数码管显示原理图和程序

时间序列分析开题报告

DS18B20中文资料--最全版

XILINX-时序约束使用指南中文

时序约束实例

GPS坐标时间序列论文文献综述

51单片机操作DS18B20汇编源程序

文献综述

DS18B20中文资料

FPGA中IO时序约束分析

DS18B20 单片机数码管显示原理图和程序