倒装芯片封装结构中SnAgCu 焊点热疲劳寿命预测方法研究

THERMO -FATIGUE LIFE PREDICTION METHODOLOGIES FOR

SnAgCu SOLDER JOINTS IN FLIP -CHIP ASSEMBLIES

李晓延 王志升

(北京工业大学材料学院,北京100022)

LI XiaoYan WANG ZhiSheng

(School of M ate rials Scienc e and Engineering ,Beijing Unive rsity of Technology ,Beijing 100022,China )

摘要 由于焊点区非协调变形导致的热疲劳失效是倒装芯片封装(包括无铅封装)结构的主要失效形式。到目前为止,仍无公认的焊点寿命和可靠性的评价方法。文中分别采用双指数和双曲正弦本构模型描述SnAgCu 焊点的变形行为,通过有限元方法计算焊点累积蠕变应变和累积蠕变应变能密度,进而据此预测倒装芯片封装焊点的热疲劳寿命。通过实验验证,评价上述预测方法的可行性。结果表明,倒装芯片的寿命可由芯片角焊点的寿命表征;根据累积蠕变应变能密度预测的焊点热疲劳寿命比根据累积蠕变应变预测的焊点热疲劳寿命更接近实测数据;根据累积蠕变应变预测的热疲劳寿命比根据累积蠕变应变能密度预测的热疲劳寿命长;采用双指数本构模型时,预测的焊点热疲劳寿命也较长。

关键词 热疲劳 寿命预测 倒装芯片焊点 无铅化中图分类号 TG407 O346.2 TB114.3

A bstract Thermal fatigue failure ,due to the fracture of solder joints which was caused by the mis match deformation ,is frequentl y encountered in flip chip (FC )assemblies .Unfortunately ,there is n o widel y accepted method to evaluate the reliability of solder joints ,especially for lead -free solder joints ,in s uch assemblies up to now .The constitutive models of double power law and the hyperbolic sine law were implemented to simulate the deformation of Sn AgCu solder joints in flip chip assemblies .The accumulated creep strain and ac -cu mulated creep strain energy dens ity of the solder joints were calculated ,via finite element method ,and were use to predict the thermal fatigue life of flip chip assemblies .The applicability of the above life prediction methods was evaluated through cross check of the present results with that of the literatures .It was found that the life of the FC assemblies could be estimated by the prediction of the life of the corner solder joints .The thermal fatigue life ,estimated according to accumulated creep strain energy density is closer to the test data than that of the life estimated according to accumulated creep strain .The life predicated according to accumulated creep strain shown a slightly high value than that predicated accordin g to accumulated creep strain energy density .The double power law constitutive equation results in a higher predicted life .

Key words Themo -fatigue ;Life prediction ;Flip chip ;Solder joint ;Lead free Corr es ponding autho r :LI Xiao Yan ,E -mail :xyli @bjut .edu .cn

The project supported b y the National Natural Science Foundation of China (No .50475043),Nature Science Foundation of Beijin g (2052006)and the Specialized Research Fund for the Doctoral Program of Higher Education of China (No .20040005012).

Manuscript received 20060712,in revised form 20060831.

1 引言

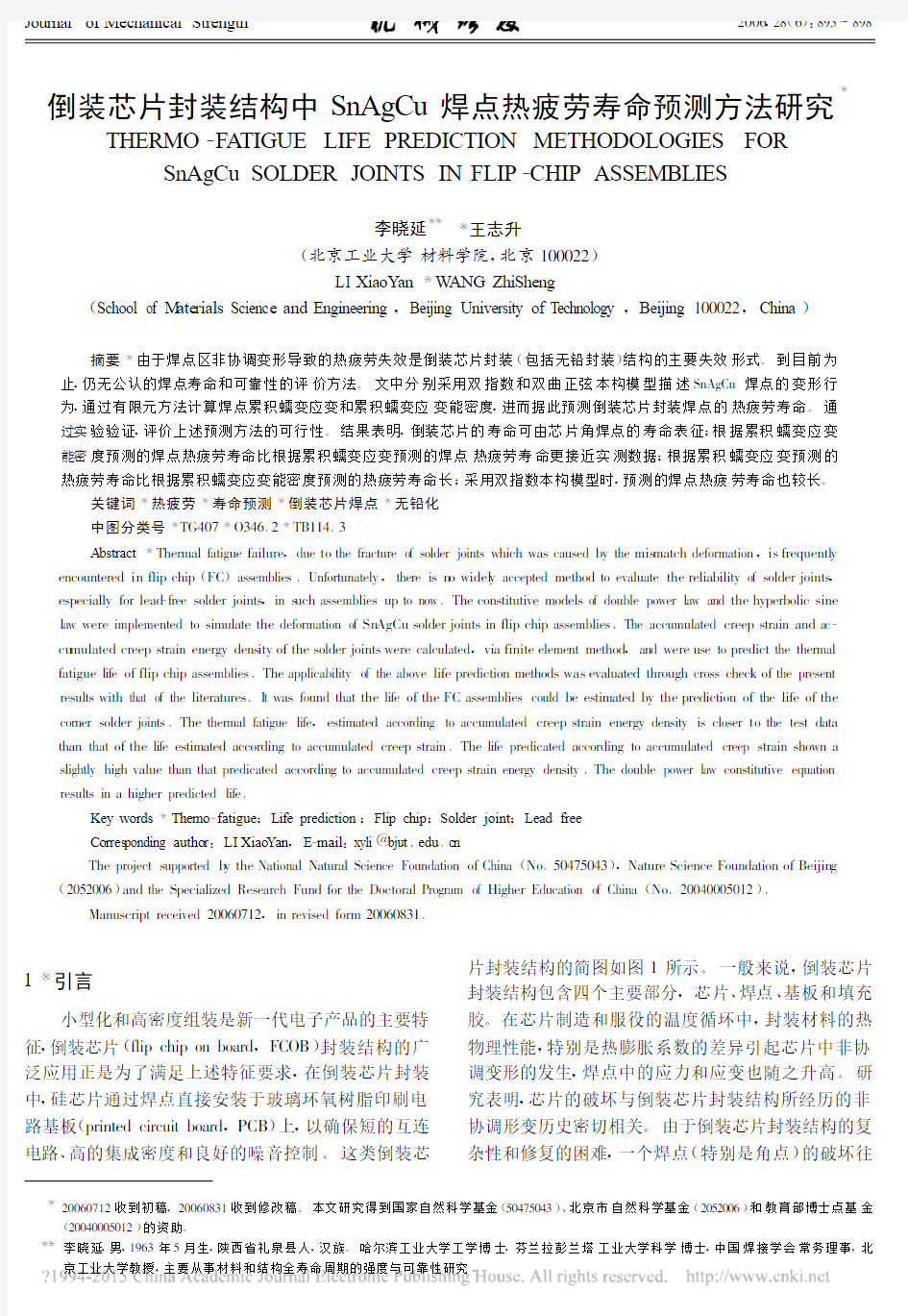

小型化和高密度组装是新一代电子产品的主要特征,倒装芯片(flip chip on board ,FCOB )封装结构的广

泛应用正是为了满足上述特征要求,在倒装芯片封装中,硅芯片通过焊点直接安装于玻璃环氧树脂印刷电路基板(printed circuit board ,PCB )上,以确保短的互连电路、高的集成密度和良好的噪音控制。这类倒装芯

片封装结构的简图如图1所示。一般来说,倒装芯片

封装结构包含四个主要部分,芯片、焊点、基板和填充胶。在芯片制造和服役的温度循环中,封装材料的热物理性能,特别是热膨胀系数的差异引起芯片中非协调变形的发生,焊点中的应力和应变也随之升高。研究表明,芯片的破坏与倒装芯片封装结构所经历的非协调形变历史密切相关。由于倒装芯片封装结构的复杂性和修复的困难,一个焊点(特别是角点)

的破坏往

Journal of Mechanical Strength

2006,28(6):893~898

李晓延,男,1963年5月生,陕西省礼泉县人,汉族。哈尔滨工业大学工学博士,芬兰拉彭兰塔工业大学科学博士,中国焊接学会常务理事,北

京工业大学教授,主要从事材料和结构全寿命周期的强度与可靠性研究。

20060712收到初稿,20060831收到修改稿。本文研究得到国家自然科学基金(50475043)、北京市自然科学基金(2052006)和教育部博士点基金

(20040005012)的资助。

往导致整个封装结构的失效[1]

。从这一意义上看,倒装芯片封装结构的热疲劳寿命由其角焊点的热疲劳寿命决定

。

图1 倒装芯片封装结构简图

Fig .1 Solder bumped flip chip on board ass embly

对SnPb 焊料焊点破坏行为及寿命的研究已有多年的基础,许多寿命预测方法被不同的研究者采用,以基于蠕变应变的的寿命方法[2,3]

和基于能量的方法

[4,5]

获得的应用最多。对新一代电子产品,由于环境保护的压力和相关法规的要求,封装的无铅化是基本要求。目前,虽然国内外有关无铅焊料开发、焊接工艺和焊点可靠性的研究已有不少报道,但能否将用于描述SnPb 焊料焊点破坏和寿命的规律直接应用到SnAgCu 系无铅焊料焊点上,仍无理论和实践的保证,其原因一方面是描述SnPb 焊料应力应变行为的本构关系并不一定适用于无铅焊料合金系统;另一方面,无铅焊料焊点的破坏行为与SnPb 焊料焊点的破坏行为并不完全相同。无疑,开展无铅焊料焊点破坏行为和寿命规律的研究对于理解无铅焊料焊点的破坏机理、预测其可靠服役寿命有重要的理论和实际意义。

要进行焊点寿命的预测,通常首先应确定焊点应力应变分布,然后计算非弹性应变和非弹性应变能密度的累积,最后依据热循环过程中非弹性应变或非弹性应变能密度的累积估算焊点的热疲劳寿命。基于上述思路,已有一些预测焊点可靠性和寿命的经验公式

被报道和应用[6~21]

。对本文的研究,由于尚无描述SnAgCu 系无铅焊料应力应变响应的公认的本构关系,在研究中,分别采用双指数本构模型和双曲正弦本构模型描述倒装芯片封装中SnAgCu 系合金焊点的应力应变行为,进而通过有限元方法计算焊点热循环过程中蠕变应变和蠕变应变能的累积,并据此估算焊点的热疲劳寿命。本文研究的主要目的在于评价将用于SnPb 焊料焊点上的本构关系及寿命计算的经验公式应用于SnAgCu 无铅焊料焊点寿命预测的可行性。

2 应力应变分析

在电子封装领域,有限元分析广泛应用于模拟热循环条件下焊点失效的物理过程。应用有限元方法研

究倒装芯片封装中热力耦合条件下的形变响应也有不

少文献报道,主要的研究集中在倒装芯片封装结构的应力分析[22~25]

、焊点界面的失效行为

[26~28]

、有限元参

量的研究[29]

等方面。

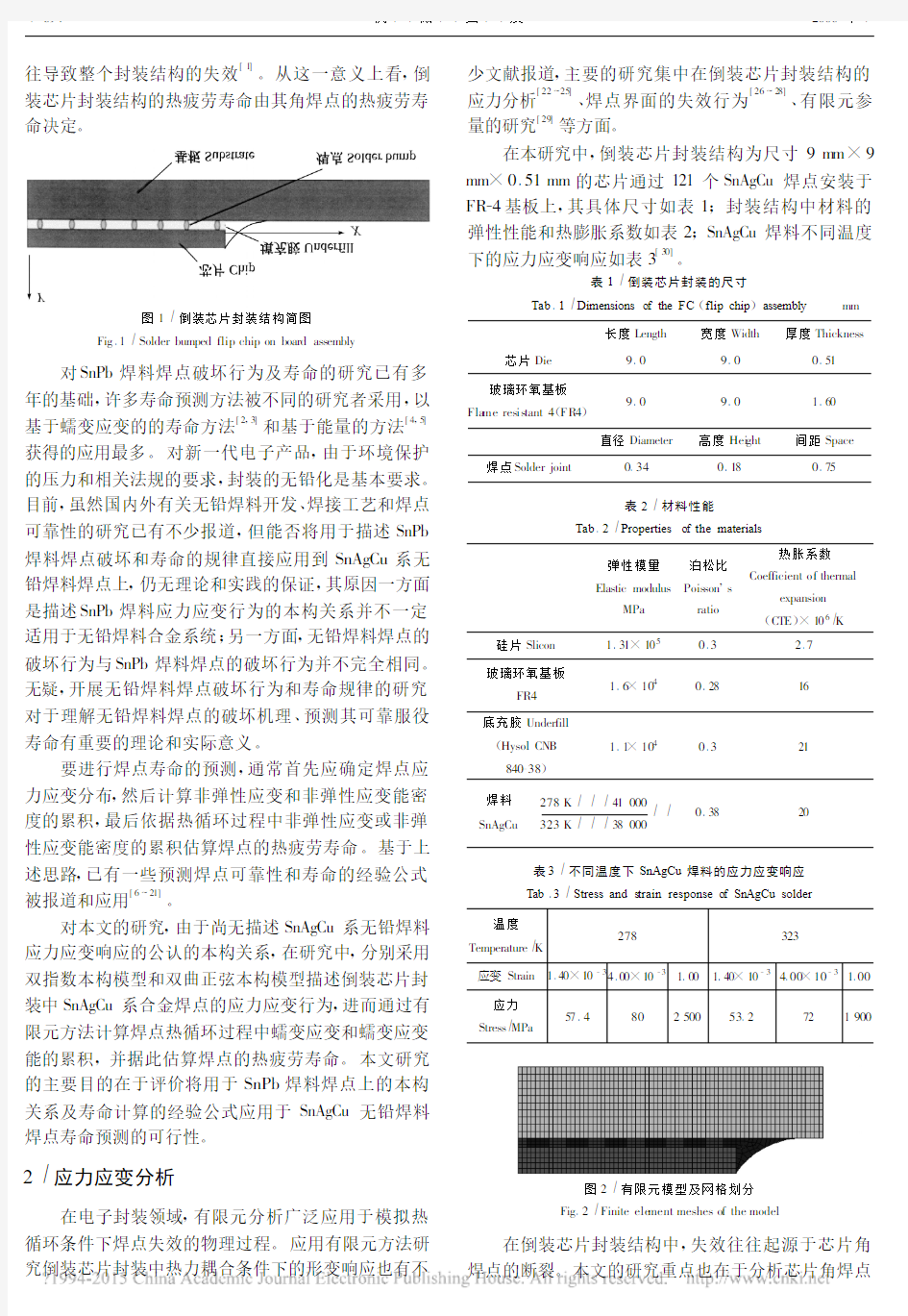

在本研究中,倒装芯片封装结构为尺寸9m m ×9mm ×0.51mm 的芯片通过121个SnAgCu 焊点安装于FR -4基板上,其具体尺寸如表1;封装结构中材料的弹性性能和热膨胀系数如表2;SnAgCu 焊料不同温度下的应力应变响应如表3

[30]

。

表1 倒装芯片封装的尺寸

T ab .1 Dimensions of the FC (flip chip )assembly

mm

长度Length

宽度Width

厚度Thicknes s

芯片Die 9.09.00.51玻璃环氧基板Fla me res is tant 4(FR 4)

9.09.01.60直径Diameter

高度Hei ght 间距Space 焊点Solder joint

0.34

0.18

0.75

表2 材料性能

T ab .2 Properties of the materials

弹性模量Elastic modulus MPa

泊松比Pois son 's

ratio 热胀系数Coefficient of thermal

expansion (CTE )×106 K

硅片Slicon 1.31×1050.32.7玻璃环氧基板

FR41.6×104

0.28

16

底充胶Underfill (Hysol CNB 840-38)1.1×104

0.3

21

焊料SnAgCu

278K 41000323K 38000

0.38

20

表3 不同温度下SnAgCu 焊料的应力应变响应Tab .3 Stress and s train res ponse of Sn AgCu solder 温度Temperature K

278

323

应变Strain 1.40×10-34.00×10-3

1.001.40×10-34.00×10-31.00

应力Stress MPa

57.480250053.2721900

图2 有限元模型及网格划分Fig .2 Finite ele ment meshes of the model

在倒装芯片封装结构中,失效往往起源于芯片角

焊点的断裂。本文的研究重点也在于分析芯片角焊点

894

机 械 强 度2006年

图3 芯片角焊点上下表面承受的剪切位移Fig .3 Shearing dis placement changes on the top s ide

and bottom s ide of the corner sol der j

oint

图4 单焊点模型及其有限元网格

Fig .4 Single joint model and its FE (finite ele ment )meshes

的应力应变状态,为此,首先分析芯片结构在热循环作用下的整体变形,以便确定芯片角焊点在热循环过程中实际承受的剪切位移载荷。对正方形倒装芯片封装结构,四个角点处的焊点承受最恶劣的服役载荷,本文在芯片对角线方向上建立平面应变二维有限元模型,模拟芯片的整体变形行为。由于结构的对称性,有限元分析对封装结构的一半进行。有限元模型及网格划分如图2,有限元分析采用MARC 软件进行。

在进行倒装芯片封装结构的整体变形分析时,假设硅芯片、玻璃环氧树脂基板以及底填充胶遵循各向同性、线弹性形变规律,变形过程中材料的热物理性能和力学性能不随温度变化。但对SnAgCu 焊料,认为材料变形遵循弹塑性形变规律。温度载荷变化范围为125℃~-40℃。在计算过程中,认为初始温度125℃时封装结构处于零应力状态,然后均匀降温到-40℃,结构中不存在不均匀温度梯度。在上述条件下冷却时,角焊点上下表面所承受的剪切位移载荷如图3。

以上述整体分析中获得的剪切位移差为外加机械载荷,倒装芯片角焊点所经历的热力耦合形变过程可在图4所示的模型上采用三维有限元方法进行分析。

温度载荷如图5所示。温度区间为-40℃~+

125℃,

图5 温度荷载循环

Fig .5 Profil e of temperature c ycling

图6 剪切位移循环

Fi g .6 Profile of shearing dis placement c ycling

加热 冷却速率为11℃ 分钟,保温时间为15分钟。

在上述温度循环条件下,倒装芯片封装结构整体分析所获得的芯片角焊点所承受的剪切位移载荷循环

如图6。在进行单焊点的热力疲劳详细分析时,图5和图6所示的温度载荷和位移载荷同步施加,热力耦合为同相位耦合。

对大多数工程材料,在加载速率较小时,如果归一化温度(实际服役绝对温度 理论熔点绝对温度)大于0.5,蠕变将在变形中起重要作用。对SnAgCu 系焊料合金,在-40℃时的归一化温度约为0.47,蠕变无疑是其服役中的主要形变。在进行单焊点的热力耦合形变分析时,将以热弹塑性蠕变本构关系描述SnAgCu 焊点的形变行为。

在对SnAgCu 系无铅焊料的研究中,不同的学者已提出多种本构关系表达式来描述焊料的应力应变行为,其中Wise

[31]

提出双指数关系在描述焊料在低应力

条件下以位错攀移机制为主导的蠕变行为和高应力条

件下以滑移和攀移联合主导的蠕变行为上得到不少学者的认同,这一关系的表达式如方程(1)。另一个得到认同的本构关系是Schubert

[32]

提出的双曲正弦模型,

这一关系可描述高应力条件下应力应变的指数规律,这一关系的表达式见方程(2)。在本文的研究中,上述εcr =A 12

(1)

第28卷第6期李晓延等:倒装芯片封装结构中SnAgCu 焊点热疲劳寿命预测方法研究895

其中,A 1=4×10-7

s -1

,H 1 k =3223,n 1=3.0,

A 2=10

-12

s -1

,H 2 k =7348,n 2=12,σn =1MPa εcr =A 1[sinh (ασ)]n

exp

-H 1

kT

(2)

其中,A 1=277984s -1

,α=0.02447MPa ,n =6.41,H 1 k =6500

依据双指数本构关系和双曲正弦本构关系计算所得的蠕变回线分别如图7和图8。可以看出,在经历第

一热力循环后,两种情况下的蠕变回线均趋于稳定。从图7和图8可确定累积的蠕变应变,在采用双指数规律时,累积蠕变应变为0.

0102,在采用双曲正弦规律时,累积蠕变应变为0.0100。

图7 基于双指数规律的蠕变回线

Fig .7 Creep hysteresis loops according to double power law

图8 基于双曲正弦关系的蠕变回线

Fig .8 Creep hys teresis loops according to hyperbolic sine law

3 寿命预测

目前,对焊点破坏和寿命的研究已引起国内外学者的广泛关注,提出了SnPb 焊料和SnAgCu 焊料寿命的不同模型,这些模型或者以应变幅为表征参量,或者以累积蠕变应变为表征参量,或者以累积蠕变应变能密度为表征参量。在这些模型中,美国Amkor 公司Syed

[33,34]

提出的基于累积蠕变应变和基于累积蠕变应

变能密度的寿命模型得到较多关注和应用。根据Syed

模型,蠕变是控制SnAgCu 焊料损伤的主要机制,蠕变是描述焊料损伤行为的单一参量,因而寿命预测也应以蠕变变形为基础。Syed 模型认为,循环载荷是蠕变的特殊形式,只不过蠕变是在顺序加载或重复加载的情况下发生。这样,以累积蠕变应变为基础的寿命方程可简化为

N f =(C ′εacc )

-1

(3)

其中,N f 是失效时的循环数,εacc 是每一循环累积的蠕变应变,C ′=1 εf 是蠕变延性的倒数,εf 是表达蠕变延性的常数。

以累积蠕变应变能密度为表征参量的焊点寿命方程可简化为

N f =(W ′w acc )

-1

(4)

其中,N f 是失效时的循环数,w acc 是每一循环累积的蠕变应变能密度,W ′是失效时的蠕变应变能密度。

图9 根据双指数规律计算得到的蠕变应变能密度Fig .9 The creep strain energy density evaluated according

to double power law

图10 根据双曲正弦规律计算得到的蠕变应变能密度Fig .10 The creep strain energy density evaluated according

to hyperbolic sine law

在本文的研究中,分别按照双指数规律(方程(1))

和双曲正弦规律(方程(2))计算焊点的蠕变应变能历史,其结果如图9和图10。从这两图上可获得稳定蠕变时蠕变应变能密度的幅值。采用双指数材料模型时,每一循环的累积蠕变应变能密度为0.362MPa ,采用双曲正弦材料模型时,每一循环累积的蠕变应变能密度为

896

机 械 强 度2006年

0.295MPa。

在获得了累积蠕变应变和累积蠕变应变能密度后,可依据方程(3)和方程(4)计算焊点的热力疲劳寿命,材料常数采用文献[34]中相同材料的实验数据,其结果如表4。从表4可以看出,依据累积蠕变应变预测的寿命较依据累积蠕变应变能密度预测的寿命长。

表4 SnAgCu焊点的预测寿命

Tab.4 Predicted life of SnAgCu solder joint

寿命模型Life model 寿命预测结果Predicted life

cycle

双指数规律Double power law

基于累积蠕变应变

According to accumulated

creep strain

2095

基于累积蠕变应变能密度

According to accumulated

creep strain energy density

1842

双曲正弦规律Hyperbolic

sine law

基于累积蠕变应变

According to accumulated

creep strain

1949

基于累积蠕变应变能密度

According to accumulated

creep strain energy density

1784

为了验证本文预测方法的可靠性,将本文的预测方法应用于文献[34]的CB GA(ceramic ball grid array)封装结构,并将预测结果与文献[34]的实验结果进行比较。文献[34]的研究对象是一个CBGA实验样品,上层的陶瓷芯片为8mm×8mm,有64个SnAgCu焊料焊点,焊点下面与PCB相连,其材料为FR-4树脂,热循环加载条件为125℃~-40℃,该CB GA结构的尺寸如表5所示。

本文预测结果与文献[34]实验结果的比较如表6。可以看出,在应用双曲正弦规律描述SnAgCu焊料的本构关系时,根据焊点累积蠕变应变能密度预测的倒装芯片热疲劳寿命与实验测量寿命良好吻合。同时发现,依据累积蠕变应变所预测的寿命均高于依据累积蠕变应变能密度所预测的寿命,采用双指数规律的材料本构模型时,所预测的寿命高于采用双曲正弦本构模型所预测的寿命,也高于实验测得的寿命。

表5 CBGA封装的尺寸[34]

Tab.5 Dimens ions of the CBGA assemb l y[34]mm

厚度Thickness 芯片Die玻璃环氧基板FR4

1.01.6

焊点Solder joint 直径Diameter高度Height间距Space

0.460.30.8

表6 CBG A封装结构预测寿命与实验寿命的比较

Tab.6 Comparison of the predicted life of a CBGA assemble

with that of tes ted data

寿命模型

Life model

预测寿命

Predicted

life c ycle

实验寿命[34]

Life of test[34]

双指数

规律

Double

power

law

基于累积蠕变应变

According to accumulated

creep strain

514

基于累积蠕变应变能密度

According to accumulated

creep s train energy density

439

最短

寿命

1st

fail ure

Weibull

表征

寿命

Weibull

char.life

平均

寿命

M ean

life

双曲正

弦规律

Hyperbolic

sine law

基于累积蠕变应变

According to accumulated

creep strain

489

基于累积蠕变应变能密度

According to accumulated

creep s train energy density

318

445417417

4 结论

本文分别采用双指数材料本构关系和双曲正弦本

构关系,根据热力疲劳条件下的累积蠕变应变和累积

蠕变应变能密度对倒装芯片结构的热疲劳寿命进行预

测,考察以芯片角焊点寿命表征芯片寿命的合理性。获

得如下主要结论:

1)倒装芯片的热疲劳寿命由其角焊点的寿命决

定,芯片的寿命预测可以通过对芯片角焊点寿命的预

测实现。

2)采用双曲正弦本构模型,依据累积蠕变应变能

密度所预测的热疲劳寿命与实际测试寿命最为接近。

3)依据累积蠕变应变所预测的寿命均高于依据

累积蠕变应变能密度所预测的寿命,采用双指数规律

的材料本构模型时,所预测的寿命高于采用双曲正弦

本构模型所预测的寿命,也高于实验测得的寿命。

致谢

本文的研究得到国家自然科学基金(50475043)、

北京市自然科学基金(2052006)和教育部博士点基金

(20040005012)的资助。

References

1 IPC-Ass ociation Connecting Electronics Industries.Performance and

reliability test methods for flip chip,chip scale,BGA and other surface

mount array package applications.U SA:Published by IPC,J-STD-029,

Feb.,2000.

2 Knecht S,Fox L R.Constitutive relation and creep-fatigue life model for

eutectic tin-lead solder.IEEE https://www.doczj.com/doc/c69453546.html,pon.,Hybrids,Manuf.

Technol.,1990,13(2):424~433.

3 Syed A.Solder joint life prediction model and application to ball grid

array des ign optimization.Proc.Experimental Numerical Mechanics in

Electronic Packaging,Nashville,TN,USA,SEM,1996,1:136~144.

第28卷第6期李晓延等:倒装芯片封装结构中SnAgCu焊点热疲劳寿命预测方法研究897

4 Akay H,Zhang H,Paydar N.Experimental correlations of an energy-based fatigue life prediction method for solder joints.Advance in Electronic Packaging,Proc.of the Pacific R im ASME International Intersociety Electronic and Photonic Packaging Conference, InterPack'97,Now York,USA,1997,2:1567~1574.

5 Darveaux R.Solder joint fatigue life model,in design and reliability of s olders and solder interconnections.Orlando,Florida,USA:The Minerals,Metals and Materials Society(TMS),1997.213~218.

6 Lau John H,Pao Yi-Hsin.Solder joints reliability of BGA,CSP,flip chip,and fine pitch SMT assemblies.New York,USA:M cGraw-Hill, 1997.

7 Pang J ohn H L,Chong D Y,Low T H.Thermal cycling anal ysis of flip-chip solder j oint reliability.IEEE Trans actions on Components and Packaging Technologies,2001,24(4):705~712.

8 Vianco P T,Burchett S.N.Solder joint reliability predictions for leadless chip resistors,chip capacitors,and ferrite chip inductors using the SRS T M software.Sandia Report,SAND2001-1665,Sandia National Laboratories,California,USA,August2001.

9 Shi X Q,Yang Q J,Wang Z P,et al.New creep constitutive relationship and modified energy-based life prediction model for eutectic s older alloys.Singapore:Singapore Institute of Manufacturing Technology,SIMTech Technical R eport(PT01021J T),2003.

10 Lee S W R icky,Zhang X.Sensitivity s tudy on material properties for the fatigue life prediction of solder joints under c yclic thermal loading.

Circuit World,1998,24(3):26~31.

11 Lee W W,Nguyen L T,Selvaduray G S.Solder joint fatigue models: review and applicability to chip scale packages.M icroelectronics Reliability,2000,44:231~244.

12 Towashiraporn P,Subbarayan G,M cIlvanie B,et al.The effect of model building on the accuracy of fatigue life prediction.Thermal and Thermomechanical Phenomena in Electronic System,ITHERM2002, the Eighth Inters ociety Conference,San Diego,CA,USA,M ay29-June1,2002.854~861.

13 Stoyanov S,Bailey C,Lu H,et al.Solder joint reliability optimiz ation.

Conference on Advances in Packaging,Singapore,APACK2001,ISBN 981-04-4638-1.2001.178~186.

14 Solomon J D.Fatigue of6040solder.IEEE Transaction on Component, Hybrid,and M anufacturing Technology,1986,CHMT-9:423~433. 15 Pang J H L,Seetoh C W,Wang Z P.CBGA solder joint reliability evaluation based on elastic-plastic-creep anal ysis.Transaction of ASME,Journal of Electronic Packaging,2000,122:255~261.

16 Engelmaier W.Fatigue life of leadless chip carrier solder joints during power cycling.IEEE Trans action on Component,Hybrid,and Manufacturing Technology,1984,6(3):232~237.

17 Norris K C,Landzberg A H.R eliability of controlled collapse interconnections.IBM Journal of Res earch and Development,1969,13: 266~271.

18 Lau J H,Chang C,Lee S W R.Solder joint crack propagation analysis of wafer level chip scale package on printed circuit board assemblies.

IEEE Transaction on Component,Hybrid,and Manufacturing Technology,2001,24(2):285~292.

19 Pao Y H.A fracture mechanics approach to thermal fatigue life prediction of s older joints.IEEE Transaction on Component,Hybrid, and M anufacturing Technology,1992,15(4):559~570.20 Syed A.Reliability of lead-free solder connections for area array packages.Presented at IP SM EMA APEX SM2001,San Diego,CA, USA,Jan.14-18,2001LF2-7:1~9.

21 LI XiaoYan,YAN YongChang.Reliability and life prediction methodologies for solder joint of electronic packages.Journal of Mechanical Strength,2005,27(4):470~479(In Chinese)(李晓延,严永长.电子封装焊点可靠性及寿命预测方法.机械强度,2005, 27(4):470~479).

22 Peterson D W,Sweet J N,Burchett S N,et al.S tresses from flip-chip assembly and underfill;meas urements with ATC4.1assembly test chip and analysis by finite element method.Proc.47th Electronic Components and Technology Conf.,San Jose,CA,USA,1997.134~

143.

23 Zhao J H,Dai X,Ho P S.Anal ysis and modeling verification for thermal-mechanical deformation in flip-chip packages.Proc.48th Electronic Components and Technology Conf.,Seattle,WA,USA, 1998.336~344.

24 Michaelides S,Sitaraman S K.Die cracking and reliable die des ign for flip-chip ass emblies.IEEE Trans,Adv.Packag.,1999,26(1):795~

801.

25 Pang J ohn H L,Chong D Y R,Low T H.Thermal cycling analysis of flip-chip solder joint reliability.IEEE https://www.doczj.com/doc/c69453546.html,ponents and Packaging Technologies,2001,24(4):705~712.

26 Yan X,Agarwal RK.Two test specimens for determining the interfacial fracture toughness in flip-chip assemblies.ASM E J.Electron.

Packag.,1998,120:150~155.

27 Park J E,Jasiuk I,Zubelewicz A.Stress es and fracture at the chip underfill interface in flip-chip assemblies.ASME J.Electron.

Packag.,2003,125:44~52.

28 LI XiaoYan,YAN YongChang,SHI YaoWu.Influence of IMC on the interface failure of tin-silver-copper solder joints.Journal of Mechanical Strength,2005,27(5):666~671(In Chinese)(李晓延,严永长,史耀武.金属间化合物对SnAgCu Cu界面破坏行为的影响.机械强度,2005,27(5):666~671).

29 Yeh C P,Zhou W X,Wyatt K.Parametric finite element analysis of flip-chip s tructures.Int.J.Microcircuits Electron.Packag.,1996, 19:120~127.

30 Wiese S,R zepka S.Time-independent elastic plastic behaviour of s older materials.Microelectronics Reliability,2004,44:1893~

1900.

31 Wise S,M eusel E,Wolter K.Microstructural dependence of constitutive properties of eutectic SnAg and SnAgC solders.53rd ECTC 2003,New Orleans,Louisiana,USA,May27-30,2003.197~206. 32 Schubert A,Dudek R,Auerswald E,et al.Fatigue life models of SnAgCu and SnPb solder joints evaluated by experiments and s imulations.53rd ECTC2003,New Orleans,Louisiana,USA,M ay 27-30,2003.630~610.

33 Syed A.ACES of finite element and life prediction models for solders and solder interconnections.Proc.Symp.TMS Conf.,Interlaken, Switzerland,August11-15,1997.347~355.

34 Syed A.Accumulated creep strain and energy density bas ed thermal fatigue life prediction models for SnAgCu solder joints.54th ECTC 2004,Las Vegas,Nevada,USA,June1-4,2004.737~746.

898机 械 强 度2006年

工程预测焊点疲劳寿命 介绍了一种预测焊点疲劳寿命的工程计算方法及其软件系统。这一方法用有限元中的刚性梁单元模拟焊核,用壳单元模拟连接板,求取通过梁单元传递的力和力矩;根据这些力和力矩计算焊核附近连接板和焊核周围的“结构应力”;然后通过一组以结构应力为控制参数的焊点S—N曲线估计焊点的疲劳损伤。描述了软件系统的框架和特点,用两个简单的例子说明这一方法的应用。结果表明,分析结果与试验结果相比有一定的保守性。 在汽车工业中,点焊被广泛地用于零部件和结构的制造。点焊构件的耐久性主要取决于焊点的疲劳强度。在一条生产自动线上装备一个焊点的点焊机械装置可能需要30万美元,为了补救某一问题而必须在生产时再增加一个点焊装置,其费用可能不止2倍。如果我们能在设计的早期预测焊点的疲劳寿命,那么显然这些费用可以降到最低点。更有意义的是,它也有助于缩短产品的开发周期,提高产品的质量。 Smith和Cooper用断裂力学方法研究过受剪切载荷焊点的疲劳寿命预测问题。他们指出:“一个焊点也许可以被认为是一个外表面有一环向深裂纹的实心圆棒,当这一圆棒受一个Ⅰ—Ⅱ复合型载荷时,它会在最大的局部Ⅰ型方向产生分叉裂纹并扩展”。他们说明了根据计算的裂纹扩展速率可以较好地预测焊点的疲劳寿命,并用他们的计算结果作出一些简单的设计曲线。Smith和Cooper所建议的方法基于对简单受剪搭接接头的有限元模拟,这种方法需要进一步的发展才能用于其它不同的焊点型式,处理变幅异相复杂载荷。发展的结

果可能是一个简单的专门针对焊点的规范,按照英国标准BS7608的方法,给出适用于不同点焊类型的载荷—寿命曲线族。 事实上,关联不同加载条件下焊点的疲劳强度,载荷是一个相当糟糕的参量。Raji和Sheppard提到,不同型式受不同载荷的焊点,它的疲劳耐久性能够通过分析板内焊点周边的局部应力得到更好的理解,这一局部应力指的是焊点附近的结构应力。Rupp等人描述了如何计算这些结构应力。他们根据最大应力、最小应力和一个载荷谱对焊点的疲劳寿命进行了预测。本文介绍的技术类似于Rupp等人的工作,不同的是进一步地将结构应力计算与应力缩放、叠加以及应用瞬态有限元分析结果等方法结合起来。下面将先介绍软件的技术细节,然后给出两个说明简例。 1 方法概述 方法要求将焊点模拟成为MSC/NASTRAN中的刚性梁单元;经这些梁单元传递的力和力矩被用来计算结构(名义)应力,这些应力为围绕焊点熔核和连接板的局部应力;按照S—N总寿命方法,用这些结构应力预估焊点的疲劳寿命。 软件系统由一些经过修改的MSC/FATIGUE模块组成,它的核心为焊点疲劳分析器SPOTW,图1表示了这一软件的框架。该系统当前只支持两板焊点的疲劳计算。焊点应当用连接两板中面且垂直于这两个中面的刚性梁表达,而板用位于板中面的壳单元模拟。焊点的长度因此是板厚之和的一半。焊点附近的网格不需要做任何细化,对壳单元的唯一要求是它们能将正确的力传至刚性梁。事实上,使用大尺寸的壳单元(大于2倍的熔核直径)似乎能获得最好的结果,即最

收稿日期:2007-07-09基金项目:国家“863”高技术研究发展计划资助项目(2006AA04Z 126) 双相钢搭接点焊接头疲劳寿命分析 许 君, 张延松, 朱 平, 陈关龙 (上海交通大学车身制造技术中心,上海 200240) 摘 要:研究了双相钢焊点特征,对不同匹配双相钢搭接焊点进行了疲劳试验,获得了焊点的载荷寿命曲线。研究了双相钢焊点的疲劳裂纹扩展及失效形式,分析和解释了疲劳过程中的现象,并根据裂纹的实际扩展路径,提出了局部等效张开应力强度因子 k eq ,从断裂力学的角度对双相钢焊点的疲劳失效进行了分析。结果表明,k eq 能够有效 地关联具有不同厚度,不同熔核直径的搭接焊点试样的疲劳寿命,是反映双相钢焊点疲劳强度的有效参量,能够用来预测焊点疲劳寿命。关键词:双相钢;点焊;疲劳强度;局部等效应力强度因子 中图分类号:TG 115.28 文献标识码:A 文章编号:0253-360X (2008)05-0045- 04 许 君 0 序 言 在汽车工业中,为适应提高油效和减少尾气排放的需要,汽车轻量化已经成为21世纪汽车技术 的前沿和热点[1] 。减少汽车重量的主要途径就是使用轻量化材料。传统的低碳钢以及高强度低碳合金钢(HS LA )现在正越来越多地被双相高强度钢(DP )所取代,双相钢的抗拉强度可以达到600MPa 甚至更高,它能够在不降低车身强度和刚度等各项性能指标的前提下,减少车身重量,而它现在也是整个汽车工业以及钢铁工业研究的热点。双相高强钢由低碳钢和低碳低合金钢经临界区处理或控制轧制而得到,主要由铁素体和马氏体组成。具有屈服强度低,初始加工硬化速率高,在加工硬化和屈服强度上表现高应变速率敏感性以及强度和延性配合好等特点[2,3]。不仅如此,双相高强钢还具有极强的吸能作用,从而在车辆发生碰撞或其它事故时更好地保护驾乘者的安全。 近年,虽然汽车白车身部件的连接出现了许多新的方法,比如激光焊接、粘接等等,但是电阻点焊仍然是车身构件连接的最主要方式。一般情况下,一辆轿车的白车身上有大约3000个焊点,焊点周围存在较严重的应力集中,疲劳裂纹易于形成和扩展,车身结构的大部分疲劳失效都发生在焊点或者焊点周围,焊点的局部失效会降低整个车辆的各种 功能指标,包括刚度、振动、噪声、以及车辆耐久性等 [4] 。随着双向高强钢越来越多地应用于汽车车身 制造中,双相钢焊点疲劳强度也逐渐成为各大汽车厂商的研究焦点。 在双相钢搭接点焊接头进行疲劳试验的基础上,对双相钢点焊接头疲劳裂纹扩展及失效形式进行了讨论,获得了焊点的载荷寿命曲线,分析和解释了疲劳过程中的现象,并根据裂纹的实际扩展路径,提出了局部等效张开应力强度因子k eq ,它是反映焊点疲劳寿命的有效参量。 1 试验方法 1.1 材料与试样 疲劳试验试样使用了双相高强钢DP600GI 以及DP780GI ,对应于DP600GI 有0.8mm 以及1.4mm 两 种厚度钢板,而DP780GI 则有1.0mm 以及1.6mm 两种厚度钢板,两种材料化学成分以及力学性能分别列于表1和表2。用于疲劳试验的拉剪试样具体几何尺寸见图1。为了保证获得焊点的一致性,所有试样的几何尺寸都保持一致,且焊接钢板都是同种厚度的组合,具体焊接参数如表3。 表1 DP600GI 和DP780GI 的化学成分(质量分数,%) Table 1 Chemical compo sitions of DP600GI and DP780GI 材料 C Mn P S Al Fe DP600GI 0.11 1.430.010.0010.02余量DP780GI 0.13 2.01 0.03 0.002 0.049 余量 第29卷第5期2008年5月 焊 接 学 报 TRANS ACTI ONS OF THE CHI NA WE LDI NG I NSTIT UTI ON V ol.29 N o.5May 2008

常见芯片封装类型的汇总 芯片封装,简单点来讲就是把制造厂生产出来的集成电路裸片放到一块起承载作用的基板上,再把管脚引出来,然后固定包装成为一个整体。它可以起到保护芯片的作用,相当于是芯片的外壳,不仅能固定、密封芯片,还能增强其电热性能。所以,封装对CPU和其他大规模集成电路起着非常重要的作用。 今天,与非网小编来介绍一下几种常见的芯片封装类型。 DIP双列直插式 DIP是指采用双列直插形式封装的集成电路芯片,绝大多数中小规模集成电路均采用这种封装形式,其引脚数一般不超过100个。采用DIP封装的CPU芯片有两排引脚,需要插入到具有DIP结构的芯片插座上。当然,也可以直接插在有相同焊孔数和几何排列的电路板上进行焊接。DIP封装的芯片在从芯片插座上插拔时应特别小心,以免损坏引脚。DIP封装结构形式有多层陶瓷双列直插式DIP,单层陶瓷双列直插式DIP,引线框架式DIP (含玻璃陶瓷封接式,塑料包封结构式,陶瓷低熔玻璃封装式)等。 DIP是最普及的插装型封装,应用范围包括标准逻辑IC,存储器和微机电路等。 DIP封装 特点: 适合在PCB(印刷电路板)上穿孔焊接,操作方便。 芯片面积与封装面积之间的比值较大,故体积也较大。 最早的4004、8008、8086、8088等CPU都采用了DIP封装,通过其上的两排引脚可插到主板上的插槽或焊接在主板上。 在内存颗粒直接插在主板上的时代,DIP 封装形式曾经十分流行。DIP还有一种派生方式SDIP(Shrink DIP,紧缩双入线封装),它比DIP的针脚密度要高六倍。 现状:但是由于其封装面积和厚度都比较大,而且引脚在插拔过程中很容易被损坏,可靠性较差。同时这种封装方式由于受工艺的影响,引脚一般都不超过100个。随着CPU内

焊点疲劳强度研讨 一.疲劳强度 电子元器件的焊点必须能经受长时间的微小振动和电路发散的热量。随着电子产品元器件安装密度的增加,电路的发热量增加,经常会发生焊接处的电气特性劣化,机械强度下降或出现断裂等现象。材料在变动载荷和应变长期作用下,因累积损伤而引起的断裂现象,称为疲劳。疲劳是一种低应力破坏。 二.提高疲劳强度性能的方法 2.1提高焊点的可靠性 提高焊点可靠性的最好方法有三个:提高焊点合金的耐用性;减少元件与PCB之间热膨胀系数(CTE)的失配;尽可能按照实际的柔软性来生产元件,向焊点提供更大的应变; 2.1.1提高焊点合金的耐用性 2.1.1.1选择合适的焊膏 2.1.1 润湿性能 对于焊料来说,能否与基板形成较好的浸润,是能否顺利地完成焊接的关键。如果一种 合金不能浸润基板材料,则会因浸润不良而在界面上产生空隙,易使应力集中而在焊接 处发生开裂。 焊料的润湿性主要的指标浸润角和铺展率。从现象上看,任何物体都有减少其自身表面 能的倾向。因此液体尽量收缩成圆球状,固体则把其接触的液体铺展开来覆盖其表面。 如果液体滴在固体表面,则会形成图一所示的情况。 图二和图三分别表示浸润不良和良好的现象。 θ为浸润角,显然浸润角越小,液态焊料越容易铺展,表示焊料对基板的润湿性能越好。 a. 当θ<900,称为润湿,B角越小,润湿性越好,液体越容易在固体表面展开; b. 当θ>90时称为不润湿,B角越大,润湿性越不好,液体越不容易在固体表面上铺展开, 越容易收缩成接近圆球的形状;

c. 当θ=00或180“时,则分别称为完全润湿和完全不润湿。 通常电子工业焊接时要求焊料的润湿角θ<200。 影响焊料润湿性能主要有:焊料和基板的材料组分、焊接温度、金属表面氧化物、环境介质、基板表面状况等。 IPC-SPVC用润湿力天平来测量并用润湿时间以及最大润湿力来表示的方法评估了不同组成的 SAC 合金的润湿性,结果发现其中(零交时间与最大润湿力)并无差异,见图4。各候选合金与锡铅共晶合金的润湿性比较见图5。 图 4 不同组成的SAC的润湿性评估结果

摘要:倒装芯片在产品成本,性能及满足高密度封装等方面体现出优势,它的应用也渐渐成为主流。由于倒装芯片的尺寸小,要保证高精度高产量高重复性,这给我们传统的设备及工艺带来了挑战。 器件的小型化高密度封装形式越来越多,如多模块封装(MCM )、系统封装(SiP )、倒装芯片(FC ,Flip-Chip )等应用得越来越多。这些技术的出现更加模糊了一级封装与二级装配之间的界线。毋庸置疑,随着小型化高密度封装的出现,对高速与高精度装配的要求变得更加关键,相关的组装设备和工 艺也更具先进性与高灵活性。 由于倒装芯片比BGA 或CSP 具有更小的外形尺寸、更小的球径和球间距、它对植球工艺、基板技术、材料的兼容性、制造工艺,以及检查设备和方法提出了前所未有的挑战。 倒装芯片的发展历史 倒装芯片的定义 什么器件被称为倒装芯片?一般来说,这类器件具备以下特点: 1. 基材是硅; 2. 电气面及焊凸在器件下表面; 3. 球间距一般为4-14mil 、球径为2.5-8mil 、外形尺寸为1 -27mm ; 4. 组装在基板上后需要做底部填充。 其实,倒装芯片之所以被称为“倒装”,是相对于传统的金属线键合连接方式(Wire Bonding)与植球后的工艺而言的。传统的通过金属线键合与基板连接的芯片电气面朝上(图1),而倒装芯片的电气面朝下(图2),相当于将前者翻转过来,故称其为“倒装芯片”。在圆片(Wafer)上芯片植完球后(图3),需要将其翻转,送入贴片机,便于贴装,也由于这一翻转过程,而被称为“倒装芯片”。 图1 图2

图3 倒装芯片的历史及其应用 倒装芯片在1964年开始出现,1969年由IBM发明了倒装芯片的C4工艺(Controlled Collap se Chip Connection,可控坍塌芯片联接)。过去只是比较少量的特殊应用,近几年倒装芯片已经成为高性能封装的互连方法,它的应用得到比较广泛快速的发展。目前倒装芯片主要应用在Wi- Fi、SiP、M CM、图像传感器、微处理器、硬盘驱动器、医用传感器,以及RFID等方面(图5)。 图4

金属疲劳寿命的预测 摘要 当一个金属样品受到循环载荷时,大量的起始裂纹将在它的体内出现。样品形成了有初始裂纹的样本:样品越大,样本也越大。在作者先前的研究中表明,在极值统计的帮助下,通过估计最大预期裂纹深度能够预测疲劳极限。本来表明,在一个类似的方式下,疲劳极限以上的疲劳裂纹萌生时间是可以预测的。用最小的分布可得到最短预期初始时间的预测,代替了用最大分布估计最大裂纹尺寸,并以广泛的实验数据获得了好的赞同。 本文为构件的总的疲劳寿命估计提供了一种新的方法。当得知了预计的裂纹萌生寿命和临界裂纹尺寸时,稳定的裂纹扩展就能通过Paris law计算出来。总的疲劳寿命的估算值是裂纹萌生和裂纹扩展的总和。本文介绍的是:为发现任何一种材料裂纹萌生寿命而相应的构建设计曲线的方法。 1、介绍 估计金属构件疲劳寿命的最古老和最常用的方法是S-N曲线,尽管它的缺点众所周知。其中之一是,因观察试样缺口的光滑程度不同而使得疲劳寿命有很大的不同。有些手册尝试通过为不同的应力值浓度的因素单独设计曲线解决这个问题,如Buch。其被当时看作是避免这一问题的局部应变方法。在这种方法中,提出了无论试样的形状如何,相同的应变振幅总是相同的疲劳寿命。 一个构件的总疲劳寿命可以分为3个阶段:裂纹产生、裂纹稳定扩展和裂纹失稳生长。最后一个阶段很迅速,在估计总的疲劳寿命时可以在实际工作中忽略。利用LEFM可获得裂纹稳定生长的可靠样本。不同几何的应力强度因子和所收录例子的大量的公式都可在文献中找到,并且权函数的使用为扩展这种方法的使用提供了可能性。 用类似LEFM的方式对裂纹初始相位的建模,或裂纹的扩展做了很多的尝试,例如:Miller,Austen,Cameron and Smith。另一种方法是用局部应变方法仅对初始寿命进行估计,然后用LEFM和一个合适的计算机程序完成对总疲劳寿命的计算。 经Makkonen研究表明,统计方法能够用来预测金属构件的疲劳极限。当一个构件受到交变载荷时,大量的微裂纹将在它的内部产生,裂纹的数量取决于试样的大小。运用极值统计法来计算裂纹样品类型中的最大裂纹的估计值成为可

— 1 — 焊点可靠性之焊点寿命预测 在产品设计阶段对SMT 焊点的可能服役期限进行预测,是各大电子产品公司为保证电子整机的可靠性所必须进行的工作,为此提出了多种焊点寿命预测模型。 (1) 基于Manson-Coffin 方程的寿命预测模型 M-C 方程是用于预测金属材料低周疲劳失效寿命的经典经验方程[9]。其基本形式如下: C N p f =ε?β (1-1) 式中 N f — 失效循环数; ?εp — 循环塑性应变范围; β, C — 经验常数。 IBM 的Norris 和Landzberg 最早提出了用于软钎焊焊点热疲劳寿命预测的M-C 方程修正形式[2]: )/exp()(max /1kT Q Cf N n p m f -ε?= (1-2) 式中 C, m, n — 材料常数; Q — 激活能; f — 循环频率; k — Boltzmann 常数; T max — 温度循环的最高温度。 Bell 实验室的Engelmaier 针对LCCC 封装SMT 焊点的热疲劳寿命预测对M-C 方程进行了修正[10]: c f f N /1'221???? ??εγ?= (1-3) )1ln(1074.1106442.024f T c s +?+?--=-- (1-4) 式中 ?γ — 循环剪切应变范围; f 'ε— 疲劳韧性系数,2f 'ε=0.65; c — 疲劳韧性指数; T s — 温度循环的平均温度。 采用M-C 型疲劳寿命预测方程,关键在于循环塑性应变范围的确定。主要有两种方法:一种是解析法[10,11],通过对焊点结构的力学解析分析计算出焊点在热循环过程中承受的循环应变范围,如Engelmaier 给出[10]:

FC倒装芯片装配技术介绍 器件的小型化高密度封装形式越来越多,如多模块封装(MCM)、系统封装(SiP)、倒装芯片(FC,Flip-Chip)等应用得越来越多。这些技术的出现更加模糊了一级封装与二级装配之间的界线。毋庸置疑,随着小型化高密度封装的出现,对高速与高精度装配的要求变得更加关键,相关的组装设备和工艺也更具先进性与高灵活性。 由于倒装芯片比BGA或CSP具有更小的外形尺寸、更小的球径和球间距、它对植球工艺、基板技术、材料的兼容性、制造工艺,以及检查设备和方法提出了前所未有的挑战。 倒装芯片的发展历史 倒装芯片的定义 什么器件被称为倒装芯片?一般来说,这类器件具备以下特点: 1. 基材是硅; 2. 电气面及焊凸在器件下表面; 3. 球间距一般为4-14mil、球径为2.5-8mil、外形尺寸为1-27mm; 4. 组装在基板上后需要做底部填充。 其实,倒装芯片之所以被称为“倒装”,是相对于传统的金属线键合连接方式(Wire Bonding)与植球后的工艺而言的。传统的通过金属线键合与基板连接的芯片电气面朝上(图1),而倒装芯片的电气面朝下(图2),相当于将前者翻转过来,故称其为“倒装芯片”。在圆片(Wafer)上芯片植完球后(图3),需要将其翻转,送入贴片机,便于贴装,也由于这一翻转过程,而被称为“倒装芯片”。 倒装芯片的历史及其应用 倒装芯片在1964年开始出现,1969年由IBM发明了倒装芯片的C4工艺(Controlled Collapse Chip Connection,可控坍塌芯片联接)。过去只是比较少量的特殊应用,近几年倒装芯片已经成为高

性能封装的互连方法,它的应用得到比较广泛快速的发展。目前倒装芯片主要应用在Wi- Fi、SiP、MCM、图像传感器、微处理器、硬盘驱动器、医用传感器,以及RFID等方面(图5)。 与此同时,它已经成为小型I/O应用有效的互连解决方案。随着微型化及人们已接受SiP,倒装芯片被视为各种针脚数量低的应用的首选方法。从整体上看,其在低端应用和高端应用中的采用,根据TechSearch International Inc对市场容量的预计,焊球凸点倒装芯片的年复合增长率(CAGR)将达到31%。 倒装芯片应用的直接驱动力来自于其优良的电气性能,以及市场对终端产品尺寸和成本的要求。在功率及电信号的分配,降低信号噪音方面表现出色,同时又能满足高密度封装或装配的要求。可以预见,其应用会越来越广泛。 倒装芯片的组装工艺流程 一般的混合组装工艺流程在半导体后端组装工厂中,现在有两种模块组装方法。在两次回流焊工艺中,先在单独的SMT生产线上组装SMT器件,该生产线由丝网印刷机、贴片机和第一个回流焊炉组成。然后再通过第二条生产线处理部分组装的模块,该生产线由倒装芯片贴片机和回流焊炉组成。底部填充工艺

IC的常见封装形式 常见的封装材料有:塑料、陶瓷、玻璃、金属等,现在基本采用塑料封装。 按封装形式分:普通双列直插式,普通单列直插式,小型双列扁平,小型四列扁平,圆形金属,体积较大的厚膜电路等。 按封装体积大小排列分:最大为厚膜电路,其次分别为双列直插式,单列直插式,金属封装、双列扁平、四列扁平为最小。 封装的历程变化:TO->DIP->PLCC->QFP->BGA ->CSP 1、DIP(DualIn-line Package)双列直插式封装 D—dual两侧 双列直插式封装。插装型封装之一,引脚从封装两侧引出 2、SIP(single in-line package)单列直插式封装 引脚从封装一个侧面引出,排列成一条直线。当装配到印刷基板上时封装呈侧立状 3、SOP(Small Out-Line Package) 小外形封装双列表面安装式封装 以后逐渐派生出SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电路) 4、PQFP(Plastic Quad Flat Package)塑料方型扁平式封装 芯片引脚之间距离很小,管脚很细,一般大规模或超大型集成电路都采用这种封装形式,其引脚数一般在100个以上。适用于高频线路,一般采用SMT技术应用在PCB板上安装

5、BQFP(quad flat package with bumper)带缓冲垫的四侧引脚扁平封装 QFP 封装之一,在封装本体的四个角设置突起(缓冲垫) 以防止在运送过程中引脚发生弯曲变形 6、QFN(quad flat non-leaded package)四侧无引脚扁平封装 封装四侧配置有电极触点,由于无引脚,贴装占有面积比QFP 小,高度比QFP 低。但是,当印刷基板与封装之间产生应力时,在电极接触处就不能得到缓解。因此电极触点难于作到QFP 的引脚那样多,一般从14 到100 左右。材料有陶瓷和塑料两种。当有LCC 标记时基本上都是陶瓷QFN 7、PGA(Pin Grid Array Package)插针网格阵列封装 插装型封装之一,其底面的垂直引脚呈阵列状排列,一般要通过插座与PCB板连接。引脚中心距通常为2.54mm,引脚数从64 到447 左右。 8、BGA(Ball Grid Array Package)球栅阵列封装 其底面按阵列方式制作出球形凸点用以代替引脚。适应频率超过100MHz,I/O 引脚数大于208 Pin。电热性能好,信号传输延迟小,可靠性高。

倒装封装介绍 什么是LED倒装芯片?近年来,在芯片领域,倒装芯片技术正异军突起,特别是在大功率、户外照明的应用市场上更受欢迎。但由于发展较晚,很多人不知道什么叫LED倒装芯片,LED倒装芯片的优点是什么?今天慧聪LED屏网编辑就为你做一个简单的说明。先从LED正装芯片为您讲解LED倒装芯片,以及LED倒装芯片的优势和普及难点。 要了解LED倒装芯片,先要了解什么是LED正装芯片 LED正装芯片是最早出现的芯片结构,也是小功率芯片中普遍使用的芯片结构。该结构,电极在上方,从上至下材料为:P-GaN,发光层,N-GaN,衬底。所以,相对倒装来说就是正装。 LED倒装芯片和症状芯片图解 为了避免正装芯片中因电极挤占发光面积从而影响发光效率,芯片研发人员设计了倒装结构,即把正装芯片倒置,使发光层激发出的光直接从电极的另一面发出(衬底最终被剥去,芯片材料是透明的),同时,针对倒装设计出方便LED封装厂焊线的结构,从而,整个芯片称为倒装芯片(Flip Chip),该结构在大功率芯片较多用到。 正装、倒装、垂直LED芯片结构三大流派

倒装技术并不是一个新的技术,其实很早之前就存在了。倒装技术不光用在LED行业,在其他半导体行业里也有用到。目前LED芯片封装技术已经形成几个流派,不同的技术对应不同的应用,都有其独特之处。 目前LED芯片结构主要有三种流派,最常见的是正装结构,还有垂直结构和倒装结构。正装结构由于p,n电极在LED同一侧,容易出现电流拥挤现象,而且热阻较高,而垂直结构则可以很好的解决这两个问题,可以达到很高的电流密度和均匀度。未来灯具成本的降低除了材料成本,功率做大减少LED颗数显得尤为重要,垂直结构能够很好的满足这样的需求。这也导致垂直结构通常用于大功率LED应用领域,而正装技术一般应用于中小功率LED。而倒装技术也可以细分为两类,一类是在蓝宝石芯片基础上倒装,蓝宝石衬底保留,利于散热,但是电流密度提升并不明显;另一类是倒装结构并剥离了衬底材料,可以大幅度提升电流密度。 LED倒装芯片的优点 一是没有通过蓝宝石散热,可通大电流使用;二是尺寸可以做到更小,光学更容易匹配;三是散热功能的提升,使芯片的寿命得到了提升;四是抗静电能力的提升;五是为后续封装工艺发展打下基础。 什么是LED倒装芯片 据了解,倒装芯片之所以被称为“倒装”是相对于传统的金属线键合连接方式(Wire Bonding)与植球后的工艺而言的。传统的通过金属线键合与基板连接的晶片电气面朝上,而倒装晶片的电气面朝下,相当于将前者翻转过来,故称其为“倒装芯片”。 倒装LED芯片,通过MOCVD技术在蓝宝石衬底上生长GaN基LED结构层,由P/N结发光区发出的光透过上面的P型区射出。由于P型GaN传导性能不佳,为获得良好的电流扩展,需要通过蒸镀技术在P区表面形成一层Ni- Au组成的金属电极层。P 区引线通过该层金属薄膜引出。为获得好的电流扩展,Ni-Au金属电极层就不能太薄。为此,器件的发光效率就会受到很大影响,通常要同时兼顾电流扩展与出光效率二个因素。但无论在什麼情况下,金属薄膜的存在,总会使透光性能变差。此外,引线焊点的存在也使器件的出光效率受到影响。采用GaN LED倒装芯片的结构可以从根本上消除上面的问题。 在倒装芯片的技术基础上,有厂家发展出了LED倒装无金线芯片级封装。 什么是LED倒装无金线芯片级封装 倒装无金线芯片级封装,基于倒装焊技术,在传统LED芯片封装的基础上,减少了金线封装工艺,省掉导线架、打线,仅留下芯片搭配荧光粉与封装胶使用。作为新封装技术产品,倒装无金线芯片级光源完全没有因金线虚焊或接触不良引起的不亮、闪烁、

芯片封装形式 芯片封装形式主要以下几种:DIP,TSOP,PQFP,BGA,CLCC,LQFP,SMD,PGA,MCM,PLCC等。 DIP DIP封装(Dual In-line Package),也叫双列直插式封装技术,双入线封装,DRAM的一种元件封装形式。指采用双列直插形式封装的集成电路芯片,绝大多数中小规模集成电路均采用这种封装形式,其引脚数一般不超过100。DIP封装的CPU芯片有两排引脚,需要插入到具有DIP结构的芯片插座上。当然,也可以直接插在有相同焊孔数和几何排列的电路板上进行焊接。DIP封装的芯片在从芯片插座上插拔时应特别小心,以免损坏管脚。DIP封装结构形式有:多层陶瓷双列直插式DIP,单层陶瓷双列直插式DIP,引线框架式DIP(含玻璃陶瓷封接式,塑料包封结构式,陶瓷低熔玻璃封装式)等。 DIP封装具有以下特点: ?适合在PCB(印刷电路板)上穿孔焊接,操作方便。 ?芯片面积与封装面积之间的比值较大,故体积也较大。 ?最早的4004、8008、8086、8088等CPU都采用了DIP封装,通过其上的两排引脚 可插到主板上的插槽或焊接在主板上。 ?在内存颗粒直接插在主板上的时代,DIP 封装形式曾经十分流行。DIP还有一种派 生方式SDIP(Shrink DIP,紧缩双入线封装),它比DIP的针脚密度要高6六倍。 DIP还是拨码开关的简称,其电气特性为 ●电器寿命:每个开关在电压24VDC与电流25mA之下测试,可来回拨动2000次; ●开关不常切换的额定电流:100mA,耐压50VDC ; ●开关经常切换的额定电流:25mA,耐压24VDC ; ●接触阻抗:(a)初始值最大50mΩ;(b)测试后最大值100mΩ; ●绝缘阻抗:最小100mΩ,500VDC ; ●耐压强度:500VAC/1分钟; ●极际电容:最大5pF ; ●回路:单接点单选择:DS(S),DP(L) 。 TSOP 到了上个世纪80年代,内存第二代的封装技术TSOP出现,得到了业界广泛的认可,时至今日仍旧是内存封装的主流技术。TSOP是“Thin Small Outline Package”的缩写,意思是薄型小尺寸封装。TSOP内存是在芯片的周围做出引脚,采用SMT技术(表面安装技术)直接附着在PCB板的表面。TSOP封装外形尺寸时,寄生参数(电流大幅度变化时,引起输出电压扰动)减小,适合高频应用,操作比较方便,可靠性也比较高。同时TSOP封装具有成品率高,价格便宜等优点,因此得到了极为广泛的应用。 TSOP封装方式中,内存芯片是通过芯片引脚焊接在PCB板上的,焊点和PCB板的接触面积较小,使得芯片向PCB办传热就相对困难。而且TSOP封装方式的内存在超过150MHz 后,会产品较大的信号干扰和电磁干扰。 PQFP PQFP: (Plastic Quad Flat Package,塑料方块平面封装)一种芯片封装形式。 BGA BGA封装内存 BGA封装(Ball Grid Array Package)的I/O端子以圆形或柱状焊点按阵列形式分布在封装下面,BGA技术的优点是I/O引脚数虽然增加了,但引脚间距并没有减小反而增加了,从而提

焊点可靠性之焊点寿命改善 提高SMT焊点可靠性的方法主要有以下四种: (1) 研制开发新型基板材料以减小陶瓷芯片载体与树脂基板之间的热膨胀系数差。研究主要集中于印刷电路板材料,已经研制开发了42%Ni-Fe合金(CTE=5ppm/o C)、Cu-因瓦合金-Cu复合材料板(CTE=2.8~13ppm/o C)等新型基板材料,效果较好[41]。但是由于新型材料制作工艺复杂、价格昂贵,其实用性受到很大限制,90年代起极少有此类研究见于文献。 (2) 提高软钎料合金自身的力学性能,向Sn-Pb共晶合金基体中加入微量合金元素以实现合金强化。由于实际生产中需综合考虑成本、工艺性等多方面问题,对Sn-Pb基钎料合金而言,这方面的工作较少,主要是添加Ag[42]。朱颖博士开发了Sn-Pb-RE系列钎料合金,不仅提高表面组装焊点热循环寿命2-3倍,而且在成本和工艺性方面均有很好的应用前景[43]。近年来,随着环境保护呼声的日益提高,开发无铅钎料(Lead-Free Solder)成为了软钎焊材料研究的热点,HP公司的Glazer对此作了很好的综述[44],焦点在于新型无铅钎料合金在保证润湿性的前提下,其熔点要与现有工艺条件匹配且其力学性能要优于Sn-Pb共晶合金。 (3) 焊点形态优化设计。作为承受载荷的结构件,不同的焊点形态将导致焊点内部不同的热应力-应变分布,从而导致不同的焊点热疲劳性能。焊点形态优化设计包括两方面的内容:一是焊点形态预测,即在钎料量、焊点高度、焊盘几何、软钎焊规范等工艺参数确定的条件下,借助于焊点成型的数学物理模型计算出焊点的最终形态。近年来提出了多种基于能量最小原理的焊点形态预测模型[45-47]。二是优化设计,即何种焊点形态才具有最优的热疲劳性能。优化判据的确定是一个涉及到焊点失效机制的理论问题,目前还远没有 —1 —

最早的表面安装技术——倒装芯片封装技术(FC)形成于20世纪60年代,同时也是最早的球栅阵列封装技术(BGA)和最早的芯片规模封装技术(CSP)。 倒装芯片封装技术为1960年IBM公司所开发,为了降低成本,提高速度,提高组件可靠性,FC使用在第1层芯片与载板接合封装,封装方式为芯片正面朝下向基板,无需引线键合,形成最短电路,降低电阻;采用金属球连接,缩小了封装尺寸,改善电性表现,解决了BGA为增加引脚数而需扩大体积的困扰。再者,FC通常应用在时脉较高的CPU或高频RF上,以获得更好的效能,与传统速度较慢的引线键合技术相比,FC更适合应用在高脚数、小型化、多功能、高速度趋势IC的产品中。 随着电子封装越来越趋于向更快、更小、更便宜的方向发展,要求缩小尺寸、增加性能的同时,必须降低成本。这使封装业承受巨大的压力,面临的挑战就是传统SMD封装技术具有的优势以致向我们证实一场封装技术的革命。 2 IBM的FC IBM公司首次成功地实施直接芯片粘接技术(DCA),把铜球焊接到IC焊盘上,就像当今的BGA 封装结构。图1示出了早期固态芯片倒装片示意图。IBM公司继续采用铜球技术并寻求更高生产率的方法,最终选择的方案为锡-铅焊料的真空淀积。为了形成被回流焊进入球凸点的柱状物,应通过掩模使焊料淀积。由于淀积是在圆片级状况下完成的,因而此过程获得了良好的生产率。这种凸点倒装芯片被称为C4技术(可控塌陷芯片连接)一直在IBM公司和别的生产厂家使用几十年,并保持着高的可靠性记录。 虽然C4在更快和更小方面显得格外突出,但是呈现出更节省成本方面的不足。与C4相关的两个重要的经济问题是:形成凸点的成本和昂贵的陶瓷电路的各项要求。然而,正确的形成凸点技术及连接技术能够提供更进一步探求较低成本的因素。 3 形成凸点技术 凸点形成技术分为几个简单的类型,即淀积金属、机械焊接、基于聚合物的胶粘剂以及别的组合物。最初的C4高铅含量焊料凸点,熔点在300℃以上,被低共熔焊料和胶粘剂代替,从而使压焊温度下降到易于有机PCB承受的范围。然而,如果低共熔焊膏作为接合材料使用,那么C4仍可用于FR-4上。 3.1 机械形成凸点技术 十多年前,IBM公司和K&S公司开发了球凸点形成工艺技术,称为柱式凸点形成技术。此工艺过程首先涉及到对铝芯片载体的球压焊技术,接着把焊丝拉到断裂点,最后形成有短尾部的凸点。为了在球附近形成光滑的断裂口,可使用含有1%铂的金丝。焊料和别的金属也是起作用的。很多改变是明显的,包括平面性方面的凸点精压技术和更高、更复杂的金属化的双凸点形成技术。柱式凸点形成技术,长期使用于试制形式。由于通过引线键合机获得了惊人的速度,已移入生产模式。金和金凸点及焊料凸点均被实施。Delco公司和K&S公司联合生产柱式凸点的倒装芯片产品,别的公司在不远的将来预计生产凸点芯片。 3.2 金属电镀技术 电镀技术要求首先形成总线接头,选择电镀掩模,并用于TAB的金凸点芯片技术。虽然通过在晶圆片上方汽相淀积金属,在典型状况下形成总线,但是总线必须能被清除。再者,必须提供光成像电镀保护膜,在电镀之前成像并显影。很多步骤和精确的电镀掩模工艺的要求增加了成本和不便因素。 化学镀是无掩模和无总线的方法,看上去是一种较好的方法。该技术已广泛地应用于印刷电路行业,但是化学形成凸点的技术仅仅是近年来才应用于倒装芯片的。化学镀镍,也许由于其非常精确的化学性质,已呈现为首要的且普遍的化学倒装片凸点技术工艺。如果铝没有直接与镍一起电镀,就可使用中间浸液电镀锌技术。图2示出了最普遍的镍凸点技术顺序。注意到在典型状况下,镍受到薄的、易于产生浸液的金涂层保护。形成的金毛刺适于焊接及胶粘剂压焊。

LED倒装工艺流程分析 近年来LED在电视机背光、手机、和平板电脑等方面的应用也迎来了爆发式的增长,LED具有广阔的应用发展前景。 倒装LED技术的发展及现状 倒装技术在LED领域上还是一个比较新的技术概念,但在传统IC行业中已经被广泛应用且比较成熟,如各种球栅阵列封装(BGA)、芯片尺寸封装(CSP)、晶片级芯片尺寸封装(WLCSP)等技术,全部采用倒装芯片技术,其优点是生产效率高、器件成本低和可靠性高。 倒装芯片技术应用于LED器件,主要区别于IC在于,在led芯片制造和封装过程中,除了要处理好稳定可靠的电连接以外,还需要处理光的问题,包括如何让更多的光引出来,提高出光效率,以及光空间的分布等。 针对传统正装LED存在的散热差、透明电极电流分布不均匀、表面电极焊盘和引线挡光以及金线导致的可靠性问题,1998年,J.J.Wierer等人制备出了1W倒装焊接结构的大功率AlGaInN-LED蓝光芯片,他们将金属化凸点的AIGalnN芯片倒装焊接在具有防静电保护二极管(ESD)的硅载体上。 测试结果表明,在相同的芯片面积下,倒装led芯片(FCLED)比正装芯片有着更大的发光面积和非常好的电学特性,在200-1000mA的电流范围,正向电压(VF)相对较低,从而导致了更高的功率转化效率。 2006年,O.B.Shchekin等人又报道了一种新的薄膜倒装焊接的多量子阱结构的LED(TFFC-LED)。所谓薄膜倒装LED,就是将薄膜LED与倒装LED的概念结合起来。 在将LED倒装在基板上后,采用激光剥离(Laser lift-off)技术将蓝宝石衬底剥离掉,然后在暴露的N型GaN层上用光刻技术做表面粗化。 随着硅基倒装芯片在市场上销售,逐渐发现这种倒装LED芯片在与正装芯片竞争时,其成本上处于明显的劣势。 由于LED发展初期,所有封装支架和形式都是根据其正装或垂直结构LED 芯片进行设计的,所以倒装LED芯片不得不先倒装在硅基板上,然后将芯片固定在传统的支架上,再用金线将硅基板上的电极与支架上的电极进行连接。 使得封装器件内还是有金线的存在,没有利用上倒装无金线封装的优势;而且还增加了基板的成本,使得价格较高,完全没有发挥出倒装LED芯片的优势。 为此,最早于2007年有公司推出了陶瓷基倒装led封装产品。这一类型的产品,陶瓷既作为倒装芯片的支撑基板,也作为整体封装支架,实现整封装光源的小型化。

倒装芯片封装结构中SnAgCu 焊点热疲劳寿命预测方法研究 THERMO -FATIGUE LIFE PREDICTION METHODOLOGIES FOR SnAgCu SOLDER JOINTS IN FLIP -CHIP ASSEMBLIES 李晓延 王志升 (北京工业大学材料学院,北京100022) LI XiaoYan WANG ZhiSheng (School of M ate rials Scienc e and Engineering ,Beijing Unive rsity of Technology ,Beijing 100022,China ) 摘要 由于焊点区非协调变形导致的热疲劳失效是倒装芯片封装(包括无铅封装)结构的主要失效形式。到目前为止,仍无公认的焊点寿命和可靠性的评价方法。文中分别采用双指数和双曲正弦本构模型描述SnAgCu 焊点的变形行为,通过有限元方法计算焊点累积蠕变应变和累积蠕变应变能密度,进而据此预测倒装芯片封装焊点的热疲劳寿命。通过实验验证,评价上述预测方法的可行性。结果表明,倒装芯片的寿命可由芯片角焊点的寿命表征;根据累积蠕变应变能密度预测的焊点热疲劳寿命比根据累积蠕变应变预测的焊点热疲劳寿命更接近实测数据;根据累积蠕变应变预测的热疲劳寿命比根据累积蠕变应变能密度预测的热疲劳寿命长;采用双指数本构模型时,预测的焊点热疲劳寿命也较长。 关键词 热疲劳 寿命预测 倒装芯片焊点 无铅化中图分类号 TG407 O346.2 TB114.3 A bstract Thermal fatigue failure ,due to the fracture of solder joints which was caused by the mis match deformation ,is frequentl y encountered in flip chip (FC )assemblies .Unfortunately ,there is n o widel y accepted method to evaluate the reliability of solder joints ,especially for lead -free solder joints ,in s uch assemblies up to now .The constitutive models of double power law and the hyperbolic sine law were implemented to simulate the deformation of Sn AgCu solder joints in flip chip assemblies .The accumulated creep strain and ac -cu mulated creep strain energy dens ity of the solder joints were calculated ,via finite element method ,and were use to predict the thermal fatigue life of flip chip assemblies .The applicability of the above life prediction methods was evaluated through cross check of the present results with that of the literatures .It was found that the life of the FC assemblies could be estimated by the prediction of the life of the corner solder joints .The thermal fatigue life ,estimated according to accumulated creep strain energy density is closer to the test data than that of the life estimated according to accumulated creep strain .The life predicated according to accumulated creep strain shown a slightly high value than that predicated accordin g to accumulated creep strain energy density .The double power law constitutive equation results in a higher predicted life . Key words Themo -fatigue ;Life prediction ;Flip chip ;Solder joint ;Lead free Corr es ponding autho r :LI Xiao Yan ,E -mail :xyli @bjut .edu .cn The project supported b y the National Natural Science Foundation of China (No .50475043),Nature Science Foundation of Beijin g (2052006)and the Specialized Research Fund for the Doctoral Program of Higher Education of China (No .20040005012). Manuscript received 20060712,in revised form 20060831. 1 引言 小型化和高密度组装是新一代电子产品的主要特征,倒装芯片(flip chip on board ,FCOB )封装结构的广 泛应用正是为了满足上述特征要求,在倒装芯片封装中,硅芯片通过焊点直接安装于玻璃环氧树脂印刷电路基板(printed circuit board ,PCB )上,以确保短的互连电路、高的集成密度和良好的噪音控制。这类倒装芯 片封装结构的简图如图1所示。一般来说,倒装芯片 封装结构包含四个主要部分,芯片、焊点、基板和填充胶。在芯片制造和服役的温度循环中,封装材料的热物理性能,特别是热膨胀系数的差异引起芯片中非协调变形的发生,焊点中的应力和应变也随之升高。研究表明,芯片的破坏与倒装芯片封装结构所经历的非协调形变历史密切相关。由于倒装芯片封装结构的复杂性和修复的困难,一个焊点(特别是角点) 的破坏往 Journal of Mechanical Strength 2006,28(6):893~898 李晓延,男,1963年5月生,陕西省礼泉县人,汉族。哈尔滨工业大学工学博士,芬兰拉彭兰塔工业大学科学博士,中国焊接学会常务理事,北 京工业大学教授,主要从事材料和结构全寿命周期的强度与可靠性研究。 20060712收到初稿,20060831收到修改稿。本文研究得到国家自然科学基金(50475043)、北京市自然科学基金(2052006)和教育部博士点基金 (20040005012)的资助。