DDR2 SDRAM介绍及其基于MPC8548 CPU的硬件设计2009-02-26 01:35:44 文章出处:与非网

DDR2 SDRAM芯片提供一个ODT引脚来控制开或关芯片内部的终结电阻。在只有一个DDR2 SDRAM芯片作为存储器控制器的负载的情况下,写操作时,由于DDR2 SDRAM作为接收端,所以ODT引脚为高电平以打开芯片内部终结电阻

DDR2 SDRAM引入的新技术

DDR2(Double Data Rate 2,两倍数据速率,版本2) SDRAM,是由JEDEC标准组织开发的基于DDR SDRAM的升级存储技术。相对于DDR SDRAM,虽然其仍然保持了一个时钟周期完成两次数据传输的特性,但DDR2 SDRAM在数据传输率、延时、功耗等方面都有了显著提高,而这些性能的提高,主要来源于以下技术的提升:ODT,Post CAS,4n数据预取,封装等。

ODT

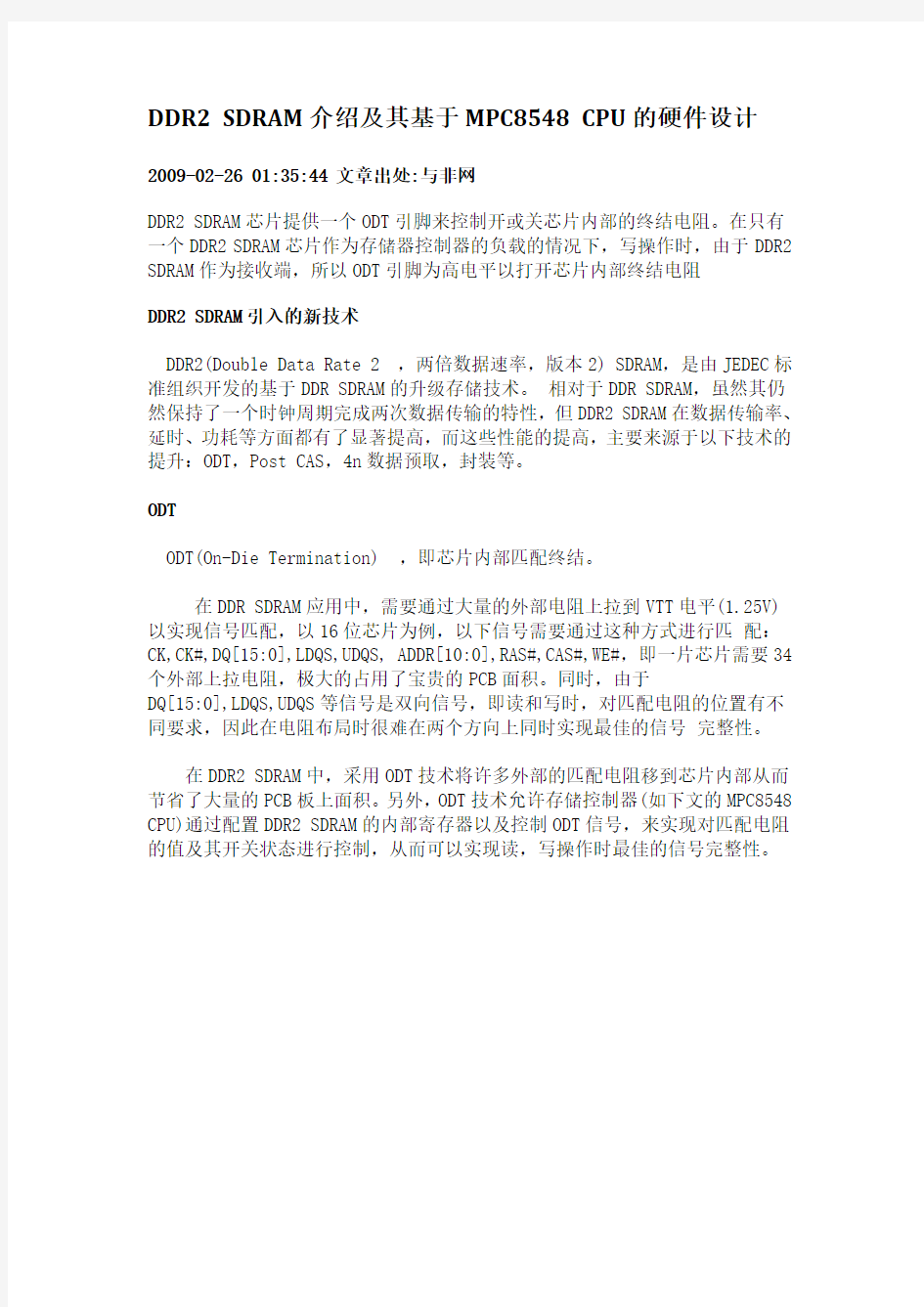

ODT(On-Die Termination),即芯片内部匹配终结。

在DDR SDRAM应用中,需要通过大量的外部电阻上拉到VTT电平(1.25V)以实现信号匹配,以16位芯片为例,以下信号需要通过这种方式进行匹配:CK,CK#,DQ[15:0],LDQS,UDQS, ADDR[10:0],RAS#,CAS#,WE#,即一片芯片需要34个外部上拉电阻,极大的占用了宝贵的PCB面积。同时,由于

DQ[15:0],LDQS,UDQS等信号是双向信号,即读和写时,对匹配电阻的位置有不同要求,因此在电阻布局时很难在两个方向上同时实现最佳的信号完整性。

在DDR2 SDRAM中,采用ODT技术将许多外部的匹配电阻移到芯片内部从而节省了大量的PCB板上面积。另外,ODT技术允许存储控制器(如下文的MPC8548 CPU)通过配置DDR2 SDRAM的内部寄存器以及控制ODT信号,来实现对匹配电阻的值及其开关状态进行控制,从而可以实现读,写操作时最佳的信号完整性。

图1 ODT功能图

DDR2 SDRAM芯片提供一个ODT引脚来控制开或关芯片内部的终结电阻。在只有一个DDR2 SDRAM芯片作为存储器控制器的负载的情况下,写操作时,由于DDR2 SDRAM作为接收端,所以ODT引脚为高电平以打开芯片内部终结电阻;读操作时,由于DDR2 SDRAM作为发送端,所以ODT引脚为低电平以关闭芯片内部终结电阻。其中,ODT引脚的状态由存储器控制器(如MPC8548)来控制。

ODT终端电阻值RTT可以通过DDR2 SDRAM内部的EMR寄存器来设定:首先配置EMR[15:14]=01来选定该寄存器工作于EMR(扩展模式寄存器)模式,然后通过EMR[6]和 EMR[2]两位来设置内部RTT的值,允许选择为RTT关闭,75欧姆,150欧姆,50欧姆这四种模式。以选择75欧姆这种模式为例,图1中,DQ引脚内部的上拉电阻和下拉电阻将配置为150欧姆。

需要注意,DDR2 SDRAM的ODT技术,只是对DQ,DQS,DM这些信号(在选择了差分DQS的情况下,也包括DQS#信号)实现了内部匹配。而地址和控制信号等仍需要通过外部匹配。

Posted CAS

以读DDR2 SDRAM为例。

图2 多块数据读取时的间隙问题

DDR2 SDRAM和DDR SDRAM一样,是通过Bank(块地址),Row(行地址)和Column(列地址)三者结合实现寻址。每一次对DDR2 SDRAM的操作,都以ACTIVE 命令(图2的ACT命令,通过有效#RAS信号实现)开始,在发出该命令的同时,通过地址信号线发出本次操作的Bank和Row地址,此后等待tRCD时间后,发起READ/AUTO PRECHARGE命令(图2 的RD AP命令,通过有效#CAS信号实现),该命令的作用是发出读取命令,同时通过地址信号线发出本次操作的Column地址。最后,等待CAS Latency时间之后,数据即通过数据总线输出。

由于DDR2 SDRAM的存储空间相对DDR SDRAM有所增加,因此Bank数目也有所增加。例如,DDR SDRAM单片最大容量为1Gbit,Bank数目是4,而DDR2 SDRAM 单片最大容量为2Gbit,Bank数目达到了8。DDR SDRAM的Bank数目最少是2,而DDR2 SDRAM的Bank数目最少是4。为了提高性能,经常需要在一个Bank的操作完成之前插入对下一个Bank的操作。如图2,在发出对Bank0的ACT命令之后,无需等待对应的RD AP命令发出,只用满足tRRD时间要求,即可发出对另一个Bank的ACT命令。

按照这种工作模式,从图2中可以发现,对Bank2的ACT命令实际上延迟了一个时钟周期,该命令本来应该在RD AP(Bank 0)的位置出现,但由于RD

AP(Bank 0)命令已经出现在该时钟周期(占用了地址总线,以发出Column地址),从硬件信号上来说,即在这个周期已经使能了CAS#信号,所以无法使能对应另一个Bank的RAS#信号,因此只能延时一个时钟周期。其结果是,本来应该是流水线式的数据输出流被打断,Bank1的数据输出后,需要等待一个时钟周期,Bank2的数据才得到输出。数据流间隙的出现,将影响芯片的性能。

针对这个问题,DDR2 SDRAM做了改进。DDR2 SDRAM允许RD AP命令提前发出,甚至可以紧跟ACT命令发出,但是要等待一个Additive Latency(即AL,附加延时)后,该RD AP命令才能执行。如图3所示。

图3 引入附加延迟AL的DDR2 SDRAM读取模式

在图3中,AL设置为tRCD-1,此时,可以实现ACT和RD AP命令背靠背的发出,只不过,DDR2 SDRAM需要抑制RD AP命令,直到AL延时满足后才能执行。

图4 引入AL后的多Bank数据读取

如图4,引入AL并设置AL为tRCD-1后,对于多个Bank数据读取,输出数据流之间不再出现间隙。

这种为了避免ACT命令和RD AP命令冲突而提出的技术就叫做Posted CAS 技术。其本质就是将CAS#信号的使能时间段(即RD AP命令)直接插入到紧跟RAS#信号的使能时间段(即ACT命令)之后,虽然读和写操作并没有得到提前,总的延迟时间也没有发生改变,但引入这种技术后,可以避免在多Bank操作中的一个Bank的CAS#信号和其他Bank的RAS#信号发生冲突,从而提高了存储芯片的使用效率。

可以通过配置DDR2 SDRAM芯片内部的EMR寄存器的第3~5位,将附加延时AL配置为0~5个时钟周期。

采用差分DQS/DQS#信号,其优势在于:减少信号间串扰的影响,减少DQS 输出脉宽对工作电压和温度稳定性的依赖等。因而,建议在使用数据传输率为533Mb/s以上的DDR2 SDRAM系列时,尽量采用差分DQS/DQS#信号。

使能差分DQS信号是通过设置DDR2 SDRAM的EMR寄存器的第10位为0来实现。

功耗和封装

DDR SDRAM的电平常用SSTL-2,即信号引脚是利用2.5V电源供电,而DDR2 SDRAM则采用SSTL-18电平,即信号引脚是利用1.8V电源供电。在相同存储容量和相同数据传输率的情况下,DDR2 SDRAM将有更低的功耗。

DDR SDRAM的封装种类有:66引脚的TSOP封装,60引脚的FBGA封装。由于DDR SDRAM的数据传输率不是特别高,因此TSOP封装能较好的工作在这种频率上。而DDR2 SDRAM的最高数据传输率已经达到1066Mb/s,在高频下,TSOP

封装的过长的引脚将产生很高的感抗和寄生电容,严重影响芯片工作的稳定性。

DDR2 SDRAM直接采用FBGA封装,基于其良好的电气性能和散热性,保证了芯片在高速工作下的稳定性。

由于DDR2 SDRAM有4位,8位,16位(芯片的DQ引脚的数目,16位表示芯片有16根DQ引脚)三种不同系列,因而无法采用统一引脚数目的封装。目前,4位和8位的芯片采用60或者68引脚的FBGA封装,16位的芯片采用92或者84引脚的FBGA封装。

OCD

OCD(Off-Chip Driver)即离线驱动调整技术。这是DDR2 SDRAM刚问世时开发的技术,而目前的DDR2 SDRAM芯片已不再支持该技术【2】,因此不再详述。

基于MPC8548 CPU的应用

MPC8548是Freescale公司开发的新一代PowerQUICC III系列的高性能处理器。其内部工作频率可达1.33GHz,在该工作频率上处理性能可达3065 MIPS。一级缓存有指令缓存和数据缓存各32KB,二级缓存为512KB,支持DDR1和DDR2存储器控制器,支持PCI,PCI-X和PCI Express接口,支持SRapid IO接口,支持4个GbE接口。本文将重点讨论基于MPC8548的DDR2 SDRAM接口的硬件设计。

MPC8548最高支持667Mb/s数据传输率的DDR2 SDRAM。因此选型中需要注意不能选用800Mb/s和1066Mb/s系列的芯片。本设计中选用667Mb/s数据传输率的DDR2 SDRAM的DIMM(Dual-Inline-Menory-Modules,双列内存条)内存条,每个内存条上包含9片8位的DDR2 SDRAM 芯片,组成64位数据线和8位ECC(Error Checking and Correcting,错误检查和纠正)校验线的工作方式。

DDR2 SDRAM接口的信号线分为4组,以下以MPC8548命名方式为准,命名和DDR2 SDRAM芯片资料的区别在于信号名之前多一个字母”M”【7】:

1) 数据组:MDQS/MDQS#[8:0], MDM[8:0], MDQ[63:0], MECC[7:0]

2) 地址组:MBA[2:0], MA[15:0], MRAS#, MCAS#, MWE#

3) 命令组:MCS#[3:0], MCKE[3:0], MODT[3:0]

4) 时钟组:MCK/MCK#[5:0]

PCB设计时,建议布线顺序依次为:数据组,地址组,控制组,时钟组,电源。

对于单端信号线,阻抗控制在50~60欧姆内。对于差分信号线,阻抗控制在100~120欧姆内。

如果使能了ODT功能,数据组无需外部匹配电阻,走线直接从MPC8548连接到内存条即可。而地址组和命令组需要在内存条末端利用外部电阻RTT上拉到VTT电平实现匹配,电阻值需要经过仿真确定。如图6,考虑到最佳的信号完整性,RTT应该放在内存条之后,即地址/命令组信号走线从MPC8548出来,应该先到内存条的引脚,然后再走到RTT电源平面实现终端匹配。对于时钟组,一般而言,内存条上都包含了100~120欧姆的差分终端电阻,所以在 PCB上无需外加匹配。

图6 MPC8548和DDR2 SDRAM内存条硬件接口设计

由于本设计采用8位的DDR2 SDRAM芯片,因此,对数据组可以分为9个小组:MDQS/MDQS#[0],MDQ[7:0],MDM0为第一组;MDQS/MDQS#[1], MDQ[15:8],MDM1

为第二组;依次类推;MDQS/MDQS#[8],MECC[7:0],MDM8为第九组。对这九小组数据线,要求各小组之内,走线在同一层并拥有相同数目的过孔,走线长度差异控制在20mil之内,所有的信号线走线必须以完整的地层作为参考。不同小组之间,走线长度差异控制在500mil之内。对每一小组,小组内的8根MDQS信号线的线序可以根据走线方便的目的进行调整。需要注意,在本设计中,采用的内存条上的存储芯片是 8位的(即内存条上每片DDR SDRAM芯片有8根DQ数据线),因此每8位MDQ信号归为一个小组,市场上还有许多4位,16位的内存条,如果需要兼容这些内存条,硬件设计中需要注意应该以每4位MDQ信号归为一个小组。数据组的信号线和其他组的信号线间距要求在25mil以上,数据组内信号线间距要求在10mil以上。对于差分的 MDQS和MDQS#信号,走线长度差异应该控制在10mil之内。

对地址/命令组,该组内信号线长度差异应控制在100mil之内。走线以1.8V 电源平面或完整的地层作为参考层。走线和其他组的信号线间距保证在25mil

以上。该组内信号线间距保证在10mil以上。

对时钟组,差分信号对内走线长度差异控制在10mil内,尽量在同一层内走线,如果需要换层,两根差分信号应该一起换层。与其他组的信号间距在 25mil 以上。在MPC8548一侧,一共提供了6对相位相同的时钟对,即MCK/MCK#[5:0],其目的是为了兼容内存条设计和分立的内存芯片设计。例如在本设计中,如果选用分立的8位存储芯片,一共需要9片,如果MPC8548只提供一对时钟对,其驱动能力显然无以满足9片存储芯片,因此需要由 MPC8548提供更多的时钟对输出。如果选用内存条,需要根据内存条的不同种类来决定需要使用多少对时钟对。根据对MCK/MCK#信号是否提供驱动,内存条可以分为Buffered DIMM(缓冲驱动式内存条)和Unbuffered DIMM (非缓冲驱动式内存条),对于前者而言,由于MCK/MCK#在内存条上需要经过缓冲再送到DDR2 SDRAM芯片,即在内存条上利用缓冲器(通常是带锁相环的缓冲器)保证了该信号的驱动能力,所以只需要MPC8548提供一对时钟对(例如MCK/ MCK#[0])送到内存条即可。对于后者而言,内存条上不提供对时钟对的驱动,通过计算可以知道从MPC8548提供的每对时钟对,能可靠驱动3个 DDR2 SDRAM芯片作为负载。因此需要使用MPC8548输出的3对时钟对以驱动内存条上的9片DDR2 SDRAM芯片。对于没有使用到的时钟对,可以通过配置MPC8548的内部寄存器DDRCLKDR进行关闭。

在电源设计方面,需要仔细计算VTT电源发生器及其电源平面是否能满足设计所需要的功耗;需要仔细对VTT, VDDQ, VREF进行去耦滤波;VTT电源平面应该和内存条紧紧相邻;VREF走线宽度建议为20~25mil并和同层的其他电源或信号有至少20mil的间距,VREF必须能跟随VDDQ的变化,建议VREF通过电阻分压网络从VDDQ直接得到,分压电阻精度要求为1%;

设计时,还需要仔细考虑信号时序的要求。数据组信号的时序需要参考本小组的MDQS/MDQS#信号,并利用这对差分对的交叉点采样;地址和命令组信号的时序需要参考对应的时钟组信号,并利用其上升沿采样。对于DDR2 SDRAM,建立时间和保持时间需要考虑由于信号边沿不单调造成的时序降额,计算公式如下:

tSETUP = tSETUP(base) + tSETUP(derating)

tHOLD = tHOLD(base) + tHOLD(derating)

其中,tSETUP和tHOLD是总的建立时间和保持时间要求;tSETUP(base)和tHOLD(base)是从芯片文档能直接得到的建立时间和保持时间的基本要

求;tSETUP(derating)和tHOLD(derating)是根据信号及其参考时钟的真实爬升速率查表得出的降额值,该表格可以从芯片文档得到。

这种查表计算降额值的方法,将造成很大的工作量。在实际设计中,一般是利用Hyperlynx等仿真软件直接得到降额值,从而确定信号的时序裕量。特别需要注意的是地址组,由于地址组信号的负载数目一般都比相应的时钟信号多,因此需考虑负载对时序造成的影响。

结语

存储芯片在电子产品中扮演着重要的角色,其性能的高低直接决定着产品的性能。相比DDR SDRAM,DDR2 SDRAM在多方面进行了技术提升,其必将在电子产品市场中发挥越来越重要的作用。

作者:王剑宇思科公司高级硬件工程师

计算机与信息学院 《系统硬件综合设计》 课程设计报告 学生姓名:李 学号: 1234567890 专业班级:计算机 2017 年 07 月 01日

一、实验原理及设计 本次试验我主要根据上图进行理解和编程,起先参考了5个基础实验,期间又翻阅了自己动手写cpu,并且在网上查了很多资料,下面我将对该图做出我的理解和设计: 1.pcf部分 always @(posedge Clk) begin PCPlus4F_Reg = PCPlus4F; if (BranchM&ZeroM) PCF = PCBranchM; else PCF = PCPlus4F; InstructionF_Reg = InstructionF; if (InstructionF[31:26] == 6'b000010) begin PCF = {6'h0,InstructionF[25:0]}; PCF = PCF << 2; end End assign PCPlus4F = PCF + 4; assign ImemRdAddrF = PCF; 每个时钟上升沿到来,根据上一个时钟的PCSrcM判断是否为分支指令,若是,则选择PCBranchM作为这个时钟的指令地址,否则选PCF+4作为这个指令的指令地址,另外对于J类指令,我设计了一个特定的OpCode==“000010”,即为跳转指令,因为每个指令以字节格式存储,占用,4个字节,故将后26位立即数进行位扩展后将其左移两位,效果等同于乘4,再将其赋值给PCF,这样下一跳的指令地址即为所要跳转的地址。对于这个部分,我起先是准备将其设计成一个模块的,之后由于模块接口连接时出现了无法解决的错误:输出PCF要作为Instruction Memory的输入,又要作为自身模块下一跳的输入,导致三者关联一起变化,程序报错,后来我又想到将PCF的输出改成两个,PCFout 及PCFnext,PCFout作为Instruction Memory的输入,PCFnext作为自身模块下一跳的输入,但是程序仍无法正常运行,最后我想到了在top模块中对PCF进行处理并得以实现。

计算机与信息学院 系统硬件综合设计》 课程设计报告 学生姓名:李 学号:1234567890 专业班级:计算机 2017 年07 月01 日

1.pcf 部分 always @(posedge Clk) begin PCPlus4F_Reg = PCPlus4F; if (BranchM&ZeroM) PCF = PCBranchM; else PCF = PCPlus4F; InstructionF_Reg = InstructionF; if (InstructionF[31:26] == 6'b000010) begin PCF = {6'h0,InstructionF[25:0]}; PCF = PCF << 2; end End assign PCPlus4F = PCF + 4; assign ImemRdAddrF = PCF; 每个时钟上升沿到来,根据上一个时钟的PCSrcM判断是否为分支指令,若是,则选择 PCBranchM作为这个时钟的指令地址,否则选PCF+4作为这个指令的指令地址,另外对于J 类指令,我设计了一个特定的OpCode=“= 000010”,即为跳转指令,因为每个指令以字节格式存储,占用,4 个字节,故将后26 位立即数进行位扩展后将其左移两位,效果等同于乘4,再将其赋值给PCF,这样下一跳的指令地址即为所要跳转的地址。对于这个部分,我起先是准备将其设计成一个模块的,之后由于模块接口连接时出现了无法解决的错误:输出PCF要作为Instruction Memory 的输入,又要作为自身模块下一跳的输入,导致三者关联一起变化,程序报错,后来我又想到将PCF的输出改成两个,PCFout 及PCFnext,PCFout 作为Instruction Memory的输入,PCFnext 作为自身模块下一跳的输入,但是程序仍无法正常运行,最后我想到了在top 模块中对PCF进行处理并得以实

2011 年春季学期《输电线路设计》课程考试试卷( A 卷) 注意:1、本试卷共 2 页; 2、考试时间:110分钟; 3、姓名、学号、网选班级、网选序号必须写在指定地方。 一、填空题 (每空1分,共30分) 1、 输电线路的主要任务是 ,并联络各发电厂、变电站使 之并列运行。 2、 镀锌钢绞线 1×19-12.0-1370-A YB/T5004-2001中,1×19表示 , 12.0表示 ,1370表示 。 3、 某线路悬垂串的绝缘子个数为 13片,该线路的电压等级是 kV 。 4、 线路设计的三个主要气象参数是 、 、 。 5、 输电线路设计规范规定,导线的设计安全系数不应小于 ;年平 均气象条件下的应力安全系数不应小于 。 6、 导线换位的实现方式主要有 、 、 三种。 7、 架空线呈“悬链线”形状的两个假设条件是 、 。 8、 档距很小趋于零时, 将成为控制气象条件;档距很大趋于无限 大时, 将成为控制气象条件。 9、 判定架空线产生最大弧垂的气象条件,常用方法有 和 。 10、状态方程式建立的原则是 。 11、已知某档档距为 498 m ,高差为40 m ,相同条件下等高悬点架空

线的悬挂曲线长度L h=0=500 m,则该档架空线悬挂曲线长度为______________ m。 12、孤立档的最大弧垂位于相当梁上剪力的地方,最低点位于相当 梁上剪力的地方。 13、排定直线杆塔位置时需使用____________________模板,校验直 线杆塔上拔时需使用_____________________模板。 14、在杆塔定位校验中,摇摆角临界曲线的临界条件是 _____________;悬点应力临界曲线的临界条件是_________________;悬垂角临界曲线的临界条件是________________。 15、发生最大弧垂的可能气象条件是_______ _________或_____ _________。 二、判断题(每题2分,共10分) 1、架空线上任意两点的垂向应力差等于比载与相应高差的乘积。 () 2、架空线的平均应力等于平均高度处的应力。() 3、如果临界档距,则两者中较小者对应的气象条件不起 控制作用。 ( ) 4、导线只有在最低气温时产生最大张力。() 5、在连续倾斜档紧线施工时,各档的水平应力不等,山上档比山下 档大。() 三、简答题 (共24分)

8086CPU系统、总线操作和时序 第一节 8086的引脚信号与功能 回顾:8086/8088微型计算机的组成、结构及微机系统的工作过程,微机系统的存储器组织及相关概念。 本讲重点:8086/8088CPU的两种工作模式,8086/8088CPU的外部结构,即引脚信号及其功能。 讲授内容: 一、 8086/8088微处理器工作模式及外部结构 1.8086/8088CPU的两种工作模式 为了适应各种使用场合,在设计8088/8086CPU芯片时,就考虑了其应能够使它工作在两种模式下,即最小模式与最大模式。 所谓最小模式,就是系统中只有一个8088/8086微处理器,在这种情况下,所有的总线控制信号,都是直接由8088/8086CPU产生的,系统中的总线控制逻辑电路被减到最少,该模式适用于规模较小的微机应用系统。 最大模式是相对于最小模式而言的,最大模式用在中、大规模的微机应用系统中,在最大模式下,系统中至少包含两个微处理器,其中一个为主处理器,即8086/8086CPU,其它的微处理器称之为协处理器,它们是协助主处理器工作的。 与8088/8086CPU配合工作的协处理器有两类,一类是数值协处理器8087 另一类是输入/输出协处理器8089。 8087是一种专用于数值运算的协处理器,它能实现多种类型的数值运算,如高精度的整型和浮点型数值运算,超越函数(三角函数、对数函数)的计算等,这些运算若用软件的方法来实现,将耗费大量的机器时间。换句话说,引入了8087协处理器,就是把软件功能硬件化,可以大大提高主处理器的运行速度。 8089协处理器,在原理上有点像带有两个DMA通道的处理器,它有一套专门用于输入/输出操作的指令系统,但是8089又和DMA控制器不同,它可以直接为输入/输出设备服务,使主处理器不再承担这类工作。所以,在系统中增加8089协处理器之后,会明显提高主处理器的效率,尤其是在输入/输出操作比较频繁

导线截面的选择 1、按经济电流密度选择 线路的投资总费用Z1 Z1 =(F0+αΑ)L 式中:F0—与导线截面无关的线路单位长费用; α—与导线截面相关的线路单位长度单位截面的费用; Α—导线的截面积; L—线路长度。 线路的年运行费用包括折旧费,检修维护费和管理费等,可用百分比 b 表示为 Z 2=bZ 1=b(F 0+aA)L 线路的年电能损耗费用(不考虑电晕损失): Z 3=3I 2max Ci A PL 式中i —最大负荷损耗小时数。可依据最大负荷利用小时数和功率因数 I max —线路输送的最大电流 C —单位电价 P —导线的电阻率 若投资回收年限为 n 得到导线的经济截面A n A m =I max ) 1(3nb a nPCi + 经济电流密度J n Jn= n A I max =nPCi nb a 3) 1(+ An=n J I max 我国的经济电流密度可以按表查取。

2、按电压损耗校验 在不考虑线路电压损耗的横分量时,线路电压、输送功率、功率因数、电压损耗百分数、导线电阻率以及线路长度与导线截面的关系,可用下式表示 )(01 2?δtg X R U L P m += 式中:δ—线路允许的电压损耗百分比; P m —线路输送的最大功率,MW ; U i —线路额定电压KV L —线路长度m ; R —单位长度导线电阻,Ω/m ; X 0—单位长度线咱电抗,Ω/m ,可取0.4×10-3 Ω/m ; tg ?—负荷功率因数角的正切。 3、按导线允许电流校验 (1)按导线的允许最大工作电流校验 导线的允许最大工作电流为 Im= 1 0) R t t F -(β 其中 R1=[] A P t t 0 0)(21-+ 上二式中a —导线的电阻温度系数 t —导线的允许正常发热最高温度。我国钢芯铝绞线一般采用+70℃,大跨越可采用+90℃;钢绞线的允许温度一般采用+125℃; t 0—周围介质温度,应采用最高气温月的最高平均气温,并考虑太阳辐射的影响; β—导线的散热系数; F —单位长度导线的散热面积,F=md ; R 1—温度t 时单位长度导线的电阻; P 0—温度t 0时导线的电阻率; A —导线的截面积 d —导线的直径; (2)按短路电流校验

单片机硬件系统设 计原则 1

单片机硬件系统设计原则 一个单片机应用系统的硬件电路设计包含两部分内容:一是系统扩展,即单片机内部的功能单元,如ROM、RAM、I/O、定时器/计数器、中断系统等不能满足应用系统的要求时,必须在片外进行扩展,选择适当的芯片,设计相应的电路。二是系统的配置,即按照系统功能要求配置外围设备,如键盘、显示器、打印机、A/D、D/A转换器等,要设计合适的接口电路。 系统的扩展和配置应遵循以下原则: 1、尽可能选择典型电路,并符合单片机常规用法。为硬件系统的标准 化、模块化打下良好的基础。 2、系统扩展与外围设备的配置水平应充分满足应用系统的功能要求,并留有适当余地,以便进行二次开发。 3、硬件结构应结合应用软件方案一并考虑。硬件结构与软件方案会产生相互影响,考虑原则是:软件能实现的功能尽可能由软件实殃,以简化硬件结构。但必须注意,由软件实现的硬件功能,一般响应时间比硬件实现长,且占用CPU时间。 2

4、系统中的相关器件要尽可能做到性能匹配。如选用CMOS芯片单片机构成低功耗系统时,系统中所有芯片都应尽可能选择低功耗产品。 5、可靠性及抗干扰设计是硬件设计必不可少的一部分,它包括芯片、器件选择、去耦滤波、印刷电路板布线、通道隔离等。 6、单片机外围电路较多时,必须考虑其驱动能力。驱动能力不足时,系统工作不可靠,可经过增设线驱动器增强驱动能力或减少芯片功耗来降低总线负载。 7、尽量朝”单片”方向设计硬件系统。系统器件越多,器件之间相互干扰也越强,功耗也增大,也不可避免地降低了系统的稳定性。随着单片机片内集成的功能越来越强,真正的片上系统SoC已经能够实现,如ST公司新近推出的μPSD32××系列产品在一块芯片上集成了80C32核、大容量FLASH 存储器、SRAM、A/D、I/O、两个串口、看门狗、上电复位电路等等。单片机系统硬件抗干扰常见方法实践 影响单片机系统可靠安全运行的主要因素主要来自系统内部和外部的各种电气干扰,并受系统结构设计、元器件选择、安装、制造工艺影响。这些都构成单片机系统的干扰因素,常会导致单片机系统运行失常,轻则影响产品质量和产量,重则会导致事故,造成重大经济损失。 3

计算机系统概述 现代人都知道,计算机由硬件系统和软件系统组成,但是不了解计算机的产生和设计原理,很难真正理解计算机的结构。 从刀耕火种到坐在计算机前冲浪,人类经历了漫长的探索,在这种艰辛且充满惊喜的探索中计算机一步步向我们的理想逼近。 第一节计算机的创始及结构 一、从原始计数法到机械计算机 在远古时代,人类首先从自身找到了最原始的计数工具——手,用手指来计数。为了能表达比10个手指更多的数目,古代人们想出第二种计数工具——石子。石子、贝壳、绳结、木棒不但作为统计财产、人数、猎物的工具,还能保留下统计的结果,这是现代计算机原理中存储思想的最初萌芽。 大约1000多年前,东方文明古国——中国开始使用算盘,这是世界上最古老的、流传最广的计算工具。古代算盘是用小棒(或石子、金属块等)排放在不同位置上,表示不同的位权,并按此进位与借位。可见,那时已经有了进位计数的概念。 1642年,19岁的法国数学家布莱斯·帕斯卡(Blaise Pascal)发明了装有手转圆轮的机械加法器。 帕氏加法器里,一个圆轮代表一位数。轮上分为10个相等部分,刻有0~9十个数字。做加法时,顺时针转动圆轮,当转到0刻度,便自动将高位圆轮带进一格。巴氏加法器用纯粹机械运动代替人们的思考和记录,表示人类开始向自动计算工具的迈进。为了纪念他,程序设计语言Pascal就是以他的名字命名的。 现代计算机的先驱者是英国的数学家查尔斯·巴贝奇(Charles Babbage)(1792一1871)。1833年在他的微分分析机(differential analyzer)的设计方案中,他天才地提出了计算工具至少必须具有五个独立的部分: ①输入部分送入需要处理的问题和信息.; ②存储库保存信息,以便机器使用; ③运算室能进行各种实际的运算; ④控制器指挥机器按顺序工作; ⑤输出部分送出问题处理的结果。 这台机器仍属于机械计算机,但是他的思想在当时确实太先进了,直至100多年后才开发了电子计算机。巴贝奇的许多观点被一位女伯爵、著名的女诗人Augusta AdaByron记载下来,并深入分析。她可以算是世界上第一个计算机程序设计员,程序设计语言Ada则因她的荣耀而命名。 二、电子计算机的诞生 聪明的人脑可以记忆、可以计算、可以判断,但是成功地描述、模拟乃至制造出大脑功

2 系统硬件设计 2.1 系统总体设计结构 太阳能热水器控制器主要由温度水位数据采集模块、单片机控系统。本次设计选用的是AT89C52单片机作为核心控制器,组成热水器微控制系统。传感器采用的是单片集成两端感温电流源DS18B20温度传感器,用于检测水温,并负责将检测到的水压转换成0~5V的模拟信号,然后通过ADC0832模数转换器把检测到的温度电压信号转换成数字信号,一方面由单片机AT89C52完成最终完成太阳能热水器控制器的控制功能,另一方面通过LED显示当前温度和水位值,另外一方面与温度和水位设定值进行比较、运算,根据结果发出相应的上水、加热指令,对热水器的温度和水位进行控。 2.2 温度检测电路 温度检测部分是实现温度智能控制的重要环节,只有准确地检测出温度,才能通过软件实现辅助加热。其性能的好坏直接影响系统的性能,对于温度检测,目前比较理想的是集成温度传感器DS18B20,因此温度传感器采用是美国模拟器件公司生产的单片集成两端感温电流源DS18B20。DS18B20温度传感器是一种已经IC化的温度感测器,它会将温度转换为电流,在单片机的各种课本中经常看到。其规格如下: (1)温度每增加1℃,它会增加1μA输出电流; (2)可测量范围-55℃至125℃; (3)供电电压范围+3V至+5V。 AD590的管脚图及元件符号如2.2所示:

图2.2 DS18B20的管脚图及元件符号 DS18B20的输出电流值说明如下: 其输出电流是以绝对温度零度(-273℃)为基准,每增加1℃,它会增加1μA输出电流,因此在室温25℃时,其输出电流Iout=(273+25)=298μA。 2.2.1 DS18B20的主要特性 (1)适应电压范围更宽,电压范围:3.0~5.5V,在寄生电源方式下可由数据线供电; (2)独特的单线接口方式,DS18B20在与微处理器连接时仅需要一条口线即可实现微处理器与DS18B20的双向通讯; (3)DS18B20支持多点组网功能,多个DS18B20可以并联在唯一的三线上,实现组网多点测温; (4)DS18B20在使用中不需要任何外围元件,全部传感元件及转换电路集成在形如一只三极管的集成电路内; (5)温范围-55℃~+125℃,在-10~+85℃时精度为±0.5℃; (6)可编程的分辨率为9~12位,对应的可分辨温度分别为0.5℃、0.25℃、0.125℃和0.0625℃,可实现高精度测温; (7)在9位分辨率时最多在 93.75ms内把温度转换为数字,12位分辨率时最多在750ms内把温度值转换为数字,速度更快; (8)测量结果直接输出数字温度信号,以"一线总线"串行传送给CPU,同时可传送CRC校验码,具有极强的抗干扰纠错能力; (9)负压特性:电源极性接反时,芯片不会因发热而烧毁,但不能正常工作。 2.2.2 DS18B20工作原理 图2.3 DS18B20测温原理图 DS18B20的读写时序和测温原理与DS1820相同,只是得到的温度值的位数因分辨率不同而不同,且温度转换时的延时时间由2s 减为750ms。 DS18B20测温原

第三章系统硬件设计 3.1 孵化恒温箱的介绍 本系统使用单片机AT89C2051来实现对孵化箱温度的控制,蛋类孵化是一个复杂的生物学过程,其内部环境条件随着不同的孵化进程,发生较大的变化。孵化温度一般就认为是孵箱内部温度,孵化温度控制的原则和依据“看胎施温”是孵化温度控制的原则。孵化温度控制的影响因素孵化箱的类型、规模、密封程度、进出气孔的大小、加热系统与孵化规模的匹配程度、孵化的家禽种类、孵化箱的室温等等,每个因素的变化都会影响到孵化温度的稳定。 温度是家禽孵化的首要条件,保持合适的温度是获得较高孵化率及健雏率的前提,虽然孵化的最佳温度是37.8℃,然而在生产中还应该根据实际情况来进行温度的控制,本文就鸡种蛋孵化不同情况下的温度控制进行论述。孵化是养鸡生产中一项重要的技术环节。种蛋质量和孵化条件影响种蛋的孵化率和健雏率,而在孵化条件中,温度自始至终是禽蛋孵化中的主要矛盾,起主导作用。根据胚胎发育状况掌握好孵化温度是禽蛋孵化稳产高产的关键,即必须给胚胎提供一个最适宜的环境温度,这样才能正常完成胚胎的发育,获得较高的孵化率和健雏率。虽然在孵化中有一个最佳温度。然而在实际生产中,影响温度的因素很多。以下是鸡种蛋孵化生产中温度控制的一些基本原则。温度范围与最佳温度孵化中低于某一温度胚胎发育将被抑制。要高于某一温度,胚胎才开始发育,这一温度被称为“生理零度”,也叫临界温度,一般认为鸡的生理零度约为23.9℃,同时胚胎发育对环境温度有一定的适应能力,以鸡为例,温度在35~40.5℃之间,都会有一些种蛋孵出小鸡。在35~40.5℃之间这个温度范围内有一个最佳温度,应该环境温度保持在24~26℃,孵化箱内的最佳温度为37.8℃。环境温度对孵化有一定的影响,环境温度的高低主要影响孵化过程温度控制的精确度。在生产中一般根据不同地域、不同季节而灵活掌握。 恒温孵化和变温孵化是根据环境温度的不同而经常采用的两种孵化方式,恒温孵化与变温孵化如果操作恰当均可取得较好的效果。恒温孵化是在孵化过程中把温度控制在37.0~38.0℃之间,恒温孵化对孵化的环境要求条件较高,环境温度应该保持在22~26℃之间,并且要通风良好。变温孵化是根据孵化机类型、孵化室温度和胚胎发育日龄,给予不同的温度。如果环境温度低于20℃,则孵化温度可比最佳温度高0.5~0.7℃;如果环境温度高于30℃,则可以降低孵化温度0.2~0.6℃。表3.1为一个变温孵化方案[3]。

计算机系统的硬件和软件 一、计算机的发展与未来: 1、计算机的诞生(重点):(时间、名称、地点):1946年,第一台计算机ENIAC(埃尼阿克)诞生于美国。 2、计算机的发展(重点)(四代发展换代的主要标志为使用的电子元件的不同。)每代使用的电子元件分别是什么。 计算机各代划分及特征简表 计算机起始年份使用的电子元件应用范围 第一代1946—1959 电子管科学计算 第二代1959—1965 晶体管科学计算、数据处理 第三代1965—1971 中小规模集成电路科学计算、数据处理、过程控制第四代1971—至今大规模集成电路或超大规模集成电路社会、生活各个领域 3、计算机的特点、分类。(重点) 计算机的特点:速度快、精度高、大容量(存储能力)、多功能、高智能。 计算机的分类(以其性能分类、与体积无关):巨型机、大型机、中型机、小型机和微机。 4、计算机的应用及发展趋势:了解 二、信息的数字化表示: 1、感性了解数字信号和模拟信号。 2、进制的引入。(月为12进制、时间为24进制、日常计数用十进制、理解逢几进1) 3、计算机能识别(或直接处理)的是二进制数。 4、二进制的重要性:人与计算机的交流的介质 三、计算机的硬件结构: 1、电脑是模仿人脑进行工作的(这也是“电脑”名称的来源),其部件如输入设备、存储器、运算器、控制器、输出设备等分别与人脑的各种功能器官对应,以完成信息的输入、处理、输出。 ①.一切工作都是在控制器的指挥下进行的 ②由输入设备输入信息 ③由运算器处理信息 ④由输出设备输出信息 ⑤.由存储器记录信息 2、CPU的重要性:CPU,即中央处理器,由运算器与控制器组成。是计算机的指挥中心。 3、内存与外存的区别(重点):内存容量较小,存取信息的速度快,带电时可暂时存储,断电后丧失存储能力;外存容量大,存取信息的速度较慢,无论是否带电都具有存储功能。 4、信息在计算机中存储的形式(强调以文件形式存放、以二进制数形式存储) 5、计算机中存储信息的基本单位是字节(B),及其换算。分清b(一个二进制位)和B(存储器中最小的单位字节)的区别。 1B=8b(b为二进制位)1KB=1024B(K为千字节) 1MB=1024KB (MB为兆字节)1GB=1024MB (GB为吉字节) 一个汉字占两个字节、一个字母占一个字节。 四、计算机硬件: 1、了解主机箱内有哪些主要设备:CPU、21、内存、外存、显示卡、声卡 2、常用的输入设备和输出设备。(磁盘驱动器既是输出设备,又是输入设备,普通光驱只能输入,刻录光驱能输入也能输出。) 五、计算机软件

导线截面的选择 1、按经济电流密度选择 线路的投资总费用Z1 Z1 =(F0+αΑ)L 式中:F0—与导线截面无关的线路单位长费用; α—与导线截面相关的线路单位长度单位截面的费用; Α—导线的截面积; L—线路长度。 线路的年运行费用包括折旧费,检修维护费和管理费等,可用百分比 b 表示为 Z 2=bZ 1=b(F 0+aA)L 线路的年电能损耗费用(不考虑电晕损失): Z 3=3I 2max Ci A PL 式中i —最大负荷损耗小时数。可依据最大负荷利用小时数和功率因数 I max —线路输送的最大电流 C —单位电价 P —导线的电阻率 若投资回收年限为 n 得到导线的经济截面A n A m =I max ) 1(3nb a nPCi + 经济电流密度J n Jn= n A I m ax =nPCi nb a 3)1(+ An= n J I m ax 我国的经济电流密度可以按表查取。

2、按电压损耗校验 在不考虑线路电压损耗的横分量时,线路电压、输送功率、功率因数、电压损耗百分数、导线电阻率以及线路长度与导线截面的关系,可用下式表示 )(01 2?δtg X R U L P m += 式中:δ—线路允许的电压损耗百分比; P m —线路输送的最大功率,MW ; U i —线路额定电压KV L —线路长度m ; R —单位长度导线电阻,Ω/m ; X 0—单位长度线咱电抗,Ω/m ,可取0.4×10-3 Ω/m ; tg ?—负荷功率因数角的正切。 3、按导线允许电流校验 (1)按导线的允许最大工作电流校验 导线的允许最大工作电流为 Im= 1 0) R t t F -(β 其中 R1=[] A P t t 0 0)(21-+ 上二式中a —导线的电阻温度系数 t —导线的允许正常发热最高温度。我国钢芯铝绞线一般采用+70℃,大跨越可采用+90℃;钢绞线的允许温度一般采用+125℃; t 0—周围介质温度,应采用最高气温月的最高平均气温,并考虑太阳辐射的影响; β—导线的散热系数; F —单位长度导线的散热面积,F=md ; R 1—温度t 时单位长度导线的电阻; P 0—温度t 0时导线的电阻率; A —导线的截面积 d —导线的直径; (2)按短路电流校验

毕业论文 题目:ARM9系统的硬件设计 学员姓名黄俊礼 学号XXXXXXXX 所在单位电子技术学院 指导教师罗长远 完成日期2007年7月2日

摘要 本文首先对ARM9系统的基本原理进行简单的介绍,然后从具体的工程应用出发,详细介绍ARM9系统硬件开发的具体流程,包括元器件的选型,原理图的绘制,PCB的设计,焊接与调试等。工程所使用的绘图软件是Protel DXP,ARM9系统所选用的CPU是三星公司的S3C2410。 关键词:ARM9系统;PCB设计;Protel DXP;S3C2410 Abstract At first, this article has a summary introduction of keystone about advances risc machines, and then, it gives the material flow of hardware design on ARM9 system which is based on real engineering application, including choose the components, protract schematic, design the PCB, jointing and testing, and so on. The software of protracting in the engineering is Protel DXP, and the CPU used in system is SamSung S3C2410. Key Words: Advances RISC Machines;Printed Circuit Board Design;Protel DXP;S3C2410

计算机硬件发展史概述 航天学院 物理电子学 摘要:计算机硬件的性能直接决定着计算机的性能。计算机硬件的发展大致经历了机械计算机、电子计算机、晶体管计算机、集成电路时代,功能越来越强,性能越来越高,技术越来越完善。 关键词:计算机,硬件,发展历程,性能 1计算机的诞生 1.1诞生历程 现代计算机问世之前,计算机的发展经历了机械式计算机、机电式计算机和萌芽期的电子计算机三个阶段。 从17世纪初开始,欧洲一批数学家已经开始设计和制造能进行简单数学运算的机器。最初,1614年苏格兰人John Napier发表了一篇论文,其中提到他发明了一种可以计算四则运算和方根运算的精巧装置,不久后有了计算尺的发明。1642年,著名的法国数学家帕斯卡在计算尺的基础上,采用与钟表类似的齿轮传动装置,制成了最早的十进制加法器,可以进行加减运算,一般认为这是第一台机械式计算机,如图1.1所示。1678年,德国数学家莱布尼茨制成的演算机,进一步解决了十进制数的乘、除运算。1822年,英国人巴贝奇设计了能根据数学议程进行运算的差分机,后来又于1834年提出分析机的设想。在这之后的一百多年,伴随着电磁学、电工电子学不断取得重大进展,现代计算机的雏形逐渐形成。 图1.1帕斯卡的加法器 1.2电子计算机的诞生 20世纪30年代,随着数学和物理等科学技术的蓬勃发展,数值分析得到重视,大量的

运算迫切需要能替代人工运算的先进计算机。第二次世界大战爆发前后,军事科学技术对高速计算工具的需要非常迫切,比如导弹弹道问题就需要大量的科技人员去计算,电子计算机就是在这样的背景下诞生的。 第一台真正意义上的计算机诞生于1946年,是宾夕法尼亚大学物理学家谟克利和工程师埃克特领导数人花时3年多研制而成的,并被命名为ENIAC。这台计算机含有电子管18000个,电阻和电容数万个,占地170平方米,功率为25千瓦,最初是用于计算导弹弹道和氢弹的研制。当ENIAC公开展示时,一条炮弹的轨迹用20s就能算出,比炮弹本身的飞行时间还要短。 2计算机硬件的发展历史 2.1硬件简介 硬件系统通常指机器的物理系统,是看得到、摸得着的物理器件。现在我们所使用的计算机硬件系统的结构基本是沿用了由著名数学家冯·诺依曼提出的模型,它由运算器、控制器、存储器、输入设备、输出设备五大功能部件组成,如图2.1所示。当我们打开计算机的机箱时,可以看到主机板,它是主机中的基础部件,在它上面密集地安装着CPU、内存储器,输入输出接口等。一台计算机的硬件的核心是CPU,它一般是将运算器、控制器配以寄存器组集成在一块芯片上。 图2.1 硬件系统基本组成和工作原理 2.2计算机硬件的发展 2.2.1计算机硬件发展综述 现代计算机的硬件发展经历了电子计算机、晶体管计算机、集成电路时代以及大规模和超大规模集成电路时代这四个重要阶段。每个阶段的基本性能和特点如表2.2.1所示。计算机的发展遵从著名的摩尔定律,即当价格不变时,集成电路上可容纳的晶体管数目,约每隔

软硬件配置方案设计 很多时候我们需要将软硬件完美结合在一起才能达到目标要求,下面就是为您收集的软硬件配置方案设计的相关文章,希望可以帮到您,如果你觉得不错的话可以分享给更多小伙伴哦! 随着现代网络技术的发展,嵌放式系统如单片机、DSP等系统 对接入网络的需求日益增加,例如具有远程抄表功能的电表系统、楞以进行远程控制的信息电系统等。本文采用TI公司的TMS320VC33DSP 芯片设计与Realtek公司的RTL8019网卡的硬件接口电路,并在DSP 中用软件实现TCP/IP协议,使DSP芯片具备上网功能,从而可以用 计算机通过网卡与DSP电路板进行大量数据交换并对其进行控制。 1、硬件设计 DSP与网卡的硬件接口电路图如图1所示。 DSP的数据总线低16位接ISA网卡的16位数据线,ISA网卡的IOCS16线接高电平,设置网卡为16位的模式。 网卡共有20根地址线。将A7~A8、A10~A19接地,A0~A6和A9分别接DSP的A0~A7,用到的网卡地址为0240H~025FH,映射到DSP的Page3空间,地址映射为C000C0H~C000DFH。 DSP的Reset信号用于复位网卡,由于DSP的Reset信号低有效,而网卡的Reset信号高有效,故中间应接非门。 DSP的Page3和R/W信号用于选能网卡的读写信号IOR、IOW, 实现的逻辑关系如图2所示。 IORQ是网卡的中断9,通过非门后接DSP的INT1引脚。

RTL8019网卡有三种工作方式: 第一种为跳线方式,网卡的I/O和中断由跳线决定; 第二种为即插即用方式,由软件进行自动配置plugandplay; 第三种为免跳线方式,网卡的I/O和中断由外接的93C46里的内容决定。 计算机上一是即插即用方式,为了降低软件编程的复杂度,将网卡设置为跳线方式。 上述所有的译码逻辑都在EPM7129中实现。 74ALVC16425是总线驱动芯片,可实现3.3V到5V的电平转换。由于TMS320VC33和EPM7128是3.3V的器件,而ISA总线是5V的,所以信号线不能直接连接,需要通过74ALVC164245进行电平转换和隔离。 2、软件设计 2.1网卡硬件驱动程序的设计 网卡驱动程序主要包括以下几部分: (1)NIC的初始化 NIC是网络接口控制芯片,它负责网络上数据的接收和发送。为了能够使NIC启动并处于准备接收或准备发送数据的状态,必须对相关的寄存器进行初始化。这些寄存器包括CR、DCR、RBCR、PSTART、PSTOP、ISR、IMR、PAR0~PAR5、MAR0~MAR7、CURR、TCP、RCR等。 (2)中断服务程序

引言 嵌入式系统是以应用为中心,软件硬件可裁剪,适应应用系统对功能、可靠性、成本、体积、功耗等综合性严格要求的专用计算机系统。本文主要研究了基于S3C2410的嵌入式最小系统,围绕其设计出相应的存储器、总电源电路、复位电路等一系列电路模块。 嵌入式最小系统 嵌入式最小系统即是在尽可能减少上层应用的情况下,能够使系统运行的最小化模块配置。以ARM内核嵌入式微处理器为中心,具有完全相配接的Flash电路、SDRAM电路、JTAG电路、电源电路、晶振电路、复位信号电路和系统总线扩展等,保证嵌入式微处理器正常运行的系统,可称为嵌入式最小系统。对于一个典型的嵌入式最小系统,以ARM处理器为例,其构成模块及其各部分功能如图1所示,其中ARM微处理器、FLASH和SDRAM模块是嵌入式最小系统的核心部分。

微处理器——采用了S3C2410A ; 电源模块——本电源运用5V 的直流电源通过两个三端稳压器转换成我们所设计的最小系统所需要的两个电压,分别是3.3V 和1.8V ,3.3V 的给VDDMOP ,VDDIO,VDDADC 等供电,而1.8V 的给VDDi 和RTC 供电。 时钟模块(晶振)——通常经ARM 内部锁相环进行相应的倍频,以提供系统各模块运行所需的时钟频率输入。32.768kHz 给RTC 和Reset 模块,产生计数时钟,10MHz 作为主时钟源; Flash 存储模块——存放嵌入式操作系统、用户应用程序或者其他在系统掉电后需要保存的用户数据等; SDRAM 模块——为系统运行提供动态存储空间,是系统代码运行的主要区域; 复位模块——实现对系统的复位; 1.8V 电源LDD 稳压 SDARM 32MB (use JTAG 接口 REST 电路256字 节E2PROM E2PROM UART 串口功能扩展 32768Hz 晶振RTC 时钟源 S3C2410A-20 (ARM920T) (16KB I-Cache,16KB D-Cache) SDARM 32MB (use NOR FLASH 2MB (use

第四章 均布荷载下架空线的计算 在高压架空线路的设计中,不同气象条件下架空线的弧垂、应力、和线长占有十分重要的位置,是输电线路力学研究的主要内容。这是因为架空线的弧垂和应力直接影响着线路的正常安全运行,而架空线线长微小的变化和误差都会引起弧垂和应力相当大的改变。设计弧垂小,架空线的拉应力就大,振动现象加剧,安全系数减少,同时杆塔荷载增大因而要求强度提高。设计弧垂过大,满足对地距离所需杆塔高度增加,线路投资增大,而且架空线的风摆、舞动和跳跃会造成线路停电事故,若加大塔头尺寸,必然会使投资再度提高。因此设计合适的弧垂是十分重要的。 架空线悬链方程的积分普遍形式 假设一:架空线是没有刚度的柔性索链,只承受拉力而不承受弯矩。 假设二:作用在架空线上的荷载沿其线长均布;悬挂在两基杆塔间的架空线呈悬链线形状。 由力的平衡原理可得到一下结论: 1、架空线上任意一点C 处的轴向应力σx 的水平分量等于弧垂最低点处的轴向应力σ0,即架空线上轴向应力的水平分量处处相等。 σx cos θ=σ0 2、架空线上任意一点轴向应力的垂直分量等于该点到弧垂最低点间线长L oc 与比载γ之积。 σx sin θ=γL oc 推导出: 0 t g L o c γ θσ= 0 dy L oc dx γσ= 即 0 'y L o c γσ= (4-3) 由(4-3)推导出 10 ()dy sh x C dx γσ=+ (4-4) 结论:当比值γ/σ0一定时,架空线上任一点处的斜率于该点至弧垂最低点之间的线长成正比。最 后推到得到架空线悬链方程的普遍积分形式。C1、C2为积分常数,其值取决于坐标系的原点位置。

计算机硬件系统 一、电源 电源是电脑中不可缺少的供电设备,它的作用是将220V 交流电转换为电脑中使用的5V、12V、3.3V直流电,其性能的好坏,直接影响到其他设备工作的稳定性,进而会影响整机的稳定性。手提电脑在自带锂电池情况下,为手提电脑提供有效电源。 二、主板 主板是电脑中各个部件工作的一个平台,它把电脑的各个部件紧密连接在一起,各个部件通过主板进行数据传输。也就是说,电脑中重要的“交通枢纽”都在主板上,它工作的稳定性影响着整机工作的稳定性。 三、中央处理器 CPU即中央处理器,是一台计算机的运算核心和控制核心。其功能主要是解释计算机指令以及处理计算机软件中的数据。CPU由运算器、控制器、寄存器、高速缓存及实现它们之间联系的数据、控制及状态的总线构成。作为整个系统的核心,CPU也是整个系统最高的执行单元,因此CPU已成为决定电脑性能的核心部件,很多用户都以它为标准来判断电脑的档次。 四、内存

内存又叫内部存储器或者是随机存储器(RAM),分为DDR内存和SDRAM内存,(但是SDRAM由于容量低,存储速度慢,稳定性差,已经被DDR淘汰了)内存属于电子式存储设备,它由电路板和芯片组成,特点是体积小,速度快,有电可存,无电清空,即电脑在开机状态时内存中可存储数据,关机后将自动清空其中的所有数据。内存有DDR、DDR II、DDR III三大类,容量1-64GB。 五、硬盘 硬盘属于外部存储器,机械硬盘由金属磁片制成,而磁片有记忆功能,所以储到磁片上的数据,不论在开机,还是关机,都不会丢失。硬盘容量很大,已达TB级,尺寸有3.5、2.5、1.8、1.0英寸等,接口有IDE、SATA、SCSI等,SATA 最普遍。移动硬盘是以硬盘为存储介质,强调便携性的存储产品。市场上绝大多数的移动硬盘都是以标准硬盘为基础的,而只有很少部分的是以微型硬盘(1.8英寸硬盘等)为基础,但价格因素决定着主流移动硬盘还是以标准笔记本硬盘为基础。因为采用硬盘为存储介质,因此移动硬盘在数据的读写模式与标准IDE硬盘是相同的。移动硬盘多采用USB、IEEE1394等传输速度较快的接口,可以较高的速度与系统进行数据传输。固态硬盘用固态电子存储芯片阵列而制成的硬盘,由控制单元和存储单元(FLASH芯片)组成。

基于底层硬件的软件设计,涉及了设备驱动程序的设计、嵌入式实时操作系统的定制/移植、基于底层硬件的软件体系架构等实用技术。主要包括两个方面的内容:一是通用计算机在Windows、Linux和VxWorks等常见操作系统下的串/并/网络通信实现和USB、ISA、PCI 设备/板卡的驱动程序设计;二是嵌入式应用体系的直接基本软件架构与基于μC/OS、DSP/BIOS、WinCE/EXP、μCLinux及VxWorks等常见嵌入式实时操作系统下的基本软件架构及各类常见嵌入式软件体系下的UART、SPI、CAN、EMAC、ADC、DAC、存储器件等外设/接口的驱动软件设计。书中还介绍了如何使用CPLD/FPGA/PAC等器件进行可编程数字/模拟逻辑软件的设计,进而实现所需的特定外设/接口及其连接与FPGASoPC软硬件协同的设计。请参考《基于底层硬件的软件设计》 软硬件协同设计 一、软硬件协同设计的定义: 软硬件协同设计是指对系统中的软硬件部分使用统一的描述和工具进行集成开发,可完成全系统的设计验证并跨越软硬件界面进行系统优化。 二、软硬件协同设计理论: 首先是系统的描述方法。目前广泛采用的硬件描述语言是否仍然有效?如何来定义一个系统级的软件功能描述或硬件功能描述?迄今为止,尚没有一个大家公认的且可以使用的系统功能描述语言可供设计者使用。 其次是这一全新的设计理论与已有的集成电路设计理论之间的接口。可以预见,这种全新的设计理论应该是现有集成电路设计理论的完善,是建立在现有理论之上的一个更高层次的设计理论,它与现有理论一起组成了更为完善的理论体系。在这种假设下,这种设计理论的输出就应该是现有理论的输入。 第三,这种全新的软硬件协同设计理论将如何确定最优性原则。显然,沿用以往的最优性准则是不够的。除了芯片设计师们已经熟知的速度、面积等硬件优化指标外,与软件相关的如代码长度、资源利用率、稳定性等指标也必须由设计者认真地加以考虑。 第四,如何对这样的一个包含软件和硬件的系统的功能进行验证。除了验证所必须的环境之外,确认设计错误发生的地方和机理将是一个不得不面对的课题。最后,功耗问题。传统的集成电路在功耗的分析和估计方面已有一整套理论和方法。但是,要用这些现成的理论来分析和估计含有软件和硬件两部分的SOC将是远远不够的。简单地对一个硬件设计进行功耗分析是可以的,但是由于软件运行引起的动态功耗则只能通过软硬件的联合运行才能知道。 其实,还可以举出很多新理论要涉及的问题,它们一起构成了面向SOC的软硬件协同设计的理论体系。 软硬件协同设计所涉及到的内容有:HW-SW 协同设计流程、HW-SW 划分、HW-SW 并行综合、HW-SW 并行仿真。 三、软件硬件协同设计的设计流程:

输电线路设计计算公式汇总 均布荷载下架空线的计算 在高压架空线路的设计中,不同气象条件下架空线的弧垂、应力、和线长占有十分重要的位置,是输电线路力学研究的主要内容。这是因为架空线的弧垂和应力直接影响着线路的正常安全运行,而架空线线长微小的变化和误差都会引起弧垂和应力相当大的改变。设计弧垂小,架空线的拉应力就大,振动现象加剧,安全系数减少,同时杆塔荷载增大因而要求强度提高。设计弧垂过大,满足对地距离所需杆塔高度增加,线路投资增大,而且架空线的风摆、舞动和跳跃会造成线路停电事故,若加大塔头尺寸,必然会使投资再度提高。因此设计合适的弧垂是十分重要的。 架空线悬链方程的积分普遍形式 假设一:架空线是没有刚度的柔性索链,只承受拉力而不承受弯矩。 假设二:作用在架空线上的荷载沿其线长均布;悬挂在两基杆塔间的架空线呈悬链线形状。 由力的平衡原理可得到一下结论: 1、架空线上任意一点C 处的轴向应力σx 的水平分量等于弧垂最低点处的轴向应力σ0,即架空线上轴向应力的水平分量处处相等。 σx cos θ=σ0 2、架空线上任意一点轴向应力的垂直分量等于该点到弧垂最低点间线长L oc 与比载γ之积。 σx sin θ=γL oc 推导出: 0 tg Loc γ θσ= dy Loc dx γ σ= 即 0'y Loc γσ= (4-3) 由(4-3)推导出 10 ()dy sh x C dx γ σ=+ (4-4) 结论:当比值γ/σ0一定时,架空线上任一点处的斜率于该点至弧垂最低点之间的线长成正比。最

后推到得到架空线悬链方程的普遍积分形式。C1、C2为积分常数,其值取决于坐标系的原点位置。 0(1)20 y ch x C C σγγσ= ++ (4-5) 等高悬点架空线的弧垂、线长和应力 等高悬点架空线的悬链方程 等高悬点是指架空线的两个挂点高度相同。由于对称性,等高悬点架空线的弧垂最低点位于档距中央,将坐标原点取在该点,如图: 0(1)0 y ch x σγγσ= - (4-6) 由上式可以看出,架空线的悬链线具体形状完全由比值σ0 /γ决定,即无论何种架空线、 何种气象条件。只要σ0 /γ相同,架空线的悬挂曲线形状就相同。在比载γ一定的情况下,架空线的水 平应力是决定悬链线形状的唯一因素,所以平时架空线的水平张力对架空线的空间形状有着决定性的影响。 等高悬点架空线的弧垂 架空线上任意一点的弧垂是指该点距两悬点连线的垂直距离。在设计中需要计算架空线任意一点x 处的弧垂f x ,以验算架空线对地的安全距离。参照图4-2 20000 2(1)24B l l f y ch sh σσγγγσγσ== -= 0(1)20 B l y ch σγγσ= - 可得到式: 0 1100 2() 22x x l x f sh sh σγγγ σσ-= (4-8) 在档距中央,弧垂有最大值,此时x=0或x 1=L/2,所以有 20000 2(1)24B l l f y ch sh σσγγγσγσ== -= (4-9) 架空线的弧垂一般指的是最大弧垂。最大弧垂在线路的设计、施工中占有重要的位置。 等高悬点架空线的线长 L oc 弧垂最低点O 与任意一点C 之间的架空线的线长。