XDC约束技巧之I/O篇 (上)

《XDC约束技巧之时钟篇》中曾对I/O约束做过简要概括,相比较而言,XDC中的

I/O约束虽然形式简单,但整体思路和约束方法却与UCF大相径庭。加之FPGA的应用特

性决定了其在接口上有多种构建和实现方式,所以从UCF到XDC的转换过程中,最具挑

战的可以说便是本文将要讨论的I/O约束了。

I/O约束的语法

XDC中可以用于I/O约束的命令包括set_input_delay / set_output_delay和

set_max_delay / set_min_delay 。其中,只有那些从FPGA管脚进入和/或输出都不经过任何时序元件的纯组合逻辑路径可以用set_max_delay / set_min_delay来约束,其余I/O时序路

径都必须由set_input_delay / set_output_delay来约束。如果对FPGA的I/O不加任何约束,Vivado会缺省认为时序要求为无穷大,不仅综合和实现时不会考虑I/O时序,而且在时序

分析时也不会报出这些未约束的路径。

本文以下章节将会着重讨论XDC接口约束和时序分析的基础,介绍如何使用

set_input_delay / set_output_delay对FPGA的I/O时序进行约束。

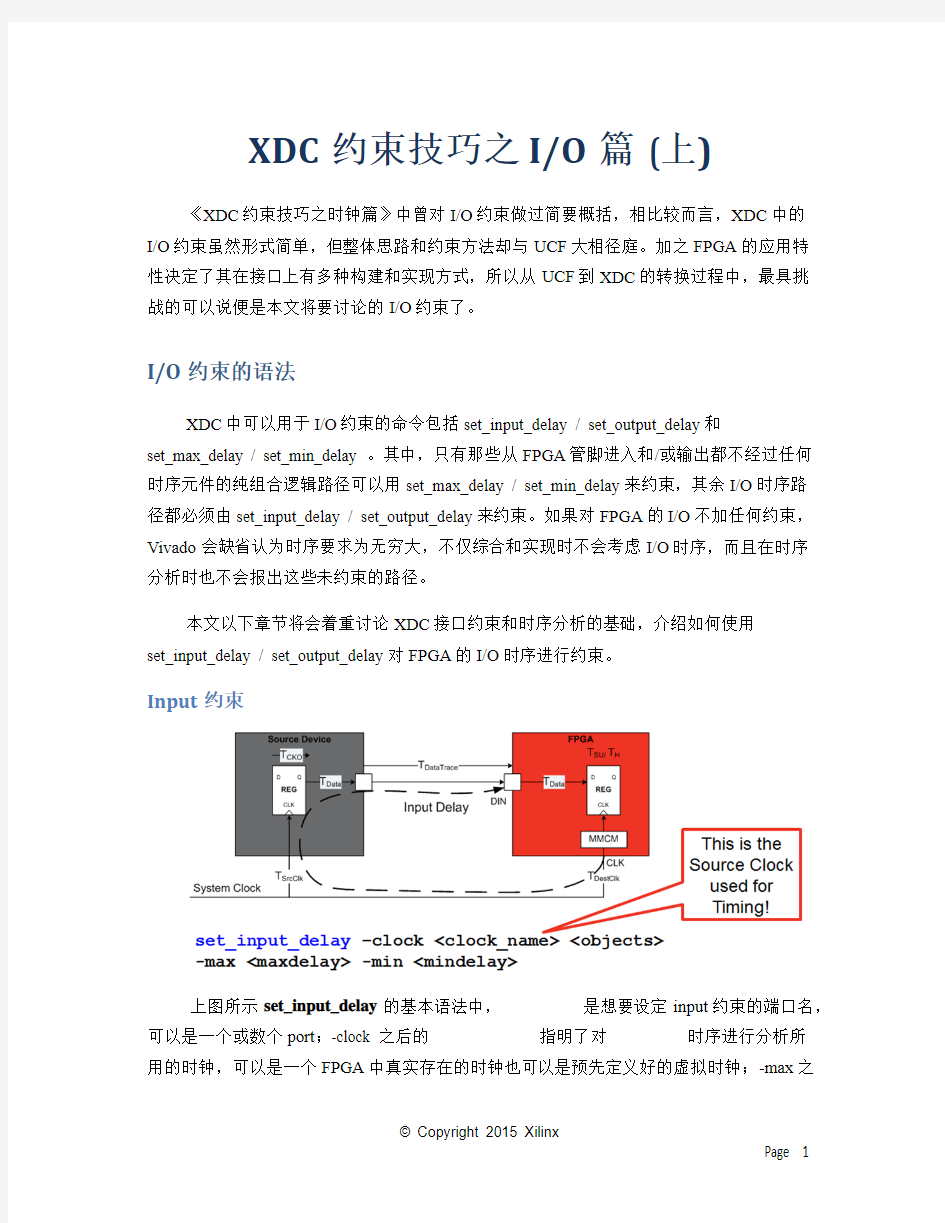

Input约束

上图所示set_input_delay的基本语法中,

用的时钟,可以是一个FPGA中真实存在的时钟也可以是预先定义好的虚拟时钟;-max之

后的

的

上述这些选项是定义Input约束时必须写明的,还有少数几个可选项,如 -add_delay

和 -clock_fall用于DDR接口的约束。

Output约束

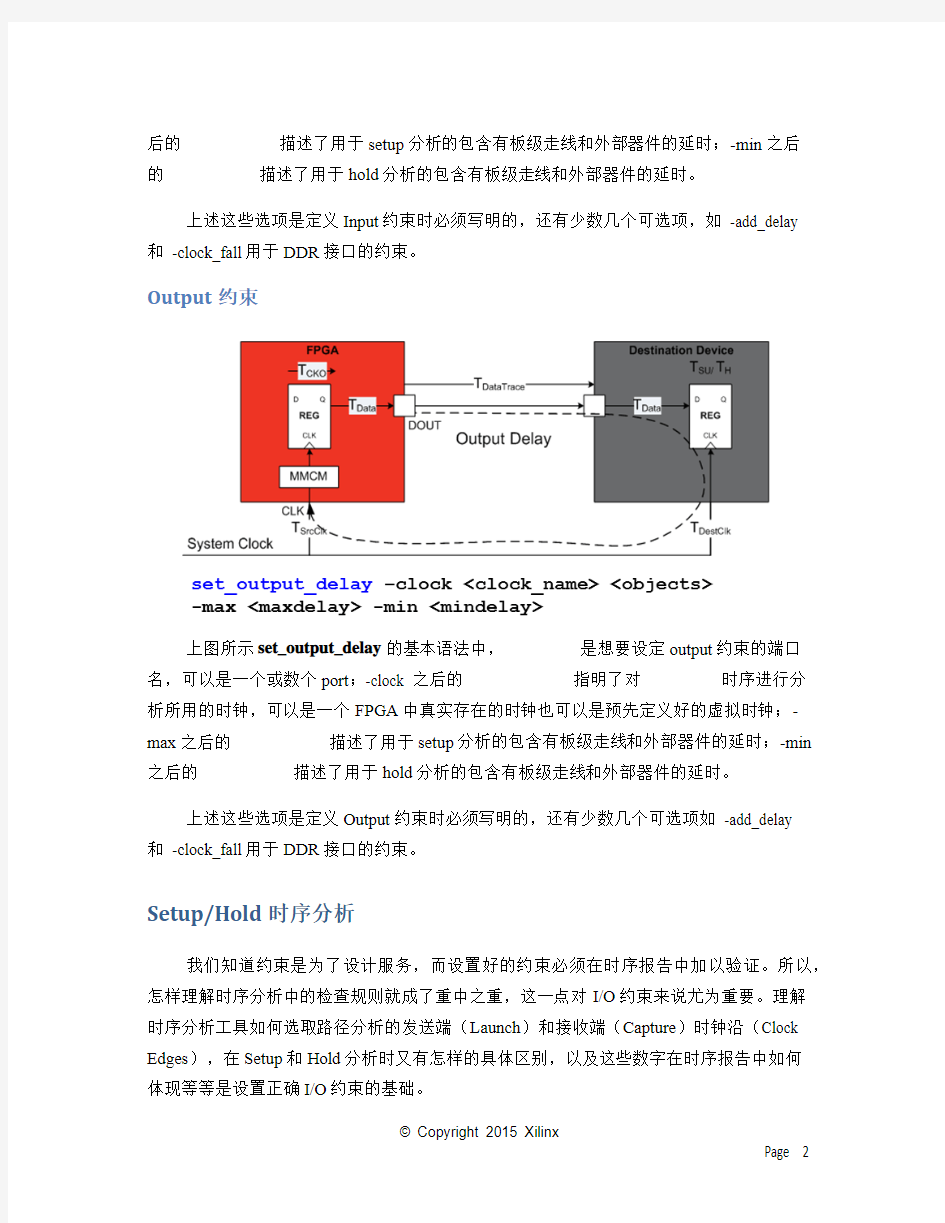

上图所示set_output_delay的基本语法中,

析所用的时钟,可以是一个FPGA中真实存在的时钟也可以是预先定义好的虚拟时钟;-max之后的

之后的

上述这些选项是定义Output约束时必须写明的,还有少数几个可选项如 -add_delay

和 -clock_fall用于DDR接口的约束。

Setup/Hold时序分析

我们知道约束是为了设计服务,而设置好的约束必须在时序报告中加以验证。所以,怎样理解时序分析中的检查规则就成了重中之重,这一点对I/O约束来说尤为重要。理解

时序分析工具如何选取路径分析的发送端(Launch)和接收端(Capture)时钟沿(Clock Edges),在Setup和Hold分析时又有怎样的具体区别,以及这些数字在时序报告中如何

体现等等是设置正确I/O约束的基础。

更具体的时序分析方法以及如何深入解读时序报告等内容将会在后续另开主题文章

详述,这里仅就Setup/Hold分析时对时钟边沿的选择加以描述,便于以下章节的展开。Setup时序分析

同步电路设计中,一般情况下,数据在时钟上升沿发送,在下一个时钟上升沿接收,发送的时钟沿称作Launch Edge,接收沿称作Capture Edge。时序分析中的Setup Check跟Capture Edge的选择息息相关。

在SDR接口的setup分析中,工具如下图这样识别发送和接收时钟沿。

而在DDR接口的setup分析中,因为数据是双沿采样,所以发送和接收时钟沿变成

上升(下降)沿发送,下降(上升)沿接收。

Hold时序分析

Hold Check主要是为了保证数据在接收(采样)端时钟沿之后还能稳定保持一段时间,对Hold分析而言,同一个时钟沿既是Launch Edge也是Capture Edge,这一点对SDR 和DDR(不论是中心对齐还是边沿对齐)都一样。

Input接口类型和约束

由于历史的原因,相当一部分FPGA设计仍然在系统中起到胶合逻辑(Glue Logic)的作用,当然,如今的FPGA中嵌入了高速串行收发器和嵌入式处理器等,早就不仅仅局限于系统设计的配角,反而成为了其中的主角甚至是明星。但数据接口的同步一直是FPGA设计中的常见问题,也是一个重点和难点,很多设计不稳定都是因为数据接口的同步有问题。

FPGA的数据接口同步根据系统级设计方式来讲可以分为系统同步和源同步两种。系统同步接口

系统同步接口(System Synchronous Interface)的构建相对容易,以FPGA做接收侧来举例,上游器件仅仅传递数据信号到FPGA中,时钟信号则完全依靠系统板级来同步。时钟信号在系统级上同源,板级走线的延时也要对齐。正因为这样的设计,决定了数据传递的性能受到时钟在系统级的走线延时和skew以及数据路径延时的双重限制,无法达到更高速的设计要求,所以大部分情况也仅仅应用SDR方式。

对系统同步接口做Input约束相对容易,只需要考虑上游器件的Tcko和数据在板级的延时即可。下图是一个SDR上升沿采样系统同步接口的Input约束示例。

设置和分析I/O约束一定要有个系统级思考的视角,如上右图所示,Launch Edge对应的是上游器件的时钟,而Capture Edge则对应FPGA的输入时钟,正因为是系统同步时钟,所以可以将其视作完全同步而放在一张图上分析,这样一来,就可以用一般时序分析方法来看待问题。

一条完整的时序路径,从源触发器的C端开始,经过Tcko和路径传输延时再到目的触发器的D端结束。放在系统同步的接口时序上,传输延时则变成板级传输延时(还要考虑skew),所以上述 -max 后的数值是Tcko的最大值加上板级延时的最大值而来,而-min 后的数值则是由两个最小值相加而来。

源同步接口

为了改进系统同步接口中时钟频率受限的弊端,一种针对高速I/O的同步时序接口应运而生,在发送端将数据和时钟同步传输,在接收端用时钟沿脉冲来对数据进行锁存,重新使数据与时钟同步,这种电路就是源同步接口电路(Source Synchronous Interface)。

源同步接口最大的优点就是大大提升了总线的速度,在理论上信号的传送可以不受传输延迟的影响,所以源同步接口也经常应用DDR方式,在相同时钟频率下提供双倍于SDR接口的数据带宽。

源同步接口的约束设置相对复杂,一则是因为有SDR、DDR、中心对齐(Center Aligned)和边沿对齐(Edge Aligned)等多种方式,二则可以根据客观已知条件,选用与

系统同步接口类似的系统级视角的方式,或是用源同步视角的方式来设置约束。

如上图所示,对源同步接口进行Input约束可以根据不同的已知条件,选用不同的约

束方式。一般而言,FPGA作为输入接口时,数据有效窗口是已知条件,所以方法2更常见,Vivado IDE的Language Templates中关于源同步输入接口XDC模板也是基于这种方

法。但不论以何种方式来设置Input约束,作用是一样,时序报告的结果也应该是一致的。

知条件和计算方式虽然不同,但却可以得到完全一样的结果。

DDR接口的约束设置

DDR源同步接口的约束稍许复杂,需要将上升沿和下降沿分别考虑和约束,以下以

源同步接口为例,分别就输入接口数据为中心对齐或边沿对齐的方式来举例。

DDR源同步中心对齐输入接口

已知条件如下:

?时钟信号src_sync_ddr_clk的频率: 100 MHz

?数据总线:src_sync_ddr_din[3:0]

?上升沿之前的数据有效窗口 ( dv_bre ) : 0.4 ns

?上升沿之后的数据有效窗口 ( dv_are ) : 0.6 ns

?下降沿之前的数据有效窗口 ( dv_bfe ) : 0.7 ns

?下降沿之后的数据有效窗口 ( dv_afe ) : 0.2 ns

可以这样计算输入接口约束:DDR方式下数据实际的采样周期是时钟周期的一半;

上升沿采样的数据(Rise Data)的-max 应该是采样周期减去这个数据的发送沿(下降沿)之前的数据有效窗口值dv_bfe,而对应的-min 就应该是上升沿之后的数据有效窗口值

dv_are ;同理,下降沿采样的数据(Fall Data)的 -max 应该是采样周期减去这个数据的发

送沿(上升沿)之前的数据有效窗口值dv_bre,而对应的-min 就应该是下降沿之后的数据有效窗口值dv_afe 。

所以最终写入XDC的Input约束应该如下所示:

set period 10.0;

create_clock -period $period -name clk [get_ports src_sync_ddr_clk];

set_input_delay -clock clk -max [expr $period/2 – 0.7] [get_ports src_sync_ddr_din[*]] ; set_input_delay -clock clk -min 0.6 [get_ports src_sync_ddr_din[*]] ;

set_input_delay -clock clk -max [expr $period/2 – 0.4] \

[get_ports src_sync_ddr_din[*]] -clock_fall -add_delay ;

set_input_delay -clock clk -min 0.2 [get_ports src_sync_ddr_din[*]] -clock_fall -add_delay; DDR源同步边沿对齐输入接口

已知条件如下:

?时钟信号src_sync_ddr_clk的频率: 100 MHz

?数据总线:src_sync_ddr_din[3:0]

?上升沿之前的数据skew (skew_bre ) : 0.6 ns

?上升沿之后的数据skew (skew_are ) : 0.4 ns

?下降沿之前的数据skew (skew_bfe ) : 0.3 ns

?下降沿之后的数据skew (skew_afe ) : 0.7 ns

可以这样计算输入接口约束:因为已知条件是数据相对于时钟上升沿和下降沿的skew,所以可以分别独立计算;上升沿的 -max 是上升沿之后的数据skew (skew_are ),对应的-min 就应该是负的上升沿之前的数据skew (skew_bre );下降沿的 -max 是下降沿之后的数据skew (skew_afe ),对应的-min 就应该是负的下降沿之前的数据skew (skew_bfe )。

所以最终写入XDC的Input约束应该如下所示:

create_clock -period 10.0 -name clk [get_ports src_sync_ddr_clk];

set_input_delay -clock clk -max 0.4 [get_ports src_sync_ddr_din[*]] ;

set_input_delay -clock clk -min -0.6 [get_ports src_sync_ddr_din[*]] ;

set_input_delay -clock clk -max 0.7 [get_ports src_sync_ddr_din[*]] -clock_fall -add_delay ;

set_input_delay -clock clk -min -0.3 [get_ports src_sync_ddr_din[*]] -clock_fall -add_delay;

出现负值并不代表延时真的为负,而是跟数据相对于时钟沿的方向有关。请一定牢

记set_input_delay中 -max/-min的定义,即时钟采样沿到达之后最大与最小的数据有效窗

口(set_output_delay中 -max/-min的定义与之正好相反,详见后续章节举例说明)。

在这个例子中,数据是边沿对齐,只要有jitter跟skew的存在,最差情况下,数据有

效窗口在到达时钟采样沿之前就已经结束,所以会有负数出现在-min之后。因此,在实际

应用中,FPGA用作输入的边沿对齐DDR源同步接口的情况下,真正用来采样数据的时

钟会经过一个MMCM/PLL做一定的相移,从而把边沿对齐变成中心对齐。

另外,在经过MMCM/PLL相移后的采样时钟跟同步接口输入的时钟之间需要做

set_false_path的约束(如下述例子)而把那些伪路径从时序报告中剔除,这里不再详述。

set_false_path –setup –rise_from [get_clocks adc_dclk_p] –rise_to [get_clocks clk_outp0_adc_pll_1]

set_false_path –setup –fall_from [get_clocks adc_dclk_p] –fall_to [get_clocks clk_outp0_adc_pll_1]

set_false_path –hold –fall_from [get_clocks adc_dclk_p] –rise_to [get_clocks clk_outp0_adc_pll_1]

set_false_path –hold –rise_from [get_clocks adc_dclk_p] –fall_to [get_clocks clk_outp0_adc_pll_1]

虚拟时钟

在FPGA做系统同步输入接口的情况下,很多时候上游器件送入的数据并不是跟某

个FPGA中已经存在的真实的时钟相关,而是来自于一个不同的时钟,这时就要用到虚拟

时钟(Virtual Clock)。

举例来说,上游器件用一个100MHz的时钟送出数据到FPGA,实际上这个数据每两

个时钟周期才变化一次,所以可以用50MHz的时钟来采样。FPGA有个100MHz的输入时钟,经过MMCM产生一个50MHz 的衍生时钟,并用其来采样上游器件送来的同步数据。

当然,系统级的设计上,必须有一定的机制来保证上游器件中的发送时钟和FPGA中的接收时钟的时钟沿对齐。

此时,我们可以借助虚拟时钟的帮助来完成相应的Input接口约束。

create_clock -period 10 -name clk_100 [get_ports i_clk_100MHz] ;

create_clock -period 20 -name clk_50_virtual ;

set_input_delay -max 5.2 -clock clk_50_virtual [get_ports i_data_50] ;

set_input_delay -min 2.0 -clock clk_50_virtual [get_ports i_data_50] ;

篇幅所限,对XDC中I/O约束的设计思路、分析方法以及如何具体设置Input接口约束的讨论就到这里,下一篇我们接着分析如何设置Output接口约束,看看 Vivado中有什么方式可以帮助用户准确便捷地定义接口时序约束。

Ally Zhou2015-2-28 于Xilinx上海Office

时序分析基础与时钟约束实例(1) 文中实例配套SF-CY3开发套件。更多内容请参考《SF-CY3 FPGA套件开发指南》。 何谓静态时序分析(STA,Static Timing Analysis)? 首先,设计者应该对FPGA内部的工作方式有一些认识。FPGA的内部结构其实就好比一块PCB板,FPGA的逻辑阵列就好比PCB板上的一些分立元器件。PCB通过导线将具有相关电气特性的信号相连接,FPGA也需要通过内部连线将相关的逻辑节点导通。PCB板上的信号通过任何一个元器件都会产生一定的延时,FPGA的信号通过逻辑门传输也会产生延时。PCB的信号走线有延时,FPGA的信号走线也有延时。这就带来了一系列问题,一个信号从FPGA的一端输入,经过一定的逻辑处理后从FPGA的另一端输出,这期间会产生多大的延时呢?有多个总线信号从FPGA的一端输入,这条总线的各个信号经过逻辑处理后从FPGA 的另一端输出,这条总线的各个信号的延时一致吗?之所以关心这些问题,是因为过长的延时或者一条总线多个信号传输时间的不一致,不仅会影响FPGA本身的性能,而且也会给FPGA之外的电路或者系统带来诸多问题。 言归正传吧,之所以引进静态时序分析的理论也正是基于上述的一些思考。它可以简单的定义为:设计者提出一些特定的时序要求(或者说是添加特定的时序约束),套用特定的时序模型,针对特定的电路进行分析。分析的最终结果当然是要求系统时序满足设计者提出的要求。 下面举一个最简单的例子来说明时序分析的基本概念。假设信号需要从输入到输出在FPGA内部经过一些逻辑延时和路径延时。系统要求这个信号在FPGA内部的延时不能超过15ns,而开发工具在执行过程中找到了如图所示的一些可能的布局布线方式。那么,怎样的布局布线能够达到系统的要求呢?仔细分析一番,发现所有路径的延时可能为14ns、15ns、16ns、17ns、18ns,有两条路径能够满足要求,那么最后的布局布线就会选择满足要求的两条路径之一。 静态时序分析的前提就是设计者先提出要求,然后时序分析工具才会根据特定的时序模型进行分析,即有约束才会有分析。若设计者不添加时序约束,那么时序分析就无从谈起。特权同学常常碰见一些初学者在遇到问题时不问青红皂白就认为是时序问题,实际上只有在添加了时序约束后,系统的时序问题才有可能暴露出来。 下面我们再来看一个例子,我们假设有4个输入信号,经过FPGA内部一些逻辑处理后输出。FPGA内部的布线资源有快有慢之分,好比国道和高速公路。通过高速通道所需要的路径延时假设为3ns-7ns,但只有两条可用;而通过慢速通道的路径延时则>10ns。

人教版选修二第1章第1节抗生素及其合理使用教学设计 一、学习目标 1.说明抗生素在控制感染性疾病等方面所起的重要作用。 2.简述常用抗生素的作用机制。 3.列举生活中不合理使用抗生素的实例,讨论、分析滥用抗生素的危害。 4.认同应合理使用抗生素。 二、学习重点和难点 1.学习重点 生活中滥用抗生素的实例及滥用抗生素的危害。 合理使用抗生素。 2.教学难点 滥用抗生素的实例及滥用抗生素的危害。 三、学习策略 在日常生活中,抗生素的使用很普遍,因此这一节的内容比较贴近学生的现实生活。教学中尤其要突出“从社会中来,到社会中去”的教材设计思想。具体建议如下:关于抗生素在人类控制感染性疾病等方面所起的重要作用,既要讲“史话”,还要讲现实。在现实生活中,当我们发生各种炎症时,通常要使用相应的抗生素。正是抗生素帮助我们治愈了多种疾病。教学中可以从“史话”说到现实;也可以从现实说起,再回顾历史。关于抗生素的作用机制,以及日常生活中不合理使用抗生素的资料分析,一定要调动学生已有的知识经验,可以联系诸如细菌的正常结构、蛋白质的合成、内环境稳态、自然选择、食物链等相关内容,以帮助学生深入理解上述问题。关于抗生素的合理使用,可以结合上述资料分析,让学生利用教材中的讨论,从现实中存在的问题出发,得出正确的使用方法,而不应直接灌输给学生几个条目。 四、教学过程 (一)导入新课 展示给学生两个患病的宝宝,让学生讨论宝宝患病的可能原因是什么病原体感染? 学生回答:病毒、细菌或支原体、衣原体感染。给学生展示这些微生物的图片。 再提出问题:“这些微生物用肉眼是看不到的,如果你是医生你怎样诊断孩子的病因及给家长提供怎样的治疗方案?” 学生回答:通过验血,诊断是哪种病原体感染,根据病情给孩子开抗生素或抗病毒的药物,如果很严重建议静脉输液。 实际上医生一般不建议静脉输液抗生素,因为长期对宝宝的健康有影响,而且容易产生耐药菌。那么抗生素是怎么被发现的呢?最初的产量很高吗? 导入抗生素的史话 (二)教学过程 1、抗生素的史话 尽管早在1928年,英国细菌学家弗莱明就发现了青霉菌分泌的青霉素能有效地杀死细菌,但是,当时提取青霉素十分困难,人们也没有意识到青霉素的应用价值。 “亚历山大·弗莱明于1881年出生在苏格兰的洛克菲尔德。弗莱明从伦敦圣马利亚医院医科学校毕业后,从事免疫学研究。在第一次世界大战中作为一名军医,研究伤口感染,他注意到许多防腐剂对人体细胞的伤害甚于对细菌的伤害,他认识到需要某种有害于细菌而无害于人体细胞的物质。

ASIC时序约束、时序分析 2009-11-13 22:13 A 时序约束的概念和基本策略 时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移约束(IPAD到FFS、FFS到OPAD)以及静态路径约束(IPA 综合布线工具调整映射和布局布线过程,使设计达到时序要求。例如用OFFSET_IN_BEFORE约束可以告诉综合布线工具输入信号在以根据这个约束调整与IPAD相连的Logic Circuitry的综合实现过程,使结果满足FFS的建立时间要求。 附加时序约束的一般策略是先附加全局约束,然后对快速和慢速例外路径附加专门约束。附加全局约束时,首先定义设计的所有分组附加周期约束,然后对FPGA/CPLD输入输出PAD附加偏移约束、对全组合逻辑的PAD TO PAD路径附加约束。附加专门约束时速例外路径和多周期路径,以及其他特殊路径。 B 附加约束的基本作用 1. 提高设计的工作频率 对很多数字电路设计来说,提高工作频率非常重要,因为高工作频率意味着高处理能力。通过附加约束可以控制逻辑的综时,从而提高工作频率。 2. 获得正确的时序分析报告 几乎所有的FPGA设计平台都包含静态时序分析工具,利用这类工具可以获得映射或布局布线后的时序分析报告,从而对束作为判断时序是否满足设计要求的标准,因此要求设计者正确输入约束,以便静态时序分析工具输出正确的时序分析 3. 指定FPGA/CPLD引脚位置与电气标准 FPGA/CPLD的可编程特性使电路板设计加工和FPGA/CPLD设计可以同时进行,而不必等FPGA/CPLD引脚位置完全确定,从成后,设计者要根据电路板的走线对FPGA/CPLD加上引脚位置约束,使FPGA/CPLD与电路板正确连接。另外通过约束还特性。为了满足日新月异的通信发展,Xilinx新型FPGA/CPLD可以通过IO引脚约束设置支持诸如 AGP、BLVDS、CTT、G LVPECL、LVDSEXT、LVTTL、 PCI、PCIX、SSTL、ULVDS等丰富的IO接口标准。另外通过区域约束还能在FPGA上规划各个成模块化设计等。 C 周期(PERIOD)的含义 周期的含义是时序中最简单也是最重要的含义,其它很多时序概念会因为软件商不同略有差异,而周期的概念确是最通用的,周期面要讲到的其它时序约束都是建立在周期约束的基础上的,很多其它时序公式,可以用周期公式推导。周期约束是一个基本时序和具根据PERIOD约束检查时钟域内所有同步元件的时序是否满足要求。PERIOD约束会自动处理寄存器时钟端的反相问题,如果相迟将被默认限制为PERIOD约束值的一半。如下图所示, 图1 周期的定义 时钟的最小周期为: TCLK = TCKO +TLOGIC +TNET +TSETUP -TCLK_SKEW TCLK_SKEW =TCD2 -TCD1

浅谈抗生素的利与弊 要说人类医学史上最伟大的事件莫过于抗生素的发现和使用,抗生素在人类历史上挽救了无数的生命,人类寿命的增加,约有10岁得益于抗生素的广泛使用,由此可见,抗生素对人类来说是多么重要。但是,通过本节课的学习,我对抗生素有了新的认识。 抗生素(antibiotics)是由微生物(包括细菌、真菌、放线菌属)或高等动植物在生活过程中所产生的具有抗病原体或其它活性的一类次级代谢产物,能干扰其他生活细胞发育功能的化学物质。现临床常用的抗生素有微生物培养液液中提取物以及用化学方法合成或半合成的化合物。目前已知天然抗生素不下万种。 抗生素以前被称为抗菌素,事实上它不仅能杀灭细菌而且对霉菌、支原体、衣原体等其它致病微生物也有良好的抑制和杀灭作用,近年来通常将抗菌素改称为抗生素。抗生素可以是某些微生物生长繁殖过程中产生的一种物质,用于治病的抗生素除由此直接提取外;还有完全用人工合成或部分人工合成的。通俗地讲,抗生素就是用于治疗各种细菌感染或抑制致病微生物感染的药物。 凡事物都有两面性,抗生素也不例外。 从青霉素、红霉素、头孢、阿奇霉素等针对病菌耐药性而分阶段研制的新药特药相继问世,几乎都需相隔十年以上,并要花费上亿美金。而随着一款新的抗生素类药物出现,经过几年的时间,病菌又具有了新的耐药性。为此,我们曾提倡尽量少用抗生素药物,以尽可能的延长病菌耐药性期限。 细菌的耐药性已经逼得抗生素不断更新的周期越来越短,尤其是对于病情较长的复合感染更是成为临床处方的一个棘手难题。 目前针对日常使用的药品、保健品,为了达到更好的疗效,都会不同程度的含有抗生素类药物,以达到更好的杀菌抑菌作用。医院用药已经毋庸置疑,为了达到疗效,都会不同程度的含有抗生素类。目前市面上流行的各类药物牙膏、具有口腔护理功能的漱口水、杀菌抑菌清洗液等,以及人们间接食用的使用抗生素药物的肉类食品、果蔬食品等,由于长期使用,在人们期望达到杀菌抑菌保健功效的同时,也都不同程度的遗留轻微毒素和抗生素类,进而促使病菌逐渐产生耐药性,并慢慢危害人体健康。由此,很多类似产品明确标明儿童孕妇不宜使用。 抗生素可以治疗各种病原菌,疗效可靠,使用安全。但由于个体差异以及长期大剂量地使用等问题,也可引起了各种不良反应。 (1)过敏反应:由于个体差异,任何药物均可引起过敏反应,只是程度上的不同。易引起过敏反应或过敏性休克的药物主要有青霉素类、头抱菌素类、氨基糖类、四环素类、氯霉素、洁霉素。磺胺类等抗生素。 (2)肝损害:通过直接损害或过敏机制导致肝细胞损害或胆汁郁滞的药物主要有四环素、氯霉素、无味红霉素、林可霉素等。 (3)肾损害:大多数抗生素均以原形或代谢物经肾脏排泄,故肾脏最容易受其损害。主要有氨基贰类(庆大毒素等)、磺胺类、头孢菌素类(尤其是第一代)、多粘菌素B、二性霉素B等。 (4)白细胞、红细胞、血小板减少,甚至再生障碍性贫血、溶血性贫血:主要见于氯霉素、抗肿瘤抗生素(阿霉素等)、链霉素、庆大霉素、四环素、青霉素、头孢菌素等。(5)恶心、呕吐、腹胀、腹泻和便秘等消化道反应:较多见于四环素、红霉素、林可霉素、氯霉素、制霉菌素、灰黄霉素、新霉素、头孢氨苯等。 (6)神经系统损害:可表现为头痛、失眠、抑郁、耳鸣、耳聋、头晕以及多发性神经炎,甚至神经肌肉传导阻滞。多见于氨基威类抗生素,如链霉素、卡那霉素等,以及新霉素,

在进行FPGA的设计时,经常会需要在综合、实现的阶段添加约束,以便能够控制综合、实现过程,使设计满足我们需要的运行速度、引脚位置等要求。通常的做法是设计编写约束文件并导入到综合实现工具,在进行FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。 一、周期约束 周期约束是Xilinx FPGA 时序约束中最常见的约束方式。它附加在时钟网线上,时序分析工具会根据周期约束来检查时钟域内所有同步元件的时序是否满足需求。周期约束会自动的寄存器时钟端的反相。如果相邻的两个元件的时钟相位是相反的,那么它们之间的延迟将被默认的限制成周期约束的一半。 在进行周期约束之前,必须对电路的时钟周期明了,这样才不会出现约束过松或者过紧的现象。一般情况下,设计电路所能达到的最高运行频率取决于同步元件本身的Setup Time 和Hold Time,以及同步元件之间的逻辑和布线延迟。周期约束一般是使用下面的约束方法: 1、period_item PERIOD=period {HIGH|LOW} [high_or low_item] 其中,period_item可以是NET或TIMEGRP,分别代表时钟线名称net name或元件分组名称group-name。用NET表示PERIOD约束作用到名为“net name”的时钟网线所驱动的同步元件上,用TIMEGRP表示PERIOD约束作用到TIMEGRP所定义的分组(包括FFS、LATCH和RAM等同步元件)上。period是目标时钟周期,单位可以是ps、ns、μS和ms 等。HIGH|LOW指出时钟周期中的第1个脉冲是高电平还是低电平,high or low time为HIGH LOW指定的脉冲的持续时间,默认单位是ns。如果没有该参数,时钟占空比是50%。例如,NET SYS_CLK PERIOD=10 ns HIGH 4ns 2、NET“clock net name”TNM_NET=“timing group name”; TIMESPEC“TSidentifier”=PERIOD “TNM reference”period {HIGH | LOW} [high or low item]INPUT_JITTER value; 很多时候为了能够定义比较复杂的派生关系的时钟周期,就要使用该方法。其中TIMESPEC在时序约束中作为一个标识符表示本约束为时序规范;TSidentifier包括字母TS和一个标识符identifier共同作为一个TS属性;TNM reference指定了时序约束是附加在哪一个组上,一般情况下加在TNM_NET定义的分组上。HIGH | LOW 指的是时钟的初始相位表明第一个时钟是上升沿还是下降沿;high or low item 表示的是时钟占空比,即就是high或者low的时间,默认为1:1, INPUT_JITTER 表示的是时钟的抖动时间,时钟会在这个时间范围内抖动,默认单元为ps。比如周期约束: NET "ex_clk200m_p" TNM_NET = TNM_clk200_p; TIMESPEC "TS_clk200_p" = PERIOD "TNM_clk200_p" 5.000 ns HIGH 50 %; 建立一个TNM_clk200_p的时序分组,包括时钟网络ex_clk200m_p驱动的所有同步

抗生素使用5大误区 很多人在感冒、腹泻时会自己吃抗生素,觉得这样能预防感染。实际上,临床上的某些外科手术确实会提前使用抗生素预防感染,但使用的前提是符合相应的指征,例如进行了某些腔道手术,患者是糖尿病人或身体虚弱的老人等。

误区1 提前服,防感染 很多人在感冒、腹泻时会自己吃抗生素,觉得这样能预防感染。实际上,临床上的某些外科手术确实会提前使用抗生素预防感染,但使用的前提是符合相应的指征,例如进行了某些腔道手术,患者是糖尿病人或身体虚弱的老人等。 感冒多是病毒感染,造成腹泻的原因也很多,大多不需要用抗生素;即使是细菌感染引起的,也未必人人需要用。一般来说,患慢性支气管炎者和老人发生感染可能需要用。此外,已经有研究表明,事先口服抗生素并不能预防细菌感染。面积较小的皮肤切口感染不要急着用药,如果不能通过身体免疫能力康复,再遵医嘱使用,也并不晚。 误区2 用广谱,更放心

有人认为,广谱抗生素能对付的细菌种类多,杀伤范围大,效果肯定更好。实际上,这只是在寻求心理安慰。应对细菌感染如同打仗,用广谱抗生素是狂轰滥炸,用窄谱抗生素则是针对性打击。体内的细菌并不是都有害,例如我们没生病时,体内也有大肠杆菌,如果乱用广谱抗菌药,容易破坏人体内环境,造成真菌感染等二重感染。合理用窄谱抗生素,反而更有针对性,可能效果更好。 药品说明书写明能应对的细菌种类越多,抗菌谱通常越广,但也不是绝对的。为了保证我们用抗生素时能集中火力攻击,应在医生指导下用药。

误区3 越高级,越有效 不少患者觉得高级的抗生素好,一些非感染科的医生也可能在认识上存在不足。据美国《科技日报》8月2日报道,超过60%的美国医生选择最强效的抗生素,其中有些用过头了。实际上,用抗生素不像买车,只有“更有效”的,没有“更高级”的。所谓“高级”抗生素,是对抗生素的新旧、价格而言,并非对某种感染更有效。例如老牌药红霉素,价格便宜,对于支原体感染引起的肺炎具有相当好的疗效,而相对较新、价格较高的三代头孢菌素对付这类病就不如红霉素。盲目用“更高级”的抗生素,不仅易引起耐药,还可能在今后出现较严重的细菌感染时无药可用。 误区4 先输液,见效快

XILINX时序约束使用指南笔记 第一章 时序约束介绍 第二章 时序约束方法 第三章 时序约束原则 第四章 在XST中指定时序约束 第五章 在Synplify中指定时序约束方法 第六章 时序约束分析

第一章 时序约束介绍 基本的时序约束包括: “PERIOD Constraints” “OFFSET Constraints” “FROM:TO(Multi‐Cycle)约束”

第二章 时序约束方法 1,简介: 2,基本的约束方法 根据覆盖的路径不同,时序要求变成一些不同的全局约束。 最普通的路径类型包括: 1,输入路径 2,同步元件到同步元件路径 3,指定路径 4,输出路径 XILINX的时序约束与每一种全局约束类型都有关。最有效的方法就是一开始就指定全局约束然后再加上指定路径的约束。在很多案例中,只要全局约束就可满足需求。 FPGA器件执行工具都是由指定的时序要求驱动的。如果时序约束过头的话,就会导致内存使用增加,工具运行时间增加。更重要的是,过约束还会导致性能下降。因此,推荐使用实际设计要求的约束值。 3,输入时序约束 输入时序约束包括2种 “系统同步输入” “源同步输入” 输入时钟约束覆盖了输入数据的FPGA外部引脚到获取此数据的寄存器之间的路径。输入时钟约束经常用”OFFSET IN”约束。指定输入时钟要求的最好方法,取决于接口的类型(源/系统同步)和接口是SDR还是DDR。 OFFSET IN定义了数据和在FPGA引脚抓取此数据的时钟沿之间的关系。在分析OFFSET IN 约束时,时序分析工具自动将影响时钟和数据延迟的因素考虑进去。这些因素包括: 时钟的频率和相位转换 时钟的不确定 数据延迟调整 除了自动调整,还可以在与接口时钟相关的”PERIOD”约束中另外增加时钟不确定。 关于增加”INPUT_JITTER”的更多信息,参见第三章的”PERIOD Constraints”。 “OFFSET IN”与单输入时钟有关,默认情况下,OFFSET IN约束覆盖了从输入pad到内部同步元件之间的所有路径。用于抓取那些从pad输入的数据的同步元件由指定的OFFSET IN 时钟触发。应用OFFSET IN约束被称为”global”方法。这是指定输入时序的最有效的方法。 系统同步输入 在体统同步接口中,发送和抓取数据共用一个系统时钟。板上的布线延迟和时钟倾斜限制了接口的工作频率。更低的频率也会导致系统同步输入接口典型的采用SDR应用。 系统同步SDR应用例子,见图2‐1。系统同步SDR应用中,在时钟上升沿从源器件发送

说明文《抗生素》阅读答案 说明文《抗生素》阅读答案 抗生素是现在家庭的常备药,但是人们在使用抗生素方面还存在许多误区。有的人认为抗生素越贵越好,有的人感冒时用抗生素来抗病毒,有的人用青霉素来预防胆囊炎,有的人同时服用几种抗生素类药物。这些认识都不正确。 抗生素药物是最常见的抗菌药物。抗菌药物的不合理使用,会增加药品不良反应和药源性疾病的发生。乱用抗生素所带来的最大不良反应是加速体内耐药菌的增长,结果将导致“抗药性”的出现。 抗生素类药物都必须按照医生处方服用,千万不要随意改变服药时间,因为服药间隔太近,会造成药物在血液中浓度过高,从而引起肠胃不适;间隔太久,则药物对细菌的抵抗力会减弱。在细菌感染后,尚未就医以前.宁可不服药也不要擅自吃抗生素。 12.根据文意,为什么抗生素类药物不能治感冒? 答:。 13.文中“抗药性”的含义是什么 答: 14.为什么“在细菌感染后,尚未就医以前,宁可不服药也不要擅自吃抗生素”? 答: 15.请拟一个能概括上文中心的标题。 答:

参考答案: 12.因为抗生素类药物是抗菌药物,不能抗感冒病毒。或抗生素对付的是细菌而不是病毒感染,而感冒属于病毒感染。 13.抗生素类药物使用不当,加速体内耐药菌的增长,使此类药物在人体内不能正常发挥效力。 14.答案要点:①因为不具备足够的医学知识,就不能科学使用抗生素; ②会增加药物不良反应和药源性疾病发生。 15.参考答案:①不可随便使用抗生素。

20XX—019学年度第一学期生物教研组工作计划 指导思想 以新一轮课程改革为抓手,更新教育理念,积极推进教学改革。努力实现教学创新,改革教学和学习方式,提高课堂教学效益,促进学校的内涵性发展。同时,以新课程理念为指导,在全面实施新课程过程中,加大教研、教改力度,深化教学方法和学习方式的研究。正确处理改革与发展、创新与质量的关系,积极探索符合新课程理念的生物教学自如化教学方法和自主化学习方式。 主要工作 一、教研组建设方面: 、深入学习课改理论,积极实施课改实践。 、以七年级新教材为“切入点”,强化理论学习和教学实践。 、充分发挥教研组的作用,把先进理念学习和教学实践有机的结合起来,做到以学促研,以研促教,真正实现教学质量的全面提升。 、强化教学过程管理,转变学生的学习方式,提高课堂效益,规范教学常规管理,抓好“五关”。 ()备课关。要求教龄五年以下的教师备详案,提倡其他教师备详案。要求教师的教案能体现课改理念。 ()上课关。 ()作业关。首先要控制学生作业的量,本着切实减轻学生负担的精神,要在作业批改上狠下工夫。 ()考试关。以确保给学生一个公正、公平的评价环境。 ()质量关。 、加强教研组凝聚力,培养组内老师的团结合作精神,做好新教师带教工作。 二、常规教学方面: 加强教研组建设。兴教研之风,树教研氛围。特别要把起始年级新教材的教研活动作为工作的重点。 、教研组要加强集体备课共同分析教材研究教法探讨疑难问题由备课组长牵头每周集体备课一次,定时间定内容,对下一阶段教学做到有的放矢,把握重点突破难点 、教研组活动要有计划、有措施、有内容,在实效上下工夫,要认真落实好组内的公开课教学。 、积极开展听评课活动,每位教师听课不少于20节,青年教师不少于节,兴“听课,评课”之风,大力提倡组内,校内听随堂课。 、进一步制作、完善教研组主页,加强与兄弟学校的交流。 我们将继续本着团结一致,勤沟通,勤研究,重探索,重实效的原则,在总结上一学年经验教训的前提下,出色地完成各项任务。 校内公开课活动计划表 日期周次星期节次开课人员拟开课内容 10月127四王志忠生物圈 10月137五赵夕珍动物的行为 12月114五赵夕珍生态系统的调节 12月2818四朱光祥动物的生殖 镇江新区大港中学生物教研组 xx- 20X下学期生物教研组工作计划范文 20X年秋季生物教研组工作计划 化学生物教研组的工作计划 生物教研组工作计划 下学期生物教研组工作计划 年下学期生物教研组工作计划 20X年化学生物教研组计划 20X年化学生物教研组计划 中学生物教研组工作计划 第一学期生物教研组工作计划 20XX—019学年度第二学期高中英语教研组工作计划 XX—XX学年度第二学期高中英语教研组工作计划 一.指导思想: 本学期,我组将进一步确立以人为本的教育教学理论,把课程改革作为教学研究的中心工作,深入学习和研究新课程标准,积极、稳妥地实施和推进中学英语课程改革。以新课程理念指导教研工作,加强课程改革,紧紧地围绕新课程实施过程出现的问题,寻求解决问题的方法和途径。加强课题研究,积极支持和开展校本研究,提高教研质量,提升教师的研究水平和研究能力。加强教学常规建设和师资队伍建设,进一步提升我校英语教师的英语教研、教学水平和教学质量,为我校争创“三星”级高中而发挥我组的力量。 二.主要工作及活动: .加强理论学习,推进新课程改革。 组织本组教师学习《普通高中英语课程标准》及课标解度,积极实践高中英语牛津教材,组织全组教师进一步学习、熟悉新教材的体系和特点,探索新教材的教学模式,组织好新教材的研究课活动,为全组教师提供交流、学习的平台和机会。 .加强课堂教学常规,提高课堂教学效率。 强化落实教学常规和“礼嘉中学课堂教学十项要求”。做好集体备课和二备以及反思工作。在认真钻研教材的基础上,抓好上课、课后作业、辅导、评价等环节,从而有效地提高课堂教学效率。加强教学方法、手段和策略的研究,引导教师改进教学方法的同时,引导学生改进学习方法和学习策略。 .加强课题研究,提升教科研研究水平;加强师资队伍建设,提升教师的教学能力。 组织教师有效开展本组的和全校的课题研究工作做到有计划、有研究、有活动、有总结,并在此基础上撰写教育教学论文,并向报刊杂志和年会投稿。 制订好本组本学期的校公开课、示范课、汇报课计划,并组织好听课、评课等工作。 三.具体安排: 二月份:制订好教研组工作计划、课题组工作计划和本学期公开课名单。 三月份:、组织理论学习。 、高一英语教学研讨活动。 、组织好高三第一次模考、阅卷、评卷和总结等工作。 四月份:、组织好高三英语口语测试。 、高三英语复习研讨会。 五月份:、组织好高三第二次模考、阅卷、评卷和总结等工作。 、协助开展好我校的区级公开课。 六月份:、组织好高考的复习迎考工作。 、收集课题活动材料。 2019学年春季学期小学语文组教研计划 一、指导思想 坚持以《基础教育课程改革纲要》为指导,认真学习贯彻课程改革精神,以贯彻实施基础教育课程改革为核心,以研究课堂教学为重点,以促进教师队伍建设为根本,以提高教学质量为目标,全面实施素质教育。 本学期教研组重点加强对教师评课的指导,使教师的评课规范化,系统化,定期举行主题教学沙龙和“会诊式行动研究”,促进新教师的成长,加快我镇小学语文教师队伍成长速度和小学语文教育质量的全面提高。结合区里的活动安排,开展各项有意义的学生活动,培养提高学生的语文素养,调动启发学生的内在学习动机。 二、工作目标 、以课改为中心,组织教师学习语文课程标准,转变教学观念,深入课堂教学研究,激发学生主动探究意识,培养学生创新精神和实践能力,努力提高学生语文素养。 、进一步加强语文教师队伍建设,让“语文研究小组”,充分发挥学科带头人、骨干教师的示范作用,重视团队合作智慧、力量。开展“师徒结对”活动,以老带新,不断提高教师的业务素质。 、组织教师开展切实有效的说课沙龙、评课沙龙,提高教师说课能力,和评课能力,能够结合主题教研活动,对典型课例进行互动研讨,开展教例赏析活动。 、加强教研组集体备课,每周以段为单位组织一次集体备课,分析教材,赏析重点课文,进行文本细读,交流教学心得。让备课不再是走场,形式主义,而是真真实实为提高课堂效率服务,提高教师的素质服务。 、根据上学期制定的语文常规活动计划,开展形式多样的学习竞赛活动、过关活动,激发学生学习语文的兴趣,在自主活动中提高学生的综合实践能力,促进个性和谐发展。 、加强学习质量调查、检测工作,及时分析,寻找得失,确保完成各项教学指标。 三、主要工作及具体措施 (一)骨干教师示范、把关,当好“领头羊”。 、本学期,语文研究小组成员继续充分发挥学科带头人、骨干教师的示范作用,重视团队合作智慧、力量。教研组将围绕“探索实效性语文课堂教学模式”这个主题,深入开展精读课文教学有效性研讨活动。低段(1-2年级)则继续进行识字教学的有效性的探讨。分层、有序地开展教研活动,使教研活动更成熟、有效,切实提高我校语文老师的专业水平。 、开展“师徒结对”活动,以老带新,不断提高教师的业务素质。 (二)年轻教师取经、学习,争取出成绩。 、为了提高教学质量,促成新教师迅速成长,—年教龄新教师每一学期上堂模仿课和一堂校内研讨课。上模仿课的内容可以通过观看名师的关盘、视频或者教学实录等途径,根据个人教学需要,有选择性地进行局部模仿,从而使新教师形成个人的教学风格。 2019年高二历史第二学期教学工作计划范文1 一、指导思想 高二的历史教学任务是要使学生在历史知识、历史学科能力和思想品德、情感、态度、价值观各方面得到全面培养锻炼和发展,为高三年级的文科历史教学打下良好的基础,为高校输送有学习潜能和发展前途的合格高中毕业生打下良好基础。 高考的文科综合能力测试更加强调考生对文科各学科整体知识的把握、综合分析问题的思维能力、为解决问题而迁移知识运用知识的能力。教师在教学中要体现多学科、多层次、多角度分析解决问题的通识教育理念。教师要认真学习和研究教材转变教学观念,紧跟高考形势的发展,研究考试的变化,力争使高二的教学向高三教学的要求靠拢。 按照《教学大纲》和《考试说明》的要求,认真完成高二阶段的单科复习工作。坚持学科教学为主,落实基础知识要到位,适当兼顾史地政三个学科的综合要求,培养提高学生学科内综合的能力。从学生的实际出发,落实基础,提高学科思维能力和辩证唯物主义、历史唯物主义的理论水平。 二、教学依据和教材使用 全班共40人,其中男生15人,女生人。学生的数学基础较一般,多数学生能掌握所学内容,少部分学生由于反映要慢一些,学习方法死板,没有人进行辅导,加之缺乏学习的主动性,不能掌握学习的内容。能跟上课的学生,课上活泼,发言积极,上课专心听讲,完成作业认真,学习比较积极主动,课后也很自觉,当然与家长的监督分不开。部分学生解答问题的能力较强,不管遇到什么题,只要读了两次,就能找到方法,有的方法还相当的简捷。有的学生只能接受老师教给的方法,稍有一点变动的问题就处理不了。个别学生是老师怎么教也不会。 二、教材分析 本册的教学内容:()混合运算和应用题;()整数和整数四则运算;()量的计量;()小数的意义和性质;()小数的加法和减法;()平行四边形和梯形 本册的重点:混合运算和应用题是本册的一个重点,这一册进一步学习三步式题的混合运算顺序,学习使用小括号,继续学习解答两步应用题的学习,进一步学习解答比较容易的三步应用题,使学生进一步理解和掌握复杂的数量关系,提高学生运用所学知识解决得意的实际问题的能力,并继续培养学生检验应用题的解答的技巧和习惯。第二单元整数和整数的四则运算,是在前三年半所学的有关内容的基础上,进行复习、概括,整理和提高。先把整数的认数范围扩展到千亿位,总结十进制计数法,然后对整数四则运算的意义,运算定律加以概括总结,这样就为学习小数,分数打下较好的基础。第四单元量的计量是在前面已学的基础上把所学的计量单位加于系统整理,一方面使学生所学的知识更加巩固,一方面使学生为学习把单名数或复名数改写成用小数表示的单名数做好准备。 三、教学目标 (一)知识与技能: 、使学生认识自然数和整数,掌握十进制计数法,会根据数级正确地读、写含有三级的多位数。 、使学生理解整数四则运算的意义,掌握加法与减法、乘法与除法之间的关系。 ③提出教学任务:在全面发展体能的基础上,进一步发展灵敏、力量,速度和有氧耐力,武德的培养;引导学生学会合理掌握练习与讨论的时间,了解实现目标时可能遇到的困难。在不断体验进步和成功的过程中,表现出适宜的自信心,形成勇于克服困难积极向上,乐观开朗的优良品质;认识现代社会所必需的合作和竞争意识,在武术学习过程中学会尊重和关心他人,将自身健康与社会需要相,表现出良好的体育道德品质,结合本身项目去了解一些武术名人并能对他们进行简单的评价;加强研究性的学习,去讨论与研究技能的实用性,加强同学之间的讨论交流的环节。 ()教学目标: ①总体目标:建立“健康第一”的理念,培养学生的健康意识和体魄,在必修田径教学的基础上进一步激发学生学习“初级长拳”、“剑”的兴趣,培养学生的终身体育意识,以学生身心健康发展为中心,重视学生主体地位的同时关注学生的个体差异与不同需求,确保每一个学生都受益,以及多样性和选择性的教学理念,结合学校的实际情况,设计本教学工作计划,以满足学生选项学生的需求,加深学生的运动体验和理解,保证学生在高一年田径必修基础上再加上“长拳”来引导男女生学习体育模块的积极性,再结合高二年的“剑”选项课的学习中修满学分。加强学习“长拳”以及“剑”的基本套路,提升学习的的兴趣,提升学生本身的素质,特别是武德的培养。 ②具体目标: 运动参与:养成良好的练武的锻炼习惯。根据科学锻炼的原则,制定并实施个人锻炼计划。学会评价体育锻炼效果的主要方法。 运动技能:认识武术运动项目的价值,并关注国内外重大体赛事。有目的的提高技术战术水平,并进一步加强技、战术的运用能力。学习并掌握社会条件下活动的技能与方法,并掌握运动创伤时和紧急情况下的简易处理方法。 身体健康:能通过多种途径发展肌肉力量和耐力。了解一些疾病等有关知识,并理解身体健康在学习、生活中和重要意义。形成良好的生活方式与健康行为。 心理健康:自觉通过体育活动改变心理状态,并努力获得成功感。在武术练习活动中表现出调节情绪的意愿与行为。在具有实用技能练习中体验到战胜困难带来喜悦。 社会适应:在学习活动中表现出良好的体育道德与合作创新精神。具有通过各种途径获取体育与健康方面知识和方法的能力。 ()教学措施: 采用教师示范与讲解,学生讨论,练习,教师评价,再进行个别指导,后进行学生练习,最后进行展示与学生的综合评价相结合的方式方法,培养学生的良好的学习习惯、学习方法更好地完成教学任务,达到教学目标;实行培优扶中辅差,,采用学习小组的建立,加强学习小组的相互学习、相互讨论、相互研究的功能,提升学习的效率;加强多边学科的整合,特别是加强心理健康的教育,加强运动力学、运动医学等进行学习,以提升学生的运动自我保护意识与能力。 二、教学研究的计划 ()课题研究:加强校本课程“剑”、“平山初级长拳”的开发与教学;做好“趣味奥运会进入校园”课题的开题准备。做为“青春期健康教育进入校园”课题组的成员,协助课题组进行研究,开展活动。 ()校本教研:加强校本课程的开发,加强体育备课组的教研能力,做为备课组长的我与其他老师加强讨论校本的研究与开发,本次校本开发重点放在“剑”、“初级长拳”、“花样篮球”三个项目上,有所侧重。 ()论文撰写:结合课题研究的内容进行撰写。 ()校际、教研组、备课组教研活动:做为晋江市兼职中学体育教研员及校际组成员,积极参加校际组开展的各项活动,加强提升在校际组的教研水平,做好兼职教研员的本职工作,协助教研员开展教研活动;积极参加教研组的各项活动,提升教研水平;做为备课组长的我,我计划是积极组织本组老师一起提高高中的课改力度与水平,集中老师的备课时间与讨论在备课过程中出现的一系列问题,针对选项会出现的问题进行沟通,加强学习过程的评价,协调选项内容的评价标准及认证过程。 高二下学期语文备课组工作计划 高二下学期化学教学计划 高二下学期语文教学工作计划 关于高二下学期班主任工作计划范文 20X学年高二下学期班主任工作计划范文 20X高二下学期班主任工作计划 高二下学期工作计划范文 20X年高二下学期地理教学计划 高二下学期物理教学计划 高二下学期语文教学计划 生积极性,要求作业在课堂上完成,并及时反馈。 4. 做好后进生的辅导工作,实施“课内补课”的方法,组织互帮互学。 5.培养学生的分析、比较和综合能力。 6. 培养学生的抽象、概括能力。 7. 培养学生的迁移类推能力。 8. 培养学生思维的灵活性。 五、课时安排 四年级下学期数学教学安排了课时的教学内容。各部分教学内容教学课时大致安排 一、混合运算和应用题(11课时) 、混合运算课时 、两、三步计算的应用题课时 、整理和复习课时 二、整数和整数四则运算(18课时) 、十进制计数法课时 、加法的意义和运算定律课时 、减法的意义和运算定律课时 、乘法的意义和运算定律课时 、除法的意义课时 、整理和复习课时 三、量的计量(课时) 、常用的计量单位课时 、名数的改写课时 四、小数的意义和性质(17课时) 、小数的意义和读写法课时 、小数的性质和小数的大小比较课时 、小数点位置移动引起小数大小的变化课时 、小数和复名数课时 、求一个小数的近似数 2课时 、整理和复习课时 五、小数的加法和减法(课时) 小管家课时 六、三角形、平行四边形和梯形(10课时) 、角的度量课时 、垂直和平行课时 、三角形课时 、平行四边形和梯形课时 、整理和复习课时 七、总复习(课时) XX年月26日 向纵深发展。 、做好论文的撰写、参评工作。 活动安排: 二月份:课例展示交流。王钧、李汪俊、罗建上研究课;课题成员进行子课题研究交流。 三月份:课例展示交流。(姚爱祥)组织课题学习,程中华、戴辉文、孙小娟上研究课;课题成员进行子课题研究交流。 四月份:课例展示交流。(姚爱祥)组织课题学习,刘华波、曹辉、钱芸上研究课;课题成员进行子课题研究交流。 五月份:课题研究小结 、组织年轻教师开展会诊式课堂教学诊断活动、同课异构活动、同构异教活动,有效,切实提高我校年轻语文老师的专业水平,获得快速成长。 、选拔教龄——年新教师参加区教研室组织的区新生代课堂教学比赛,并做好指导、培训工作。 (三)教研形式稳中有变,踏实而生动。 、继续组织两周一次的专题学习沙龙和互动式评课沙龙,结合教研活动的主题组织好教师学习、交流。听展示课的教师对听课内容进行精心、系统的评点,写成评课稿,在两周一次的互动式教学研讨沙龙中进行交流、探讨。与往年不同的是,在保证互动评课活动开展同时,不影响正常教学,本学期安排次集体评课活动,其他评课通过qq群来交流、研讨。

用Quartus II Timequest Timing Analyzer进行时序分析:实例讲解 (一) (2012-06-21 10:25:54) 转载▼ 标签: 杂谈 一,概述 用Altera的话来讲,timequest timing analyzer是一个功能强大的,ASIC-style的时序分析工具。采用工业标准--SDC(synopsys design contraints)--的约束、分析和报告方法来验证你的设计是否满足时序设计的要求。在用户的角度,从我使用TimeQuest的经验看,它与IC设计中经常用到的比如prime time,time craft等STA软件是比较类似的。用过prime time或time craft的朋友是非常容易上手的。 在这一系列的文章里,我将会拿一个DAC7512控制器的verilog设计作为例子,详细讲解如何使用TimeQuest进行时序设计和分析。 二,TimeQuest的基本操作流程 做为altera FPGA开发流程中的一个组成部分,TimeQuest执行从验证约束到时序仿真的所有工作。Altera推荐使用下面的流程来完成TimeQuest 的操作。

1. 建立项目并加入相关设计文件 不管做什么事情,都需要有一个目标或者说对象。我们用TimeQuest 做时序分析,当然也需要一个对象,这个对象实际上就是我们的设计。所以首先是要建立一个Quartus II的项目,并把所有需要的设计文件都加入到项目中去。需要注意的一点是,这里的设计文件,不仅仅包含逻辑设计相关的文件,也包含已经存在的时序约束文件,当然,需要以synopsys Design Constraints(.sdc)的格式存在的。 2. 对项目进行预编译(initial compilation) 项目建立以后,如果从来没有对项目进行过编译的话,就需要对项目进行预编译。这里的预编译是对应于全编译(full compilation)来讲的,我们可以理解为预编译是对项目进行部分的编译,而全编译是对项目进行完整的编译。做预编译的目的是为了生成一个initial design database,

成语辨析与使用的七大误区 成语辨析与使用是行测考试中言语理解与表达部分的经典题型,由于成语数量多而且日常生活中不常用,因此容易造成考生失分和弃分。如果掌握了一定的方法技巧,成语题完全是可以战胜的。对于成语辨析类题目,我们首先要明确公务员考试中所考查的都是我们常用的成语,不会是生僻的成语。而考查内容则有两大类型:一类是我们常用的成语中意义相近,容易混淆的;另一类是我们常用成语中容易误用的。对于成语,应试者可以从两个方面把握,一是正确理解常用常考成语的含义,不要只看字面意思;二是在恰当的语境中正确使用成语。要想准确地掌握成语的用法,华图教育提醒各位考生,主要应克服以下几种误区。 误区一:望文生义,主观臆断 有的成语的含义并不在字面上,而是与其字面意义相左、相反或无关,使用时一定要仔细分析、甄别其内涵,考查其与所在语境是否协调。如果对成语意义不仔细辨析,粗枝大叶,一瞥而过,就极易造成望文生义的错误。例如: (1)虽然交通事故的发生率已经每况愈下,但我们仍然不能有丝毫大意。 (2)他们差强人意的服务质量,不仅给社区居民的生活带来不便,而且有损职能部门在公众中的形象。 辨析:(1)句中,“每况愈下”是指情况愈来愈坏,显然与题意不符。(2) 句中,“差强人意”是指大体上让人满意,而并非字面含义:不太让人满意。 误区二:对象错误,张冠李戴 有些成语有特定的使用对象,如果把握不准,就极易扩大使用的范围或误作他用。例如: (1)近十年来,我国的城市“夜景观”建设琳琅满目,发展十分迅速。 (2)在学校举行的元旦文艺晚会上,我们班女生自编自演了个话剧,两位同学将剧中人物演得绘声绘色,博得了观众的热烈掌声。 辨析:(1)句中,“琳琅满目”一般是比喻各种美好的东西很多(多指书籍或工艺品),这里用在“城市‘夜景观’”上不合适。(2)句中,“绘声绘色”用来形容描写叙述生动逼真,用于形容“演出”显然不妥。 误区三:褒贬颠倒,感情失当 有的成语意思相近,然而感情色彩却截然不同,这时就需要根据语境加以区别,不可褒贬颠倒,以至于不能确切地表达出意思和感情。例如: 当中国女排捧回冠军奖杯的时候,举国弹冠相庆,无不佩服陈忠和教练的坚韧和勇气。

第1章FPGA中IO口时序分析 作者:屋檐下的龙卷风 博客地址:https://www.doczj.com/doc/b39235342.html,/linjie-swust/ 日期:2012.3.1 1.1 概述 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。 1.2 FPGA整体概念 由于IO口时序约束分析是针对于电路板整个系统进行时序分析,所以FPGA需要作为一个整体分析,其中包括FPGA的建立时间、保持时间以及传输延时。传统的建立时间、保持时间以及传输延时都是针对寄存器形式的分析。但是针对整个系统FPGA的建立时间保持时间可以简化。 图1.1 FPGA整体时序图 如图1.1所示,为分解的FPGA内部寄存器的性能参数: (1) Tdin为从FPGA的IO口到FPGA内部寄存器输入端的延时; (2) Tclk为从FPGA的IO口到FPGA内部寄存器时钟端的延时; (3) Tus/Th为FPGA内部寄存器的建立时间和保持时间; (4) Tco为FPGA内部寄存器传输时间; (5) Tout为从FPGA寄存器输出到IO口输出的延时; 对于整个FPGA系统分析,可以重新定义这些参数:FPGA建立时间可以定义为:(1) FPGA建立时间:FTsu = Tdin + Tsu – Tclk; (2) FPGA保持时间:FTh = Th + Tclk; (3) FPGA数据传输时间:FTco = Tclk + Tco + Tout; 由上分析当FPGA成为一个系统后即可进行IO时序分析了。FPGA模型变为如图1.2所示。