ARM7数据手册https://www.doczj.com/doc/b15741820.html,

翻译:aufan

序言:

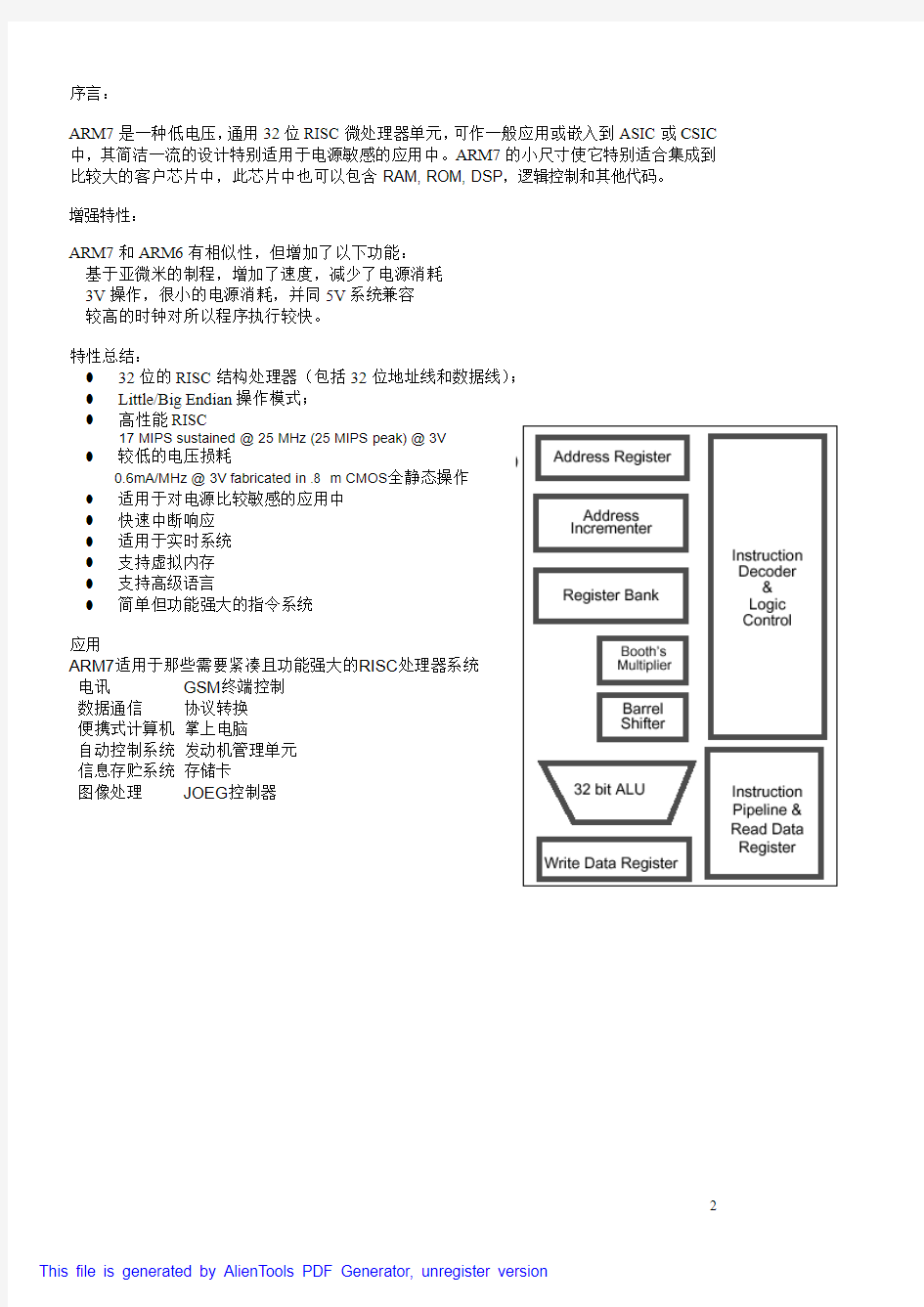

ARM7是一种低电压,通用32位RISC微处理器单元,可作一般应用或嵌入到ASIC或CSIC 中,其简洁一流的设计特别适用于电源敏感的应用中。ARM7的小尺寸使它特别适合集成到比较大的客户芯片中,此芯片中也可以包含RAM,ROM,DSP,逻辑控制和其他代码。

增强特性:

ARM7和ARM6有相似性,但增加了以下功能:

基于亚微米的制程,增加了速度,减少了电源消耗

3V操作,很小的电源消耗,并同5V系统兼容

较高的时钟对所以程序执行较快。

特性总结:

l32位的RISC结构处理器(包括32位地址线和数据线);

l Little/Big Endian操作模式;

l高性能RISC

17MIPS sustained@25MHz(25MIPS peak)@3V

l较低的电压损耗

0.6mA/MHz@3V fabricated in.8 m CMOS全静态操作

l适用于对电源比较敏感的应用中

l快速中断响应

l适用于实时系统

l支持虚拟内存

l支持高级语言

l简单但功能强大的指令系统

应用

ARM7适用于那些需要紧凑且功能强大的RISC处理器系统

电讯GSM终端控制

数据通信协议转换

便携式计算机掌上电脑

自动控制系统发动机管理单元

信息存贮系统存储卡

图像处理JOEG控制器

目录

1.0简介

1.1ARM7模块图

1.2ARM7功能图

2.0信号描述

3.0编程模式

3.1硬件配置信号

3.2操作模式选择

3.3寄存器

3.4异常

3.5复位信号

4.0指令系统

4.1指令系统总述

4.2条件代码

4.3分支和分支连接指令

4.4数据处理指令

4.5PSR传输指令(MRS,MSR)

4.6乘法和乘加指令(MUL,MLA)

4.7单次数据传输(LDR,STR)

4.8数据块传输(LDM,STM)

4.9单次数据交换(SWP)

4.10软件中断

4.11协处理器数据操作(CDP)

4.12协处理器数据传输(LDC,STC)

4.13协处理器寄存器传输(MRC,MCR)

4.14无定义指令

4.15举例

5.0存储器界面

5.1周期类型

5.2字节寻址

5.3地址时序

5.4存储器管理

5.5锁操作

5.6延续访问时间

6.0微处理器接口

6.1接口信号

6.2数据传输周期

6.3寄存器传输周期

6.4特权指令

6.5幂次访

6.6无定义指令

7.0指令周期操作

7.1分支和分支连接

7.2数据操作

7.3乘法和乘加

7.4加载寄存器

7.5存储寄存器

7.6加载乘数寄存器

7.7存储乘数寄存器

7.8数据交换

7.9软件中断和故障入口

7.10协处理器数据操作

7.11协处理器数据传输(从存储器到协处理器)

7.12协处理器数据传输(从协处理器到存储器)

7.13协处理器寄存器传输(从协处理器加载)

7.14协处理器寄存器传输(存储到协处理器)

7.15无定义指令和协处理器空缺

7.16不可执行的指令

7.17指令速度总结

8.0DC参数

8.1Absolute Maximum Ratings

8.2DC操作条件

9.0AC参数

9.1AC参数注释

19.0附录—向下兼容性

1.0简介

ARM7是32位通用微处理器ARM(Advanced RISC Machines)家族中的一员,具有比较低的电源消耗和良好的性价比,基于(精简指令)RISC结构,指令集和相关的译码机制与微程序控制的复杂指令系统的计算机相比要相对简单,这使得它拥有比较高的指令处理能力和实时中断响应能力。

指令集包含11种基本类型:

两种类型用于偏上算术逻辑单元,桶式移位器和乘法器,在31个寄存器(32位)间执行高速操作;

三种类型的指令控制数据在存储器和寄存器之间传送,一种用于弹性地址,一种用于高速内容切换,一种用于交换数据;

三种类型的指令用于控制流程和特权级执行;

三种专门用于控制外部的协处理器,此种协处理器允许指令集的功能以开放和统一的格式扩展到片外。

ARM指令集对不同高级语言的编译器来讲都比较适用,需要临界的代码段,汇编语言的编程也很简单,不像其它的微处理器,需要依靠复杂的编译器来管理指令。

由于应用了流水线技术,所以指令处理和存储系统的各个部分都可以连续运行。典型的例子,一条指令正在执行,下一条指令正被译码,第三条指令同时从存储器中取出。

在存储系统中,存储接口的设计可以最大限度地发挥性能潜力而不需要花费很大的代价,速度敏感信号做成流水线方式,允许系统控制功能应用于标准的低电压逻辑,这些控制信号推动了由工业DRAM提供的快速局部访问模式。

ARM7有32位的地址总线,所有的ARM处理器共享同一个指令集,ARM7可以配制成26位地址线,向下兼容其它早期的处理器。

ARM7是全静态CMOS,允许时钟在周期的任意部分被停止,但不丢失状态。

注意:

0x--十六进制

BOLD--外部信号用黑体字显示

2.0信号描述

NAME TYPE DESCRIPTION

A[31:0]O处理器的地址总线,如果ALE(地址所存使能)为高,在要寻址的前一

个周期的Phase2地址有效并保持至寻址周期的Phase1,保持时间由

ALE控制。

ABORT I存储器异常。这是一个输入信号,存储器系统发出此信号告诉处理器

请求的访问不被允许。

ALE I地址锁存使能,用来控制地址输出锁存,通常地址在周期的Phase2

变成下一个周期需要的值,但是对ROM的直接接口来讲,地址需要

保持稳定至Phase2结束,所以ALE需要保持低电平至Phase2。此信

号对以下的信号有相同的影响,nB W,nR W,LOC K,Nopc和

nTRAN S。如果一个系统不需要地址线以这种方式工作,ALE必须拉

高,地址锁存是静态的,所以ALE必须保持长时间低电平,以锁存地

址。

BIGEND I Big Endian配置。为高电平时,处理器认为存储器中数据为Big

Endian模式,为低电平时,认为存储器中数据为Little Endian模式。

那些不可以选择Endianism的处理器(ARM2As,ARM3,ARM61)为

Little Endian模式。

CPA I协处理器Absent。可以处理ARM7请求的协处理器(通过nCP I))必

须立即将CPA置为低电平。如果在nCP I为低电平的周期的Phase1结束

时,CPA仍为高电平,ARM7将中止与协处理器握手,启动无定义指

令陷阱。如果CPA为低电平,并且继续保持,ARM7将等待,直到CPB

为低电平,然后完成协处理器指令。

CPB协处理器忙。可以处理ARM7请求的协处理器(通过Ncp i),但不能

立即开始响应,应该通过将CPB置高表明此情况。当协处理器准备好

时,置CPB为低电平。当nCPI为低电平时,ARM7在每个周期的Phase1

结尾采样CPB。

DATA[31:0]I数据输入总线。在读周期(nRW=0),此数据输入线必须保证在传

输周期的Phase2结尾之前保持有效。

DATA32I32位数据配置。当此信号为高时,处理器可以访问32位地址空间

(A[31:0])的数据,当此信号为低时,处理器可以访问26位地址空间

(A[25:0])的数据。在后一种配置中,地址线A[31:26]没有用到。在改

变此信号电平之前,要确保处理器在下一个周期不会访问到大于

0X3FFFFFF的空间。

DBE I数据总线使能。当DBE为低电平时,写数据BUFFER被禁止。当DBE

为高电平时,写数据BUFFER在下一个真正的写周期时可以被使能,

DBE促进了数据总线共享(DMA或其它)。

DOUT[31:0]O数据输出总线,在写周期(when nRW=1)的Phase1数据有效,并保持

至传输周期的Phase2结束。

LOCK O Lock操作。当LOCK为高时,处理器执行一个Locked的MEM访

问,MEM控制器必须等到LOCK为低时,才允许其它设备访问MEM。

当MCLK为高电平时,LOCK信号改变,并在被锁的MEM访问周期

一直保持高电平。只有执行数据交换指令(SWP)时,才被激活。此信

号的时序可以通过ALE改变,就像ALE改变地址一样。驱动ABE为低

电平,LOCK为高阻态。

MCLK I MEM时钟输入。此信号定时ARM7所有MEM访问和内部操作。此信

号有两个不同的相位。Phase1:MCLK为低,Phase2:MCLK(和

Nwait)为高。此信号可以在任何一相被任意延伸,用于访问比较慢

的外设或MEM。与此相似,Nwait输入也可以和一个正常运行的

MCLK相与取得相同的效果。

nBW O字节或者字使能。处理器输出此信号告诉外部MEM系统,当前数据

传输为字节长度。在读或者写周期,高电平表示字传输,低点平表

示字节传输。此信号在数据传输的前一个周期的Phase2有效,并在

本次数据传输周期的整个Phase1有效。此信号的时序像地址线一样

可以通过ALE信号来改变。当ABE信号位低时,此信号为高阻态。nCPI O协处理器指令。当ARM7执行一条协处理指令,此信号将被置为低

电平,并等待协处理器响应。ARM7将依据协处理器的CPA和CPB

的不同状态,做出相应的反应。

nENOUT O数据输出使能。处理器通过此信号表明写周期正在发生,

DOUT[31:0]被送到外部的MEM系统。如果系统需要双向数据总线,

此信号可以使能三态Buffer,DOUT[31:0]通过三态Buffer送至

DATA[31:0]

nENIN I输入使能。在写周期,此信号和nENOUT一起控制数据总线。请参

考第五章:MEM接口。

nFIQ I快速中断请求。对处理器来讲,为异步中断请求,当此信号为低电

平,并且处理器内部的相应的使能信号有效时,处理器被中断。此

信号为电平敏感,并且在处理器做出响应之前应保持低电平。nIRQ I中断请求。像nFIQ,但优先级较低。当使能时,产生异步中断。Nm[4:0]O处理器模式。输出信号为内部状态位的反向,表示处理器的操作模

式。

NMREQ O MEM请求。此信号位低电平时,表示下一个周期,处理器请求MEM

访问。此信号在Phase1时有效,至访问周期的整个Phase2。

NOPC O OP代码取。此信号位低时,表示处理器正从MEM中预取指令;为高

时,表示数据正在传输(如果总线上有数据),此信号在前一个周期

的Phase2有效,至访问周期的整个Phase1。此信号的时序像地址线一

样可以通过ALE信号来改变。当ABE信号位低时,此信号位高阻态。nRESET I复位。此为电平敏感输入信号。从一个已知地址启动处理器。低电平

将会导致正在执行的指令被异常中止。nRESET为高电平至少一个周期

之后,处理器将从地址0重新启动。nRESET必须保持低电平(nWAIT

必须为高)至少两个周期。在低电平周期,处理器会执行虚拟的指令

预取,地址为复位被激活时的地址增加,如果nRESET继续保持,地址

超过最大限制时,溢出为0。

nRW O读/写。高电平表示处理器写周期,地电平表示读周期。此信号应该

在前一个周期的Phase2有效,并保持到访问周期的Phase1结束。

此信号的时序像地址线一样可以通过ALE信号来改变。当ABE信号位

低时,此信号为高阻态。

nTRANS O MEM传输。低电平时表示处理器在用户模式,告诉MEM管理硬件,

何时应该打开调用地址,或者非用户模式激活的指示器。此信号的时

序像地址线一样可以通过ALE信号来改变。当ABE信号位低时,此信

号位高阻态。

nWAIT O等待。当访问较慢外设时,通过驱动nWAIT为低,使ARM7可以进入

长达数个MCLK周期的等待状态。在ARM7内部,Nwait和MCLK相与,

并只有当MCLK为低时nWAIT状态才改变。如果nWAIT不用,必须上

拉。

PROG32I32位的程序配置。当此信号为高时,处理器可以从32位的地址空间

取指,用地址线A[31:0];为低时,处理器从26位的地址空间取指,用

地址线A[25:0]。在后一种配置中,指令预取没有用到地址线A[31:26]。

在改变PROG32,之前,必须保证处理器在26位模式,并且下一个周期

不会写地址空间0到0X1F(包括)。

SEQ O顺序地址。当下一个MEM周期的地址同上一个周期的地址相关联

时,此信号为高。新地址将和旧地址一样或者在当一个地址的基础

上加四。

在地址可以预料的周期之前,此信号在phase1有效,并在phase2

保持。此信号可以和地位地址线一起应用,表示下一个周期为快速

MEM模式(DRAM页模式),或者旁路地址转换系统。

VDD P电源。

VSS P GND

表1:信号描述

I:INPUT

O:OUTPUT

P:POWER

3.0编程模式

ARM7支持不同的操作配置。一种为硬件配置,由输入信号控制。其他为软件控制,称为操作模式。3.1硬件配置信号

ARM7提供了三个硬件配置信号,处理器正在运行的时候可以改变,具体如下:3.1.1BigandLittleEndian(bigend 位)

ARM7依据BIGNED 信号为高或者低,将MEM 中的数据当作Big Endian 或Little Endian 格式,MEM 被看作字节线性存储,序号从0向上排列,字节0到3为第一个存储字,4到7为第二个,以此类推。

在LittleEndian格式,一个字的最小号字节被当作最低字节,最大号字节被当作最高字节。字节0将被连结到数据线D[7:0]。

最低字节在最低地址字通过最低字节的地址寻址图3:Little Endian 格式的地址

在Big Endian 格式下,最高字节被存在MEM 中的最低地址,最低字节被存在MEM 的最高地址。MEM 中字节0对应数据线D[31:24],endianism只影响加载和存储指令。参考4.7.3第37页。

????μμóé Foxit Reader ±à?-°?è¨??óD ·-°?2?????1??à1à?£

最高字节在最低地址

字通过最高字节的地址寻址

图4:Big Endian地址格式

3.1.2向下兼容的配置位

其它两个输入PROG32,DATA32用于和早期的ARM处理器兼容(参考第十章),但通常应该置1,这种配置扩展地址空间到32位,编程模式的主要改变如下面所介绍,在32位的环境下支持26位程序。推荐用32位模式编码,以便和将来的ARM处理器兼容。

为了适应32位操作,原始的ARM指令集已被改变,程序员必须注意一些附加的限制条件,这些限制条件在下面的文章里有提示。也可参考ARM应用注意事项“Rules for ARM Code Writers,”“Notes for ARM Code Writers。

3.2操作模式选择

ARM7有32位地址和32位数据线。处理器支持字节(8位),字(32位)数据类型,字必须四个字节对齐。指令按字执行,数据操作(比如加法)以字为单位执行,加载和存储操作可以为字或字节传送。

ARM7支持六种操作模式:

(1)用户模式(usr):正常的程序执行状态

(2)FIQ模式(fiq):支持数据传送或通道处理

(3)IRQ模式(irq):用于通用的中断处理

(4)管理模式(svc):用于操作系统的保护模式

(5)异常模式(abt):数据或者指令预取异常时进入

(6)无定义模式(und):当无定义指令被执行时进入

(7)

软件控制,外部中断,异常处理都可以改变操作模式。大部分的应用程序在用户模式下执行。其他模式,比如管理模式,在中断、异常服务、或者访问被保护资源时进入。

3.3寄存器

ARM7处理器共有37个寄存器,包括31个(32位)通用寄存器,6个状态寄存器。在任意时候,16个通用寄存器(R0-R15)和一个或者两个状态寄存器对处理器来讲是可见的。可见寄存器依据处理器模式和其它寄存器(bankedregisters)将被切换去支持IRQ,FIQ,管理,异常,无定义模式的处理。异常模式,非定义模式。图5显示了寄存器Bank组成,banked的寄存器在图中用阴影显示。

在所有的模式中,16个寄存器(R0-R15)都可以直接访问。除过R15,其他的寄存器都是通用寄存器,可以用来保存数据和地址。R15保存可编程计数器PC的值,当R15被读时,位[1:0]为’0’,位[31:2]保存计数器的值。第十七个寄存器(CPSR-当前程序状态寄存器)也是可以访问的。它包括了条件代码标志位和当前模式位,可以当作是PC的扩展。

R14可以当作子程序连接寄存器,当执行一个分支或者连接指令时,可以保存R15的值。在其它情况下,可以当作通用寄存器用。R14_svc,R14_irq,R14_fiq,R14_abt,R14_und与R14相似,当中断或者异常发生时,或者是中断和异常程序中,分支和分支连接指令被执行时,可以保存R15的返回值。

通用寄存器和可编程计数器模式

可编程状态寄存器

图5:寄存器组织

FIQ模式有7个Banked寄存器,映射到R8-14(R8_fiq-R14_fiq)。有些FIQ程序不需要存储任何寄存器。用户模式,IRQ模式,管理模式,无定义模式都有两个Banked寄存器,映射到R13和R14。这两个Banked寄存器允许每个模式有自己的堆栈指针和l链接寄存器。管理模式,IRQ模式,异常模式和无定义模式的程序(需要不止两个Banked寄存器)能够在它们自己的堆栈中存储部分或者全部的调用程序的寄存器(R0-R12),这样就可以无限制地用这

些寄存器(R0-R12),这些寄存器在调用程序返回之前被恢复。另外,有5个SPSRs寄存器(存储可编程状态寄存器),当异常发生时拷贝CPSR。每一个特权级模式有一个SPSR。

标志控制

313029282787654321

可编程状态寄存器的格式在图6中显示,N,Z,C,和V位条件代码标志位。当作处理器的算术或者逻辑运算结束时这些条件代码标志位可能被改变,也可以在程序中以此作为条件来判断指令是否被执行。

I和F位为中断禁止位。当I置’1’时,禁止IRQ中断,当F置’1’时,禁止FIQ中断。M[4:0]为模式位,这些位决定了处理器的操作模式。表2解释了模式位M[4:0]。并不是所有的组合都表示了有效的操作,只有那些明确定义的组合才有效。

PSR寄存器的低28位(包括I,F,M[4:0])全部作为控制位。如果有异常产生这些控制位将改变,或者在管理模式,通过软件改变控制位。没有用到的位为保留位,它们的状态在在控制位和标志位改变时可以保留。当检查PSR状态时,程序并不需要依靠保留位的值来判断,因为它们在将来的处理器中中可能为’1’或者’0’。

M[4:0]模式可访问的寄存器

10000用户PC,R14…R0CPSR

10001FIQ PC,R14_fiq…R8_fiq,R7…R0CPSR,SPSR_fiq

10010IRQ PC,R14_irq…R13_irq,R12…R0CPSR,SPSR_irq

10011管理PC,R14_svc…R13_svc,R12…R0CPSR,SPSR_svc

10111异常PC,R14_abt..R13_abt,R12..R0CPSR,SPSR_abt

11011无定义PC,R14_und..R13_und,R12..R0CPSR,SPSR_und

表2模式位定义

3.4异常

当正常的程序流程需要被中断时,异常产生,使得处理器可以执行外设产生(例)的中断。进入异常处理之前,处理器的状态必须保存,以便异常处理完之后源程序可以继续执行。可能会有几个异常同时产生。

ARM7处理异常时,通过banked 寄存器保存状态。PC 和CPSR 寄存器中的内容被拷贝到相应的R14和SPSR 中,PC 和CPSR 中的模式位M[0:4]根据异常类型被强制改变。在异常断处理中,如果要禁止其它难以管理异常的嵌套,可以置位中断禁止标志位。在需要重复进入中断处理程序的情况下,R14和SPSR 应该在中断被使能之前保存到主MEM 的堆栈中;当传送SPSR 寄存器到堆栈或者从堆栈传送时,需要注意的是必须传送整个字(32位),而不只是标志位或者控制位。当多个异常同时产生时,固定的优先级决定异常响应的顺序。优先级将在以后章节中说明。3.4.1FIQ

FIQ (快速中断请求)异常是由外部产生,将Nfiq 输入拉低。此输入可以接受异步转换,在影响处理器的执行流程之前,会被延迟一个时钟周期,以便与处理器保持同步。此设计支持数据传输或者通道处理,有足够的私有寄存器转移在某些应用中需要保存的值(最小化切换成本)。可以置位在CPSR 中的F 标志位屏蔽FIQ 异常(除过用户模式),如果F 位清零,ARM7在每一条指令结束时会检查FIQ 同步器的输出是否为低电平。当检测到有FIQ 低电平输入时,ARM7执行以下步骤:

(1)将下一条将要执行的指令地址+4,保存到R14_fiq ,保存CPSR 的值到SPSR_fiq (2)强制M[4:0]=10001(FIQ 模式),置位CPSR 中的F,I (3)强制PC 从地址0X1C 取下一条指令

为了从FIQ 返回,执行SUBS PC,R14_fiq ,#4将恢复PC(从R14)和CPSR(从SPSR_fiq)并继续执行的被中断的程序。3.4.2IRQ

IRQ (中断请求)为普通异常,当nIRQ 输入位低电平时产生IRQ 。它的优先级低于FIQ ,并且当进入FIQ 异常处理程序时,它被屏蔽。在任何时候将CPSR 中I 位置1,都可以屏蔽此中断(用户模式除外)。当I 位清零时,,ARM7在每一条指令结束时会检查IRQ 同步器的输出是否有低电平。当检测到有IRQ 输入时ARM7执行以下步骤:

(1)将下一条将要执行的指令地址+4,保存到R14_fiq ,保存CPSR 的值到SPSR_fiq (2)强制M[4:0]=10010(IRQ 模式),置位CPSR 中的I (3)强制PC 从地址0X18取下一条指令

????μμóé Foxit Reader ±à?-°?è¨??óD ·-°?2?????1??à1à?£

为了从IRQ状态恢复正常,执行SUBS PC,R14_fiq,#4将恢复PC(从R14)和CPSR(从SPSR_fiq)并继续执行的被中断的程序。

3.4.3异常中断

异常中断由外部的ABORT输入产生。ABORT表示当前存储器访问没有完成。举例来讲,在虚拟存储器系统中,当前地址上相应的数据可能已经从存储器被移到disc,在访问完成之前,可能要求处理器动作以恢复这些数据。Arm7在存储器访问周期检查ABORT信号,如果有异常产生,ARM7将执行以下两种步骤之一:

(1)如果异常在指令预取时产生(预取异常),预取的指令被标志为无效,但是异常中断并不立即产生。如果指令没有被执行,举例来讲,在流水线中的一个分支指令,

将不会产生异常,如果指令到流水线的出口并将要被执行时,异常产生。

(2)如果异常在数据访问时产生(数据异常),ARM7的动作将依靠指令类型

(A)单次数据传输指令(LDR,STR)将回写改变过的基址寄存器,异常处理程序必须注意到这一点。

(B)交换指令异常(SWP),虽然外部的读写访问可能发生,但就好像此指令没有被执行一样

(C)块数据传输指令完成(LDM,STM),如果回写位置1,基址将改变。如果正常情况下,指令回写基址寄存器(LDM传输列表中的基址),则回写被禁止。当

异常产生时,所有寄存器回写都被禁止。这就意味着当LDM指令异常时,R15

(总是最后一个被传送)将保留。

在指令预取异常或数据异常发生,ARM7进行以下操作:

(1)保存地址(异常指令地址加4for指令预取异常,加8for数据异常)到R14_abt,保存CPSR到SPSR_abt

(2)强制M[4:0]=10111(异常模式),置位CPSR中的I

(3)强制PC从地址0X0C(预取异常)或0X10(数据异常)取下一条指令

为了从异常返回,执行SUBS PC,R14_abt,#4(预取异常)或SUBS PC,R14_abt,#8(数据异常),恢复PC和CPSR并继续执行被异常的指令。

当适当的MEM管理软件有效时,异常机制允许执行需要的页式虚拟MEM系统。处理器可以产生任意地址,如果地址中的数据无效时,MMU产生异常。处理器进入系统软件陷阱,系统软件必须找出异常原因,使请求的数据有效,重新执行被异常的指令。应用程序不需要知道它用到的有效MEM的总量,也不需要异常时的状态。

3.4.4软件中断

软件中断指令(SWI )从其它模式进入管理模式。通常情况下,请求一个特殊的管理函数。当SWI 指令被执行时,ARM7执行以下动作:

(1)将SWI 指令地址加4保存到R14_svc ,保存CPSR 的值到SPSR_svc (2)强制M[4:0]=10011(管理模式),置位CPSR 中的I (3)强制PC 在地址0X80取下一条指令

为了从SWI 返回,执行指令MOVS PC,R14_svc ,恢复PC 和CPSR 的值,返回到SWI 的下一条指令。

3.4.5无定义的指令陷阱

当ARM7遇到自己没有办法处理的指令(第四章:指令集),它将此指令提供给现场的协处理器。如果协处理器可以执行此指令,但当时又比较忙,ARM7将进入等待状态,直到协处理器准备好或者中断产生。如果没有协处理器可以处理此指令,ARM7将进入无定义指令陷阱。

当系统中没有协处理器硬件时,陷阱可以用来做协处理器的软件仿真,或者通过软件仿真用于通用指令集扩展。

当ARM7接收到无定义指令陷阱时,执行以下步骤:

(1)将无定义指令或协处理器指令加4保存到R14_und;保存CPSR 到SPSR_und.(2)强制M[4:0]=11011(无定义模式),置位CPSR 中的I (3)强制PC 在地址0X04取下一条指令

在仿真失败的指令之后,为了从陷阱返回,执行MOVS PC,R14_und,恢复CPSR 并返回到无定义指令的下一条指令。

????μμóé Foxit Reader ±à?-°?è¨??óD ·-°?2?????1??à1à?£

3.4.6向量总结

地址异常进入模式

0X00000000复位管理模式

0X00000004无定义指令无定义

0X00000008软件中断管理

0X0000000C异常(预取)异常

0X00000010异常(数据)异常

0X00000014保留--

0X00000018IRQ IRQ

0X0000001C FIQ FIQ

表3:向量总结

这些是字节地址,通常包括了指向相关程序的分支指令。

FIQ程序处于0X1C,从而不需要分支指令(和执行时间)。

3.4.7异常优先级

当多个异常时产生时,固定的优先级系统决定异常处理的顺序:

(1)复位(最高优先级)

(2)数据异常中断

(3)FIQ

(4)IRQ

(5)预取异常

(6)无定义异常,软件中断(最低优先级)

注意,不是所有的异常都会立即产生,无定义指令和软件中断互为排斥,因为它们都依靠当前指令的特定译码(不能重叠)。

如果数据异常和FIQ同时发生,且FIQ被使能(CPSR中F标志位为0),ARM7将进入数据异常处理,然后立即进入FIQ中断向量处理,从FIQ的正常返回将使数据异常处理器继续运行。数据异常优先级高于FIQ,保证能够检测到传输错误,计算数据异常响应时间应该加上最差的情况下FIQ处理的时间。

新版汇编语言程序设计习题答案(钱晓捷主 编)

新版汇编语言程序设计习题答案(钱晓捷主编) 第一章汇编语言基础知识 1.1、简述计算机系统的硬件组成及各部分作用 1.2、明确下列概念或符号: 主存和辅存,RAM和ROM,存储器地址和I/O端口,KB、MB、GB和TB 1.3、什么是汇编语言源程序、汇编程序、目标程序? 1.4、汇编语言与高级语言相比有什么优缺点? 1.5、将下列十六进制数转换为二进制和十进制表示 (1)FFH (2)0H (3)5EH (4)EFH (5)2EH (6)10H (7)1FH (8)ABH 1.6、将下列十进制数转换为BCD码表示 (1)12 (2)24 (3)68 (4)127 (5)128 (6)255 (7)1234 (8)2458 1.7、将下列BCD码转换为十进制数 (1)10010001 (2)10001001 (3)00110110 (4)10010000 (5)00001000 (6)10010111 (7)10000001 (8)00000010 1.8、将下列十进制数分别用8位二进制数的原码、反码和补码表示 (1)0 (2)-127 (3)127 (4)-57 (5)126 (6)-126 (7)-128 (8)68 1.9、完成下列二进制数的运算 (1)1011+1001 (2)1011-1001 (3)1011×1001 (4)10111000÷1001 (5)1011 ∧~1011 (8)1011 ⊕ 1001 1001(6)1011 ∨1001(7) 1.10 数码0~9、大写字母A~Z、小写字母a~z对应的ASCII码分别是多少?ASCII码为0dh、0ah对应的是什么字符? 1.11、计算机中有一个“01100001”编码,如果把它认为是无符号数,它是10进制什么数?如果认为它是BCD码,则表示什么数?又如果它是某个ASCII码,则代表哪个字符? 1.12、简述Intel 80x86系列微处理器在指令集方面的发展。 1.13、什么是DOS和ROM-BIOS? 1.14、简述PC机最低1MB主存空间的使用情况。 1.15、罗列8086CPU的8个8位和16位通用寄存器,并说明各自的作用。 1.16、什么是标志,它有什么用途?状态标志和控制标志有什么区别?画出标志寄存器FLAGS,说明各个标志的位置和含义。

第1章汇编语言基础知识 1.简述汇编语言源程序、汇编程序、和目标程序的关系。 答:用汇编语言编写的程序称为汇编源程序;汇编源程序在汇编程序的翻译下转换成计算机语言变成目标程序。 2. 简述汇编语言的优缺点。 答:(1) 汇编语言的优点: ①可有效地访问、控制计算机各种硬件设备,如磁盘、存储器、CPU、I/O端口等。. ②目标代码简短,占用内存少,执行速度快,是高效的程序设计语言。 ③可与高级语言配合使用,应用十分广泛。 (2) 汇编语言的缺点: ①通用性和可移植性较差 ②相对于高级语言来说较繁锁、易出错、不够直观。 3.CPU的寻址能力为8KB,那么它的地址总线的宽度为多少? 答:13 4. 1KB的存储器有多少个存储单元? 答:1024个字节。 5. 指令中的逻辑地址由哪两部分组成? 答:指令中的逻辑地址由段基址和偏移量组成。 6. 以下为用段基址:偏移量形式表示的内存地址,试计算它们的物理地址。 (1) 12F8:0100 (2) 1A2F:0103 (3) 1A3F:0003 (4) 1A3F:A1FF 答: (1) 13080H (2) 1A3F3H (3) 1A3F3H (4) 245EFH 7. 自12FA:0000开始的内存单元中存放以下数据(用十六进制形式表示): 03 06 11 A3 13 01,试分别写出12FA:0002的字节型数据、字型数据及双字型数据 的值。 答:字节型数据:11H 字型数据:0A311H 双字型数据:0113A311H 8. 内存中某单元的物理地址是19318H,段基地址为1916H,则段内偏移地址为 多少?若段内偏移地址为2228H,则段基地址为多少? 答:若段基地址为1916H,则段内偏移地址为01B8H;若段内偏移地址为2228H,则段基地址为170FH 9. 在实模式环境中,一个段最长不能超过多少字节? 答:64KB 10. 实模式可寻址的内存范围是多少? 答:1MB

《汇编语言程序设计》课程教学大纲 二、课程简介 汇编语言是计算机能够提供给用户使用的最快最有效的语言,也是能够利用计算机所有硬件特性并能直接控制硬件的唯一语言,因而,对程序的空间和时间要求很高的场合及需要直接控制硬件的应用场合,汇编语言的应用是必不可少三、课程目标 汇编语言课程是计算机专业的一门专业选修课。通过本课程的学习,应使学 生系统地了解计算机组成原理与内部的运行机理,掌握汇编语言程序设计及相关 知识,为学习本专业后继课程和进行与硬件有关的技术工作打下良好基础。通过 上机实验,使学生受到软硬件实验的初步训练,并培养学生分析问题和解决问题 的能力。 四、教学内容及要求 第一章基础知识 1.教学内容 (1) 为什么要用汇编语言编写程序 (2) 进位计数制与不同基数的数之间的转换 (3) 二进制数和十六进制数运算 (4) 计算机中数和字符的表示 (5) 几种基本的逻辑运算 2.基本要求 了解机器指令、代码指令、机器语言、汇编指令、汇编语言、汇编语言源程 序、汇编程序、汇编等概念;掌握进位计数制与不同基数的数之间的转换及

运算;计算机中数和字符的表示;“与”、“或”、“非”、“异或”等几种基本的逻辑运算; 第二章80X86计算机组织 1.教学内容 计算机系统概述、存储器、中央处理机和外部设备。 2.基本要求 理解计算机的硬件和软件系统及其关系。掌握计算机的基本结构及总线;存储器的内容、地址及存储器的分段;中央处理机的组成、80X86系列CPU工作寄存器构成和功能,特别是段寄存器和标志寄存器;外设接口、端口和8086/8088的端口地址范围和访问方法。 第三章80X86的指令系统 1.教学内容(重点内容) IBM PC机的寻址方式、IBM PC机的指令系统。 2.基本要求 熟练掌握IBM PC机寻址方式及物理地址的计算;数据传送、算术、逻辑、串处理、控制转移和处理机控制指令六组中的所有指令的格式、操作、及影响的标志位。了解机器语言的指令组成; 第四章汇编语言程序格式 1.教学内容 汇编程序功能、伪操作、汇编语言程序格式、汇编语言程序的上机过程。 2.基本要求 掌握DEBUG程序和命令及能用DEBUG 程序调试和运行简单小程序;汇编语言上机步骤、汇编程序的功能;数据定义及存储器分配、表达式赋值“EQU”和“=”、段定义、程序开始和结束、对准、基数控制等六类伪操作;汇编语言程序格式中的名字、操作、操作数和注释等项。 第五章循环与分支程序设计 1.教学内容 程序设计的一般步骤和基本结构、循环程序设计和分支程序设计 2.基本要求 掌握汇编语言程序的编制步骤和结构化程序设计的三种基本结构;循环的设计方法和多层循环的设计;分支程序的设计方法,并能编制相应的程序。第六章子程序结构 1.教学内容 子程序的设计方法、嵌套与递归子程序、子程序举例和DOS系统功能调用

汇编语言程序设计(第二版) 钱晓捷习题答案 第二章(01) 2.1 (1)AX=1200h (2)AX=0100h (3)AX=4C2Ah (4)AX=3412h (5)AX=4C2Ah (6)AX=7856h (7)AX=65B7h 2.2(1) 两操作数类型不匹配 (2) IP指令指针禁止用户访问 (3) 立即数不允许传给段寄存器 (4) 段寄存器之间不允许传送 (5) 两操作数类型不匹配 (6) 目的操作数应为[ BP ] (7) 源操作数应为[BX+DI] (8) 立即数不能作目的操作数 2.3 lea bx,table ;获取table的首地址,BX=200H mov al,8 ;传送欲转换的数字,AL=8 xlat ;转换为格雷码,AL=12H 2.4 堆栈是一种按“先进后出”原则存取数据的存储区域。 堆栈的两种基本操作是压栈和出栈,对应的指令是PUSH和POP。 2.5 mov ax,8057h push ax mov ax,0f79h push ax pop bx ;bx=0f79h pop [bx] ;DS:[0f79h]=8057h 2.6 AL=89h CF ZF SF OF PF AL=12h 1 0 0 1 1 AL=0afh 0 0 1 0 1 AL=0afh 1 0 1 0 1 AL=00h 0 1 0 0 1 AL=0ffh 0 0 1 0 1 AL=00h 0 1 0 0 1 2.7 W=X+Y+24-Z

2.8 (1)ADD DX,BX (2)ADD AL,[BX+SI] (3)ADD [BX+0B2H],CX (4)ADD WORD PTR [0520H],3412H (5)ADD AL,0A0H 2.9;为了避免与操作数地址混淆,将题中X,Y,Z,V 字操作数改为A,B,C,D mov ax,X ;ax=A imul Y ;dx,ax = A*B (将操作数看作符号数,以下同) mov cx,ax mov bx,dx ;bx,ax <-- dx,ax =A*B mov ax,Z ;ax = C cwd ;dx,ax =C (扩展符号后为双字) add cx,ax adc bx,dx ;bx,cx <-- bx,cx+dx,ax=A*B+C sub cx,540 sbb bx,0 ;bx,cx<-- A*B+C-540 mov ax, V ;ax= D cwd ;dx,ax= D (扩展符号后为双字) sub ax, cx sbb dx, bx ;dx,ax = dx,ax - bx,cx = D-(A*B+C-540) idiv X ;运算结果:[D-(A*B+C-540h)]/A ;ax存商,dx存余数 2.10;(1)xchg的操作数不能是立即数 (2不能对CS直接赋值 (3)两个操作数不能都是存储单元 (4)堆栈的操作数不能是字节量 (5)adc的操作数不能是段寄存器 (6)没有确定是字节还是字操作 (7)in不支持超过FFH的直接寻址 (8)out只能以AL/AX为源操作数 第二章(02) 2.11; 指令AX的值CF OF SF ZF PF Mov ax,1407h1470h----- And ax,ax1470h00000 Or ax,ax1470h00000 Xor ax,ax000011 Not ax0ffffh----- Test ax,0f0f0h0ffffh00101 注意: 1. mov, not指令不影响标志位 2. 其他逻辑指令使CF=OF=0, 根据结果影响其他标志位。

第四章MCS-51汇编语言程序设计 重点及难点: 单片机汇编语言程序设计的基本概念、伪指令、单片机汇编语言程序的三种基本结构形式、常用汇编语言程序设计。 教学基本要求: 1、掌握汇编语言程序设计的基本概念; 2、掌握伪指令的格式、功能和使用方法; 3、掌握顺序结构、分支结构和循环结构程序设计的步骤和方法; 4、掌握常用汇编语言程序设计步骤和方法。 教学内容 §4.1汇编语言程序设计概述 一、汇编语言的特点 (1)助记符指令和机器指令一一对应,所以用汇编语言编写的程序效率高,占用存储空间小,运行速度快,因此汇编语言能编写出最优化的程序。 (2)使用汇编语言编程比使用高级语言困难,因为汇编语言是面向计算机的,汇编语言的程序设计人员必须对计算机硬件有相当深入的了解。 (3)汇编语言能直接访问存储器及接口电路,也能处理中断,因此汇编语言程序能够直接管理和控制硬件设备。 (4)汇编语言缺乏通用性,程序不易移植,各种计算机都有自己的汇编语言,不同计算机的汇编语言之间不能通用;但是掌握了一种计算机系统的汇编语言后,学习其他的汇编语言就不太困难了。 二、汇编语言的语句格式 [<标号>]:<操作码> [<操作数>];[<注释>] 三、汇编语言程序设计的步骤与特点 (1)建立数学模型 (2)确定算法 (3)制定程序流程图 (4)确定数据结构 (5)写出源程序 (6)上机调试程序 §4.2伪指令 伪指令是程序员发给汇编程序的命令,也称为汇编命令或汇编程序控制指令。 MCS- 51常见汇编语言程序中常用的伪指令:

第四章MCS-51汇编语言程序设计91 1.ORG (ORiGin)汇编起始地址命令 [<标号:>] ORG <地址> 2.END (END of assembly)汇编终止命令 [<标号:>] END [<表达式>] 3.EQU (EQUate)赋值命令 <字符名称> EQU <赋值项> 4.DB (Define Byte)定义字节命令 [<标号:>] DB <8位数表> 5.DW (Define Word)定义数据字命令 [<标号:>] DW <16位数表> 6.DS (Define Stonage )定义存储区命令 [<标号:>] DW <16位数表> 7.BIT位定义命令 <字符名称> BIT <位地址> 8.DA TA数据地址赋值命令 <字符名称> DATA <表达式> §4.3单片机汇编语言程序的基本结构形式 一、顺序程序 [例4-1]三字节无符号数相加,其中被加数在内部RAM的50H、51H和52H单元中;加数在内部RAM的53H、5414和55H单元中;要求把相加之和存放在50H、51H和52H单元中,进位存放在位寻址区的00H位中。 MOV R0 ,# 52H ;被加数的低字节地址 MOV R1 ,# 55H ;加数的低字节地址 MOV A ,@ R0 ADD A ,@ R1 ;低字节相加 MOV @ R0 , A ;存低字节相加结果 DEC R0 DEC R1 MOV A ,@ R0 ADDC A ,@ R1 ;中间字节带进位相加 MOV @ R0 , A ;存中间字节相加结果 DEC R0 DEC R1 MOV A ,@ R0 ADDC A ,@ R1 ;高字节带进位相加 MOV @ R0 , A ;存高字节相加结果 CLR A

实验1 简单汇编语言程序设计 一、实验目的与要求 1.熟悉汇编语言运行、调试环境及方法。 2.掌握简单汇编语言程序的设计方法。 3.熟悉调试工具DEBUG,并运用DEBUG 工具调试程序。 二、实验内容 根据下列要求,编写汇编源程序,汇编连接汇编源程序,并利用DEBUG 工具调试程序,验证程序的正确性。 1. 若X、Y、R、W 是存放8 位带符号数字节单元的地址,Z 是16 位字单元的 地址。试编写汇编程序,完成Z←((W-X) ÷5-Y)?(R+ 2) 。 2.试编写一个程序,测试某数是否是奇数。如该数是奇数,则把DL 的第0 位置1,否则将该位置0。 三、实验报告要求 1.程序算法流程图。 2.源程序清单。 3.程序运行结果。 4.调试过程中遇到的问题和解决的方法。

实验2 分支及循环程序设计 一、实验目的与要求 1.熟悉汇编语言运行、调试环境及方法。 2.掌握分支程序和循环程序的设计方法。 3.熟悉调试工具DEBUG,并运用DEBUG工具调试程序。 二、实验内容 根据下列要求,编写汇编源程序,汇编连接汇编源程序,并利用DEBUG工具调试程序,验证程序的正确性。 1.编写汇编程序,统计某存储区若干个数据中英文字母的个数,并将结果在屏幕上显示。 2.从键盘任意输入一组字符数据,请编写汇编程序将该组数据加密后在屏幕上显示。参考加密方法是:每个数乘以2。(说明:本题的加密方法,同学们可以自己拟定) 三、实验报告要求 1.程序算法流程图。 2.源程序清单。 3.程序运行结果。 4.调试过程中遇到的问题和解决的方法。

实验3 子程序程序设计 一、实验目的与要求 1.熟悉汇编语言运行、调试环境及方法。 2.掌握子程序的设计方法。 3.熟悉调试工具DEBUG,并运用DEBUG工具调试程序。 二、实验内容 根据下列要求,编写汇编源程序,并利用DEBUG工具调试程序,验证程序的正确性。 1.编程以十进制形式和十六进制形式显示AX的内容,并把两个显示功能分别封装成子程序dispDEC和dispHEX。 2.设在以EXAMSCORE为首地址的数据缓冲区依次存放某班10名同学5门功课的成绩,现要统计各位同学的总分,并将总分放在该学生单科成绩后的单元,并调用第1个程序封装好的子程序,以十进制方式显示统计情况,显示格式自行设计。请编程完成此功能。数据缓冲区参考数据定义如下: EXAMSCORE DB 01 ;学号 DB 89,76,54,77,99 ;单科成绩 DW ? ;该学生的总分 DB 02 ;学号 DB 79,88,64,97,92 ;单科成绩 DW ? ;该学生的总分 三、实验报告要求 1.程序算法流程图。 2.源程序清单。 3.程序运行结果。 4.调试过程中遇到的问题和解决的方法。

汇编语言程序设计试卷 一、单项选择题(在每小题的四个备选答案中,选出一个正确的答案,并将其号码填在题干后的括号内,每小题1分,共20分) 1.十六进制数88H,可表示成下面几种形式,请找出错误的表示()。 ① 无符号十进制数136 ② 带符号十进制数-120 ③ 压缩型BCD码十进制数88 ④ 8位二进制数-8的补码表示 2.指令指针寄存器是()。 ① IP ② SP ③ BP ④ PSW 3.当执行指令ADD AX,BX后,若AX的内容为2BA0H, 设置的奇偶标志位PF=1,下面的叙述正确的是()。 ① 表示结果中含1的个数为偶数 ② 表示结果中含1的个数为奇数 ③ 表示该数为偶数 ④ 表示结果中低八位含1的个数为偶数 4.完成将累加器AL清零,并使进位标志CF清零, 下面错误的指令是()。 ① MOV AL,00H ② AND AL,00H

③ XOR AL,AL ④ SUB AL,AL 5.下列指令执行后总是使CF=0,OF=0的是()。 ① AND ② NEG ③ NOT ④ INC 6.完成同指令XCHG AX,BX相同功能的指令或指令序列是()。 ① MOV AX,BX ② MOV BX,AX ③ PUSH AX POP BX ④ MOV CX,AX MOV AX,BX MOV BX,CX 7.设AH=0,AL=06H,BL=09H,执行指令 ADD AL,BL AAA 之后,其结果应是()。 ① AH=01,AL=05 ② AH=1 AL=15 ③ AH=0 AL=0FH ④ AH=0 AL=05 8.设AL=0B4H,BL=11H,指令“MUL BL”和指令“IMUL BL”分别执行后OF,CF的值为

第一章. 习题 1.1用降幂法和除法将下列十进制数转换为二进制数和十六进制数: (1) 369 (2) 10000 (3) 4095 (4) 32767 答:(1) 369=1 0111 0001B=171H (2) 10000=10 0111 0001 0000B=2710H (3) 4095=1111 1111 1111B=FFFH (4) 32767=111 1111 1111 1111B=7FFFH 1.2将下列二进制数转换为十六进制数和十进制数: (1) 10 1101 (2) 1000 0000 (3) 1111 1111 1111 1111 (4) 1111 1111 答:(1) 10 1101B=2DH=45 (2) 1000 0000B=80H=128 (3) 1111 1111 1111 1111B=FFFFH=65535 (4) 1111 1111B=FFH=255 1.3将下列十六进制数转换为二进制数和十进制数: (1) FA (2) 5B (3) FFFE (4) 1234 答:(1) FAH=1111 1010B=250 (2) 5BH=101 1011B=91 (3) FFFEH=1111 1111 1111 1110B=65534 (4) 1234H=1 0010 0011 0100B=4660 1.4完成下列十六进制数的运算,并转换为十进制数进行校核: (1) 3A+B7 (2) 1234+AF (3) ABCD-FE (4) 7AB×6F 答:(1) 3A+B7H=F1H=241 (2) 1234+AFH=12E3H=4835 (3) ABCD-FEH=AACFH=43727 (4) 7AB×6FH=35325H=217893 1.5下列各数均为十进制数,请用8位二进制补码计算下列各题,并用十六进制数表示其 运算结果。 (1) (-85)+76 (2) 85+(-76) (3) 85-76 (4) 85-(-76) (5) (-85)-76 (6) -85-(-76) 答:(1) (-85)+76=1010 1011B+0100 1100B=1111 0111B=0F7H;CF=0;OF=0 (2) 85+(-76)=0101 0101B+1011 0100B=0000 1001B=09H;CF=1;OF=0 (3) 85-76=0101 0101B-0100 1100B=0101 0101B+1011 0100B=0000 1001B=09H;CF=0; OF=0 (4) 85-(-76)=0101 0101B-1011 0100B=0101 0101B+0100 1100B=10100001B=0A1H; CF=0;OF=1 (5) (-85)-76=1010 1011B-0100 1100B=1010 1011B+1011 0100B=0101 1111B=5FH; CF=0;OF=1 (6) -85-(-76)=1010 1011B-1011 0100B=1010 1011B+0100 1100B=11110111B=0F7H; CF=0;OF=0 1.6下列各数为十六进制表示的8位二进制数,请说明当它们分别被看作是用补码表示的 带符号数或无符号数时,它们所表示的十进制数是什么?

考核方式与要求 期末总成绩构成:期末开卷考试60% + 平时作业10% + 实验和实验报告30%。 1、试卷考核方式与要求 “汇编语言程序设计”的课程要求是使学生具有一定的程序设计能力。虽然课程是通过80x86微处理机来开展教学的,但学习的重点不仅仅是学会80x86指令的语法和规范,更重要的是通过多读程序、多练习编写程序来掌握程序设计的基本方法和技术,要求学生在工作中遇到其他机型,都应该能利用所掌握的方法和技术顺利解决实际问题。因此,我们在教学过程的各个环节,特别是具有指挥棒作用的考核环节中,着重体现了“能力培养是首位”的指导思想。 为此,汇编课一直实行多元化考核方式,在考核评分上,平时练习和上机实验占40%,期末考试占60%。期末考试实行开卷考试,这样学生平时学习的关注点就会放在分析问题和编程实现的方法上,有利于学生开阔思路,发挥自身创造力。每年设计开卷考试的考题是有一定难度的,教师必须非常熟悉课程的知识点、重点和难点,以及体现这些知识和能力水平的多种题目类型。 2、实验方式与要求 实验的目标为:加强课堂上相关理论和技术学习的有效性;提高学生上机编程和调试的能力;培养学生科学实践的理念和独立分析问题、解决问题的能力。其设计思想是:实验内容兼顾基础性和综合性,实验题目由简单→复杂,程序功能由单一→综合,实验安排有基本要求题+自选题,实验题类型有验证型和自主创新设计型。 √实验课组织形式: 1.系教学实验室按课程要求负责上机环境配置及实验设备管理; 2.以班为单位组织上机实验,并将上机时间安排表发至每位同学; 3.每单元实验课安排一位助教(助博)负责实验指导和答疑; 4.学生每做完一个实验即可提交老师验收,老师将实验运行结果记录下来作为实验成 绩的依据。验收时教师要注意发现比较突出的好的实验例题(完成时间短、程序运行效率高); 5.要求提交实验报告,根据实验报告及实验运行结果的记录,评出实验成绩,实验成 绩一般占总成绩的30%。 √教师指导方法: 1.大课集体指导。每学期实验前教师安排一次实验指导课,讲解实验方法和实验要求; 2.每次实验课都安排助教(助博)进行个别或集体的实验指导和答疑; 3.对具有共性的、问题比较多的实验,主讲教师在课堂上再进行集体指导; 4.每学期对实验中出现的问题,对照实验题目进行分析、总结,以利于以后的教学。 5.对于实验中有创新点的学生,还可以请他上讲台为同学们介绍他的设计思路,引发大家展开讨论。

第1章汇编语言基础知识(全) 2010-10-18 19:32:40| 分类:答案集锦| 标签:|字号大中小订阅 第1章汇编语言基础知识 〔习题1.1〕简述计算机系统的硬件组成及各部分作用。 〔解答〕 CPU:包括运算器、控制器和寄存器组。运算器执行所有的算术和逻辑运算;控制器负责把指指令逐条从存储器中取出,经译码分析后向机器发出各种控制命令,并正确完成程序所要求的功能;寄存器组为 处理单元提供所需要的数据。 存储器:是计算机的记忆部件,它用来存放程序以及程序中所涉及的数据。 外部设备:实现人机交换和机间的通信。 〔习题1.2〕明确下列概念或符号: 主存和辅存,RAM和ROM,存储器地址和I/O端口,KB、MB、GB和TB 〔解答〕 主存又称内存是主存储器的简称,主存储器存放当前正在执行的程序和使用的数据,CPU可以直接存取,它由半导体存储器芯片构成其成本高、容量小、但速度快。辅存是辅助存储器的简称,辅存可用来长期保存大量程序和数据,CPU需要通过I/O接口访问,它由磁盘或光盘构成,其成本低、容量大,但速 度慢。 RAM是随机存取存储器的英语简写,由于CPU可以从RAM读信息,也可以向RAM写入信息,所以RAM也被称为读写存储器,RAM型半导体存储器可以按地址随机读写,但这类存储器在断电后不能保存信息;而ROM中的信息只能被读出,不能被修改,ROM型半导体通常只能被读出,但这类存储器断电 后能保存信息。 存储器由大量存储单元组成。为了区别每个单元,我们将它们编号,于是,每个存储单元就有了一个存储地址,I/O接口是由一组寄存器组成,为了区别它们,各个寄存器进行了编号,形成I/O地址,通常 称做I/O端口。 KB是千字节、MB是兆字节、GB是吉字节和TB是太字节,它们都是表示存储器存储单元的单位。 〔习题1.3〕什么是汇编语言源程序、汇编程序、目标程序? 〔解答〕 用汇编语言书写的程序就称为汇编语言源程序;完成汇编工作的程序就是汇编程序;由汇编程序编 译通过的程序就是目标程序。

汇编语言程序设计实验 网络*** *** 实验一 顺序与分支程序设计 一 、实验目的 1) 掌握顺序程序设计方法。 2) 掌握分支程序的结构及分支程序的设计,调试方法。 2) 学习数据传送及算术和逻辑运算指令的用法。 3) 熟悉在pc 机上建立、汇编、连接、调试和运行汇编语言程序的过程。 二、实验内容 1.实验六 从键盘上接收一位十进制数x ,计算y 值,并以十六进制形式显示出来,y 按下列公式计算。 ???????===-=+=) 6(2/) 5()4(2) 3(22 2 2X X X X X X X X X X Y 2..实验七 实验内容:从键盘上接收两个一位十六进制数x 和y ,然后再输入一个a-d 之间的一个字符,按下列要求计算。 a) 当输入字符为a ,则计算x+y ,并以十六进 制形式显示出来 b) 当输入字符为b ,则计算|x-y|,并以十六进制形式显示出来 c) 当输入字符为c ,则计算x*y ,并以十六进制形式显示出来 d) 当输入字符为d ,则计算x/y ,并以十六进制形式显示出来 三、实验代码 实验六 DATE SEGMENT X DB ?

DATE ENDS ;数据段 CODE SEGMENT ASSUME CS:CODE,DS:DATE START:MOV AX,DATE ;代码段 MOV DS,AX ;初始化ds寄存器 MOV AH,1 INT 21H ;读文件到缓冲区 CMP AL,33H ;比较指令 JB L0 ;A汇编语言程序设计习题-答案

4.1 分析执行下列指令序列后的结果: 1)MOV AX,1234H MOV BX,00FFH AND AX,BX 【答】(AX)=0034H 2)MOV AL,01010101B AND AL,00011111B ;(AL)=00010101B OR AL,11000000B ;(AL)=11010101B XOR AL,00001111B ;(AL)=11011010B NOT AL 【答】(AL)=00100101B 3)MOV DL,05H MOV AX,0A00H MOV DS,AX MOV SI,0H MOV CX,0FH AGAIN: INC SI CMP [SI],DL LOOPNE A GAIN HLT 本程序实现了什么功能? 【答】在以0A001H开始的15个单元中查找05H。 4)MOV AX,DSEGADDR MOV DS, AX MOV ES,AX MOV SI, OFFSET B1ADDR MOV DI,OFFSET B2ADDR MOV CX,N CLD REP MOVSB HLT 本程序实现了什么功能? 【答】将B1ADDR中N个字节数据传送到B2ADDR开始的15个存储单元。 5)MOV AX, 0H MOV DS,AX MOV ES, AX MOV AL,05H MOV DI,0A000H MOV CX,0FH CLD AGAIN: SCASB LOOPNE AGAIN HLT 本程序实现了什么功能? 【答】从地址0A000H开始的15个单元中查找字节型数据05H,用条件循环LOOPNZ,控制数据05H的查找。 4.2 阅读程序: 1). CLD LEA DI,[0100H] MOV CX, 0080H XOR AX, AX REP STOSW 本程序实现了什么功能? 【答】将DS中起始地址为0100H的128个字节单元清零。 2). MOV AL, 08H SAL AL,01H ;(AL)=00010000H MOV BL, AL MOV CL ,02H

汇编语言的编程步骤与调试方法 一、汇编源程序的建立 1. 使用工具 (1)EDIT,记事本等文本编辑软件,编辑源程序,保存为.asm文 件; (2)ASM,MASM汇编程序,对源程序进行汇编,生成.obj文件- 目标文件,以及调试用.LST-列表文件和.CRF-交叉引用表; (3)Link连接程序,对使用的目标文件和库文件进行连接,生 成.exe文件,同时调试用.map-地址映像文件; 如果源程序无语法错误,上述三步将生成可运行的.exe文件, 如果运行结果无误,则完成对汇编程序的编程,如果运行后结果存 在错误,需要进行调试。 (4)Debug调试程序,对.exe文件进行调试,修改,直到程序正 确。 图3 目标程序生成步骤图2. 编程过程 (1)用文本编辑软件,编写扩展名为.asm的源文程序文件。 (2)用汇编程序对编好的源文件进行汇编。 命令行:masm [*.asm] ↙ 如果源文件中存在语法错误,则汇编程序将指出错误类型及位置,可根据这些信息重新编辑源文件,直至无语法错误,汇编后,将生成指定名称的目标文件.obj。 使用MASM50汇编程序进行汇编,输入命令行masm或者masm *.asm后,根据提示,输入文件名,在汇编没有错误的情况下,如屏幕所示:汇编程序可生成三个文件,*.obj,*.lst和*.crf。 *.obj-目标文件,用于连接生成可执行文件; *.lst-列表文件(可选),汇编语言汇编的机器语言与汇编语言对照表,可用于

调试; *.crf-交叉引用文件(可选),给出了用户定义的所有符号和对每个符号定义、引用的行号。 (3)目标文件的连接 命令行:link [*.obj] [*.obj] [*.lib] ↙ 连接程序,将多个目标程序及库文件,连接生成可执行的*.exe文件,同时可选择生成*.map文件。 *.map-地址映像文件,给出内存地址分配的有关信息。 下图所示屏幕,为Link连接两个目标文件,没有错误的情况下,生成*.exe 文件。 (4)执行程序 执行*.exe文件,观察程序运行结果,如果存在错误,需要进行调试。调试工具DEBUG是针对汇编语言程序设计的一种调试工具,熟练使用DEBUG有助于汇编语言程序员对于逻辑错误的调试。 二、汇编程序的调试

课程教学大纲 (理论课) 课程名称:汇编语言程序设计 适用专业:计算机科学与技术 课程类别:学科基础课 制订时间: 2006年8月 数学与计算机科学学院制

汇编语言程序设计课程教学大纲 (2002年制订,2006年修订) 一、课程代码:0502121009 二、课程类别:学科基础课程 三、预修课程:计算机导论、高级语言程序设计等 四、学分: 4学分 五、学时: 86学时(其中实验部分32学时) 六、课程概述: 汇编语言是计算机能提供给用户最快也最有效的语言,也是能够利用计算机所有硬件特性并能直接控制硬件的唯一语言,因而在对于程序的空间和时间要求很高的场合,汇编语言是必不可少的,至于对于很多需要直接控制硬件的应用场合,则更是非用汇编语言不可。 汇编语言作为计算机专业的一门必修课程是了解计算机体系结构和操作系统的最佳切入点。通过汇编语言课程的学习,对计算机理论中包括CPU体系结构、指令调度方式、存储器管理、基本输入输出接口的理解都会有一个比较本质而且直观的认识。在对汇编语言实际运用的基础上同时还能帮助对高级语言程序设计的深入体会,包括变量的组织,地址的访问,循环与分支在机器码中的处理,调用函数时参数的传递等,所以汇编语言在本专业中是一门核心的课程,通过对本课程的学习是加深对后续课程认识的基础。 七、教学目的: 通过对本课程的学习,掌握8086微处理器的寄存器组和基本寻址方式,学生要达到对程序在计算机中的基本调度有一定认识,对二进制基础理论有深入的理解,同时熟练掌握8086汇编语言的编写方式,掌握基本的系统调用,具备良好的源程序调试能力以及最基本的、实模式下的反汇编能力。

第七章汇编语言程序设计基本方法1.教学目的:掌握微型汇编语言程序分析和设计方法 2.教学要求: ①熟悉汇编语言程序设计的基本步骤。 ②掌握程序流程图的使用,会利用其分析问题。 ③掌握汇编语言的顺序、分支、循环程序的设计。 ④了解实模式下80386及其后继机型的汇编语言的程序设计3.教学重点: ①利用流程图分析问题。 ②顺序、分支、循环程序的设计。 4.掌握难点: ①分支程序设计 ②循环程序设计 5.教学进程安排:P137~P168 6.教学方法: 课堂讲授 7.教学内容摘要: 7.1 汇编语言程序设计概述 7.1.1 汇编语言程序设计的基本步骤 1.分析问题,抽象出描述问题的数学模型 2.确定算法 3.绘制流程图 4.分配存储空间和工作单元 5.编写程序 6.静态检查 7.上机调试运行 7.1.2 程序流程图 1. 用自然语言表示算法 2. 流程图的组成 ⑴执行框(矩形框) ⑵判别框(菱形框) ⑶开始框和终止框 ⑷指向线 ⑸连接点 3. 三种基本结构和改进的流程图 ⑴传统流程图的弊端 ⑵三种基本结构 ①顺序结构 ②选择结构 ③循环结构

图7.4 顺序结构图图7.5 选择结构图 4. 结构化程序设计的特点 ⑴只有一个入口 ⑵只有一个出口 ⑶各功能框均可执行 ⑷结构中无死循环 7.2 顺序程序设计 顺序结构程序是最简单的程序,在顺序结构程序中,指令按照先后顺序一条条执行。 【例7-3】将—个字节压缩BCD码转换为两个ASCII码。 7.3 分支程序设计 7.3.1 分支程序的结构形式 分支程序结构可以有两种形式,如图7.6 (1) IF_THEN_ELSE结构 (2) CASE结构 7.3.2 分支程序设计方法 程序的分支一般用条件转移指令来产生,利用转移指令不影响条件码的特性,连续地使用条件转移指令使程序产生了多个不同的分支,而对于数组中的每一个数,它只能是多个分支中的某一个。 【例7-5】在附加段中,有一个按从小到大顺序排列的无符号数数组,其首地址存放在DI 寄存器中,数组中的第一个单元存放着数组长度,在AX中有一个无符号数,要求在数组中查找(AX),如找到,则使CF=0,并在SI中给出该元素在数组中的偏移地址;如未找到,则使CF=1。 【例7-6】折半查找算法程序 7.3.3 跳跃表法

《汇编语言程序设计》试题 专业姓名成绩 一、单项选择题(每1分,共15分). 1将下列二进制数0111,1111,1111 转换为16进制数和10进制数是() A.07FFH 3021D B. 6FEH 1021D C. 07FFH 2012D D. 07FFH 2047D 2. 在1BM Pc机的IN和OUT 指令中,I/o端口号通常是由Dx寄存器来提供的,但有时也可以在 指令中用一个字节来表示端口号。试问可以直接由指令指定的I/o端口号有多少个?( ) A. 127D B.255D C. 256D D.128D 3. 设MYDAT是一个字变量,下列指令中,错误的是() A.MOV BX,10100B B.MOV DS,AX C.ADD BX,[10100H] D.MOV BX,MYDAT[SI] 4.设有关寄存器及存储单元的内容如下:(DS)=2000H,(BX)=0100H,(SI)=0002H, (20100)=12H,(20102)=56H,(20103)=78H,(21200)=2AH,(21201)=4CH,(20202)=0B7H,(21203)=65H,试指出:MOV AX,1100h[BX]指令执行后,AX寄存器内是() A.5678H B.4C2AH C.2A4CH D.7856H 5.一台微型计算机的字长为16位,如果采用字节编址,那么它可以访问的最大存储空间是多少字节 ( ),试用16进制数表示该机的地址范围() A.1M 0~FFFFFH B.64K 0~FFFFH C.128K 0~FFFFH D.128K –FFH~FFH 6. 如果在一个程序段开始执行之前,(cs)=0A7F0H,(1P)=2B40H,试问该程序段的第一个字的物 理地址是() A.BAA40H B.AAB40H C.AAA40H D.0D603H 7.下列指令哪个是错误的(设OP1,OP2 是已经用DB定义的变量名)( ) A.CMP BL,OP1 B.MOV [BX],111001B C. INC OP2 D.SAR AX,CL 8.假定(DX)=10111001B,(CL)=05,(CF)=1试确定:RCL DL,CL 指令执行后, DX中的值是() A.00CEH B.009DH C.00B9H D.003BH 9. 有符号定义语句如下: BUFF DB 1,2,3,‘123’ EBUFF DB 0 L EQU EBUFF - BUFF 问L的值为多少( ) A.6D B.7D C.3D D.5D. 10. IBMPC机中下列那些寄存器可以用来存储存储器地址() A、BX,BP,SP,CX B、AX,SI,DI,DX C、BX,SI,DI,SP D、DX,SI,DI,SP 11.下列指令中正确的是() A.MOV [BX],[SI] B.MOV AX,[SI][DI] C.MOV BX,OFFSET NAME[SI] D.MOV BYTE PTR [100],100 12下列程序段执行后,寄存器BX中的内容是什么()

《汇编语言程序设计》课程教学大纲 学时:32 学分:2 理论学时:24 实验学时:8 面向专业:电科、电信、通信课程代码:B2700009 先开课程:C语言程序设计课程性质:必修 执笔人:王艳春审定人:陈龙猛、张金政 第一部分:理论教学部分 一、说明 1、课程的性质、地位和任务 本课程属于专业基础课,是电科、电信和通信专业学生必修的核心课程之一,是进一步学习微机原理、操作系统等课程的基础。掌握它有助于提高学生对计算机系统的设计、研究、开发和应用能力。汇编语言是一种面向机器、实践性很强的程序设计语言,必须结合一种实际的计算机来组织教学。因此,本课程选择最广泛使用的IBM PC作为具体的机型来介绍。通过课堂教学和上机实践,培养学生用汇编语言进行编程的思路、方法,养成良好的程序设计习惯,并了解底层I/O 驱动软件的编程方法,熟悉源程序汇编、链接和调试运行的步骤和方法,掌握dos、BIOS功能的调用方法及使用debug工具的调试手段,为后续课的学习打下扎实的基础。 2、课程教学和教改基本要求 课程的目的与教学基本要求:本课程主要介绍汇编语言和宏汇编的基本概念,80X86CPU的指令系统和寻址方式;介绍汇编语言程序格式、伪操作和上机全过程。通过实际例子,详细叙述顺序、分支、循环、子程序等基本程序结构以及程序设计的基本方法和技巧。学习这门课程,应达到以下几个要求: ①掌握汇编语言的基本理论知识和有关概念;掌握用汇编语言编写源程序的基本原则、方法和技巧; ②具有阅读,分析汇编语言程序的能力; ③通过上机实践,能够熟练地掌握汇编语言程序的编辑、汇编、连接、运行 过程及debug工具的调试手段。

第1章汇编语言程序设计实验 1.1 汇编语言程序设计的实验环境及上机步骤 1.1.1 实验环境 汇编语言程序设计的实验环境如下。 1.硬件环境 微型计算机(Intel x86系列 CPU)1台。 2.软件环境 ·Windows 98/XP/Me/2000操作系统; ·任意一种文本编辑器(EDIT、NOTEPAD(记事本)、UltraEDIT等); ·汇编程序(MASM.EXE或TASM.EXE); ·链接程序(LINK.EXE或TLINK.EXE); ·调试程序(DEBUG.EXE或TD.EXE)。 本书建议文本编辑器使用EDIT或NOTEPAD,汇编程序使用MASM.EXE,链接程序使用LINK.EXE,调试程序使用TD.EXE。 1.1.2 上机步骤 汇编语言程序设计的实验2和实验3仅使用TD.EXE,关于TD.EXE的使用方法请参见附录B。下面介绍的上机实验步骤适用于除实验2和实验3的所有实验(包括硬件接口部分的全部实验)。 1.确定源程序的存放目录 建议源程序存放的目录名为ASM,并放在C盘或D盘的根目录下。如果没有创建过此目录,请用如下方法创建。 通过Windows的资源管理器找到C盘的根目录,在C盘的根目录窗口中单击右键,弹出的菜单中选择“新建”→“文件夹”,并把新建的文件夹命名为ASM。 请把MASM5文件夹下的所有文件及TD.EXE都复制到此目录中。 2.建立ASM源程序 建立*.ASM源程序可以使用记事本文本编辑器。注意:保存时扩展名必须ASM。设建立的源文件为HELLO.ASM 3.用MASM.EXE汇编源程序产生OBJ目标文件 源文件HELLO.ASM建立后,要使用汇编程序对源程序文件汇编,汇编后产生二进制的目标文件(.OBJ文件)。具体操作如下: 方法一:在Windows中操作 用资源管理器打开源程序目录C:\ASM,把HELLO.ASM拖到MASM.EXE程序图标上。 方法二:在DOS命令提示符窗口中操作 选择“开始”→“程序”→“附件”→“命令提示符”,打开DOS命令提示符窗口,然后用CD命令转到源程序目录下,接着输入MASM命令: I:>C:<回车> C:>CD\ASM<回车> C:\ASM>MASM HELL0.ASM<回车> 操作时的屏幕显示如图1所示。