* 收稿日期:2011-10-20,修回日期:2011-12-03

** 邓 伟,男,1986年生,硕士研究生,研究方向:Dr ools 规则引擎。

文章编号:1003-5850(2012)02-0008-04

基于Drools 的领域专用语言应用研究

邓 伟

(太原科技大学计算机科学与技术学院,太原 030024)

摘 要:首先介绍了Dr oo ls 规则引擎和领域专用语言DSL 的基本概念,然后通过实例说明了DSL 以类自然语言的方式来构建业务层代码,详细阐述了领域专用语言在Dr oo ls 中的应用来说明它的优点。通过DSL 的应用不仅降低了业务逻辑与应用程序的耦合度,而且能以更好的方式来处理业务需求和数据模型的变化,便于系统的维护。

关键词:D ro ols ,DSL ,规则引擎,领域专用语言,可维护性中图分类号:T P 312 文献标识码:A

Research on Domain Specific Language Based on Drools

DENG Wei

(School of Com p uter Science and T echnology ,T aiy uan U niv er sity of Science and T echnology ,T aiy uan 030024,China )

Abstract :In this thesis,the basic co ncept o f rule engine and do main specific lang uag e about Drools is intro duced at first.T hen,w e describe DSL in detail with some ex amples in o rder to prov e the advantag e of DSL.Not o nly can DSL reduce the deg ree o f coupling between business logic layer and application layer,but also it deals w ith changes to the r equirements or changes to the data m odel in a much better w ay.It is helpful to the maintenance o f the system.

Key words :Droo ls,DSL,rule engine,dom ain specific lang uag e,maintenance

随着软件规模越来越庞大,业务需求经常变动,J2EE 架构在业务逻辑层的不足越来越明显。业务需求的变动往往使得业务逻辑层代码大幅度改动,Jav a 规则引擎[1]的出现弥补了这方面的不足。Java 规则引擎起源于基于规则的专家系统。它将业务逻辑与应用程序分离,大大提高了系统的可维护性、可重用性。Dro ols 是比较优秀的规则引擎之一。它的核心是Dro ols Ex pert ,也可称为Rule Eng ine ,它将事实与业务规则进行匹配,推理出结论。它是由Red Hat 支持的,用Java 语言编写的开源规则引擎。Droo ls 实现了JSR94标准[2],即Jav a 规则引擎A PI 标准的规则引擎。JSR94提供了规则解析与注册、规则执行、规则过滤等的接口。实现JSR 94标准的好处在于减少了学习其他实现该标准的规则引擎的时间,而且各种实现该标准的规则引擎之间可以相互替换,而且不用改变应用程序。Dr ools 带来的主要优点在于,它使得规则对于业

务分析人员和一个新的开发者来说很容易理解;系统的可维护性高;很容易增加新的规则,修改和移除已经存在的规则;需求很自然地转换成规则;规则的可重用性与应用程序分离;能够嵌入到现有的应用中来实现其中某些部分的功能。

1 Dro ols 规则引擎

1.1 Drools 组成部分

Dro ols 是一个业务逻辑集成平台,它经历过5次大的发展里程,最新版本为Drools 5.3,它主要由以下4个部分组成:规则引擎本身Rule Engine ,复杂事件处理模块Drools Fusion ,工作流模块Dr ools Flow ,业务规则管理系统模块Drools Guv nor [3]

。规则引擎模块是Dro ols 的核心部分,通过它来处理基本的业务规则,该模块贯穿于整个Droo ls 业务逻辑平台。通常情况下规则操作的大部分都是静态的事实数据集合。但是对

于某些系统,它需要定义随着时间变化而变化的事实,基本的规则引擎无法高效处理这种情况,必须由复杂事件处理模块来处理。复杂事件处理模块也称为事件流处理模块。它是以事件驱动的架构方式来处理业务规则的。工作流模块很容易将业务逻辑以图形的方式展现,十分直观,便于业务逻辑的理解。工作流模块能够相对高效地来处理复杂业务逻辑。业务规则管理系统模块,有利于编写高效的规则,有效地管理规则和调试规则编得的是否正确。通过规则管理系统可以编写基于规则的单元测试、规则的集成测试、规则的接受度测试、并能创建测试脚本。另外还有一个很重要的部分,即解析器模块和关于Droo ls 的Eclipse 插件的模块,并具有语法错误检查和自动编译以及其他的辅助性的作用,方便规则高效编写与开发。Drools 还提供了一个可选的模块Drools Solv er 。它是建立于Drools 规则引擎之上的搜索算法用来解决计划任务。1.2 Drools 规则引擎核心算法

Dro ols 规则引擎采用Rete00[4]算法通过推理来进行事实和模式间的匹配。Rete00算法是一种改进了的Rete [5]算法。由于Rete 算法是以空间来换取时间,大大提高了事实和模式间匹配的效率,因此它广泛应用于专家系统和规则引擎中。Rete 00加入了面向对象的概念,它是通过节点共享,以空间换取时间来提高匹配的效率。该算法的推理过程如下所示:

将初始事实存入Wor k M em ory 。

将事实与类型节点进行比较,如果匹配,则执行 ,否则不匹配。

将事实与Alpha 节点进行比较,如果匹配,则执行 ,否则不匹配。

将事实与Beta 节点,即连接节点进行比较,如果匹配,则执行 ,否则不匹配。

匹配完成,进入终止节点。 将与规则匹配的规则放入Ag enda 。

使用规则引擎执行Agenda 里的规则。重复 ~ ,直到所有Agenda 中的规则都执行完毕。

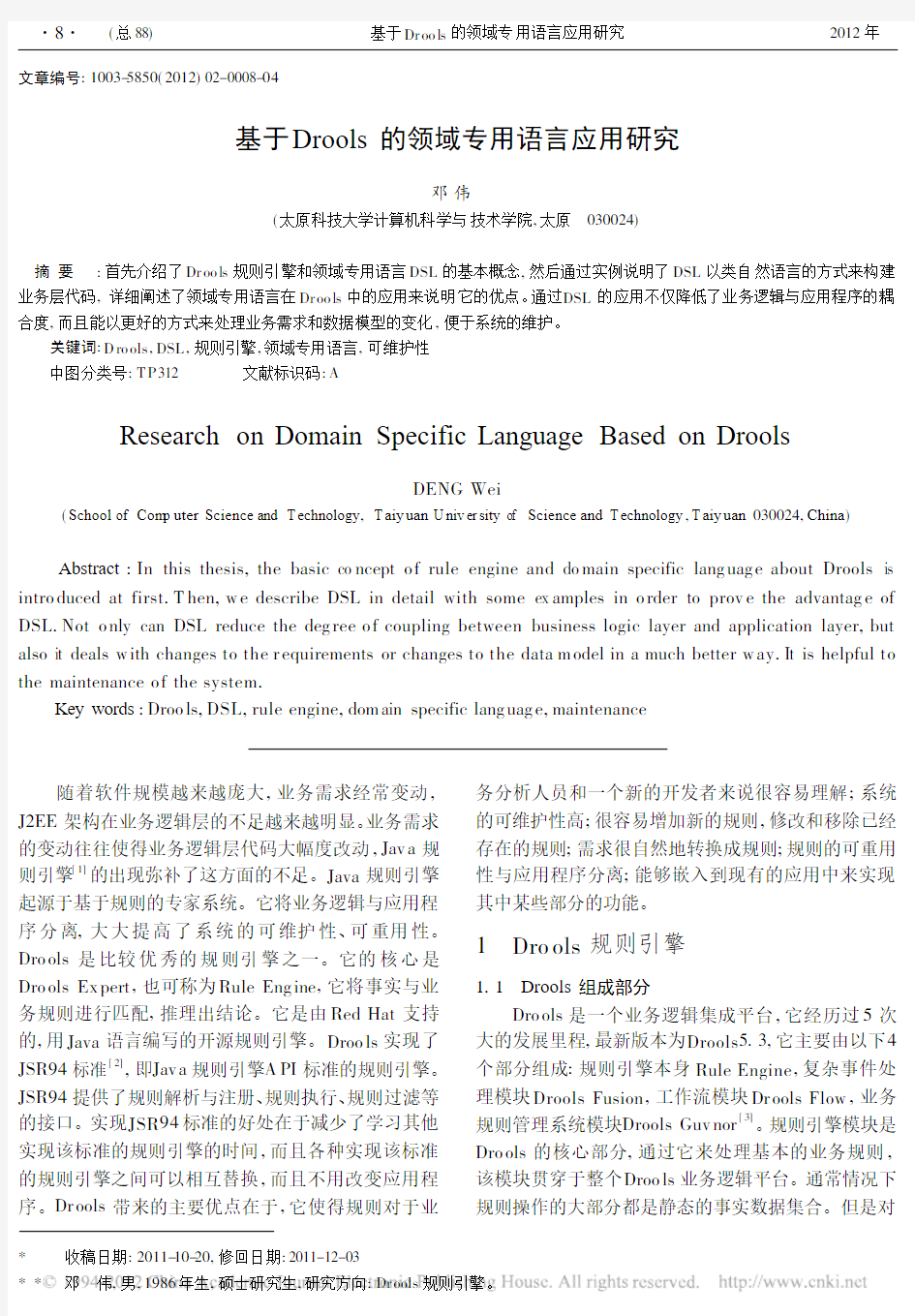

该算法会从规则的条件部分产生一个网络。当规则包加入到规则库中,网络就产生了。图1显示了一个比较简单的Rete 网络。

图1中的Rete 网络将产生两个匹配模式。最左侧部分无连接节点,只要alpha 节点满足匹配,则匹配成功。右侧部分由连接节点将左右两部分相连接。可以看到这两个模式在图中交叉的部分即产生了节点共

享。节点共享的好处在于它大大减少了内存的占用。

图1 R ete 网络

2 DSL 在Drools 中的应用

2.1 领域专用语言DSL 简介

目前业务规则的实现大部分是由开发人员来实现的。通常情况下,技术人员需要不断地将业务领域中的概念转换成相应的代码模型,然后再进行修改,这种间接性造成了计算机的程序不太可能做到与业务领域中的概念完全一致。有时候,这些业务规则需要业务分析人员能够阅读和理解,因此业务规则的可读性和用户的友好性是规则引擎的一个重要的方面。DSL [6](Do main Specific Languag e)的主要目的就是以贴近业务领域的方式,即以类自然语言[7]的方式来构造软件。DSL 的简洁性往往是思维上的简洁性,使得我们不用花费太多精力就能看懂代码所对应的业务含义。J2EE 中的DAO 、POJO 、DT O 、Action 等对于开发者已经很清晰,但是DSL 更加注重强调使用业务词汇,使得业务人员也能够通过DSL 来理解和修改业务代码。DSL 相当于是一个转换器,它能够将业务领域的语言转换成规则语言,提供给规则引擎使用。2.2 DSL 在Drools 中的应用

Dro ols [8]

中规则通常存放在dr l 规则文件中,通过

对规则的解析来实现应用程序与业务逻辑的分离。结合一个小实例来说明DSL 在Drools 中的应用来充分说明DSL 的优势。例如,对于这样的业务需求:如果两个用户的电话号码相同,则视该用户为同一个用户,删除其中一个用户,并显示一条警告信息。用户在Java 中用U ser 类表示,并重写equals 方法,判断电话号码相同则两个对象相同。对于上述业务需求可以表示成如下规则:

r ule “t wo EqualPhoneN umber ”w hen

$U ser 1:U ser (phoneN umber1!=null)$U ser 2:U ser (phoneN umber 1!=null ,eval($U ser1!=$U ser 2),t his==$U ser1)then

System.out.pr intln("the sam e");r etract ($U ser 2);

validationRepor t .a ddM essa ge

(repor tF act or y .cr eateM essag e (M essage .T ype .WA RN IN G ,kcontex t .g etRule ().g etN ame (),$U ser 2));

end

上述规则对于专业人员都得花费一定的时间来理解语句的意思,而对于非专业人士则上述规则的描述更是晦涩难懂,他们甚至不明白这些语句所要表达的意思。DSL 的出现使得业务领域的术语能够转换成规则语言来进行表达。在Dr ools 中DSL 相当于一个转换器,它能将某一领域内的术语转换成规则语言,转换的过程定义在DSL 中,而这些业务领域内的术语则存放在dslr 中。只要DSL 文件中对应于dslr 文件中的转换映射部分不存在问题,那么在Drools 中,dslr 文件通过DSL 转换之后的结果是一个符合语法的DRL 文件,这种转换相当于实现了类自然语言到规则语言的转换。对于上述DRL 文件中规则表达的意思,可以写在dslr 文件中,如下所示:

ex pander userV alidatio n.dsl r ule "t wo EqualPhoneN umber "w hen

T he U ser -1ha s an phoneN umber 1T he U ser -2ha s an phoneN umber 1-same phoneN umber as U ser -1then

r emov e the U ser-2

Display W AR N IN G fo r the U ser -2end

从上述dslr 文件中,能够快速辨认出它所表达的意思。通过DSL 可以将业务规则以类自然语言的方式来表达,这样有利于更好地理解业务规则。仅仅有上述的dslr 还不能实现业务规则与规则引擎中的规则进行转换,而必须通过DSL 文件将dslr 文件进行正确的映射,才能够在Dr ools 中使用。

DSL 文件如下:

[co ndit ion][]T he{o bject}-{id}={object }-{id}

[co ndit ion][]{object }-{id}has an {field}=${o bject }{id}:{object}({field}!=null)

[co ndit ion][]-same phoneN umber as {o bject}-{id}=this ==${o bject}{id},eval(${object }1!=${object }2)

[co nsequence][]the {object }-{id}={object}-{id}[co nsequence ][]Display {message t ype

enum }for

{object

}-{

id }

=

validatio nRepor t .addM essag e

(r epor tFacto ry .cr eateM essage (M essage .T y pe .{message type enum},kco ntex t.g etRule().g etN ame(),${object}{id}));

[co nsequence ][]remo ve {o bject }-{id }=r etra ct (${o bject }{id });

通过上述的dslr 和DSL 文件,就能够产生DRL 文件。产生的DRL 规则文件是比较特殊的,它是不能直接更改的,这是因为dslr 文件转换成Dr ools 中的基本规则这一过程是在内存中进行的,并不真正产生DRL 文件。要想改变规则的话只需要改变dslr 和对应的DSL 中的映射部分就行了。DSL 文件的编写既可以用eclipse 插件来编写,也可以用一般的文本编辑器来编写。通过Drools 在Eclipse 中的插件DRL View er ,可以查看转换前业务领域的术语和转换后的规则描述是否正确地对应。此外,DRL Viewer 还可以检查编写DSL 是否正确,定位出错误出现的地方,方便修改业务规则。

3 DSL 在Drools 中的转换

3.1 业务需求转换流程

在Dro ols 中将业务术语转换成为规则语言是通过DSL 接口。图2是在Dro ols 中将业务需求转换成能

够处理的规则语句的转换流程图。

业务分析人员或领域专家将业务领域中的概念转换成领域专用语言存放于dslr 文件中,该语言是一种类自然语言。业务领域中的概念转换到类自然语言中,这种过渡是很平缓的。DSL 能够将领域专用语言转换成规则语言,从而实现了业务需求到业务规则的转换。在不改变规则的前提下,可以改变领域专用语言,使得它更加友好和便于业务的理解。3.2 DSL 规则映射与加载

DSL 文件的一般格式为:

[

Scope 的取值有以下几个:

Conditio n :指定映射被用于条件部分;co nsequence:指定映射被用于结果部分;*:指定映射可用于以上两部分;

Key w ord :指定可以应用于整个文件。

对于多个条件ObjectT ype(条件1,条件2,条件3,…,条件n )的映射文件可处理为:

[conditio n ][]对于ObjectType 的描述=

$o bjectT ype:ObjectTy pe()

[conditio n][]-has条件1到n的自然语言描述+需要映射的字段=条件1到n 与映射字段进行比较。

图3中显示了DSL

在Drools中的加载。在

Dro ols中,从本质上来

讲是Know legeBuilder

这个类来实现领域专用

语言和规则语言之间的

转换的。Drools中加载

规则文件不同于加载属

性文件,也不同于一般

的文件读取,它内部封

装了对规则文件读取的方法。规则通过Kno w ledgeBuilder来产生规则包,然后将它们加入到知识库Kno wledgeBase中,提供给规则引擎来使用。

DSL加载到知识库中的部分源码如下:

K no w ledgeBuilder builder= K no w ledgeBuilder Facto ry.new Know ledg eBuilder();

builder.add(Reso ur ceFacto ry.new ClassPathR eso urce (“dsl文件”,Reso ur ceT y pe.DSL);

builder.add(Resour ceT ype.new ClassPat hR esource(“dslr 文件”,Resour ceT ype.D SLR);

K no w ledgeBase kno w ledgeBase= K no w ledgeBaseFacto ry.new Ko nw ledg eBase();

know ledgeBase.addK now ledg ePackag es

(builder.g etK now ledgeP ackages());

4 DSL与决策表和规则流的比较业务规则除了可以用DSL的方式表示来减小软件系统的可维护性,还可以利用决策表和规则流的方式进行。决策表通常将规则存放在excel文件或.cvs文件中,因此规则的表达很直观,它也能将业务逻辑同应用分离。决策表中的规则只是形式上与基本的规则文件drl中的规则描述略有不同,两者之间很容易相互转换。决策表的优点在于它表达直观,规则容易阅读和理解;很容易更改一组相关的规则来快速重构系统;它能够减少因遗漏输入规则而引发的错误。决策表的不足在于它将一条规则存放在ex cel或cv s中的一行中,不易利用Dro ols集成平台来编写和调试规则;将DRL规则存入决策表中不容易复用规则;以决策表的方式管理规则也比较困难。规则流是另外一种便于阅读和理解的方式来构造规则。它构造规则的方式明显不同于DSL和决策表。规则流是在复杂的规则之间定义执行流的方式来构造业务规则。复杂的业务处理需要做出复杂的决策,应用DSL和决策表来解决这种复杂的决策是不切实际的。规则流是专门针对复杂业务决策而设计的,旨在解决复杂的业务逻辑。规则流虽然可以将很复杂的规则清晰地表示出来但是它除了处理复杂的业务规则,由于本身的复杂性还得做很多额外的操作。应用规则流的另外一个缺点在于,如果业务规则同时存在于规则流和drl基本规则文件中,如果想完全理解业务规则,得反复比对规则流和drl基本规则文件。Dro ols没有在基本规则文件和规则流之间建立相应的关系。

5 结束语

对Dro ols这一优秀开源规则引擎的原理和构成作了简单介绍,并通过实例着重对其中的DSL进行了解析。实例虽小,却能体现出DSL所表现出来的好处。通过DSL不仅使得业务逻辑的实现可以更加接近于自然语言,而且大大提高了系统的可维护性。它不仅帮助开发人员在开发企业应用服务过程更加明确业务规则,并且使得这些业务规则具有更强的描述性。业务分析人员经过简单的培训也能够写出符合标准的DSL。虽然目前规则引擎和DSL在大型企业中的应用还并不广泛,但是对于它的研究已经比较成熟。对于经常变动的商业业务规则,应用规则引擎技术有着明显的优势。随着规则引擎和DSL的不断成熟,它们的应用范围也将随之扩展,成为解决大型企业中复杂业务的优秀技术之一。

参考文献:

[1]刘 伟.Jav a规则引擎-Dr oo ls的介绍及应用[J].微计

算机应用,2005,26(6):717-721.

[2]尤俊欣,饶若楠,詹晓峰.基于规则引擎的Web框架

[J].计算机应用与软件,2007,24(2):4-5.

[3]Paul Bro wne.JBoss D ro ols Business Rules[M].

N ewy or k:P ublished by Packt Publishing L td,2009. [4]庞伟正,金瑞琪,王成武.一种规则引擎的实现方法

[J].哈尔滨工程大学学报,2005,26(3):385-389.

[5]Charles L F or g y.Rete:A Fast A lg or ithm for t he

M any Pat tern/M any Object P atter n M atch Pr oblem

[J].A rt ificial Intelligence,1982,19(1):17-37.

[6]陈玲丽.DSL在软件系统中的运用和实践[J].信息与

电脑,2011(4):57-58.

[7]刘局瑞,陈颖图,冯 萍,等.基于类自然语言的图形化

工作流规则引擎[J].微电子学与计算机,2004,21

(10):144-146.

[8]郭 芳,白建军.基于Rete算法的规则引擎

JBo ssR ules[J].计算机时代,2008(1):8-10.

硬件描述语言语言设计实例 1、8-3编码器 module encode_verilog ( a ,b ); input [7:0] a ; //编码器输入 wire [7:0] a ; output [2:0] b ; //编码器输出 reg [2:0] b; always @ ( a ) begin case ( a ) //编码器某一输入端口为高电平输出相应的3位二进制数 8'b0000_0001 : b<=3'b000; //0 8'b0000_0010 : b<=3'b001; //1 8'b0000_0100 : b<=3'b010; //2 8'b0000_1000 : b<=3'b011; //3 8'b0001_0000 : b<=3'b100; //4 8'b0010_0000 : b<=3'b101; //5 8'b0100_0000 : b<=3'b110; //6 8'b1000_0000 : b<=3'b111; //7 default : b<= 3'b000; //其他情况编码器输出3’b000 endcase end endmodule 2、8-3优先编码器 module p_encode_verilog ( A ,I ,GS ,EO ,EI ); //编码器以低为有效 input [7:0] I ; //编码器输入 wire [7:0] I ; input EI ; //输入使能,EI=0时,编码器正常工作 wire EI ; output [2:0] A ; //编码器输出 reg [2:0] A ; output GS ; //优先编码器工作状态标志,编码器的八个输入端有信号输入时,GS=0 reg GS ; output EO ; //输出使能, reg EO ; always @ ( I or EI ) if ( EI ) //使用if、else if表明条件的优先级顺序 begin A <= 3'b111; GS <= 1; EO <= 1; end else if ( I[7] == 0 ) begin A <= 3'b000;

双端口RAM在高速数据采集中的应用 利用传统方法设计的高速数据采集系统由于集成度低、电路复杂,高速运行电路干扰大,电路可靠性低,难以满足高速数据采集工作的要求。应用FPGA可以把数据采集电路中的数据缓存、控制时序逻辑、地址译码、总线接口等电路全部集成进一片芯片中,高集成性增强了系统的稳定性,为高速数据采集提供了理想的解决方案。下面以一个高速数据采集系统为例介绍双端口RAM的应用。 该系统要求实现对频率为5MHz的信号进行采样,系统的计算处理需要对信号进行波形分析,信号采样时间为25μs。根据设计要求,为保证采样波形不失真,A/D采样频率用80MHz,采样精度为8位数据宽度。计算得出存储容量需要2K字节。其系统结构框图如图3所示,图4给出了具体电路连接图。

根据设计要求,双端口RAM的LPM_WIDTH参数设置为8,LPM_WIDTHAD 参数设置为11(211=2048),使用读写使能端及读写时钟。ADCLK、WRCLK和地址发生器的计数频率为80MHz。 A/D转换值对双端口RAM的写时序为顺序写方式,每完成一次A/D转换,存储一次数据,地址加1指向下一单元,因此写地址发生器(RAM_CONTROL)采用递增计数器实现,计数频率与ADCLK、WRCLK一致以保证数据写入时序的正确性。写操作时序由地址和时钟发生器、A/D转换时钟和双端口RAM的写时钟产生。停止采样时AD_STOP有效,写地址发生器停止计数,同时停止对RAM的写操作。将地址发生器的计数值接至DSP总线可以获取采样的首尾指针。地址发生器单元一般用(VHDL)语言编程实现,然后生成符号文件 RAM_CONTROL在上层文件调用。其部分VHDL语言程序如下: 对双端口RAM的读操作采用存储器映像方式,其读出端口接DSP的外扩RAM 总线,DSP可随机读取双端口RAM的任一单元数据,以方便波形分析。由于

软件设计说明

目录 1范围 (1) 1.1标识 (1) 1.2系统概述 (1) 1.3文档概述 (1) 2引用文档 (1) 3CSCI 级设计决策 (1) 4CSCI 体系结构设计 (2) 4.1CSCI部件 (2) 4.2执行方案 (3) 4.3接口设计 (3) 4.3.1接口标识和接口图 (3) 4.3.x (接口的项目唯一标识符) (4) 5CSCI 详细设计 (6) 5.X (软件单元的项目唯一标识符,或者一组软件单元的标志符) (6) 6需求可追踪性 (9) 7注解 (11) 附录A (11)

软件设计说明 1范围 1.1标识 要求:本节应包含这个文档所适用的系统和软件的完全标识,(若适用)应包括标识号、名称、缩略名、版本号及发布号。 1.2系统概述 要求: 1)本节主要描述本文档适用的系统和软件的用途; 2)概述系统开发、运行和维护的历史; 3)标识项目的投资方、需方、用户、开发方和保障机构; 4)标识当前和计划的运行现场; 5)列出其它有关文档。 1.3文档概述 本节应概述本文档的用途和内容,描述与它的使用有关的保密性或私密性考虑。 2引用文档 列出引用的所有文档,包括文档的编号、标题、修订版本和日期。 3CSCI 级设计决策 要求:本章应根据需要分节给出CSCI 级设计决策,即CSCI 行为设计的决策(忽略其内部实现,从用户角度出发描述系统将怎样运转以满足需求)和其它影响组成该CSCI 的软件单元的选择与设计的决策。如果在需求中所有这些决策是明确的,或者这些决策要推迟到CSCI 的软件单元的设计时指出,则本章应如实陈述。 针对关键性需求(例如对安全性、保密性、私密性等需求)作出的设计决策,应在专门的章节中加以叙述。 CSCI 级设计决策的例子如下: 1)关于CSCI 将接收的输入和将产生的输出的设计决策,包括与其它系统、HWCI、CSCI 和用户的接口(本文档的4.3.x 节指出本说明要考虑的主题); 2)有关响应每个输入或条件的CSCI 行为的设计决策,包括CSCI 要执行的动作、响应时间和其它性能特性,模型化的物理系统的说明,选定的方程式/算法/规则,以及对不允许的输入或条件进行的处理; 3)有关数据库/数据文件如何呈现给用户的设计决策(本文档的4.3.x 节标识了本说明

目录 1、双向电路的基本格式 (2) 2、控制条件 (3) 2.1、双向信号作一个信号的输入,作另一信号的输出 (3) 2.2、双向信号既做输出又做输出 (4) 3、实例说明-INOUT端口仿真暨三态门仿真 (6) 3.1、三态门的原理与仿真三态总线 (6) 3.3、VHDL 的三态门实现与仿真 (7) 参考文献 (12)

VHDL语言程序设计中INOUT端口的使用与实例分析 摘要:VHDL是由美国国防部为描述电子电路所开发的一种语言,其全称为(Very High Speed Integrated Circuit) Hardware Description Language。与另外一门硬件描述语言Verilog HDL相比,VHDL 更善于描述高层的一些设计,包括系统级(算法、数据通路、控制)和行为级(寄存器传输级),而且VHDL 具有设计重用、大型设计能力、可读性强、易于编译等优点逐渐受到硬件设计者的青睐。但是,VHDL是一门语法相当严格的语言,易学性差,特别是对于刚开始接触VHDL的设计者而言,经常会因某些小细节处理不当导致综合无法通过。VHDL共定义了5种类型的端口,分别是In, Out,Inout, Buffer及Linkage,实际设计时只会用到前四种。本文主要讨论讨论如何正确使用INOUT端口。 关键词:VHDL;INOUT端口;三态门原理 1、双向电路的基本格式 工程应用中,双向电路是设计者不得不面对的问题.在实际应用中,数据总线往往是双向的.如何正确处理数据总线是进行时序逻辑电路设计的基础.在程序设计过程中,关键技术在于:实体部分必须对端口属性进行申明,端口属性必须为inout类型,在构造体需要对输出信号进行有条件的高阻控制.在双向电路的处理问题上,常用的处理方式有两种,在介绍双向电路的处理方式之前,先看看双向电路的基本格式: ENTITY bidir_pin IS ( bidir : INOUT std_logic; oe, clk, from_core : IN std_logic; to_core : OUT std_logic; …… END bidir_pin; ARCHITECTURE behavior OF bidir_pin IS BEGIN

Verilog HDL Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象 设计层次的数字系统建模。被建模的数字系统对象的复杂性可以介于简单的门和完整的电子数字系统之间。数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。 Verilog HDL 语言具有下述描述能力:设计的行为特性、设计的数据流特性、设计的结构组成以及包含响应监控和设计验证方面的时延和波形产生机制。所有这些都使用同一种建模语言。此外,Verilog HDL语言提供了编程语言接口,通过该接口可以在模拟、验证期间从设计外部访问设计,包括模拟的具体控制和运行。 Verilog HDL语言不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。因此,用这种语言编写的模型能够使用Verilog仿真器进行验证。语言从C编程语言中继承了多种操作符和结构。Verilog HDL提供了扩展的建模能力,其中许多扩展最初很难理解。但是,Verilog HDL语言的核心子集非常易于学习和使用,这对大多数建模应用来说已经足够。当然,完整的硬件描述语言足以对从最复杂的芯片到完整的电子系统进行描述。 =============================== 中文版Verilog HDL简明教程:第1章简介 Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。被建模的数字系统对象的复杂性可以介于简单的门和完整的电子数字系统之间。数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。 Verilog HDL 语言具有下述描述能力:设计的行为特性、设计的数据流特性、设计的结构组成以及包含响应监控和设计验证方面的时延和波形产生机制。所有这些都使用同一种建模语言。此外,Verilog HDL语言提供了编程语言接口,通过该接口可以在模拟、验证期间从设计外部访问设计,包括模拟的具体控制和运行。 Verilog HDL语言不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。因此,用这种语言编写的模型能够使用Verilog仿真器进行验证。语言从C编程语言中继承了多种操作符和结构。Verilog HDL提供了扩展的建模能力,其中许多扩展最初很难理解。但是,Verilog HDL语言的核心子集非常易于学习和使用,这对大多数建模应用来说已经足够。当然,完整的硬件描述语言足以对从最复杂的芯片到完整的电子系统进行描述。 历史 Verilog HDL语言最初是于1983年由Gateway Design Automation公司为其模

MicroBlaze相关 by coosign 2005年12月 https://www.doczj.com/doc/bb1215127.html,/ 一、嵌入式相关知识 略 二、MicroBlaze的优势 MicroBlaze软内核是一种针对Xilinx FPGA器件而优化的功能强大的标准32位RISC 处理器。采用传统的单处理器方法进行的基础设计配合Virtex-II Pro FPGA在 150 MHz的时钟频率下,性能达到125 Dhrystone MIPS (DMIPS),如果与Spartan-3 FPGA配合,在85 MHz 的时钟频率下,性能达到68 Dhrystone MIPS (DMIPS)。为了达到更高的性能,在Virtex-II系列平台FPGA中植入32位PowerPCTM内核,它的DMIPS性能是竞争软处理器内核的五倍多。在Virtex-II Pro FPGA中实现的32位PowerPC内核,在时钟频率为450 MHz 时的性能超过680 DMIPS。总体性能如此之高,但成本却很低,这是因为集成在Virtex-II FPGA中的处理器既简化了设计,占用的片芯面积也减小了。例如,一个高效的设计仅使用了Xilinx 2VP50器件中不到2%的芯片面积。 1、用户可以根据不同的需要灵活地定制系统特性和外设 2、提升系统性能 3、降低成本 4、加快产品的上市时间 如图,使用了嵌入式CPU内核,把一些外设集成到单片FPGA中,可以减小系统复杂性,降低功耗和成本。 传统的系统框架图 SOPC框架图

个人使用体会:使用CPU软核做一些控制还是非常方便的,而且Xilinx提供了强大的模块支持,如GPIO、TIMER、UART、EMC等等。用于实现参数可变的数字滤波器也比较方便。 BUG:上次参加Xilinx的一次培训,工程师说引入CPU会给系统带来不稳定,程序容易跑飞,在极端环境下(如高温),容易死机。 三、EDK软件开发环境 Xilinx软件开发环境功能强大,而且非常容易上手。集成开发环境如下: ISE 7.1 EDK 7.1 3.1 EDK安装目录介绍 服务器上的EDK开发工具安装包:edk_71i_pc.bin,这个光盘映象文件里有安装文件和SP2的升级程序。建议大家打上SP2的补丁。 EDK安装后,安装目录树如下: 其中比较重要的子目录是doc和sw。 doc目录下放了大量的文档资料,具有重大参考价值。如: edk_getstarted.pdf Getting Started with Xilinx? EDK ps_ug.pdf Platform Studio User Guide oslib_rm.pdf OS and Libraries Document Collection iss_ug.pdf Instruction Set Simulator User’s Guide mb_ref_guide.pdf MicroBlaze Processor Reference Guide psf_rm.pdf Platform Specification Format Reference Manual 其中比较重要的是ps_ug.pdf。 sw目录下放置的是Drivers, BSP’s and software services。对于我们编写C代码来说,是非常重要的参考资料。

Quartus II 实践作业 通过一个简单的实例介绍Quartus II 9.1基本使用方法。 Introduction 典型的计算机辅助设计流程 开始——新建一个项目(project)——逻辑原理图设计输入——编译设计——管脚分配——仿真设计电路——规划、配置FPGA器件——测试设计的电路 一个典型的FPGA计算机辅助设计流程如图1所示。 图1 FPGA CAD设计流程

设计流程的步骤: ?设计输入(Design Entry)-- 用原理图或者硬件描述语言说明设计的电路。 ?综合(Synthesis)-- 将输入的设计综合成由FPGA芯片的逻辑元件(logic elements)组成的电路。 ?功能仿真(Functional Simulation)-- 测试、验证综合的电路功能正确与否,不考虑延时。 ?适配(Fitting)-- 将工程的逻辑和时序要求与器件的可用资源相匹配。它将每个逻辑功能分配给最佳逻辑单元位置,进行布线和时序分析,并选定相应的互连路径和引脚分配。 ?时序分析(Timing Analysis)-- 通过对适配电路的传播延迟的分析,提供电路的性能指标。 ?时序仿真(Timing Simulation)-- 验证电路的功能和时序的正确性。 ?编程和下载配置(Programming and Configuration)-- 在FPGA上实现设计的电路。 本文主要介绍Quartus II 的基本特性。演示如何用逻辑原理图在Quartus II平台设计和实现电路。包括: ?创建一个项目(project) ?用逻辑原理图设计输入 ?综合 ?适配 ?分配管脚 ?仿真 ?编程与下载 1 创建一个项目 (1)启动Quartus II ,选择File > New Project Wizard,弹出窗口(图2)

【最新整理,下载后即可编辑】 Quartus Ⅱ入门教程 (一个Verilog 程序的编译和功能仿真) Quartus Ⅱ 是Altera 公司推出的专业EDA 工具,支持原理图输入、硬件描述语言的输入等多种输入方式。硬件描述语言的输入方式是利用类似高级程序的设计方法来设计出数字系统。接下来我们对这种智能的EDA 工具进行初步的学习。使大家以后的 数字系统设计更加容易上手。 第一步:打开软件 ● 快捷工具栏:提供设置(setting ),编译(compile )等快捷方式,方便用户使用,用户也可以在菜单栏的下拉菜单找到相应的选项。 ● 菜单栏:软件所有功能的控制选项都可以在其下拉菜单中找到。 ● 信息栏:编译或者综合整个过程的详细信息显示窗口,包括编译通过信息和报错信息。 快捷工具栏 菜单栏 工作区 资源管理窗口 任务管理窗口

第二步:新建工程(file>new Project Wizard ) 1 工程名称: 2添加已有文件(没有已有文件的直接跳过next ) 所建工程的保存路径 工程名称 顶层模块名(芯片级设计为实体名),要求与工程名称相同 如果有已经存在的文件就在该过程中添加,软件将直接将用户所添加的文件添加到工程中。

3 选择芯片型号(我们选择MAX3000A系列下的 EPM3256AQC208-10芯片) (注:如果不下载到开发板上进行测试,这一步可以不用设置) 所选的芯片 的系列型号 快速搜索所需的芯片 选择芯片

4 选择仿真,综合工具(第一次实验全部利用quartus做,三项都选None,然后next) 5 工程建立完成(点finish) 选择第三方综合工具,如果使用Quartus内部综合工具则选择none 选择第三方仿真工具,如果使用Quartus内部仿真工具则选择none 选择时序分析仪

Verilog语言描述常见电路结构范例 组合逻辑 常见的组合逻辑有:算术逻辑部件、多路选择器、编码器、优先编码器、译码器和比较器等。 逻辑结构控制 使用括号可以改变组合逻辑的结构。虽然EDA工具可以对组合逻辑设计进行重新优化组合,但在Verilog 描述中使用括号可以降低EDA工具的压力,并且减少工具的综合时间。 在下面的例子中,虽然y2和y1的功能是一样的,但y1会使用三级加法器,使用括号的y2只使用二级加法器。 always @ (a1 or a2 or b1 or b2 or c1 or c2 or d1 or d2) begin y1 = a1 + b1 + c1 + d1; y2 = (a2 + b2) + (c2 + d2); end 二选一多路选择器 下面给出了三种描述2:1 MUX 的方法。y1是通过条件赋值语句实现的,y2和y3都是通过if语句实现的。 wire y1 = sel1? a1: b1; always @ (a2 or a3 or b2 or b3 or sel2 or sel3) begin y2 = b2; if (sel2) y2 = a2; if (sel3) y3 = a3; else y3 = b3; end 四选一多路选择器 用Verilog描述4:1 MUX 可以有如下方法: 一个if语句加多个else if从句 嵌套if 语句 case 语句 always @ (a or b or c or d or sel) begin if (sel == 2'b00) y = a; else if (sel == 2'b01) y = b; else if (sel == 2'b10) y = c; else y = d; end always @ (a or b or c or d or sel) begin

硬件描述语言范例

硬件描述语言语言设计实例 1、8-3编码器 module encode_verilog ( a ,b ); input [7:0] a ; //编码器输入 wire [7:0] a ; output [2:0] b ; //编码器输出 reg [2:0] b; always @ ( a ) begin case ( a ) //编码器某一输入端口为高电平输出相应的3位二进制数 8'b0000_0001 : b<=3'b000; //0 8'b0000_0010 : b<=3'b001; //1 8'b0000_0100 : b<=3'b010; //2 8'b0000_1000 : b<=3'b011; //3 8'b0001_0000 : b<=3'b100; //4 8'b0010_0000 : b<=3'b101; //5 8'b0100_0000 : b<=3'b110; //6 8'b1000_0000 : b<=3'b111; //7 default : b<= 3'b000; //其他情况编码器输出3’b000 endcase end

endmodule 2、8-3优先编码器 module p_encode_verilog ( A ,I ,GS ,EO ,EI ); //编码器以低为有效 input [7:0] I ; //编码器输入 wire [7:0] I ; input EI ; //输入使能,EI=0时,编码器正常工作 wire EI ; output [2:0] A ; //编码器输出 reg [2:0] A ; output GS ; //优先编码器工作状态标志,编码器的八个输入端有信号输入时,GS=0 reg GS ; output EO ; //输出使能, reg EO ; always @ ( I or EI ) if ( EI ) //使用if、else if表明条件的优先级顺序 begin A <= 3'b111; GS <= 1; EO <= 1;