October 1987

Revised January 1999

CD4069UBC Inverter Circuits ? 1999 Fairchild Semiconductor Corporation DS005975.prf https://www.doczj.com/doc/a518550187.html, CD4069UBC

Inverter Circuits

General Description

The CD4069UB consists of six inverter circuits and is man-

ufactured using complementary MOS (CMOS) to achieve

wide power supply operating range, low power consump-

tion, high noise immunity, and symmetric controlled rise

and fall times.

This device is intended for all general purpose inverter

applications where the special characteristics of the

MM74C901, MM74C907, and CD4049A Hex Inverter/Buff-

ers are not required. In those applications requiring larger

noise immunity the MM74C14 or MM74C914 Hex Schmitt

T rigger is suggested.

All inputs are protected from damage due to static dis-

charge by diode clamps to V DD and V SS.

Features

s Wide supply voltage range: 3.0V to 15V

s High noise immunity:0.45 V DD typ.

s Low power TTL compatibility:Fan out of 2 driving 74L

or 1 driving 74LS

s Equivalent to MM74C04

Ordering Code:

Device also available in Tape and Reel. Specify by appending suffix “X” to the ordering code.

Connection Diagram

Pin Assignments for SOIC and DIP

Schematic Diagram

Order Number Package Number Package Description

CD4069UBCM M14A14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150” Narrow Body

CD4069UBCSJ M14D14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

CD4069UBCN N14A14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide

https://www.doczj.com/doc/a518550187.html, 2

C D 4069U B C

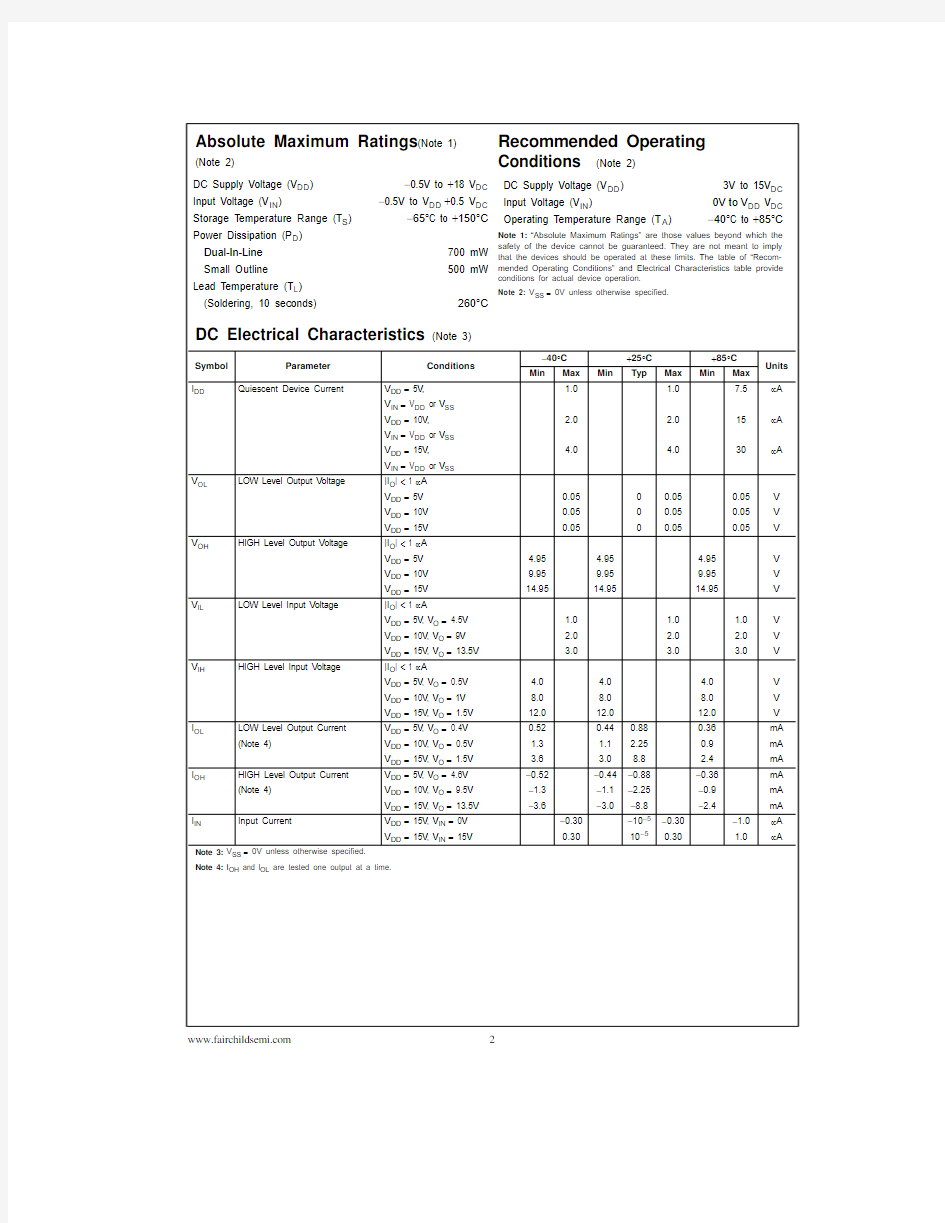

Absolute Maximum Ratings (Note 1)

(Note 2)

Recommended Operating Conditions (Note 2)

Note 1: “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The table of “Recom-mended Operating Conditions” and Electrical Characteristics table provide conditions for actual device operation.Note 2: V SS = 0V unless otherwise specified.

DC Electrical Characteristics (Note 3)

Note 3: V SS = 0V unless otherwise specified.Note 4: I OH and I OL are tested one output at a time.

DC Supply Voltage (V DD )?0.5V to +18 V DC

Input Voltage (V IN )

?0.5V to V DD +0.5 V DC

Storage T emperature Range (T S )?65°C to +150°C

Power Dissipation (P D )Dual-In-Line 700 mW Small Outline 500 mW

Lead T emperature (T L )(Soldering, 10 seconds)

260°C DC Supply Voltage (V DD )3V to 15V DC Input Voltage (V IN )

0V to

V DD V DC Operating Temperature Range (T A )

?40°C to +85°C

Symbol Parameter

Conditions

?40°C +25°C +85°C Units Min

Max Min

Typ

Max Min

Max I DD

Quiescent Device Current

V DD = 5V , 1.0 1.07.5μA V IN = V DD or V SS V DD = 10V , 2.0 2.015μA V IN = V DD or V SS V DD = 15V , 4.0

4.0

30

μA

V IN = V DD or V SS

V OL

LOW Level Output Voltage

|I O | < 1 μA V DD = 5V 0.0500.050.05V V DD = 10V 0.0500.050.05V V DD = 15V

0.05

0.05

0.05

V V OH

HIGH Level Output Voltage

|I O | < 1 μA V DD = 5V 4.95 4.95 4.95V V DD = 10V 9.959.959.95V V DD = 15V

14.95

14.95

14.95

V

V IL

LOW Level Input Voltage

|I O | < 1 μA

V DD = 5V , V O = 4.5V 1.0 1.0 1.0V V DD = 10V , V O = 9V 2.0 2.0

2.0

V V DD = 15V , V O = 13.5V

3.0

3.0

3.0

V V IH

HIGH Level Input Voltage

|I O | < 1 μA

V DD = 5V , V O = 0.5V 4.0 4.0 4.0V V DD = 10V , V O = 1V 8.08.08.0V V DD = 15V , V O = 1.5V

12.012.012.0

V I OL

LOW Level Output Current V DD = 5V , V O = 0.4V 0.520.440.880.36mA (Note 4)

V DD = 10V , V O = 0.5V 1.3 1.1 2.250.9mA V DD = 15V , V O = 1.5V 3.6 3.08.8 2.4mA I OH

HIGH Level Output Current V DD = 5V , V O = 4.6V ?0.52?0.44?0.88?0.36mA (Note 4)

V DD = 10V , V O = 9.5V ?1.3?1.1?2.25?0.9mA V DD = 15V , V O = 13.5V ?3.6

?3.0?8.8?2.4

mA

I IN

Input Current

V DD = 15V , V IN = 0V ?0.30?10?5?0.30?1.0μA V DD = 15V , V IN = 15V

0.30

10?5

0.30

1.0

μA

https://www.doczj.com/doc/a518550187.html,

CD4069UBC

AC Electrical Characteristics (Note 5)

T A = 25°C, C L = 50 pF , R L = 200 k ?, t r and t f ≤ 20 ns, unless otherwise specified

Note 5: AC Parameters are guaranteed by DC correlated testing.

Note 6: C PD determines the no load AC power consumption of any CMOS device. For complete explanation, see Family Characteristics applicatio n note—AN-90.

AC Test Circuits and Switching Time Waveforms

Symbol Parameter

Conditions

Min

Typ Max Units t PHL or t PLH

Propagation Delay Time from V DD = 5V 5090ns Input to Output

V DD = 10V 3060ns V DD = 15V 2550ns t THL or t TLH

Transition Time

V DD = 5V 80150ns V DD = 10V 50100ns V DD = 15V

4080ns C IN Average Input Capacitance Any Gate 615

pF C PD

Power Dissipation Capacitance

Any Gate (Note 6)

12

pF

https://www.doczj.com/doc/a518550187.html, 4

C D 4069U B C

Typical Performance Characteristics

Gate Transfer Characteristics

Power Dissipation vs

Frequency

Propagation Delay vs

Ambient Temperature

Propagation Delay vs Ambient Temperature

Propagation Delay Time vs Load Capacitance

https://www.doczj.com/doc/a518550187.html,

CD4069UBC

Physical Dimensions inches (millimeters) unless otherwise noted

14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150” Narrow Body

Package Number M14A

14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm wide

Package Number M14D

F a irch ild d o e s n o t a ssu m e a n y re spo n sib ility fo r u se o f a n y circu itry de scrib e d , n o circu it pa ten t lice nse s a re im p lie d a nd F a irch ild re se rv e s the rig h t a t a n y tim e w ith ou t n o tice to cha n g e sa id circu itry an d sp e cifica tio n s.

C D 4069U B C I n v e r t e r C i r c u i t s

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

1.Life support devices or systems are devices or systems

which, (a) are intended for surgical implant into the

body, or (b) support or sustain life, and (c) whose failure

to perform when properly used in accordance with

instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user.

2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or https://www.doczj.com/doc/a518550187.html, Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide

Package Number N14A

常用运放芯片实物和引脚功能图_TL081/082/084运放引 脚功能及贴片封装形式 (1)运放芯片的3种型号序列(部分器件有此序列) 如TL081、TL082、TL084,分别为8引脚单运放;8引脚双运放;14引脚四运放集成器件。封装型式一般为塑封双列直插和贴片双列,环列封装形式比较少见。 图1 TL081/082/084运放引脚功能及贴片封装形式 而常见常用,仅为下述两种器件。 世界上有几个人?有两个人,男人和女人,不失为一个智慧的回答。常用运放芯片有几片,只有两片,8脚和14脚的双运放和四运放集成器件(8脚封装单运放器件和环列式封装器件应用较少),把此两种芯片引脚功能记住,检修中就不需要随时去查资料了。

图2 常用运放芯片实物和引脚功能图 如上图。其封装一般为塑封双列直插DIP8/DIP14和塑封贴片工艺封装SO8/SO14两种形式,随着电子线路板小型化精密化要求的提高,贴片元件的应用占据主流,直插式器件逐渐淡出人们的视野。但无论何种封装模式,其引脚功能、次序都是一样的,所以仅需记准8脚(双运放)和14脚(四运放)两种运放的引脚功能就够了。 (2)运放芯片的3种温度序列 任何一种集成IC器件,按应用温度范围不同,都可细分为3种器件,如LM358,实际上有LM158、LM258、LM358三种型号的产品,其引脚功能、内部结构、工作原理、供电电压等等都无差别,仅仅是应用温度范围差异甚大。 LM158 适应工作温度-50℃~125℃,军工用品(1类); LM258 适应工作温度-25℃~85℃,工业用品(2类); LM358 适应工作温度0℃~70℃,农用品(3类)。 单看参数,似乎LM258适用于山东地区,若用于东北地区,其参数有些不足。而LM358仅能适用于江南地区。而事实上并非如此,如低于2类品规格参数被淘汰到3类品的器件,可能是-24℃~84℃温度范围

.v .. .. 常用芯片引脚 74LS00数据手册 74LS01数据手册 74LS02数据手册 74LS03数据手册 74LS04数据手册 74LS05数据手册 74LS06数据手册 74LS07数据手册 74LS08数据手册 74LS09数据手册 74LS10数据手册 74LS11数据手册

第2页 共8页 74LS12数据手册 74LS13数据手册 74LS14数据手册 74LS15数据手册 74LS16数据手册 74LS17数据手册 74LS19数据手册 74LS20数据手册 74LS21数据手册 74LS22数据手册 74LS23数据手册 74LS26数据手册 74LS27数据手册 74LS28数据手册

.v .. .. 74LS30数据手册 74LS32数据手册 74LS33数据手册 74LS37数据手册 74LS38数据手册 74LS40数据手册 74LS42数据手册 [1].要求0—15时,灭灯输入(BI )必须开路或保持高电平,如果不要灭十进制数零,则动态灭灯输入(RBI )必须开路或为高电平。 [2].将一低电平直接输入BI 端,则不管其他输入为何电平,所有的输出端均输出为低电平。 [3].当动态灭灯输入(RBI )和A,B,C,D 输入为低电平而试灯输入为高电平时,所有输出端都为低电平并且动态灭灯输入(RBO )处于第电平(响应条件)。 [4].]当灭灯输入/动态灭灯输出(BI/RBO )开朗路或保持高电平而试 灯输入为低电平时,所有各段输出均为高电平。 表中1=高电平,0=低电平。BI/RBO 是线与逻辑,作灭灯输入(BI )或动态灭灯(RBO )之用,或者兼为二者之用。

74系列芯片引脚图、功能、名称、资料大全(含74LS、74HC等),特别推荐为了方便大家,我收集了下列74系列芯片的引脚图资料。 说明:本资料分3部分:(一)、TXT文档,(二)、图片,(三)、功能、名称、资料。 (一)、TXT文档 反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门 LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373

反相器: Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )│ │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND 驱动器: Vcc 6A 6Y 5A 5Y 4A 4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A )│六驱动器(OC高压输出) 74LS07 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘

1A 1Y 2A 2Y 3A 3Y GND Vcc -4C 4A 4Y -3C 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│ Y =A+C )│四总线三态门 74LS125 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ -1C 1A 1Y -2C 2A 2Y GND Vcc -G B1 B2 B3 B4 B8 B6 B7 B8 ┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8位总线驱动器 74LS245 │20 19 18 17 16 15 14 13 12 11│ )│ DIR=1 A=>B │ 1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A └┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘ DIR A1 A2 A3 A4 A5 A6 A7 A8 GND

常用芯片引脚图 一、 单片机类 1、MCS-51 芯片介绍:MCS-51系列单片机是美国Intel 公司开发的8位单片机,又可以分为多个子系列。 MCS-51系列单片机共有40条引脚,包括32 条I/O 接口引脚、4条控制引脚、2条电源引 脚、2条时钟引脚。 引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时 的地址/数据复用口。 P1.0~P1.7:P1口8位口线,通用I/O 接口无第二功能。 P2.0~P2.7:P2口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时传送高8位地址。 P3.0~P3.7:P3口8位口线,第一功能作为 通用I/O 接口,第二功能作为为单片机的控 制信号。 ALE/ PROG :地址锁存允许/编程脉冲输入信号线(输出信号) PSEN :片外程序存储器开发信号引脚(输出信号) EA/Vpp :片外程序存储器使用信号引脚/编程电源输入引脚 RST/VPD :复位/备用电源引脚 2、MCS-96 芯片介绍:MCS-96系列单片机是美国Intel 公司继MCS-51系列单片机之后推出的16位单 片机系列。它含有比较丰富的软、硬件 资源,适用于要求较高的实时控制场合。 它分为48引脚和68引脚两种,以48引 脚居多。 引脚说明: RXD/P2.1 TXD/P2.0:串行数据传出分发 送和接受引脚,同时也作为P2口的两条 口线 HS1.0~HS1.3:高速输入器的输入端 HS0.0~HS0.5:高速输出器的输出端(有 两个和HS1共用) Vcc :主电源引脚(+5V ) Vss :数字电路地引脚(0V ) Vpd :部RAM 备用电源引脚(+5V ) V REF :A/D 转换器基准电源引脚(+5V ) AGND :A/D 转换器参考地引脚 12345678910111213141516171819204039383736353433323130292827262524232221P1.0P1.1P1.2P1.3P1.4P1.5P1.6P1.7RST RXD/P3.0TXD/P3.1INT0/P3.2INT1/P3.3T0/P3.4T1/P3.5WR/P3.6RD/P3.7XTAL2XTAL1V SS V CC P0.0/AD 0P0.1/AD 1 P0.2/AD 2P0.3/AD 3P0.4/AD 4P0.5/AD 5P0.6/AD 6P0.7/AD 7 EA/V PP ALE/PROG PSEN P2.7/A 15P2.6/A 14P2.5/A 13 P2.4/A 12P2.3/A 11P2.2/A 10P2.1/A 9P2.0/A 8803180518751

<74LS00引脚图> 74l s00 是常用的2输入四与非门集成电路,他的作用很简单顾名思义就是实现一个与非门。 Vcc 4B 4A 4Y 3B 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ __ │14 13 12 11 10 9 8│ Y = AB )│ 2输入四正与非门 74LS00 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1B 1Y 2A 2B 2Y GND 74LS00真值表: A=1 B=1 Y=0 A=0 B=1 Y=1 A=1 B=0 Y=1 A=0 B=0 Y=1

74HC138基本功能74LS138 为3 线-8 线译码器,共有54/74S138和54/74LS138 两种线路结构型式,其74LS138工作原理如下: 当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。 74LS138的作用: 利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器 用与非门组成的3线-8线译码器74LS138

图74ls138译码器内部电路 3线-8线译码器74LS138的功能表 备注:这里的输入端的三个A0~1有的原理图中也用A B C表示(如74H138.pdf中所示,试用于普中科技的HC-6800 V2.2单片机开发板)。<74ls138功能表> 74LS138逻辑图

无论从逻辑图还是功能表我们都可以看到74LS138的八个输出管脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出管脚全为高电平1。如果出现两个输出管脚在同一个时间为0的情况,说明该芯片已经损坏。 当附加控制门的输出为高电平(S=1)时,可由逻辑图写出 74ls138逻辑图 由上式可以看出,在同一个时间又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。 71LS138有三个附加的控制端、和。当、时,输出为高电平(S=1),译码器处于工作状态。否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。 带控制输入端的译码器又是一个完整的数据分配器。在图3.3.8电路中如果把作为“数据”输入端(在同一个时间),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。这就不难理解为什么把叫做地址输入了。例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。 例2.74LS138 3-8译码器的各输入端的连接情况及第六脚()输入信号A的波形如下图所示。试画出八个输出管脚的波形。

实验一:CMOS反相器的版图设计 一、实验目的 1、创建CMOS反相器的电路原理图(Schematic)、电气符号(symbol)以及版图(layout); 2、利用’gpdk090’工艺库实例化MOS管; 3、运行设计规则验证(Design Rule Check,DRC)确保版图没有设计规则错误。 二、实验要求 1、打印出完整的CMOS反相器的电路原理图以及版图; 2、打印CMOS反相器的DRC报告。 三、实验工具 Virtuoso 四、实验内容 1、创建CMOS反相器的电路原理图; 2、创建CMOS反相器的电气符号; 3、创建CMOS反相器的版图; 4、对版图进行DRC验证。

1、创建CMOS反相器的电路原理图及电气符号图 首先创建自己的工作目录并将/home/iccad/cds.lib复制到自己的工作目录下(我的工作目录为/home/iccad/iclab),在工作目录内打开终端并打开virtuoso(命令为icfb &). 在打开的icfb –log中选择tools->Library Manager,再创建自己的库,在当前的对话框上选择File->New->Library,创建自己的库并为自己的库命名(我的命名为lab1),点击OK后在弹出的对话框中选择Attach to an exiting techfile并选择gpdk090_v4.6的库,此时Library manager的窗口应如图1所示: 图1 创建好的自己的库以及inv 创建好自己的库之后,就可以开始绘制电路原理图,在Library manager窗口中选中lab1,点击File->New->Cell view,将这个视图命名为inv(CMOS反相器)。需要注意的是Library Name一定是自己的库,View Name是schematic,具体如图2所示: 图2 inv电路原理图的创建窗口 点击OK后弹出schematic editing的对话框,就可以开始绘制反相器的电路原理图(schematic view)。其中nmos(宽为120nm,长为100nm.)与pmos(宽为240nm,长为100nm.)从gpdk090_v4.6这个库中添加,vdd与gnd在analogLib这个库中添加,将各个原件用wire连接起来,连接好的反相器电路原理图如图3所示:

一:分类 74ls00 2输入四与非门 74ls01 2输入四与非门 (oc) 74ls02 2输入四或非门 74ls03 2输入四与非门 (oc) 74ls04 六倒相器 74ls05 六倒相器(oc) 74ls06 六高压输出反相缓冲器/驱动器(oc,30v) 74ls07 六高压输出缓冲器/驱动器(oc,30v) 74ls08 2输入四与门 74ls09 2输入四与门(oc) 74ls10 3输入三与非门 74ls11 3输入三与门 74ls12 3输入三与非门 (oc) 74ls13 4输入双与非门 (斯密特触发) 74ls14 六倒相器(斯密特触发) 74ls15 3输入三与门 (oc) 74ls16 六高压输出反相缓冲器/驱动器(oc,15v) 74ls17 六高压输出缓冲器/驱动器(oc,15v) 74ls18 4输入双与非门 (斯密特触发) 74ls19 六倒相器(斯密特触发) 74ls20 4输入双与非门 74ls21 4输入双与门 74ls22 4输入双与非门(oc) 74ls23 双可扩展的输入或非门 74ls24 2输入四与非门(斯密特触发)

74ls25 4输入双或非门(有选通) 74ls26 2输入四高电平接口与非缓冲器(oc,15v) 74ls27 3输入三或非门 74ls28 2输入四或非缓冲器 74ls30 8输入与非门 74ls31 延迟电路 74ls32 2输入四或门 74ls33 2输入四或非缓冲器(集电极开路输出) 74ls34 六缓冲器 74ls35 六缓冲器(oc) 74ls36 2输入四或非门(有选通) 74ls37 2输入四与非缓冲器 74ls38 2输入四或非缓冲器(集电极开路输出74ls39 2输入四或非缓 冲器(集电极开路输出) 7 4ls40 4输入双与非缓冲器 7 4ls41 bcd-十进制计数器 7 4ls42 4线-10线译码器(bcd输入) 7 4ls43 4线-10线译码器(余3码输 入) 7 4ls44 4线-10线译码器(余3葛莱 码输入) 7 4ls45 bcd-十进制译码器/驱动器 7 4ls46 bcd-七段译码器/驱动器

详细讲解cmos反相器的原理及特点 CMOS(cornplementary MOS)由成对的互补p沟道与n沟道MOSFET所组成.CMoS逻辑成为目前集成电路设计最常用技术的缘由,在于其有低功率损耗以及较佳的噪声抑止才干.事实上,由于低功率损耗的需求,目前仅有CMOS技术被运用于ULSI 的制造. CMOS反相器 如图6. 28所示,CMOS反相器为CMOS逻辑电路的基本单元.在CMOS反相器中,p 与n沟道晶体管的栅极衔接在一同,并作为此反相器的输入端,而此二晶体管的漏极也连接在一同,并作为反相器的输出端.n沟道MOSFET的源极与衬底接点均接地,而p沟道MOSFET的源极与衬底则衔接至电源供应端(VDD),需留意的是p沟道与n沟道MOSFET 均为增强型晶体管,当输入电压为低电压时(即vin=O,VGsn=o|VTp|(VGSp与VTp 为负值),所以p沟道MOSFET.为导通态, 因此,输出端经过p沟道MOSFET充电至VDD,当输入电压逐渐升高,使栅极电压等于VDD时,由于VGSn=VDD>VTn,所以n沟道MOSFET将被导通,而由于|VGSp |≈O 欲更深化天文解CMOS反相器的工作,可先画出晶体管的输出特性,如图6.29所示,其中显现Ip以及In为输出电压(V out)函数.Ip为p沟道MOSFET由源极(衔接至VDD)流向漏极(输出端)的电流;In为n沟道MOSFET由漏极(输出端)流向源极(衔接至接地端) 的电流.需留意的是在固定V out下,增加输入电压(vin)将会增加In而减少Ip,但是在稳态时,In应与Ip相同,关于给定一个Vin可由In(Vin)与Ip(Vin)的截距,计算出相对应的V out如图6. 29所示.如图6.30所示的Vin-V out曲线称为CMOS反相器的传输曲线. CMOS反相器的一个重要的特性是,当输出处于逻辑稳态(即V out=或VDD)时,仅有一个晶体管导通,因此由电源供应处流到地端的电流非常小,且相当于器件关闭时的漏电流.事实上,只需在两个器件暂时导通时的极短暂态时间内才会有大电流流过,因此与

CMOS反相器 由本书模拟部分已知,MOSFET有P沟道与N沟道两种,每种中又有耗尽型与增强型两类。由N沟道与P沟道两种MOSFET组成的电路称为互补MOS或CMOS电路。 下图表示CMOS反相器电路,由两只增强型MOSFET组成,其中一个为N沟道结构,另一个为P沟道结构。为了电路能正常工作,要求电源电压V DD 大于两个管子的开启电压的绝对值之与,即 V DD>(V TN+|V TP|) 。 1、工作原理 首先考虑两种极限情况:当v I处于逻辑0时,相应的电压近似为0V;而当v I处于逻辑1时,相应的电压近似为V DD。假设在两种情况下N沟道管T N 为工作管P沟道管T P为负载管。但就是,由于电路就是互补对称的,这种假设可以就是任意的,相反的情况亦将导致相同的结果。 下图分析了当v I=V DD时的工作情况。在TN的输出特性i D—v DS(v GSN=V DD)(注意v DSN=v O)上,叠加一条负载线,它就是负载管T P在v SGP=0V时的输出特性i D-v SD。由于v SGP<V T(V TN=|V TP|=V T),负载曲线几乎就是一条与横轴重合的水平线。两条曲线的交点即工作点。显然,这时的输出电压 v OL≈0V(典型值<10mV ,而通过两管的电流接近于零。这就就是说,电路的功耗很小(微瓦量级)

下图分析了另一种极限情况,此时对应于v I=0V。此时工作管T N在v GSN =0的情况下运用,其输出特性i D-v DS几乎与横轴重合,负载曲线就是负载管T P在v sGP=V DD时的输出特性i D-v DS。由图可知,工作点决定了V O= V OH≈V DD;通过两器件的电流接近零值。可见上述两种极限情况下的功耗都很低。 由此可知,基本CMOS反相器近似于一理想的逻辑单元,其输出电压接近于零或+V DD,而功耗几乎为零。 2、传输特性 下图为CMOS反相器的传输特性图。图中V DD=10V,V TN=|V TP|=V T= 2V。由于V DD>(V TN+|V TP|),因此,当V DD-|V TP|>vI>V TN时,T N与T P两管同时导通。考虑到电路就是互补对称的,一器件可将另一器件视为它的漏极负载。还应注意到,器件在放大区(饱与区)呈现恒流特性,两器件之一可当作高阻值的负载。因此,在过渡区域,传输特性变化比较急剧。两管在V I=V DD/2处转换状态。 3、工作速度 CMOS反相器在电容负载情况下,它的开通时间与关闭时间就是相等的,这就是因为电路具有互补对称的性质。下图表示当v I=0V时,T N截止,T P导

数字逻辑实验计划及要求(附录:实验所用芯片引脚图及功能说明)实验一逻辑门功能验证及使用电路实验 1.实验目的: (1)了解并掌握基本逻辑门电路的逻辑功能; (2)熟悉基本逻辑门电路的使用; (3)熟悉三态门和OC门电路的使用; (4)学习实验台的使用方法。 2.实验所用器件: 四二输入端和非门组件2片,型号为:74LS00 四二输入端和非门(OC)组件1片,型号为:74LS01 四二输入端或非门组件1片,型号为:74LS02 二和或非门组件1片,型号为:74LS51 四异或门组件1片,型号为:74LS86 四三态门组件1片,型号为:74LS125 排电阻(上拉电阻) 3.预习要求: (1)查出实验用器件引脚功能,画出实验电路图; (2)复习TTL各逻辑门电路的工作原理; (3)按实验内容要求设计电路。 4.实验内容 (1)测试实验所用器件的逻辑功能,填写真值表。 (2)用一片74LS00实现一2输入端异或门的功能。 (3)用一片74LS01及排电阻实现芯片74LS51的功能,做(AB+CD)’一组。 (4)用三态门组成两路总线传输电路。 5.实验要求 记录各实验观察结果并和理论所得各真值表进行比较。 6.思考 任何一逻辑电路均可分别用和非门,或非门,和或非门实现,为什么? 实验二组合电路功能验证及使用电路实验 1.实验目的: (1)熟悉常用组合逻辑芯片的功能; (2)掌握组合逻辑电路的设计方法。 2.实验所用器件 3-8线译码器一片,型号为:74LS138 8路数据选择器一片,型号为:74LS151 4位数码比较器一片,型号为:74LS85 四输入端和非门一片,型号为:74LS20 3.实验内容 (1)74LS85,74LS151的功能。 (2)用一片74LS85及一片74LS00组成5位二进制数值比较器。 (3)用74LS138和74LS20组成一位全加器。 (4)用一片74LS151实现三人多数表决器。 4.实验要求 记录各实验观察结果并和各器件功能表和一位全加器真值表进行比较。 5.思考

您的数字ID 是:463099 您的密码是:1.8667 附录三 常用芯片引脚图 一、单片机类 1、MCS-51 芯片介绍:MCS-51系列单片机是美国Intel 公司开发的8位单片机,又可以分为多个子系列。 MCS-51系列单片机共有40条引脚,包括32 条I/O 接口引脚、4条控制引脚、2条电源引脚、2条时钟引脚。引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时的地址/数据复用口。P1.0~P1.7:P1口8位口线,通用I/O 接口无第二功能。P2.0~P2.7:P2口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时传送高8位地址。 P3.0~P3.7:P3口8位口线,第一功能作为通用I/O 接口,第二功能作为为单片机的控制信号。 ALE/PROG :地址锁存允许/编程脉冲输入信号线(输出信号) PSEN :片外程序存储器开发信号引脚(输出信号) EA/Vpp :片外程序存储器使用信号引脚/编程电源输入引脚 RST/VPD :复位/备用电源引脚 2、MCS-96 芯片介绍:MCS-96系列单片机是美国Intel 公司继MCS-51系列单片机之后推出的16位单 片机系列。它含有比较丰富的软、硬件 资源,适用于要求较高的实时控制场合。 它分为48引脚和68引脚两种,以48引 脚居多。 引脚说明: RXD/P2.1TXD/P2.0:串行数据传出分发 送和接受引脚,同时也作为P2口的两条 口线 HS1.0~HS1.3:高速输入器的输入端 HS0.0~HS0.5:高速输出器的输出端(有 两个和HS1共用) Vcc :主电源引脚(+5V ) Vss :数字电路地引脚(0V ) Vpd :内部RAM 备用电源引脚(+5V ) V REF :A/D 转换器基准电源引脚(+5V ) AGND :A/D 转换器参考地引脚 XTAL1、XTAL2:内部振荡器反相器输 P1.0P1.1P1.2P1.3P1.4P1.5P1.6P1.7RST RXD/P3.0TXD/P3.1INT0/P3.2INT1/P3.3T0/P3.4T1/P3.5WR/P3.6RD/P3.7XTAL2XTAL1V SS

. . 常用芯片引脚 74LS00数据手册 74LS01数据手册 74LS02数据手册 74LS03数据手册 74LS04数据手册 74LS05数据手册 74LS06数据手册 74LS07数据手册 74LS08数据手册 74LS09数据手册 74LS10数据手册 74LS11数据手册

第2页 共8页 74LS12数据手册 74LS13数据手册 74LS14数据手册 74LS15数据手册 74LS16数据手册 74LS17数据手册 74LS19数据手册 74LS20数据手册 74LS21数据手册 74LS22数据手册 74LS23数据手册 74LS26数据手册 74LS27数据手册 74LS28数据手册

. . 74LS30 数据手册 74LS32数据手册 74LS33 数据手册 74LS37 数据手册 74LS38数据手册 74LS40 数据手册 74LS42数据手册 [1].要求0—15时,灭灯输入(BI )必须开路或保持高电平,如果不要灭十进制数零,则动态灭灯输入(RBI )必须开路或为高电平。 [2].将一低电平直接输入BI 端,则不管其他输入为何电平,所有的输出端均输出为低电平。 [3].当动态灭灯输入(RBI )和A,B,C,D 输入为低电平而试灯输入为高电平时,所有输出端都为低电平并且动态灭灯输入(RBO )处于第电平(响应条件)。 [4].]当灭灯输入/动态灭灯输出(BI/RBO )开朗路或保持高电平而试灯 输入为低电平时,所有各段输出均为高电平。 表中1=高电平,0=低电平。BI/RBO 是线与逻辑,作灭灯输入(BI )或动态灭灯(RBO )之用,或者兼为二者之用。

一、 单片机类 1、MCS‐51 芯片介绍:MCS‐51系列单片机是美国Intel公司开发的8位单片机,又可以分为多个子系列。 MCS‐51系列单片机共有40条引脚,包括32 条I/O接口引脚、4条控制引脚、2条电源引脚、2条时钟引脚。 引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为 通用I/O接口,第二功能作为存储器扩展时的地址/数据复用口。 P1.0~P1.7:P1口8位口线,通用I/O接口无第二功能。 P2.0~P2.7:P2口8位口线,第一功能作为通用I/O接口,第二功能作为存储器扩展时传送高8位地址。 P3.0~P3.7:P3口8位口线,第一功能作为通用I/O接口,第二功能作为为单片机的控制信号。 ALE/ PROG:地址锁存允许/编程脉冲输入信号线(输出信号) PSEN:片外程序存储器开发信号引脚(输出信号) EA/Vpp:片外程序存储器使用信号引脚/编程电源输入引脚 RST/VPD:复位/备用电源引脚 2、MCS‐96 芯片介绍:MCS‐96系列单片机是美国Intel公司继MCS‐51系列单片机之后推出的16位单 片机系列。它含有比较丰富的软、硬件资源,适用于要求较高的实时控制场合。它分为48引脚和68引脚两种,以48引脚居多。 引脚说明: RXD/P2.1 TXD/P2.0:串行数据传出分发 送和接受引脚,同时也作为P2口的两条口线 HS1.0~HS1.3:高速输入器的输入端 HS0.0~HS0.5:高速输出器的输出端(有 两个和HS1共用) Vcc:主电源引脚(+5V) Vss:数字电路地引脚(0V) Vpd:内部RAM备用电源引脚(+5V) VREF:A/D转换器基准电源引脚(+5V) AGND:A/D转换器参考地引脚

CMOS反相器电路版图设计与仿真 姓名:邓翔 学号:33 导师:马奎 本组成员:邓翔石贵超王大鹏

CMOS反相器电路版图设计与仿真 摘要:本文是基于老师的指导下,对cadence软件的熟悉与使用,进行CMOS反相器的电路设计和电路的仿真以及版图设计与版图验证仿真。 关键字:CMOS反相器;版图设计。 Abstract: This article is based on the teacher's guidance, familiar with cadence software and use, for CMOS inverter circuit design and circuit simulation and landscape and the landscape design of the simulation. Key word:CMOS inverter;Landscape design. 一引言 20世纪70年代后期以来,一个以计算机辅助设计技术为代表的新的技术改革浪潮席卷了全世界,它不仅促进了计算机本身性能的进步和更新换代,而且几乎影响到全部技术领域,冲击着传统的工作模式。以计算机辅助设计这种高技术为代表的先进技术已经、并将进一步给人类带来巨大的影响和利益。计算机辅助设计技术的水平成了衡量一个国家产业技术水平的重要标志。 计算机辅助设计(Computer Aided Design,CAD)是利用计算机强有力的计算功能和高效率的图形处理能力,辅助知识劳动者进行工程和产品的设计与分析,以达到理想的目的或取得创新成果的一种技术。它是综合了计算机科学与工程设计方法的最新发展而形成的一门新兴学科。计算机辅助设计技术的发

为了方便大家我收集了下列 74 系列芯片的引脚图资料,如还有需要请上电子论>坛> 推htt荐p:文//w章https://www.doczj.com/doc/a518550187.html,/b

bs/

74 系列芯片引脚图资料大全

反相器 驱动器

LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245

与门 与非门

LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38

或门 或非门 与或非门 LS02 LS32 LS51 LS64 LS65

异或门 比较器 译码器 寄存器

LS86 LS138 LS139 LS74 LS175 LS373

反相器:

Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04

┌┴—┴—┴—┴—┴—┴—┴┐ 六非门(OC 门) 74LS05

_ │14 13 12 11 10 9 8│ 六非门(OC 高压输出) 74LS06

Y=A )

│

│ 1 2 3 4 5 6 7│

└┬—┬—┬—┬—┬—┬—┬┘

1A 1Y 2A 2Y 3A 3Y GND

>> 阅读排行 lm358 pdf 应用电路资料及引 74 系列芯片引脚图资料大全 9014,9013,8050 三极管引脚图 max232 引脚图及 RS232 引脚

定 七段数码管引脚图 三极管 8550 参数管脚图 pdf 资 显示器 VGA 接口定义 LM324 引脚图资料与电路应

用 OP07,ua741 引脚图与资料 74ls48 引脚图管脚功能表

>> 相关文章

驱动器:

CMOS反相器 由本书模拟部分已知,MOSFET有P沟道和N沟道两种,每种中又有耗尽型和增强型两类。由N沟道和P沟道两种MOSFET组成的电路称为互补MOS或CMOS电路。 下图表示CMOS反相器电路,由两只增强型MOSFET组成,其中一个为N沟道结构,另一个为P沟道结构。为了电路能正常工作,要求电源电压V DD大于两个管子的开启电压的绝对值之和,即 V DD>(V TN+|V TP|) 。 1.工作原理 首先考虑两种极限情况:当v I处于逻辑0时,相应的电压近似为0V;而当v I处于逻辑1时,相应的电压近似为V DD。假设在两种情况下N沟道管T N为工作管P沟道管T P为负载管。但是,由于电路是互补对称的,这种假设可以是任意的,相反的情况亦将导致相同的结果。 下图分析了当v I=V DD时的工作情况。在TN的输出特性i D—v DS(v GSN =V DD)(注意v DSN=v O)上,叠加一条负载线,它是负载管T P在v SGP=0V 时的输出特性i D-v SD。由于v SGP<V T(V TN=|V TP|=V T),负载曲线几乎是一条与横轴重合的水平线。两条曲线的交点即工作点。显然,这时的输出电压v OL≈0V(典型值<10mV ,而通过两管的电流接近于零。这就是说,电路的功耗很小(微瓦量级)

下图分析了另一种极限情况,此时对应于v I=0V。此时工作管T N在v GSN =0的情况下运用,其输出特性i D-v DS几乎与横轴重合,负载曲线是负载管T P在v sGP=V DD时的输出特性i D-v DS。由图可知,工作点决定了V O=V OH≈V DD;通过两器件的电流接近零值。可见上述两种极限情况下的功耗都很低。 由此可知,基本CMOS反相器近似于一理想的逻辑单元,其输出电压接近于零或+V DD,而功耗几乎为零。 2.传输特性 下图为CMOS反相器的传输特性图。图中V DD=10V,V TN=|V TP|=V T= 2V。由于V DD>(V TN+|V TP|),因此,当V DD-|V TP|>vI>V TN时,T N和T P 两管同时导通。考虑到电路是互补对称的,一器件可将另一器件视为它的漏极负载。还应注意到,器件在放大区(饱和区)呈现恒流特性,两器件之一可当作高阻值的负载。因此,在过渡区域,传输特性变化比较急剧。两管在V I=V DD/2处转换状态。 3.工作速度

附录三 常用芯片引脚图 一、 单片机类 1、MCS-51 芯片介绍:MCS-51系列单片机是美国Intel 公司开发的8位单片机,又可以分为多个子系列。 MCS-51系列单片机共有40条引脚,包括32 条I/O 接口引脚、4条控制引脚、2条电源引 脚、2条时钟引脚。 引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时 的地址/数据复用口。 P1.0~P1.7:P1口8位口线,通用I/O 接口无第二功能。 P2.0~P2.7:P2口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时传送高8位地址。 P3.0~P3.7:P3口8位口线,第一功能作为 通用I/O 接口,第二功能作为为单片机的控 制信号。 ALE/ PROG :地址锁存允许/编程脉冲输入信号线(输出信号) PSEN :片外程序存储器开发信号引脚(输出信号) EA/Vpp :片外程序存储器使用信号引脚/编程电源输入引脚 RST/VPD :复位/备用电源引脚 2、MCS-96 芯片介绍:MCS-96系列单片机是美国Intel 公司继MCS-51系列单片机之后推出的16位单 片机系列。它含有比较丰富的软、硬件 资源,适用于要求较高的实时控制场合。 它分为48引脚和68引脚两种,以48引 脚居多。 引脚说明: RXD/P2.1 TXD/P2.0:串行数据传出分发 送和接受引脚,同时也作为P2口的两条 口线 HS1.0~HS1.3:高速输入器的输入端 HS0.0~HS0.5:高速输出器的输出端(有 两个和HS1共用) Vcc :主电源引脚(+5V ) Vss :数字电路地引脚(0V ) Vpd :内部RAM 备用电源引脚(+5V ) V REF :A/D 转换器基准电源引脚(+5V ) AGND :A/D 转换器参考地引脚 12345678910111213141516171819204039383736353433323130292827262524232221P1.0P1.1P1.2P1.3P1.4P1.5P1.6P1.7RST RXD/P3.0TXD/P3.1INT0/P3.2INT1/P3.3T0/P3.4T1/P3.5WR/P3.6RD/P3.7XTAL2XTAL1V SS V CC P0.0/AD 0P0.1/AD 1 P0.2/AD 2P0.3/AD 3P0.4/AD 4P0.5/AD 5P0.6/AD 6P0.7/AD 7 EA/V PP ALE/PROG PSEN P2.7/A 15P2.6/A 14P2.5/A 13 P2.4/A 12P2.3/A 11P2.2/A 10P2.1/A 9P2.0/A 8803180518751

附录五、常用IC引脚图 1、STC89C51单片机 2、8255并行I/O接口 T2/P1.0 -- 1 40 -- VCC PA3-- 1 40 --PA4 T2EX/P1.1-- 2 39 -- P0.0/AD0 PA2-- 2 39 --PA5 P1.2 -- 3 38 -- P0.1/AD1 PA1-- 3 38 --PA6 P1.3 -- 4 37 -- P0.2/AD2 PA0-- 4 37 --PA7 P1.4 -- 5 36 -- P0.3/AD3 RD -- 5 36 --WR P1.5 -- 6 35 -- P0.4/AD4 CS -- 6 35 --RESET P1.6-- 7 34 -- P0.5/AD5 GND-- 7 34 --D0 P1.7 -- 8 33 -- P0.6/AD6 A1 -- 8 33 --D1 RST -- 9 32 -- P0.7/AD7 A0 -- 9 32 --D2 RXD/P3.0-- 10 31 –EA(EA)PC7 -- 10 31 --D3 TXD/P3.1-- 11 30 --ALE/PROG PC6 -- 11 30 --D4 INT0/P3.2-- 12 29 --PSEN PC5 -- 12 29 --D5 INT1/P3.3-- 13 28 -- P2.7/A15 PC4 -- 13 28 --D6 T0/P3.4 -- 14 27 -- P2.6/A14 PC0 -- 14 27 --D7 T1/P3.5 -- 15 26 -- P2.5/A13 PC1 -- 15 26 --VCC WR/P3.6 -- 16 25 -- P2.4/A12 PC2 -- 16 25 --PB7 RD/P3.7 -- 17 24 -- P2.3/A11 PC -- 17 24 --PB6 XTAL2 -- 18 23 -- P2.2/A10 PB0 -- 18 23 --PB5 XTAL1 -- 19 22 -- P2.1/A9 PB1 -- 19 22 --PB4 VSS -- 20 21 -- P2.0/A8 PB2 -- 20 21 --PB3 注:STC89C51芯片的第31脚在用外接存储器时接低(地)电位,而在使用片内存储器时接高电位。 3、74LS373 八D锁存器 4、LED七段码显示器(共阴极型、单字) CE - 1 20 –VCC g f G a b 1Q - 2 19 –8Q 1D - 3 18 –8D a 2D -- 4 17 –7D f b 2Q -- 5 16 –7Q g 3Q -- 6 15 –6Q e c

题目: cmos反相器的电路设计及版图设计 初始条件: Cadence ORCAD和L-EDIT软件 要求完成的主要任务: 1、课程设计工作量:2周 2、技术要求: (1)学习ORCAD和L-EDIT软件。 (2)设计一个cmos反相器电路。 (3)利用ORCAD和L-EDIT软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。 3、查阅至少5篇参考文献。按《武汉理工大学课程设计工作规范》要求撰 写设计报告书。全文用A4纸打印,图纸应符合绘图规范。 时间安排: 2013.11.22布置课程设计任务、选题;讲解课程设计具体实施计划与课程设计报告格式的要求;课程设计答疑事项。 2013.11.25-11.27学习ORCAD和L-EDIT软件,查阅相关资料,复习所设计内容的基本理论知识。 2013.11.28-12.5对CMOS反相器电路进行设计仿真工作,完成课设报告的撰写。 2013.12.6 提交课程设计报告,进行答辩。 指导教师签名:年月日系主任(或责任教师)签名:年月日

目录 摘要 (3) 绪论 (5) 1软件介绍及电路原理 (6) 1.1软件介绍 (6) 1.2电路原理 (6) 2原理图绘制 (8) 3电路仿真 (10) 3.1瞬态仿真 (10) 3.2直流仿真 (11) 4版图设计及验证 (12) 4.1绘制反相器版图的前期设置 (12) 4.2绘制反相器版图 (13) 4.3 DRC验证 (15) 结束语 (17) 参考文献 (18)

摘要 CMOS技术自身的巨大发展潜力是IC高速持续发展的基础。集成电路制造水平发展到深亚微米工艺阶段,CMOS的低功耗、高速度和高集成度得到了充分的体现。本文将简单的介绍基于ORCAD和L-EDIT的CMOS反相器的电路仿真和版图设计,通过CMOS反相器的电路设计及版图设计过程,我们将了解并熟悉集成电路CAD的一种基本方法和操作过程。 关键词:CMOS反相器ORCAD L-EDIT版图设计

F007 输入;3脚=IN+,2脚=IN-.输出;6脚=OUT.电源;7脚=V+,4脚=V-.调另;1脚=OA1,5脚=OA2.

74LS244是8路3态缓冲驱动,也叫做线驱动或者总线驱动门电路。简单地说,它有8个输入端,8个输出端。 引脚定义如下: 引脚功能 1------1G 1Y1-1Y4输出控制,低电平有效,高电平高阻 2------1A1 输入端,对应的输出为1Y1 3------2Y4 输出端,对应的输入为2A4 4------1A2 5------2Y3 6------1A3 7------1Y2 8------1A4 9------2Y1 10-----GND 地 11-----2A1 12-----1Y4 13-----2A2 14-----1Y3 15-----2A3 16-----1Y2 17-----2A4 18-----1Y1 19-----2G 2Y1-2Y4输出控制端 20-----VCC 电源正

555 定时器的功能主要由两个比较器决定。两个比较器的输出电压控制RS 触发器和放电管的状态。在电源与地之间加上电压,当5 脚悬空时,则电压比较器A1 的反相输入端的电压为2VCC /3,A2 的同相输入端的电压为VCC /3。若触发输入端TR 的电压小于VCC /3,则比较器A2 的输出为1,可使RS 触发器置1,使输出端OUT=1。如果阈值输入端TH 的电压大于2VCC/3,同时TR 端的电压大于VCC /3,则A1 的输出为1,A2 的输出为0,可将RS 触发器置0,使输出为0 电平。 555 定时器成本低,性能可靠,只需要外接几个电阻、电容,就可以实现多谐振荡器、单稳态触发器及施密特触发器等脉冲产生与变换电路。它也常作为定时器广泛应用于仪器仪表、家用电器、电子测量及自动控制等方面。555 定时器的内部电路框图和外引脚排列图分别如图2.9.1 和图 2.9.2 所示。它内部包括两个电压比较器,三个等值串联电阻,一个RS 触发器,一个放电管T 及功率输出级。它提供两个基准电压VCC /3 和2VCC /3 555 定时器的功能主要由两个比较器决定。两个比较器的输出电压控制RS 触发器和放电管的状态。在电源与地之间加上电压,当5 脚悬空时,则电压比较器A1 的反相输入端的电压为2VCC /3,A2 的同相输入端的电压为VCC /3。若触发输入端TR 的电压小于VCC /3,则比较器A2 的输出为1,可使RS 触发器置1,使输出端OUT=1。如果阈值输入端TH 的电压大于2VCC/3,同时TR 端的电压大于VCC /3,则A1 的输出为1,A2 的输出为0,可将RS 触发器置0,使输出为0 电平。