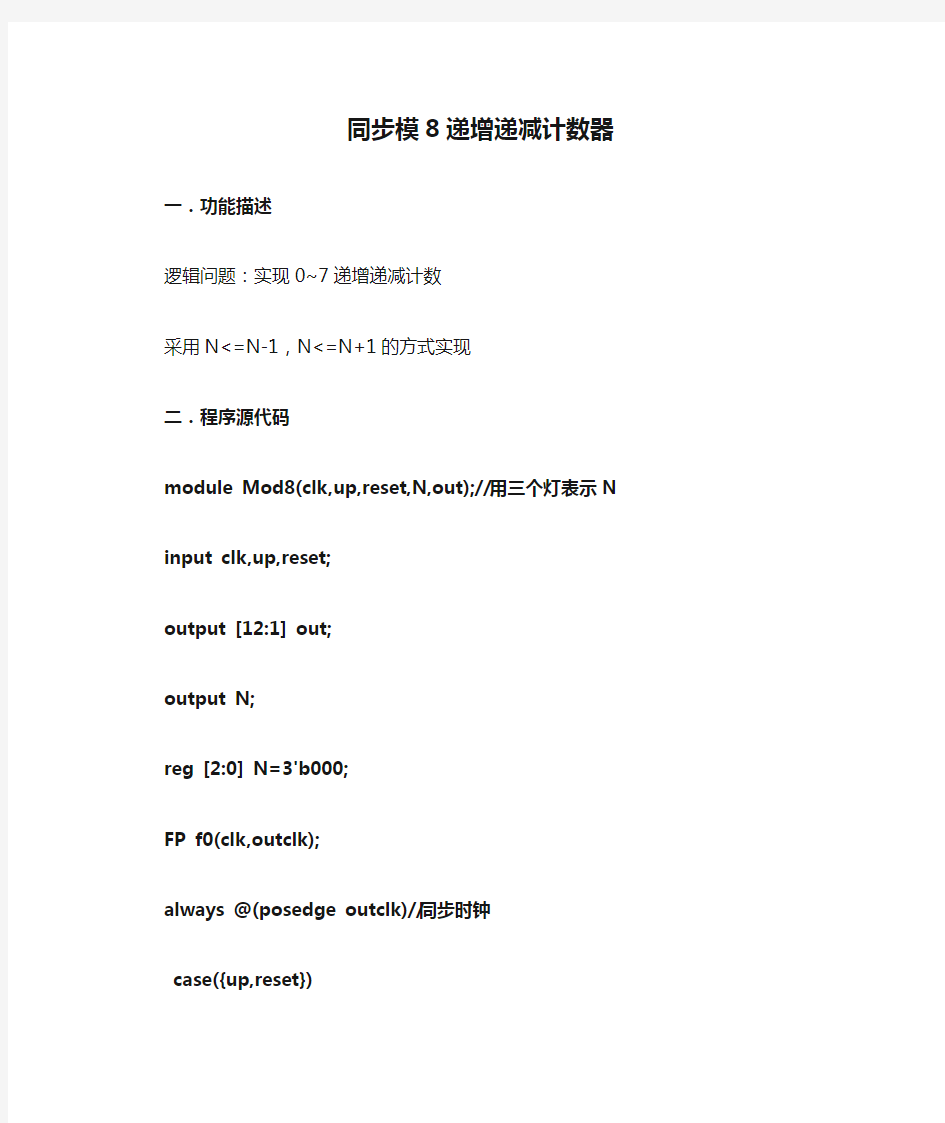

同步模8递增递减计数器一.功能描述

逻辑问题:实现0~7递增递减计数

采用N<=N-1,N<=N+1的方式实现

二.程序源代码

module Mod8(clk,up,reset,N,out);//用三个灯表示N

input clk,up,reset;

output [12:1] out;

output N;

reg [2:0] N=3'b000;

FP f0(clk,outclk);

always @(posedge outclk)//同步时钟

case({up,reset})

2'b00:N<=N-1;

2'b01:N<=0;

2'b10:N<=N+1;

default: N<=N;

endcase

BM f1(N,out);

Endmodule

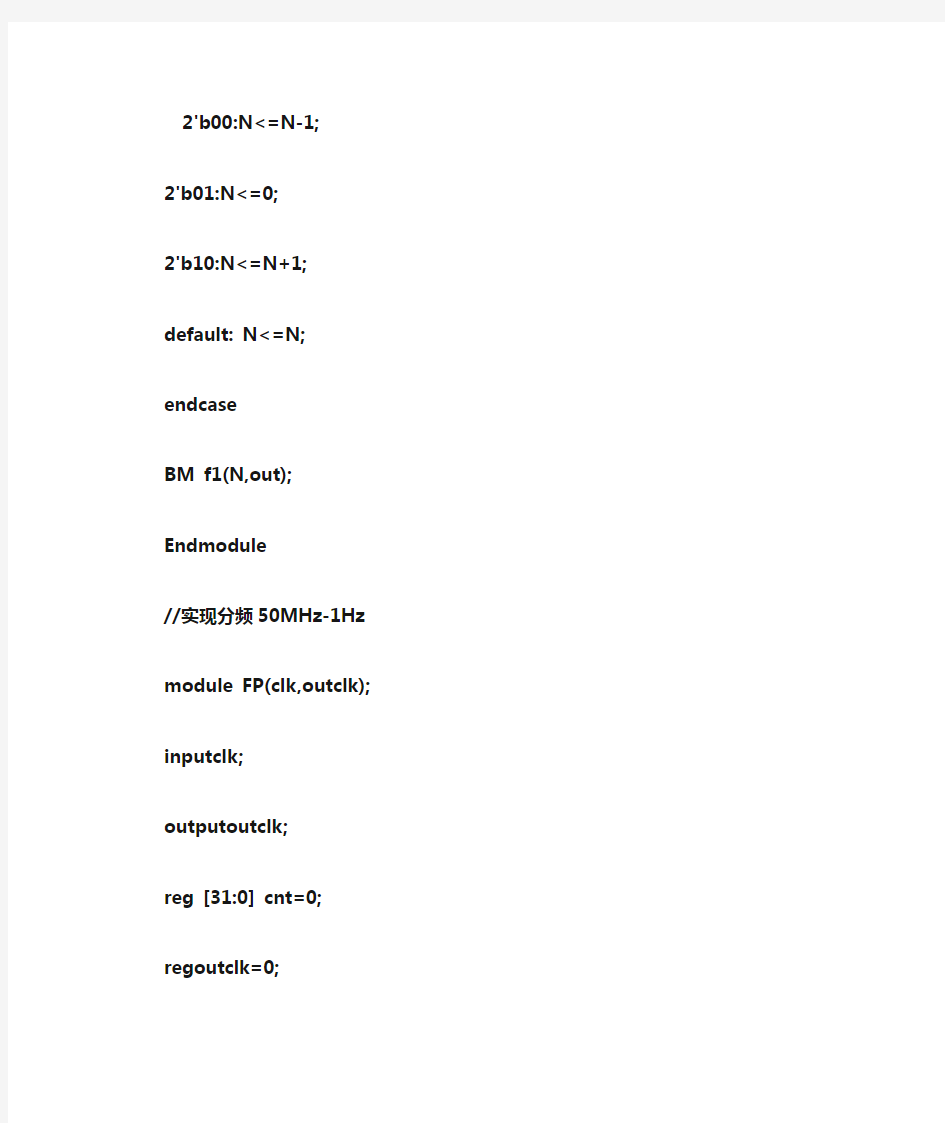

//实现分频50MHz-1Hz

module FP(clk,outclk);

inputclk;

outputoutclk;

reg [31:0] cnt=0;

regoutclk=0;

always @(posedgeclk)

begin

if(cnt<=24999999) cnt=cnt+1;

else

begin

outclk=~outclk;

cnt=0;

end

end

endmodule

//数码管编码

module BM(N,out);

input [2:0] N;

outputreg [12:1] out;

always @(N)

case(N)

3'b000:out=12'b011101000000; 3'b001:out=12'b011101111001; 3'b010:out=12'b011100100100; 3'b011:out=12'b011100110000; 3'b100:out=12'b011100011001; 3'b101:out=12'b011100010010; 3'b110:out=12'b011100000010; 3'b111:out=12'b011101111000; endcase

endmodule