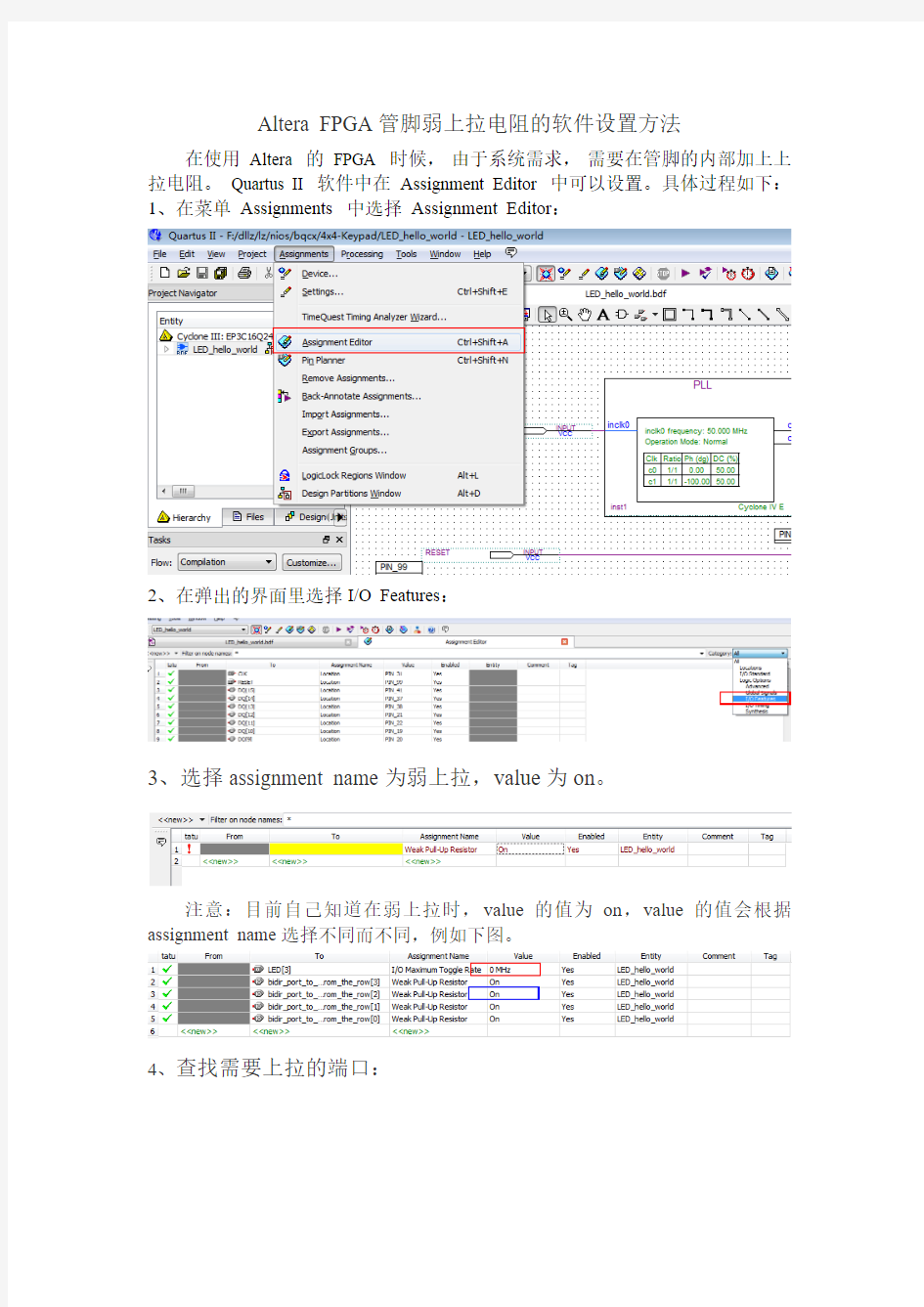

2、在弹出的界面里选择I/O Features:

3、选择assignment name为弱上拉,value为on。

注意:目前自己知道在弱上拉时,value的值为on,value的值会根据4、查找需要上拉的端口:

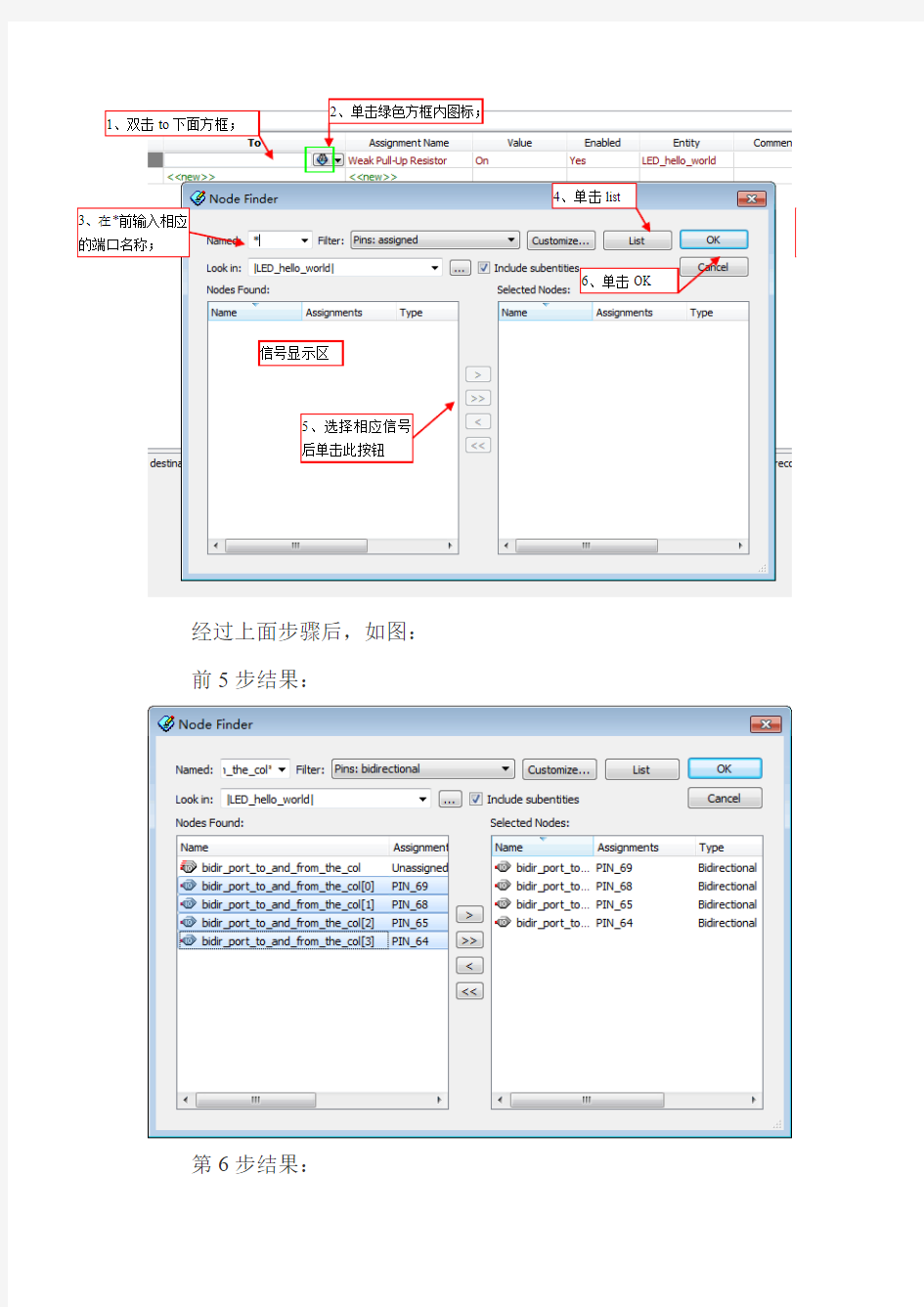

2、单击绿色方框内图标;

、双击to下面方框;

4、单击list

前输入相应

的端口名称;

6、单击OK

信号显示区

5、选择相应信号

后单击此按钮

经过上面步骤后,如图:

备注:该窗口有助于选择将要上拉的管脚。

5、保存然后再重新编译,设置完成。在.qsf中可以看到对应的端口已经上拉。

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to sw1_n

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to sw2_n

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to sw3_n

2016/2/10 笔记一:分配引脚的四种方法:(Quartus II 13.0sp1 (64-bit)) 1、常规方法,利用Pin Planner命令,适用于引脚使用比较少的工程,简洁方便; 2、使用.csv文件进行引脚分配: 步骤一:利用记事本新建一个.csv的格式文件,内容格式如图下图所示,然后保存; 步骤二:选择菜单栏Assignments-->Import Assignment,添加刚才生成的文件路径;

步骤三:点击OK,引脚分配完成。 注意:.csv文件保存路径不要有中文,建议保存在工程文件夹下。 3、使用.qsf文件进行引脚分配: 步骤一:在Quartus II中打开.qsf文件(系统默认生成.qsf文件,默认保存在该工程文件夹下) 步骤二:添加以下格式内容,格式如下图所示; 步骤三:点击保存,引脚分配完成。 4、使用.tcl文件进行引脚分配: 步骤一:生成.tcl文件,选择菜单栏Project-->Generate Tcl File For Project,点击OK,默认保存路径为该工程文件夹; 步骤二:添加以下格式内容,格式和.qsf文件格式一致; 步骤三:选择菜单栏Tool-->Tcl Scripts,选择生成的.tcl文件,点击Run,引脚分配完成。

说明:在实际的应用过程中,我们应该根据工程的子模块个数和引脚的使用多少来选择合适的引脚分配方式,笔者总结了以下几条:(不喜勿喷,还望多多赐教) 1、工程中使用的引脚数为个位数时,并且特别少,建议使用常规方法,利用Pin Planner 命令进行引脚分配; 2、工程中只有一个子模块时,如果引脚众多,尤其使用到数码管显示时,建议使用.tcl 文件进行引脚分配; 如图所示,.tcl文件中标识符和变量名已经给出,只需要输入对应引脚,比较方便。在多子模块的情况下,.tcl文件中没有给出标识符和变量名,这点需要注意。 3、多个子模块,使用引脚众多的情况下,利用.tcl文件、.csv文件和.qsf文件进行引脚分配大同小异,不过个人更喜欢利用.csv文件进行引脚分配,因为格式相对简单。

分配fpga管脚时该怎么选择,引脚有什么属性需要考虑,quartus2中引脚有几个属性:Reserved,Group,I/O Bank,Vref Group,I/O standard( 3.3-V LVTTL(default) )分别是什么意思,要怎么设置? 谢谢Totag 的回答,你看我的理解对不对:IO standard是根据你所要输入的电平来设置,Group是根据所分配的信号端口自动确定,而每个引脚的IO Bank 本身已经确定! 另外,分配的引脚所属的IO Bank不同有关系吗?引脚的分配除了要考虑专用引脚和用户引脚的区别外,还要考虑什么因素? 首先说IO standard:这个是用于支持对应不同的电平标准。FPGA IO口的电压由IO bank上的VCC引入。一个bank上引入3.3V TTL电平,那么此时整个bank上输出3.3V的TTL电平。设置这个第一是为了和current strength一起计算功率。第二个是用于在IO口上加载正确的上拉/下拉电阻。只要你设置完成,Quartus会按照你的电平标准自动布线。 第二是IO Bank:你在quartus pin planner 的top view下右键然后点击show IO banks,这个时候就会看到FPGA的管脚被几种颜色划分开了。一种颜色下的IO 口代表一组bank。你在吧管脚的location约束完成以后。IO Bank会自动填充完毕的。 第三是Group:Group就是你所输出的信号的名字啦。比如你有一组信号叫cnt。你对cnt的某一根赋值,那么。。这里的Group会自动填充为cnt 。 第四是Reserved:这个是对管脚内部的IO逻辑进行约束的,你在下面可以看到一些值。介绍几个吧。bidrectional:双向,tri-state:三态等等。这个约束的是FPGA 在IO端的输入输出区域的逻辑。比如你选择tri-state。那么这个时候,在你IO 口前部的IO区,quartus会自动给你生成一个三态门。 第五个是Vref Group:这个Group是bank内部的细分区域,因为一个bank可能多达60个脚。为了快速定位,你可以利用这个vref group来找到某个管脚。(这个是非修改属性)无法修改。 你的理解是正确的,另外,跨越IO bank的信号没有问题。只是注意跨bank的电平是否一致即可。对于跨IO bank的延迟对于FPGA而言没有多少延迟。 管脚分配呢,你可以看一下quartus里面pin planner内部那张top view对于每个管脚的说明。大多数管脚是可以当做普通IO使用的。只是有些特殊要求的时候。只可以使用对应的IO,比如差分输入,高时钟输入等等。这个是要参照对应器件的IO 手册来决定的。而且对应的设计大多数的器件生产商都会给出参考设计。里面包括了IO的设计,pcb的设计以及内部程序端口的约束。所以具体问题具体分析。

Quartus II中FPGA的管脚分配保存方法 一、摘要 将Quartus II中FPGA管脚的分配及保存方法做一个汇总。 二、管脚分配方法 FPGA 的管脚分配,除了在QII软件中,选择“Assignments ->Pin”标签(或者点击按钮),打开Pin Planner,分配管脚外,还有以下2种方法。 方法一:Import Assignments 步骤1: 使用记事本或类似软件新建一个txt文件(或csv文件),按如下格式编写管脚分配内容(不同的开发版,其内容也不同,本文以我使用的DIY_DE2开发板为范例)。【这种方式格式最为简单】 注意:To和Location两个关键字中间有一个半角逗号。 图1 pin.txt 步骤2:

在QII软件中,选择“Assignments -> Import Assignments”。如图所示,导入xxx.txt或者xxx.csv文件即可 图2 导入pin.txt 步骤3: 在QII软件中,选择“Assignments -> Pin”标签(或者点击按钮),打开Pin Planner,验证管脚是否分配正确。

图3 验证管脚是否分配正确 方法二:导入source xxx.tcl文件 步骤1: 在QII软件中,使用“Assignments -> Remove Assignments”标签,移除管脚分配内容,以确保此次操作,分配的管脚没有因为覆盖而出现错误的情况。

图4 Remove Assignments 注:在未执行任何管脚分配操作新工程中,可跳过步骤1。 步骤2: 使用记事本或类似软件新建一个tcl文件,按如下格式编写管脚分配内容(不同的开发版,其内容也不同,本文以我使用的DIY_DE2开发板为范例)。 注意关键字set_location_assignment和-to的用法。

XilinxFPGA引脚功能详细介绍 注:技术交流用,希望对大家有所帮助。 IO_LXXY_# 用户IO引脚 XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号 2.IO_LXXY_ZZZ_# 多功能引脚 ZZZ代表在用户IO的基本上添加一个或多个以下功能。 Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。配置完成后,这些引脚又作为普通用户引脚。 D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。 D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。 An:O,A[25:0]为BPI模式的地址位。配置完成后,变为用户I/O口。 AW AKE:O,电源保存挂起模式的状态输出引脚。SUSPEND是一个专用引脚,AWAKE 是一个多功能引脚。除非SUSPEND模式被使能,AWAKE被用作用户I/O。 MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。 FCS_B:O,BPI flash 的片选信号。 FOE_B:O,BPI flash的输出使能信号 FWE_B:O,BPI flash 的写使用信号 LDC:O,BPI模式配置期间为低电平 HDC:O,BPI模式配置期间为高电平 CSO_B:O,在并口模式下,工具链片选信号。在SPI模式下,为SPI flsah片选信号。 IRDY1/2,TRDY1/2:O,在PCI设计中,以LogiCORE IP方式使用。 DOUT_BUSY:O,在SelectMAP模式下,BUSY表示设备状态;在位串口模式下,DOUT 提供配置数据流。 RDWR_B_VREF:I,在SelectMAP模式下,这是一个低电平有效的写使能信号;配置完成后,如果需要,RDWR_B可以在BANK2中做为Vref。 HSW APEN:I,在配置之后和配置过程中,低电平使用上拉。 INIT_B:双向,开漏,低电平表示配置内存已经被清理;保持低电平,配置被延迟;在配置过程中,低电平表示配置数据错误已经发生;配置完成后,可以用来指示POST_CRC 状态。 SCPn:I,挂起控制引脚SCP[7:0],用于挂起多引脚唤醒特性。 CMPMOSI,CMPMISO,CMPCLK:N/A,保留。 M0,M1:I,配置模式选择。M0=并口(0)或者串口(1),M1=主机(0)或者从机(1)。 CCLK:I/O,配置时钟,主模式下输出,从模式下输入。 USERCCLK:I,主模式下,可行用户配置时钟。 GCLK:I,这些引脚连接到全局时钟缓存器,在不需要时钟的时候,这些引脚可以作为常规用户引脚。 VREF_#:N/A,这些是输入临界电压引脚。当外部的临界电压不必要时,他可以作为

FPGA入门及Quartus II使用教程FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在可编程阵列逻辑PAL(Programmable Array Logic)、门阵列逻辑GAL(Gate Array Logic)等可编程器件的基础上上进一步发展的产物。 可以这样讲,ASIC(Application Specific Integrated Circuit )内部的所有资源,是用积木堆积起来的小房子,可以是一个欧美风情的房子,还可以是一个北京四合院…….而FPGA内部就可以说是一个个小积木,也就是内部有大量的资源提供给我们,根据我们的需求进行内部的设计。并且可以通过软件仿真,我们可以事先验证设计的正确性。 第一章FPGA的基本开发流程 下面我们基于Altera 公司的QuantusII 软件来说明FPGA 的开发流程。 下图是一个典型的基于Quartus II的FPGA开发整体流程框图。

1、建立工程师每个开发过程的开始,Quartus II以工程为单位对设计过程进行管 理。 2、建立顶层图。可以这样理解,顶层图是一个容器,将整个工程的各个模块包 容在里边,编译的时候就将这些模块整合在一起。也可以理解为它是一个大元件,比如一个单片机,内部包含各个模块,编译的时候就是生成一个这样的大元件。 3、采用ALTERA公司提供的LPM功能模块。Quartus软件环境包含了大量的常 用功能模块,比如计数器、累加器、比较器等等。 4、自己建立模块。由于有些设计中现有的模块功能不能满足具体设计的要求, 那就只能自己设计。使用硬件描述语言,当然也可以用原理图的输入方法,可以独立的把它们当成一个工程来设计,并且生成一个模块符号(Symbol),类似于那些LPM功能模块。这里可以理解为,如果我们需求的滤波器,没有现成的合适的,那我们可以通过LC自己来搭建一个滤波器。 5、将顶层图的各个功能模块连线起来。这个过程类似电路图设计,把各个芯片 连起来,组成电路系统。 6、系统的功能原理图至此已经基本出炉了,下一步就是选择芯片字载体,分配 引脚,设置编译选项等等。 7、编译。这个过程类似软件开发里德编译,但是实际上这个过程比软件的编译 复杂的多,因为它最终要实现硬件里边的物理结构,包含了优化逻辑的组合,综合逻辑以及布线等步骤。 8、编译后会生成2个文件,一个是*.sof文件,一个是*.pof文件,前者可以通过 JTAG方式下载到FPGA内部,可以进行调试,但断电后数据丢失;后者通过AS或者PS方式下载到FPGA的配置芯片里边(EEPROM或者FLASH),重新上电后FPGA会通过配置将数据读出。 9、对于复杂的设计,工程编译好了,我们可以通过Quartus软件或者其他仿真 软件来对设计进行反复仿真和验证,直到满足要求。(主要是时序仿真)。 第二章基于Quartus II的实例 一、建立工程 首先,打开Quartus II软件。

Quartus II中FPGA管脚的分配策略 编写:*** 校核: 审核: 二〇一年月日

目录 目录..........................................................................................I QUARTUS II中FPGA管脚分配策略.. (1) 1.FPGA管脚介绍 (1) 1.1.电源管脚 (1) 1.2.配置管脚 (2) 1.3.普通I/O管脚 (2) 1.4.时钟管脚 (2) 2.FPGA管脚分配方法 (3) 2.1.P IN P LANNER方式 (3) 2.2.I MPORT A SSIGNMENTS方式 (4) 2.3.T CL S CRIPTS方式 (6) 2.4.项目组统一使用方式 (9) 3.编写FPGA管脚分配文件 (10) 3.1.查看PDF格式的原理图 (10) 3.2.查看P RJ PCB格式的原理图 (11) 4.保存FPGA管脚分配文件 (12) 4.1.T CL格式或CSV格式 (12) 4.2.QSF格式 (12) 4.3.项目组统一使用格式 (12) 附录管脚类型说明 (13)

Quartus II中FPGA管脚分配策略 1. FPGA管脚介绍 FPGA的管脚从使用对象来说可分为两大类:专用管脚和用户自定义管脚。一般情况下,专用管脚大概占FPGA管脚数的20% ~ 30%,剩下的70% ~ 80%为用户自定义管脚。从功能上来说可分为电源管脚、配置管脚、时钟管脚、普通I/O管脚等。 下面以Altera公司的Cyclone IV E系列芯片EP4CE30F23C8为例,如图1所示,芯片总共包含484个芯片管脚。图中不同颜色的区域代表不同的Bank,整个芯片主要分为8个Bank,FPGA的各个管脚分布在不同的Bank中。 其中,三角形标记的管脚为电源管脚,正三角表示VCC,倒三角表示GND,三角内部的O表示I/O管脚电源,I表示内核电源。 圆形标记的管脚为普通用户I/O管脚,可以由用户随意使用。 正方形标记且内部有时钟沿符号的管脚为全局时钟管脚。 五边形标记的管脚为配置管脚。 图1 Wire Bond 1.1. 电源管脚 FPGA通常需要两个电压才能运行,一个是内核电压,另一个是I/O电压。每个电压通过独立的电源管脚来提供。内核电压是用来给FPGA内部的逻辑门和触发器供电。随着FPGA的发展,内核电压从5V、3.3V、2.5V、1.8V到1.5V ,变得越来越低。I/O电压用来给各个Bank供电,每个Bank 都有独立的I/O电压输入。一般情况下,内核电压会比I/O电压低。

Quartus II中FPGA管脚分配策略Quartus II中FPGA管脚的分配策略 编写:*** 校核: 审核: 二〇一年月日

目录 目录 目录..........................................................................................I QUARTUS II中FPGA管脚分配策略.. (1) 1.FPGA管脚介绍 (1) 1.1.电源管脚 (1) 1.2.配置管脚 (2) 1.3.普通I/O管脚 (2) 1.4.时钟管脚 (2) 2.FPGA管脚分配方法 (3) 2.1.P IN P LANNER方式 (3) 2.2.I MPORT A SSIGNMENTS方式 (3) 2.3.T CL S CRIPTS方式 (6) 2.4.项目组统一使用方式 (8) 3.编写FPGA管脚分配文件 (9) 3.1.查看PDF格式的原理图 (9) 3.2.查看P RJ PCB格式的原理图 (10) 4.保存FPGA管脚分配文件 (11) 4.1.T CL格式或CSV格式 (11) 4.2.QSF格式 (11) 4.3.项目组统一使用格式 (11) 附录管脚类型说明 (12)

Quartus II中FPGA管脚分配策略 1. FPGA管脚介绍 FPGA的管脚从使用对象来说可分为两大类:专用管脚和用户自定义管脚。一般情况下,专用管脚大概占FPGA管脚数的20% ~ 30%,剩下的70% ~ 80%为用户自定义管脚。从功能上来说可分为电源管脚、配置管脚、时钟管脚、普通I/O管脚等。 下面以Altera公司的Cyclone IV E系列芯片EP4CE30F23C8为例,如图1所示,芯片总共包含484个芯片管脚。图中不同颜色的区域代表不同的Bank,整个芯片主要分为8个Bank,FPGA的各个管脚分布在不同的Bank中。 其中,三角形标记的管脚为电源管脚,正三角表示VCC,倒三角表示GND,三角内部的O表示I/O管脚电源,I表示内核电源。 圆形标记的管脚为普通用户I/O管脚,可以由用户随意使用。 正方形标记且内部有时钟沿符号的管脚为全局时钟管脚。 五边形标记的管脚为配置管脚。 图1 Wire Bond 1.1. 电源管脚 FPGA通常需要两个电压才能运行,一个是内核电压,另一个是I/O电压。每个电压通过独立的电源管脚来提供。内核电压是用来给FPGA内部的逻辑门和触发器供电。随着FPGA的发展,内核电压从5V、3.3V、2.5V、1.8V到1.5V ,变得越来越低。I/O电压用来给各个Bank供电,每个Bank 都有独立的I/O电压输入。一般情况下,内核电压会比I/O电压低。

FPGA管脚分配需要考虑的因素 在芯片的研发环节,FPGA验证是其中的重要的组成部分,如何有效的利用FPGA的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从研发的时间段上来考虑这种方法往往是不可取的,RTL 验证与验证板设计必须是同步进行的,在验证代码出来时验证的单板也必须设计完毕,也就是管脚的分配也必须在设计代码出来之前完成。所以,管脚的分配更多的将是依赖人,而非工具,这个时候就更需要考虑各方面的因素。 综合起来主要考虑以下的几个方面: 1、FPGA所承载逻辑的信号流向。 IC验证中所选用的FPGA一般逻辑容量都非常大,外部的管脚数量也相当的丰富,这个时候就必须考虑到PCB设计时的布线的难度,如果管脚的分配不合理,那么有可能在PCB设计时出现大量的交叉的信号线,这给布线带来很大的困难,甚至走不通,或者是即便是布线走通了,也有可能由于外部的延时过大而不满足时序方面的要求。所以在管脚分配前对FPGA工作的环境要相当的熟悉,要对其中的信号来自哪里去向何方非常的清楚,这就按照连线最短的原则将对应的信号分配到与外部器件连线最近的BANK中,2、掌握FPGA内部BANK的分配的情况。 现在FPGA内部都分成几个区域,每个区域中可用的I/O管脚数量各不相同。在IC验证中都是采用了ALTERA 与XILINX系列的FPGA ,这两个厂商的FPGA中内部BANK 的分配有一定的差异,这可以在设计中查阅相关的手册。下面与ALTERA中Stratix II 系列的FPGA内部BANK的分配为例来进行说明。 图中详细说明了FPGA内部BANK的分配情况和每个BANK中所支持的I/O标准。根

1 FPGA器件有三类配置下载方式:主动配置方式(AS)和被动配置方式(PS)和最常用的(JTAG)配置方式。 主动串行(AS) 由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列.如EPCS1,EPCS4配置器件专供AS模式,目前只支持Stratix II 和Cyclone系列。使用Altera串行配置器件来完成。Cyclone器件处于主动地位,配置器件处于从属地位。配置数据通过DA TA0引脚送入FPGA。配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。 AS配置器件是一种非易失性、基于flash存储器的存储器,用户可以使用altera的ByteBlaster II 加载电缆、altera的“altera programming unit”或者第三方的编程器来对配置芯片进行编程。它与FPGA的接口为以下简单的4个信号线: . 串行时钟输入(DCLK):是在配置模式下FPGA内部的振荡器(oscillator)产生的,在配置完成后,该振荡器将被关掉。工作时钟在20MHz左右,而fast AS方式下(stratix II和cyclone II支持该种配置方式),DCLK时钟工作在40MHz左右,在altera的主动串行配置芯片中,只有EPCS16和EPCS64的DCLK可以支持到40MHz,EPCS1和EPCS4只能支持20MHz。 . AS控制信号输入(ASDI) . 片选信号(nCS); . 串行数据输出(DATA)。 多片配置:控制配置芯片的FPGA为“主”,其后面的FPGA为“从”。主片的nCE需要直接接地,其nCEO输出脚驱动从片的nCE,而从片的nCEO悬空,nCEO脚在FPGA未配置时输出为低。这样,AS配置芯片中的配置数据首先写到主片的FPGA中,当其接收到它的所有的配置数据以后,随即驱动nCEO信号为高,使能从片的FPGA,这样配置芯片后面的读出的数据将被写入到从片的FPGA中。在生成配置文件对串行配置器件编程时,Quartus II 工具需要将两个配置文件合并到一个AS配置文件中,编程到配置器件中。如果这两个FPGA 的配置数据完全一样,就可以将从片的nCE也直接接地,这样只需要在配置芯片中放一个配置文件,两个FPGA同时配置。 被动串行(PS): PS(被动串行)则由外部计算机或控制器控制配置过程。所有altera FPGA都支持这种配置模式。通过altera 的下载电缆、加强型配置器件(EPC16,EPC8,EPC4)等配置器件或智能主机(如微处理器和CPLD)来完成,在PS配置期间,配置数据从外部储存部件(这些存储器可以是altera配置器件或单板上的其他flash器件),通过DATA0引脚送入FPGA。配置数据在DCLK上升沿锁存,1个时钟周期传送1位数据。FPP(快速被动并行):该配置

Xi lin X F PGA 引脚功能详细介绍 注:技术交流用,希望对大家有所帮助。 I O_LXX Y _ # 用户10弓I脚 XX代表某个Bank内唯一得一对引脚,Y=[P|N ]代表对上升沿还就是下降沿敏感,# 代表ban k 号 2. I0_LXXY —Z Z Z_ #多功能引脚 Z ZZ代表在用户10得基本上添加一个或多个以下功能。 Dn:1/ 0(在r eadb a ck期间),在selectMAP或者BPI模式下,D [1 5 :0]配置为数据口。在从Selec t MAP读反馈期间,如果RDWR_B= 1,则这些引脚变成输出口。配置完成后,这些引脚又作为普通用户引脚? D 0_DIN_ M ISO_M I SO1: I,在并口模式(Sel ec tMAP/ B PI)下,D0 就是数据得最低位,在Bit —se r ial模式下,DI N就是信号数据得输入;在SPI模式下,MISO就是主输入或者从输出;在SPI*2或者S PI * 4模式下,M I SO 1就是S P I总线得第二位。 D1_MISO 2 ,D2_MIS O 3: I,在并口模式下,D1与D2就是数据总线得低位;在S PI * 4 模式下, MISO2 与MISO3 就是SPI 总线得MSBs. A n :O, A : 25 :0]为 B PI模式得地址位。配置完成后,变为用户I/ O口。 A WAKE: O ,电源保存挂起模式得状态输出引脚。SU S P E ND就是一个专用引脚,A WA K E就是一个多功能引脚。除非SUSPEND模式被使能,AWAK E被用作用户I / O。 M O SI _CSI_B_MI S O0:I/O,在SPI模式下,主输出或者从输入在Se l ectMAP模式下,CS I_B 就是一个低电平有效得片选信号;在SPI * 2或者S P I *4得模式下,M I SO 0就是S PI总线得第一位数据。 FCS_B:O,BPI flash 得片选信号. FO E _B:O,B PI flash 得输出使能信号 FW E_ B : O , BP I f l a sh得写使用信号 LDC : O,BP I模式配置期间为低电平 HDC: 0 ,B PI 模式配置期间为高电平 CSO_B :O,在并口模式下,工具链片选信号。在SP I模式下,为SPI f ls ah片选信号。 I R DY 1/2, T R DY1 / 2:0,在PCI 设计中,以L og i C ORE IP 方式使用。 DO U T _B USY:O,在S e l ec tM A P模式下,B U SY 表示设备状态;在位串口模式下,DO UT提供配置数据流。 R D W R_B_VREF:I,在S elec t M AP模式下,这就是一个低电平有效得写使能信号;配置完成后,如果需要,R DW R_B可以在BANK 2中做为Vref. HSWA P EN:I ,在配置之后与配置过程中,低电平使用上拉。 INIT _B:双向,开漏,低电平表示配置内存已经被清理;保持低电平,配置被延迟;在配 置过程中,低电平表示配置数据错误已经发生;配置完成后,可以用来指示POST_C RC 状 态。 S CPn:I,挂起控制引脚SCP[7: 0],用于挂起多引脚唤醒特性? C MPMOSI,CMPM I S O, CMPC L K : N/A,保留。 M0, M1 : I,配置模式选择。M 0 =并口(0)或者串口(1 ),M仁主机(0)或者从机(1 )。 CC LK :I/O, 配置时钟,主模式下输出,从模式下输入。 US E RCCL K :I,主模式下,可行用户配置时钟。 GCLK:I ,这些引脚连接到全局时钟缓存器,在不需要时钟得时候,这些引脚可以作为常

精品 Quartus II中FPGA管脚的分配策略 编写:*** 校核: 审核: 二〇一年月日

目录 目录 ...................................................................................... I QUARTUS II中FPGA管脚分配策略 .. (1) 1.FPGA管脚介绍 (1) 1.1.电源管脚 (2) 1.2.配置管脚 (2) 1.3.普通I/O管脚 (3) 1.4.时钟管脚 (3) 2.FPGA管脚分配方法 (4) 2.1.P IN P LANNER方式 (4) 2.2.I MPORT A SSIGNMENTS方式 (5) 2.3.T CL S CRIPTS方式 (8) 2.4.项目组统一使用方式 (11) 3.编写FPGA管脚分配文件 (12) 3.1.查看PDF格式的原理图 (12) 3.2.查看P RJ PCB格式的原理图 (13) 4.保存FPGA管脚分配文件 (14) 4.1.T CL格式或CSV格式 (15) 4.2.QSF格式 (15) 4.3.项目组统一使用格式 (15)

附录管脚类型说明 (16)

Quartus II中FPGA管脚分配策略 1. FPGA管脚介绍 FPGA的管脚从使用对象来说可分为两大类:专用管脚和用户自定义管脚。一般情况下,专用管脚大概占FPGA管脚数的20% ~ 30%,剩下的70% ~ 80%为用户自定义管脚。从功能上来说可分为电源管脚、配置管脚、时钟管脚、普通I/O管脚等。 下面以Altera公司的Cyclone IV E系列芯片EP4CE30F23C8为例,如图1所示,芯片总共包含484个芯片管脚。图中不同颜色的区域代表不同的Bank,整个芯片主要分为8个Bank,FPGA 的各个管脚分布在不同的Bank中。 其中,三角形标记的管脚为电源管脚,正三角表示VCC,倒三角表示GND,三角内部的O表示I/O管脚电源,I表示内核电源。 圆形标记的管脚为普通用户I/O管脚,可以由用户随意使用。 正方形标记且内部有时钟沿符号的管脚为全局时钟管脚。 五边形标记的管脚为配置管脚。

ALTERA FPGA 特殊管脚说明、 管脚名称 器件系列 使用模式 配置模式 管脚类型 描述 MSEL0 MSEL1 APEX II APEX 20K Mercury ACEX 1K FLEX 10K 特殊管脚 不能做用 户I/O All 输入 设置 APEX II、 Mercury、ACEX 1K、 APEX 20K 和 FLEX 10K 器件配置模式 MSEL1 MSEL0 配置模式 0 0串行配置或使用配置器件模式 1 0 并行同步模式 1 1 并行异步模式 MSEL FLEX 6000 特殊管脚 不能做用 户I/O All 输入 MSEL 配置模式 0 串行加载或使用加载器件模式,及 MasterBlaster 或ByteBlasterMV加 载电缆模式 1 串行异步模式 nSTATUS APEX II APEX 20K Mercury ACEX 1K FLEX 10K FLEX 6000 特殊管脚 不能做用 户I/O All 双向 集电极开路 上电后被器件拉低,在5US之内,被器件释放, (当使用一个专用配置器件时,专用加载器件将 控制这个脚为低长达200ms。)这个管脚必须通 过一个1K电阻上拉到VCCIO; (APEX 20KE 或 APEX 20KC 器件为10K欧姆) 如果在配置过程中,如有错误发生,本管脚被器 件拉;。 如果在配置或初始化过程中,有一个外部的信号 源驱动本管脚为低,则器件进入一个错误的状 态; 在配置或初始化之后,驱动本管脚为低,不会影 响器件。但是,如果使用专用配置器件,驱动本 管脚低将引起配置器件试图去配置APEX 或 FLEX 器件。 (详细见AN116中的配置时序) nCONFIG APEX II APEX 20K Mercury ACEX 1K FLEX 10K FLEX 6000 特殊管脚 不能做用 户I/O All 输入 配置控制引脚: 由0-1的跳变开始配置,由1-0跳变则复位器件; 当设定本管脚为0时,所有I/O为三态。 (详细见AN116中的配置时序) CONF_DONE APEX II APEX 20K Mercury ACEX 1K FLEX 10K FLEX 6000 特殊管脚 不能做用 户I/O All 双向 集电极开路 状态输出: 在配置之前和配置过程中,器件驱动本管脚为0, 一旦所有配置数据都被接收并没有错误发生,则 初始化时钟周期开始时器件释放本管脚; 状态输入:在所有数据被接收后,本管脚为高电 平,器件初始化,然后进入用户模式; 本管脚必须通过一个1K的电阻上拉到VCCIO (APEX 20KE或APEX 20KC 器件使用10K欧姆电阻) 外部的信号源可以驱动本管脚为低,来延迟初始 化的过程,当使用一个配置器件进行配置除外, 在配置以及初始化之后,驱动本管脚为低, 不 影响配置器件。 (详细见AN116中的配置时序)

注:技术交流用,希望对大家有所帮助。 IO_LXXY_# 用户IO引脚 XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank 号 2.IO_LXXY_ZZZ_# 多功能引脚 ZZZ代表在用户IO的基本上添加一个或多个以下功能。 Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。配置完成后,这些引脚又作为普通用户引脚。 D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。 D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。 An:O,A[25:0]为BPI模式的地址位。配置完成后,变为用户I/O口。 AWAKE:O,电源保存挂起模式的状态输出引脚。SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。除非SUSPEND模式被使能,AWAKE被用作用户I/O。 MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。 FCS_B:O,BPI flash 的片选信号。 FOE_B:O,BPI flash的输出使能信号 FWE_B:O,BPI flash 的写使用信号 LDC:O,BPI模式配置期间为低电平 HDC:O,BPI模式配置期间为高电平 CSO_B:O,在并口模式下,工具链片选信号。在SPI模式下,为SPI flsah片选信号。 IRDY1/2,TRDY1/2:O,在PCI设计中,以LogiCORE IP方式使用。

附录脚配置脚本文件 ############################################## # https://www.doczj.com/doc/ad10511645.html, ############################################## set_global_assignment -name RESERVE_ALL_UNUSED_PINS "AS INPUT TRI-STATED" set_global_assignment -name ENABLE_INIT_DONE_OUTPUT OFF set_location_assignment PIN_23 -to clock set_location_assignment PIN_131 -to rst_n #--------------------LED----------------------# set_location_assignment PIN_142 -to led[1] set_location_assignment PIN_141 -to led[2] set_location_assignment PIN_139 -to led[3] set_location_assignment PIN_138 -to led[4] set_location_assignment PIN_137 -to led[5] set_location_assignment PIN_135 -to led[6] set_location_assignment PIN_134 -to led[7] set_location_assignment PIN_133 -to led[8] #--------------------KEY----------------------# set_location_assignment PIN_107 -to key[0] set_location_assignment PIN_108 -to key[1] set_location_assignment PIN_110 -to key[2]

FPGA器件管脚说明 用户I/O:不用解释了。 配置管脚: MSEL[1:0] 用于选择配置模式,比如AS、PS等。 DA TA0 FPGA串行数据输入,连接到配置器件的串行数据输出管脚。 DCLK FPGA串行时钟输出,为配置器件提供串行时钟。 nCSO(I/O)FPGA片选信号输出,连接到配置器件的nCS管脚。 ASDO(I/O)FPGA串行数据输出,连接到配置器件的ASDI管脚。 nCEO 下载链期间使能输出。在一条下载链中,当第一个器件配置完成后,此信号将使能下一个器件开始进行配置。下载链上最后一个器件的nCEO悬空。 nCE 下载链器件使能输入,连接到上一个器件的nCEO,下载链的最后一个器件nCE接地。nCNFIG 用户模式配置起始信号。 nSTATUS 配置状态信号。 CONF_DONE 配置结束信号。 电源管脚: VCCINT 内核电压。130nm为1.5V,90nm为1.2V。 VCCIO 端口电压。一般为3.3V,还可以支持多种电压,5V、1.8V、1.5V。 VREF 参考电压。 GND 信号地。 时钟管脚: VCC_PLL PLL管脚电压,直接连VCCIO。 VCCA_PLL PLL模拟电压,截止通过滤波器接到VCCINT上。 GNDA_PLL PLL模拟地。 GNDD_PLL PLL数字地。 CLK[n] PLL时钟输入。 PLL[n]_OUT PLL时钟输出。 特殊管脚: VCCPD 用于寻则驱动。 VCCSEL 用于控制配置管脚和PLL相关的输入缓冲电压。 PROSEL 上电复位选项。 NIOPULLUP 用于控制配置时所使用的用户I/O的内部上拉电阻是否工作。 TEMPDIODEN 用于关联温度敏感二极管。 ************************************************************************************ 1/1、I/O, ASDO 在AS模式下是专用输出脚,在PS和JTAG模式下可以当I/O脚来用。在AS模式下,这个脚是CII向串行配置芯片发送控制信号的脚。也是用来从配置芯片中读配置数据的脚。在AS模式下,ASDO有一个内部的上拉电阻,一直有效,配置完成后,该脚就变成三态输入脚。ASDO脚直接接到配置芯片的ASDI脚(第5脚)。 2/2、I/O,nCSO 在AS模式下是专用输出脚,在PS和JTAG模式下可以当I/O 脚来用.在AS模式下,这个脚是CII用来给外面的串行配置芯片发送的使能脚。在AS模式下,ASDO有一个内部的上拉电阻,一直有效。这个脚是低电平有效的。

X i l i n x F P G A引脚功能详细介绍

XilinxFPGA引脚功能详细介绍 注:技术交流用,希望对大家有所帮助。 IO_LXXY_# 用户IO引脚 XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号 2.IO_LXXY_ZZZ_# 多功能引脚 ZZZ代表在用户IO的基本上添加一个或多个以下功能。 Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。配置完成后,这些引脚又作为普通用户引脚。 D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO 是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。 D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。 An:O,A[25:0]为BPI模式的地址位。配置完成后,变为用户I/O口。 AWAKE:O,电源保存挂起模式的状态输出引脚。SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。 FCS_B:O,BPI flash 的片选信号。 FOE_B:O,BPI flash的输出使能信号 FWE_B:O,BPI flash 的写使用信号 LDC:O,BPI模式配置期间为低电平 HDC:O,BPI模式配置期间为高电平 CSO_B:O,在并口模式下,工具链片选信号。在SPI模式下,为SPI flsah 片选信号。 IRDY1/2,TRDY1/2:O,在PCI设计中,以LogiCORE IP方式使用。 DOUT_BUSY:O,在SelectMAP模式下,BUSY表示设备状态;在位串口模式下,DOUT提供配置数据流。 RDWR_B_VREF:I,在SelectMAP模式下,这是一个低电平有效的写使能信号;配置完成后,如果需要,RDWR_B可以在BANK2中做为Vref。 HSWAPEN:I,在配置之后和配置过程中,低电平使用上拉。 INIT_B:双向,开漏,低电平表示配置内存已经被清理;保持低电平,配置被延迟;在配置过程中,低电平表示配置数据错误已经发生;配置完成后,可以用来指示POST_CRC状态。 SCPn:I,挂起控制引脚SCP[7:0],用于挂起多引脚唤醒特性。 CMPMOSI,CMPMISO,CMPCLK:N/A,保留。

1/1.I/O, ASDO: 在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用。在AS 模式下,这个脚是CII 向串行配置芯片发送控制信号的脚。也是用来从配置芯片中读配置数据的脚。在AS 模式下,ASDO 有一个内部的上拉电阻,一直有效,配置完成后,该脚就变成三态输入脚。ASDO 脚直接接到配置芯片的ASDI 脚 (第5 脚)。 2/2.I/O,nCSO 在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用.在AS 模式下,这个脚是CII 用来给外面的串行配置芯片发送的使能脚。在AS 模式下,ASDO 有一个内部的上拉电阻,一直有效。这个脚是低电平有效的。直接接 到配置芯片的/CS 脚(第1 脚)。 3/3.I/O,CRC_ERROR 当错误检测CRC 电路被选用时,这个脚就被作为CRC_ERROR 脚,如果不用默认就用来做I/O。但要注意,这个脚是不支持漏极开路和反向的。当它作为CRC_ERROR 时,高电平输出则表示出现了CRC 校验错误(在配置SRAM 各个比特时出现了错误)。CRC 电路的支持可以在setting 中加上。这个脚一般与nCONFIG 脚配合起来用。即如果配置过程出错,重新配置. 4/4.I/O,CLKUSR 当在软件中打开Enable User-supplled start-up clock(CLKUSR)选项后,这个脚就只可以作为用户提供的初始化时钟输入脚。在所有配置数据都已经被接收后,CONF_DONE 脚会变成高电平,CII 器件还需要299 个时钟周期来初始化寄存器,I/O 等等状态,FPGA 有两种方式,一种是用内部的晶振(10MHz),另一种就是从CLKUSR 接进来的时钟(最大不能超过100MHz)。有这个功能,可以延缓FPGA 开始工作的时间,可以在需要和其它器件进行同步的特殊应用 中用到 7/13.I/O,VREF 用来给某些差分标准提供一个参考电平。没有用到的话,可以当成I/O 来用。 14/20. DATA0 专用输入脚。在AS 模式下,配置的过程是:CII 将nCSO 置低电平,配置芯片被使能。CII然后通过DCLK 和ASDO 配合操作,发送操作的命令,以及读的地址给配置芯片。配置芯片然后通过DATA 脚给CII 发送数据。DATA 脚就接到CII 的DATA0 脚上。CII 接收完所有的配置数据后,就会释放CONF_DONE 脚(即不强制使CONF_DONE 脚为低电平),CONF_DONE 脚是漏极开路(Open-Drain)的。这时候,因为CONF_DONE 在外部会接一个