基于Verilog利用SRAM设计一个FIFO

专业:电子信息工程

班级:电子092

学号:

姓名:

2012年 11 月23 日

一、设计要求:

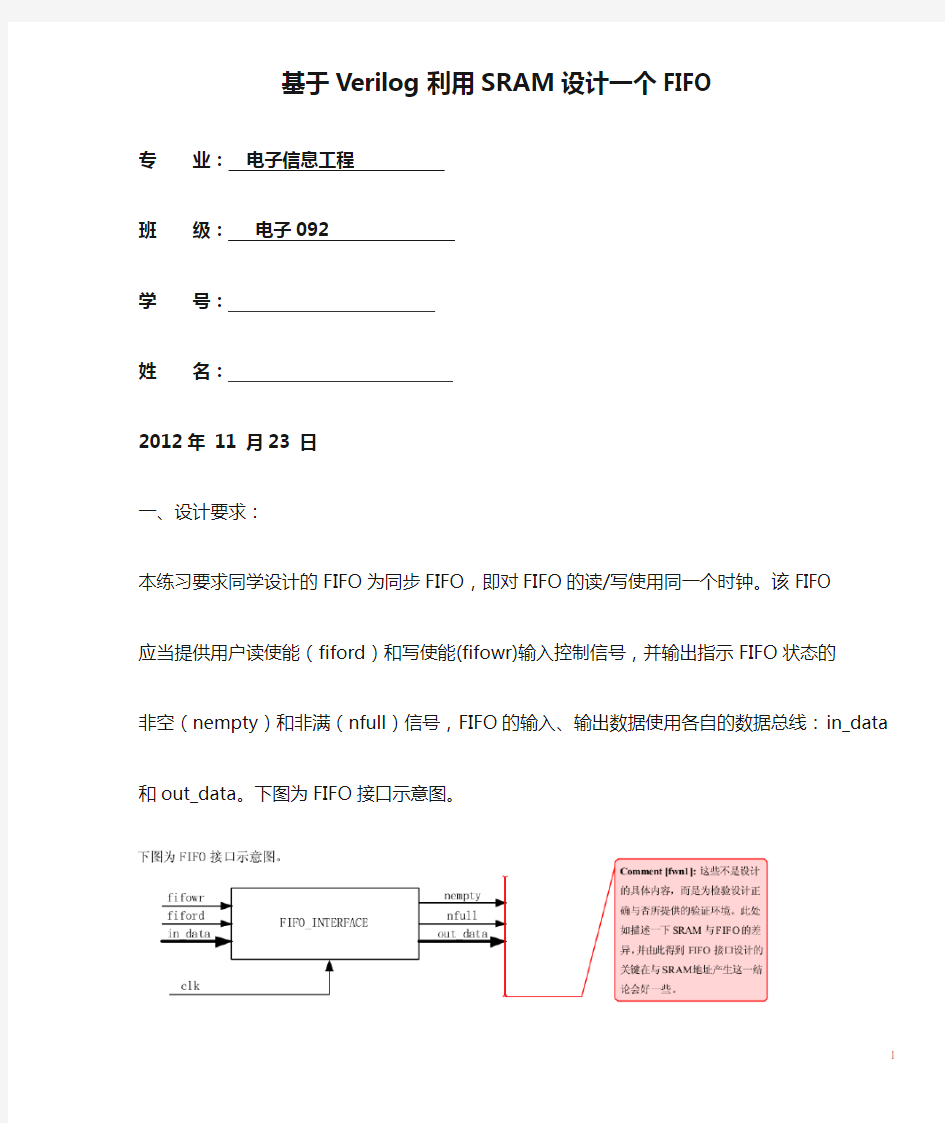

本练习要求同学设计的FIFO为同步FIFO,即对FIFO的读/写使用同一个时钟。该FIFO

应当提供用户读使能(fiford)和写使能(fifowr)输入控制信号,并输出指示FIFO状态的

非空(nempty)和非满(nfull)信号,FIFO的输入、输出数据使用各自的数据总线:in_data 和out_data。下图为FIFO接口示意图。

二、FIFO接口的设计思路

FIFO的数据读写操作与SRAM的数据读写操作基本上相同,只是FIFO没有地址。所

以用SRAM实现FIFO的关键点是如何产生正确的SRAM地址。

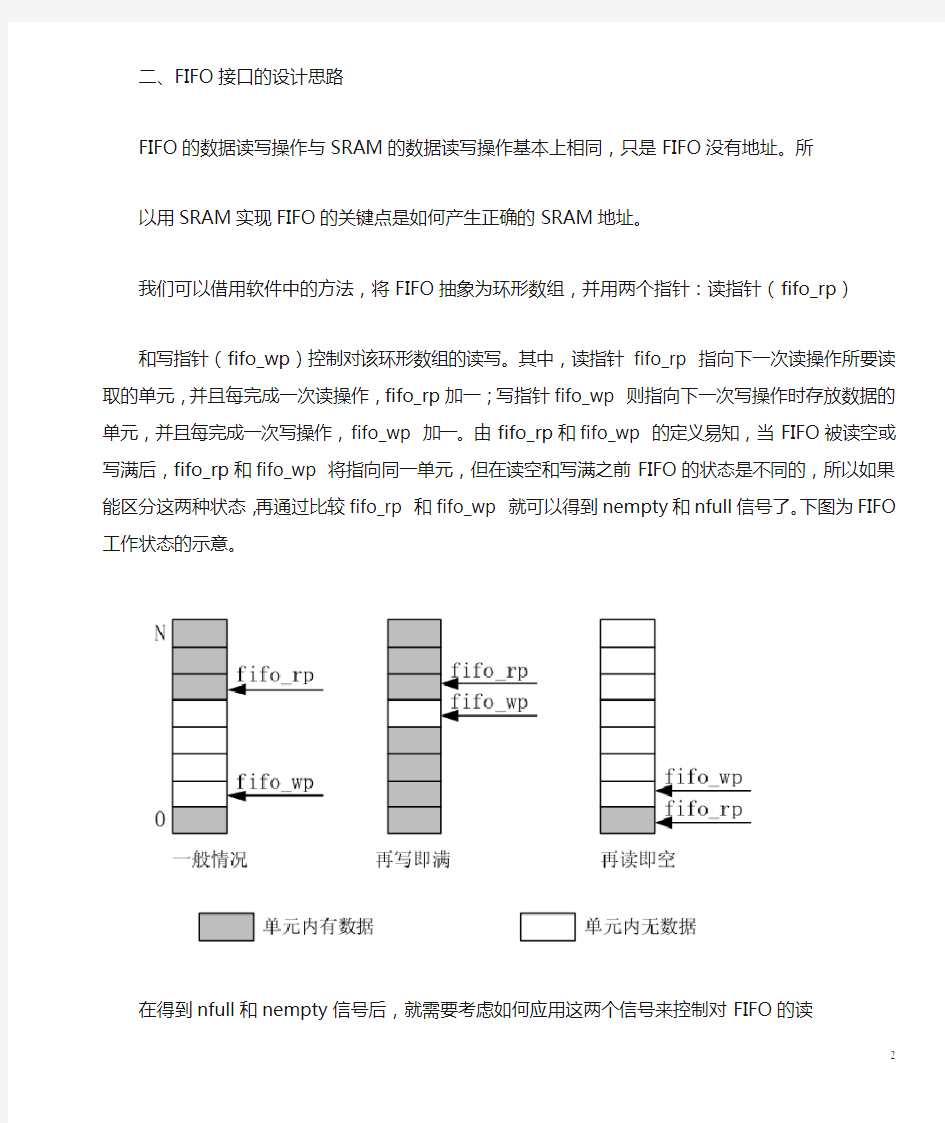

我们可以借用软件中的方法,将FIFO抽象为环形数组,并用两个指针:读指针(fifo_rp)和写指针(fifo_wp)控制对该环形数组的读写。其中,读指针fifo_rp 指向下一次读操作所要读取的单元,并且每完成一次读操作,fifo_rp加一;写指针fifo_wp 则指向下一次写操作时存放数据的单元,并且每完成一次写操作,fifo_wp 加一。由fifo_rp和fifo_wp 的定义易知,当FIFO被读空或写满后,fifo_rp和fifo_wp 将指向同一单元,但在读空和写满之前FIFO的状态是不同的,所以如果能区分这两种状态,再通过比较fifo_rp 和fifo_wp 就可以得到nempty和nfull信号了。下图为FIFO工作状态的示意。

在得到nfull和nempty信号后,就需要考虑如何应用这两个信号来控制对FIFO的读

写,使得FIFO在被写满后不能再写入,从而防止覆盖原有数据,并且在被读空后也不能再进行读操作,防止读取无效数据。

此外,在进SRAM读写操作时,应该注意建立地址、数据和控制信号的先后顺序。一

般情况下,希望对SRAM读写的波形时序如下图所示:

即写SRAM时,先建立地址和数据,然后置写使能信号WR有效,在WR保持有效一定时

间后,先复位WR,然后释放地址和数据总线。而读取SRAM时,则先建立地址,然后置

读使能RD有效,在RD维持有效一定时间后,复位RD,同时读取数据总线上的值,然后

再释放地址总线。在进行FIFO操作时,用户一般希望除了没有地址外,其它三个信号的时序关系能保持不变。请同学们在设计FIFO控制信号与SRAM控制信号间逻辑关系时注意这一点。

三、FIFO接口的测试

在完成一个设计后,需要进行测试以确认设计的正确性和完整性。而要进行测试,就需要编写测试激励和结果检查程序,即测试平台(testbench)。在某些情况下,如果设计的接口能够预先确定,测试平台的编写也可以在设计完成之前就进行,这样做的好处是在设计测试平台的同时也在更进一步深入了解设计要求,有助于理清设计思路,及时发现设计方案的错误。

编写测试激励时,除了注意对实际可能存在的各种情况的覆盖外,还要有意针对非正常情况下的操作进行测试。在本练习中,就应当进行在FIFO读空后继续读取、FIFO写满后

继续写入、FIFO复位后马上读取等操作的测试。

测试激励中通常会有一些复杂操作需要反复进行,如本练习中对FIFO的读写操作。这

时可以将这些复杂操作纳入到几个task 中,即减小了激励编写的工作量,也使得程序的可读性更好。

下面的测试程序给同学们做为参考,希望同学们能先用这段程序测试所设计的FIFO接口,然后编写自己更全面的测试程序。

`define FIFO_SIZE 8

`include “sram.v” // 有的仿真工具不需要加这句, 只要sram.v 模块编译过就可以了

`timescale 1ns/1ns

module t;

reg [7:0] in_data; //FIFO数据总线

reg fiford,fifowr; //FIFO控制信号

wire[7:0] out_data;

wire nfull, nempty; //FIFO状态信号

reg clk,rst;

wire[7:0] sram_data; //SRAM数据总线

wire[10:0] address; //SRAM的地址总线

wire rd,wr; //SRAM读写控制信号

reg [7:0] data_buf[`FIFO_SIZE:0]; //数据缓存,用于结果检查

integer index; //用于读写data_buf的指针

//系统时钟

initial clk=0;

always #25 clk=~clk;

//测试激励序列

initial

begin

fiford=1;

fifowr=1;

rst=1;

#40 rst=0;

#42 rst=1;

if (nempty) $display($time,"Error: FIFO be empty, nempty should be low.\n"); //连续写FIFO index = 0;

repeat(`FIFO_SIZE) begin

data_buf[index]=$random;

write_fifo(data_buf[index]);

index = index + 1;

end

if (nfull) $display($time,"Error: FIFO full, nfull should be low.\n");

repeat(2) write_fifo($random);

#200 //连续读FIFO

index=0;

read_fifo_compare(data_buf[index]);

if (~nfull) $display($time,"Error: FIFO not full, nfull should be high.\n");

repeat(`FIFO_SIZE-1) begin

index = index + 1;

read_fifo_compare(data_buf[index]);

end

if (nempty) $display($time,"Error: FIFO be empty, nempty should be low.\n");

repeat(2) read_fifo_compare(8'bx);

reset_fifo; //写后读FIFO

repeat(`FIFO_SIZE*2)

begin

data_buf[0] = $random;

write_fifo(data_buf[0]);

read_fifo_compare(data_buf[0]);

end //异常操作

reset_fifo;

read_fifo_compare(8'bx);

write_fifo(data_buf[0]);

read_fifo_compare(data_buf[0]);

$stop;

end

fifo_interface fifo_interface(

.in_data(in_data),.out_data(out_data),

.fiford(fiford),.fifowr(fifowr),

.nfull(nfull),.nempty(nempty),

.address(address),.sram_data(sram_data),

.rd(rd),.wr(wr),

.clk(clk),.rst(rst)

);

sram m1( .Address(address),

.Data(sram_data),

.SRG(rd), //SRAM 读使能

.SRE(1'b0), //SRAM 片选,低有效

.SRW(wr)); //SRAM写使能

task write_fifo;

input [7:0] data;

begin

in_data=data;

#50 fifowr=0; //往SRAM中写数

#200 fifowr=1;

#50;

end

endtask

task read_fifo_compare;

input [7:0] data;

begin

#50 fiford=0; //从SRAM中读数

#200 fiford=1;

if (out_data != data)

$display($time,"Error: Data retrieved (%h) not match the one stored (%h). \n",

out_data, data);

#50;

end

endtask

task reset_fifo;

begin

#40 rst=0;

#40 rst=1;

end

endtask

endmodule

4) FIFO接口的参考设计

FIFO接口的实现有多种方案,下面给出的参考设计只是其中一种。希望同学们在完成自己的设计后,和参考设计做一下比较。

`define SRAM_SIZE 8 //为减小对FIFO控制器的测试工作量,置SRAM空间为8Byte

`timescale 1ns/1ns

module fifo_interface(

in_data, //对用户的输入数据总线

out_data, //对用户的输出数据总线,

fiford, //FIFO读控制信号,低电平有效

fifowr, //FIFO写控制信号,低电平有效

nfull,

nempty,

address, //到SRAM的地址总线

sram_data, //到SRAM的双向数据总线

rd, //SRAM读使能,低电平有效

wr, //SRAM写使能,低电平有效

clk, //系统时钟信号

rst); //全局复位信号,低电平有效

//来自用户的控制输入信号

input fiford, fifowr, clk, rst;

//来自用户的数据信号

input[7:0] in_data;

output[7:0] out_data;

reg[7:0] in_data_buf, //输入数据缓冲区

out_data_buf; //输出数据缓冲区

//输出到用户的状态指示信号

output nfull, nempty;

reg nfull, nempty; //输出到SRAM的控制信号output rd, wr;

//到SRAM的双向数据总线

inout[7:0] sram_data; //输出到SRAM的地址总线

output[10:0] address;

reg[10:0] address;

//Internal Register

reg[10:0] fifo_wp, //FIFO写指针

fifo_rp; //FIFO读指针

reg[10:0] fifo_wp_next, //fifo_wp的下一个值

fifo_rp_next; //fifo_rp的下一个值

reg near_full, near_empty;

reg[3:0] state; //SRAM 操作状态机寄存器parameter idle = 'b0000,

read_ready = 'b0100,

read = 'b0101,

read_over = 'b0111,

write_ready = 'b1000,

write = 'b1001,

write_over = 'b1011;

//SRAM 操作状态机

always @(posedge clk or negedge rst)

if (~rst)

state <= idle;

else

case(state)

idle: //等待对FIFO的操作控制信号

if (fifowr==0 && nfull) //用户发出写FIFO申请,且FIFO未满

state<=write_ready;

else if(fiford==0 && nempty)//用户发出读FIFO申请,且FIFO未空

state<=read_ready;

else //没用对FIFO操作的申请

state<=idle;

read_ready: //建立SRAM操作所需地址和数据

state <= read;

read: //等待用户结束当前读操作

if (fiford == 1)

state <= read_over;

else

state <= read;

read_over: //继续给出SRAM地址以保证数据稳定state <= idle;

write_ready: //建立SRAM操作所需地址和数据

state <= write;

write: //等待用户结束当前写操作

if (fifowr == 1)

state <= write_over;

else

state <= write;

write_over: //继续给出SRAM地址和写入数据以保证数据稳定

state <= idle;

default: state<=idle;

endcase

//产生SRAM操作相关信号

assign rd = ~state[2]; //state为read_ready 或read或read_over

assign wr = (state == write) ? fifowr : 1'b1;

always @(posedge clk)

if (~fifowr)

in_data_buf <= in_data;

assign sram_data = (state[3]) ? //state为write_ready或write或write_over

in_data_buf : 8'hzz;

always @(state or fiford or fifowr or fifo_wp or fifo_rp)

if (state[2] || ~fiford)

address = fifo_rp;

else if (state[3] || ~fifowr)

address = fifo_wp;

else

address = 'bz;

//产生FIFO数据

assign out_data = (state[2]) ?

sram_data : 8'bz;

always @(posedge clk)

if (state == read)

out_data_buf <= sram_data;

//计算FIFO读写指针

always @(posedge clk or negedge rst) if (~rst)

fifo_rp <= 0;

else if (state == read_over)

fifo_rp <= fifo_rp_next;

always @(fifo_rp)

if (fifo_rp == `SRAM_SIZE-1)

fifo_rp_next = 0;

else

fifo_rp_next = fifo_rp + 1; always @(posedge clk or negedge rst) if (~rst)

fifo_wp <= 0;

else if (state == write_over)

fifo_wp <= fifo_wp_next; always @(fifo_wp)

if (fifo_wp == `SRAM_SIZE-1)

fifo_wp_next = 0;

else

fifo_wp_next = fifo_wp + 1; always @(posedge clk or negedge rst) if (~rst)

near_empty <= 1'b0;

else if (fifo_wp == fifo_rp_next)

near_empty <= 1'b1;

else

near_empty <= 1'b0;

always @(posedge clk or negedge rst) if (~rst)

nempty <= 1'b0;

else if (near_empty && state == read) nempty <= 1'b0;

else if (state == write)

nempty <= 1'b1;

always @(posedge clk or negedge rst) if (~rst)

near_full <= 1'b0;

else if (fifo_rp == fifo_wp_next)

near_full <= 1'b1;

else

near_full <= 1'b0;

always @(posedge clk or negedge rst) if (~rst)

nfull <= 1'b1;

else if (near_full && state == write) nfull <= 1'b0;

else if (state == read)

nfull <= 1'b1;

endmodule

XFP模块电路设计 一、应用要求 1、多速率应用:TELECOM(SONET OC-192 and G.709 “OTU-2”) DATACOM(10 Gb/s Ethernet and 10 Gb/s Fibre Channel) 2、XFI(9.95Gb/s~11.7Gb/s)高速信号可以在改良的FR4电路板上传输 300mm或普通的FR4电路板上传输200mm。 3、热插拔智能化,能够提供模块的实时工作状态的监视值 二、指标要求 3、封装结构:按照XFP-MSA的要求 三、方案选择 1、发射器件的选择:采用公司成熟的TO封装工艺开发的发射器件。 2、接收组件的选择:采用公司成熟的TO封装工艺开发的接收组件。

四、电路设计 1、原理框图 LOS Data In TxDis SCL SDA TxFault

2、原理图设计 3、PCB设计 (1)传输线设计: 在PCB设计中采用微带线来进行信号传输,保证高深信号在PCB上传输不发生波形畸变,我们通过AppCAD模拟可得到微带线的宽度和各微带线之间的间距。在10Gb/s的工作速率下,信号波长已经可以与器件尺寸相比拟,基于电路性能、器件选择和电磁兼容等因素的考虑,必须以网络散射分析(S参数)、信号完整性分析、电磁仿真分析、电路仿真分析等手段,来综合考量实际电路系统的工作性能。对电路板、元器件进行结构性电磁仿真并精确提取相应的SPICE电路模型参数,作为电路设计的依据,以此有效减小电感器件在高频设计应用中的误差影响。而且现在国外的产品技术参数大多包含有S参数,通常可用于精确的高频应用分析。信号传输微带线的等效分析见下图。

综合:不可综合的运算符:= = = ,!= =,/(除法),%(取余数)。 1、不使用初始化语句。 2、不使用带有延时的描述。 3、不使用循环次数不确定的循环语句,如:forever、while等。 4、尽量采用同步方式设计电路。 5、除非是关键路径的设计,一般不调用门级元件来描述设计的方法,建议采用行为语句来完成设计。 6、用always过程块描述组合逻辑,应在信号敏感列表中列出所有的输入信号。 7、所有的内部寄存器都应该能够被复位,在使用FPGA实现设计时,应尽量使用器件的全局复位端作为系统总的复位。 8、在verilog模块中,任务(task)通常被综合成组合逻辑的形式,每个函数(function)在调用时通常也被综合为一个独立的组合电路模块。 9、用户自定义原语(UDP)是不可综合的,它只能用来建立门级元件的仿真模型。 一般综合工具支持的V erilog HDL结构

移位运算符:V erilog HDL提供向右(>>)及向左(<<)两种运算符,运算符高位或地位一旦移出即予丢弃,其空缺的位则予以补零。 连续赋值语句(assign)、case语句、if…else语句都是可以综合的 initial 语句内若包含有多个语句时,必须以begin end 作聚合;单一的初值赋值,因此并不需以begin end做聚合。 循环(Loops)并不能单独地在程序中存在,而必须在initial和always块中才能使用。initial过程块中的语句仅执行一次,而always块中的语句是不断重复执行的。 编写顶层模块的注意事项 每个端口除了要声明是输入、输出还是双向外,还要声明其数据类型,是连线型(wire)还是寄存器型(reg),如果没有声明则综合器默认为wire型。 1、输入和双向端口不能声明为寄存器型。 2、在测试模块中不需要定义端口。 编写testbentch所归纳的心得

基于MRF24J40的IEEE802.15.4无线收发电 路设计 时间:2010-11-30 19:05:33 来源:作者:黄智伟何娜 IEEE802.15.4无线收发器MRF24J40芯片内部包含有SPI接口、控制寄存器、MAC 模块、PHY驱动器四个主要的功能模块,支持IEEE802.15.4,MiWiTM,ZigBee等协议,工作在2.405~2.48 GHz ISM频段,接收灵敏度为-91 dBm,最大输入电平为+5 dBm,输出功率为+0 dBm,功率控制范围为38.75 dB,集成有20 MHz和32.768 kHz主控振荡器,MAC/基带部分采用硬件CSMA-CA结构,自动ACK6和FCS检测,CTR、CCM和CBC-MAC 模式采用硬件加密(AES-128),电源电压范围为2.4~3.6 V,接收模式电流消耗为18 mA,发射模式电流消耗为22 mA,睡眠模式电流消耗为2μA。 MRF24J40采用6 mm×6 mm QFN-40封装,引脚端封装形式如图1所示。图中:引脚端RFP和RFN分别为芯片的RF差分输入/输出正端和负端,两者都是模拟输入/输出端口,与系统天线相连接;VDD为电源电压输入引脚端,每个电源电压输入引脚端都必须连接一个电源去耦电容;GND为接地引脚端,必须低阻抗的连接到电路的接地板;GPIOO~GPIO5是通用数字I/O口,其中GPIO0也被用来作为外部功率放大器使能控制,GPIO1和GPIO2也被用来作为外部TX/RX开关控制;RESET为复位引脚端,低电平有效;WAKE为外部唤醒触发输入端;INT为到微控制器的中断引脚端;SDO,SDI,SCK和CS是MRF24J40的SPI接口输入输出引脚端,其中SDO是MRF24J40的串行数据输出,SDI是MRF24J40的串行接口数据输入,SCK是串行接口的时钟,CS是串行接口使能控制引脚端;LPOSC1和LPOSC2为32 kHz晶振输入正端和负端;OSC1和OSC2为20 MHz晶振输入正端和负端;CLKOUT为20/10/5/2.5 MHz时钟输出端;LCAP引脚端用来连接一个180 pF的PLL环路滤波器电容;XIP和RXQP为接收I通道和Q通道输出正端。 2 MRF24J40构成的IEEE802.15.4无线收发电路 MRF24J40构成的IEEE802.15.4无线收发电路如图2所示,各电源电压引脚端根据需要分

时序是设计出来的 我的boss有在华为及峻龙工作的背景,自然就给我们讲了一些华为及altera 做逻辑的一些东西,而我们的项目规范,也基本上是按华为的那一套去做。在工作这几个月中,给我感触最深的是华为的那句话:时序是设计出来的,不是仿出来的,更不是湊出来的。 在我们公司,每一个项目都有很严格的评审,只有评审通过了,才能做下一步的工作。以做逻辑为例,并不是一上来就开始写代码,而是要先写总体设计方案和逻辑详细设计方案,要等这些方案评审通过,认为可行了,才能进行编码,一般来说这部分工作所占的时间要远大于编码的时间。 总体方案主要是涉及模块划分,一级模块和二级模块的接口信号和时序(我们要求把接口信号的时序波形描述出来)以及将来如何测试设计。在这一级方案中,要保证在今后的设计中时序要收敛到一级模块(最后是在二级模块中)。什么意思呢?我们在做详细设计的时候,对于一些信号的时序肯定会做一些调整的,但是这种时序的调整最多只能波及到本一级模块,而不能影响到整个设计。记得以前在学校做设计的时候,由于不懂得设计时序,经常因为有一处信号的时序不满足,结果不得不将其它模块信号的时序也改一下,搞得人很郁闷。 在逻辑详细设计方案这一级的时候,我们已经将各级模块的接口时序都设计出来了,各级模块内部是怎么实现的也基本上确定下来了。 由于做到这一点,在编码的时候自然就很快了,最重要的是这样做后可以让设计会一直处于可控的状态,不会因为某一处的错误引起整个设计从头进行。 ==================================================================== 如何提高电路工作频率 对于设计者来说,我们当然希望我们设计的电路的工作频率(在这里如无特别说明,工作频率指FPGA片内的工作频率)尽量高。我们也经常听说用资源换速度,用流水的方式可以提高工作频率,这确实是一个很重要的方法,今天我想进一步去分析该如何提高电路的工作频率。 我们先来分析下是什么影响了电路的工作频率。 我们电路的工作频率主要与寄存器到寄存器之间的信号传播时延及 clock skew有关。在FPGA内部如果时钟走长线的话,clock skew很小,基本上可以忽略, 在这里为了简单起见,我们只考虑信号的传播时延的因素。 信号的传播时延包括寄存器的开关时延、走线时延、经过组合逻辑的时延(这样划分或许不是很准确,不过对分析问题来说应该是没有可以的),要提高电路的工作频率,我们就要在这三个时延中做文章,使其尽可能的小。 我们先来看开关时延,这个时延是由器件物理特性决定的,我们没有办法去改变,所以我们只能通过改变走线方式和减少组合逻辑的方法来提高工作频率。

个人总结Verilog编程27条经验 1.强烈建议用同步设计; 2.在设计时总是记住时序问题; 3.在一个设计开始就要考虑到地电平或高电平复位、同步或异步复位、上升沿 或下降沿触发等问题,在所有模块中都要遵守它; 4.在不同的情况下用if和case,最好少用if的多层嵌套(1层或2层比较合 适,当在3层以上时,最好修改写法,因为这样不仅可以reduce area,而且可以获得好的timing); 5.在锁存一个信号或总线时要小心,对于整个design,尽量避免使用latch, 因为在DFT时很难test; 6.确信所有的信号被复位,在DFT时,所有的FlipFlop都是controllable; 7.永远不要再写入之前读取任何内部存储器(如SRAM); 8.从一个时钟到另一个不同的时钟传输数据时用数据缓冲,他工作像一个双时 钟FIFO(是异步的),可以用Async SRAM搭建Async FIFO; 9.在VHDL中二维数组可以使用,它是非常有用的。在VERILOG中他仅仅可以使 用在测试模块中,不能被综合; 10.遵守register-in register-out规则; 11.像synopsys的DC的综合工具是非常稳定的,任何bugs都不会从综合工具中 产生 12.确保FPGA版本与ASIC的版本尽可能的相似,特别是SRAM类型,若版本一致 是最理想的,但是在工作中FPGA版本一般用FPGA自带的SRAM,ASIC版本一般用厂商提供的SRAM; 13.在嵌入式存储器中使用BIST; 14.虚单元和一些修正电路是必需的; 15.一些简单的测试电路也是需要的,经常在一个芯片中有许多测试模块; 16.除非低功耗不要用门控时钟,强烈建议不要在design中使用gate clock; 17.不要依靠脚本来保证设计。但是在脚本中的一些好的约束能够起到更好的性 能(例如前向加法器); 18.如果时间充裕,通过时钟做一个多锁存器来取代用MUX; 19.不要用内部tri-state, ASIC需要总线保持器来处理内部tri-state,如IO cell; 20.在top level中作pad insertion; 21.选择pad时要小心(如上拉能力,施密特触发器,5伏耐压等),选择合适的 IO cell; 22.小心由时钟偏差引起的问题; 23.不要试着产生半周期信号; 24.如果有很多函数要修正,请一个一个地作,修正一个函数检查一个函数; 25.在一个计算等式中排列每个信号的位数是一个好习惯,即使综合工具能做; 26.不要使用HDL提供的除法器; 27.削减不必要的时钟。它会在设计和布局中引起很多麻烦,大多数FPGA有1- 4个专门的时钟通道;

【例3.1】4位全加器 module adder4(cout,sum,ina,inb,cin); output[3:0] sum; output cout; input[3:0] ina,inb; input cin; assign {cout,sum}=ina+inb+cin; endmodule 【例3.2】4位计数器 module count4(out,reset,clk); output[3:0] out; input reset,clk; reg[3:0] out; always @(posedge clk) begin if (reset) out<=0; //同步复位 else out<=out+1; //计数 end endmodule 【例3.3】4位全加器的仿真程序 `timescale 1ns/1ns `include "adder4.v" module adder_tp; //测试模块的名字 reg[3:0] a,b; //测试输入信号定义为reg型 reg cin; wire[3:0] sum; //测试输出信号定义为wire型 wire cout; integer i,j; adder4 adder(sum,cout,a,b,cin); //调用测试对象 always #5 cin=~cin; //设定cin的取值 initial begin a=0;b=0;cin=0; for(i=1;i<16;i=i+1) #10 a=i; //设定a的取值 end - 1 -

initial begin for(j=1;j<16;j=j+1) #10 b=j; //设定b的取值 end initial//定义结果显示格式 begin $monitor($time,,,"%d + %d + %b={%b,%d}",a,b,cin,cout,sum); #160 $finish; end endmodule 【例3.4】4位计数器的仿真程序 `timescale 1ns/1ns `include "count4.v" module coun4_tp; reg clk,reset; //测试输入信号定义为reg型 wire[3:0] out; //测试输出信号定义为wire型 parameter DELY=100; count4 mycount(out,reset,clk); //调用测试对象 always #(DELY/2) clk = ~clk; //产生时钟波形 initial begin//激励信号定义 clk =0; reset=0; #DELY reset=1; #DELY reset=0; #(DELY*20) $finish; end //定义结果显示格式 initial $monitor($time,,,"clk=%d reset=%d out=%d", clk, reset,out); endmodule 【例3.5】“与-或-非”门电路 module AOI(A,B,C,D,F); //模块名为AOI(端口列表A,B,C,D,F) input A,B,C,D; //模块的输入端口为A,B,C,D output F; //模块的输出端口为F - 2 -

实验四串口接收模块电路设计 一、实验目的: 1、熟练使用ISE设计工具。 2、理解串口传输协议。理解采用“自顶向下”设计思路,分解模块的方法。 3、在ISE使用Verilog HDL设计串口接收模块,完成仿真、下载。 二、原理分析 (一)串口传输协议概述 设计完成异步串口通信通用异步收发是一种典型的异步串口通信,简称UART。串口通信时序如图1所示。 图1 通用异步收发时序图 由图1可以看出,在没有数据传送时,通信线会一直处于高电平,即逻辑1状态;当有数据传送时,数据帧以起始位开始,以停止位结束。起始位为低电平,即逻辑0状态;停止位为高电平,即逻辑1状态,其持续时间可选为1位、1.5位或2位(本次设计选择持续时间1位)。接收端在接收到停止位后,知道一帧数据已经传完,转为等待数据接收状态;只要再接收到0状态,即为新一帧数据的起始状态。 数据帧的数据位低位(LSB)在前,高位(MSB)在后,根据不同的编码规则,数据位可能为5位、6位、7位或者8位(本次设计数据位定位8位)。校验位也可根据需要选择奇校验、偶校验或者不要校验(本次设计不要校验位)。 (二)串口时序分析 串口通讯常用“波特率”表述串口传输速率,常用的参数有9600 bps 和115200 bps等。在硬件传输角度看,波特率表征了传输一位数据所需要的时间。例如:波特率是9600 bps,传输一位数据的时间是1/9600= 0.000104166666666667秒。如果FPGA系统时钟是20MHZ,则一位数据传输时间相当于(1/9600)/(1/20M)=2083个20MHZ时钟周期。 设一帧数据位数=1(开始位)+8(数据位)+1(校验位)+1(结束位)=11位,所以传输一帧数据的时间是11*1/9600=0.00114583333333333333333333333333秒。 为了稳定采集串口数据帧的数据,需要在每位数据的“中间时刻”采样,由此,需要在每位数据开始时刻对时钟进行计数,若系统时钟是20MHZ,则在计数至2083/2=1042时采样此时刻的数值。 三、系统分析: 为实现串口接收电路,FPGA应该完成: 1、及时发现数据传输的开始,并判断每一位的开始。 2、按照“在数据位中间采样”的要求,确认采样时刻。 3、将采样得到串行数据转换为并行数据。

电源电路单元 前面介绍了电路图中的元器件的作用和符号。一张电路图通常有几十乃至几百个元器件,它们的连线纵横交叉,形式变化多端,初学者往往不知道该从什么地方开始,怎样才能读懂它。其实电子电路本身有很强的规律性,不管多复杂的电路,经过分析可以发现,它是由少数几个单元电路组成的。好象孩子们玩的积木,虽然只有十来种或二三十种块块,可是在孩子们手中却可以搭成几十乃至几百种平面图形或立体模型。同样道理,再复杂的电路,经过分析就可发现,它也是由少数几个单元电路组成的。因此初学者只要先熟悉常用的基本单元电路,再学会分析和分解电路的本领,看懂一般的电路图应该是不难的。 按单元电路的功能可以把它们分成若干类,每一类又有好多种,全部单元电路大概总有几百种。下面我们选最常用的基本单元电路来介绍。让我们从电源电路开始。 一、电源电路的功能和组成 每个电子设备都有一个供给能量的电源电路。电源电路有整流电源、逆变电源和变频器三种。常见的家用电器中多数要用到直流电源。直流电源的最简单的供电方法是用电池。但电池有成本高、体积大、需要不时更换(蓄电池则要经常充电)的缺点,因此最经济可靠而又方便的是使用整流电源。 电子电路中的电源一般是低压直流电,所以要想从 220 伏市电变换成直流电,应该先把220 伏交流变成低压交流电,再用整流电路变成脉动的直流电,最后用滤波电路滤除脉动直流电中的交流成分后才能得到直流电。有的电子设备对电源的质量要求很高,所以有时还需要再增加一个稳压电路。因此整流电源的组成一般有四大部分,见图 1 。其中变压电路其实就是一个铁芯变压器,需要介绍的只是后面三种单元电路。 二、整流电路 整流电路是利用半导体二极管的单向导电性能把交流电变成单向脉动直流电的电路。 ( 1 )半波整流 半波整流电路只需一个二极管,见图 2 ( a )。在交流电正半周时 VD 导通,负半周时 VD 截止,负载 R 上得到的是脉动的直流电

verilog学习心得 1.数字电路基础知识:布尔代数、门级电路的内部晶体管结构、组合逻辑电路分析与设计、触发器、时序逻辑电路分析与设计 2.数字系统的构成:传感器AD 数字处理器DA 执行部件 3.程序通在硬件上的执行过程: C语言(经过编译)-->该处理器的机器语言(放入存储器)-->按时钟的节拍,逐条取出指令、分析指令、执行指令 4.DSP处理是个广泛概念,统指在数字系统中做的变换(DFT)、滤波、编码解码、加密解密、压缩解压等处理 5.数字处理器包括两部分:高速数据通道接口逻辑、高速算法电路逻辑 6.当前,IC产业包括IC制造和IC设计两部分,IC设计技术发展速度高于IC设计 7.FPGA设计的前续课程:数值分析、DSP、C语言、算法与数据结构、数字电路、HDL语言计算机微体系结构 8.数字处理器处理性能的提高:软件算法的优化、微体系结构的优化 9.数字系统的实现方式: 编写C程序,然后用编译工具得到通用微处理器的机器指令代码,在通用微处理器上运行(如8051/ARM/PENTUIM) 专用DSP硬件处理器 用FPGA硬件逻辑实现算法,但性能不如ASIC 用ASIC实现,经费充足、大批量的情况下使用,因为投片成本高、周期长 10.FPGA设计方法:IP核重用、并行设计、层次化模块化设计、top-down思想 FPGA设计分工:前端逻辑设计、后端电路实现、仿真验证 11.matlab的应用: matlab中有许多现成的数学函数可以利用,节省了复杂函数的编写时间 matlab可以与C程序接口 做算法仿真和验证时能很快生成有用的数据文件和表格 DSP builder可以直接将simulink模型转换成HDL代码,跳过了中间的C语言改写步骤 12.常规从算法到硬件电路的开发过程: 算法的开发 C语言的功能描述 并行结构的C语言改写 verilog的改写 仿真、验证、修正 综合、布局布线、投入实用 13.C语言改写成verilog代码的困难点: 并行C语言的改写,因为C本身是顺序执行,而不是并行执行 不使用C语言中的复杂数据结构,如指针 目前有将C语言转换成verilog的工具? 14.HDL HDL描述方法是从电路图描述方法演化来的,相比来说更容易修改 符合IEEE标准的有verilog HDL和VHDL VHDL由美国国防部开发,有1987和1993两个版本 verilog由cadence持有,有1995、2001、2005三个版本 verilog较VHDL更有前景:具有模拟电路描述能力、不仅可以开发电路还可以验证电路、门级以下描述比VHDL强

5v电源电路的设计 本设计是要设计一个+5V直流电源供电,这里没有直接的+5V电压,而直流电源的输入电压为220V的电网电压,在正常情况下,这一电网电压是远远的高于本设计所需的电压值,因而需要先使用变压器,将220V的电网电压降低后,再进行下一阶段的处理[4]。 变压器是这一电源电路起始部分,将220V的电网电压转变为本设计所需的较低的电压,就可以进行下一阶段的整流部分。一般规定v1为变压器的高压侧,v2为变压器的低压侧,v1侧的线圈要比v2侧的线圈要多,这样就可以将220V 的电网电压降低,如图1所示: 图1变压器 单相桥式整流电路,就是将交流电网电压转换为所需电压,整流电路由四只整流二极管组成。下面简单介绍一下单相桥式整流电路的工作原理,为简便起见,这里所选的二极管都是理想的二极管,二极管正向导通时电阻为零,反向导通时电阻无穷大。在v2的正半周,电流从变压器副边线圈的上端流出,经过二极管D1,再由二极管D4流回变压器,所以D1、D4正向导通,D2、D3反向截止,产生一个极性为上正下负的输出电压。在v2的负半周,其极性正好相反,电流从变压器副边线圈的下端流出,经过二极管D2,再由二极管D3流回变压器,所以D1、D4反向截止,D2、D3正向导通。桥式整流电路利用了二极管的单向导电性,利用四个二极管,是它们交替导通,从而负载上始终可以得到一个单方向的脉动电压[6]。单相桥式整流电路如图2所示:

图2单相桥式整流电路 本设计的滤波电路采用的是电解电容和二极管并联方式滤波,简单的讲就是电容两端电压升高时,电容充电,电压降低时,电容放电,让电压降低时的坡度变得平缓,从而起到滤波的作用。这里选用电解电容是因为电解电容单位体积的电容量非常大,能比其它种类的电容大几十到数百倍,并且其额定的容量可以做到非常大,价格比其它种类相比具有相当大的优势,因为其组成材料都是普通的工业材料,比如铝等等。电解电容并联二极管,有效防止了电压反相。滤波电路如图3所示: 图3滤波电路 三端稳压器MC78M05CT将输出电压稳定在+5V上,三端稳压器如图4所示:

xx学院综合性实验报告 一、实验目的 使用Altium Designer设计一个基于ENC28j60的网络通信模块。 二、实验仪器或设备 1.一台计算机。 2.Altium Designer软件。 三、总体设计 (一)新建工程 (二)元件的制作 2.1.制作ENC28j60芯片的封状 2.2.制作HR911105模块的封装 (三)绘制电路原理图 3.1.系统供电电路 3.2.ENC28j60通信电路 3.3.HR911105网络接口电路

(四)电路原理图的后续操作 4.3.元件的标注 4.4.更改元器件的PCB封装 4.5.原理图的编译与查错 4.6.生成元器件报表 4.7.生成网络报表 (五)绘制PCB电路板 5.1.规划电路板 5.2.装入网络表和元件封装 5.3.元件的布局 5.4.自动布线 5.5.手工修改布线 (六)PCB设计的后续操作 6.1.重新定义电路板形状 6.2.覆铜 6.3.字符串信息整理 6.4.DRC检查 6.5.打印电路图 6.6.打印PDF文档 四、实验步骤 1.新建工程

执行【File】|【New】|【Project】|【PCB Project】命令,新建一个空白的工程文件,并将其保存在网络通信文件夹下,重新命名为“ENC28j60.PrjPCB”。 执行【File】|【New】|【Schematic】命令,新建一个空白的原理图设计文件,命名为“ENC28j60.SchDoc”。 2.元件的制作 2.1 制作ENC28j60芯片的封状 执行菜单命令【File】|【New】|【Library】|【Schematic Library】,新建库文件,命名为“ENC28j60.SchLib”并保存; ?执行菜单命令【Tools】|【New Component】,在弹出的对话框中将新建的元件命名为 ENC28j60; 图 2 添加元件 ?执行菜单命令【Place】|【Rectangle】在绘图区绘制一个大小合适的矩形; ?执行菜单命令【Place】|【Pin】放置管脚,ENC28j60 共有 28 个管脚。

相位超前的RC移相式振荡电路图 简单实用的开关电源电路 12v开关电源电路图 12v开关电源电路图 +12V、0.5A单片开关稳压电源的电路如图所示。其输出功率为6W。当输入交流电压在110~260V 范围内变化时,电压调整率Sv≤1%。当负载电流大幅度变化时,负载调整率SI=5%~7%。为简化电路,这里采用了基本反馈方式。

接通电源后,220V交流电首先经过桥式整流和C1滤波,得到约+300V的直流高压,再通过高频变压器的初级线圈N1,给WSl57提供所需的工作电压。从次级线圈N2上输出的脉宽调制功率信号,经VD7、C4、L和C5进行高频整流滤波,获得+12V、0.5A的稳压输出。反馈线圈N3上的电压则通过VD6、R2、C3整流滤波后,将控制电流加至控制端C上。由VD5、R1,和C2构成的吸收回路,能有效抑制漏极上的反向峰值电压。该电路的稳压原理分析如下:当由于某种原因致使Uo↓时,反馈线圈电压及控制端电流也随之降低,而芯片内部产生的误差电压Ur↑时,PWM比较器输出的脉冲占空比D ↑,经过MOSFET和降压式输出电路使得Uo↑,最终能维持输出电压不变。反之亦然。 单端反激开关电源变压器设计总结 单端反激开关电源的变压器实质上是一个耦合电感,它要承担着储能、变压、传递能量等工作。下面对工作于连续模式和断续模式的单端反激变换器的变压器设计进行了总结。 1、已知的参数 这些参数由设计人员根据用户的需求和电路的特点确定,包括:输入电压Vin、输出电压Vout、每路输出的功率Pout、效率η、开关频率fs(或周期T)、线路主开关管的耐压Vmos。 2、计算 在反激变换器中,副边反射电压即反激电压Vf与输入电压之和不能高过主开关管的耐压,同时还要留有一定的裕量(此处假设为150V)。反激电压由下式确定:Vf=VMos-VinDCMax-150V 反激电压和输出电压的关系由原、副边的匝比确定。所以确定了反激电压之后,就可以确定原、副边的匝比了。 Np/Ns=Vf/Vout

、不使用初始化语句; 2、不使用延时语句; 3、不使用循环次数不确定的语句,如:forever,while等; 4、尽量采用同步方式设计电路; 5、尽量采用行为语句完成设计; 6、always过程块描述组合逻辑,应在敏感信号表中列出所有的输入信号; 7、所有的内部寄存器都应该可以被复位; 8、用户自定义原件(UDP元件)是不能被综合的。 一:基本 Verilog中的变量有线网类型和寄存器类型。线网型变量综合成wire,而寄存器可能综合成WIRE,锁存器和触发器,还有可能被优化掉。 二:verilog语句结构到门级的映射 1、连续性赋值:assign 连续性赋值语句逻辑结构上就是将等式右边的驱动左边的结点。因此连续性赋值的目标结点总是综合成由组合逻辑驱动的结点。Assign语句中的延时综合时都将忽视。 2、过程性赋值: 过程性赋值只出现在always语句中。 阻塞赋值和非阻塞赋值就该赋值本身是没有区别的,只是对后面的语句有不同的影响。 建议设计组合逻辑电路时用阻塞赋值,设计时序电路时用非阻塞赋值。 过程性赋值的赋值对象有可能综合成wire, latch,和flip-flop,取决于具体状况。如,时钟控制下的非阻塞赋值综合成flip-flop。 过程性赋值语句中的任何延时在综合时都将忽略。 建议同一个变量单一地使用阻塞或者非阻塞赋值。 3、逻辑操作符: 逻辑操作符对应于硬件中已有的逻辑门,一些操作符不能被综合:===、!==。 4、算术操作符:

Verilog中将reg视为无符号数,而integer视为有符号数。因此,进行有符号操作时使用integer,使用无符号操作时使用reg。 5、进位: 通常会将进行运算操作的结果比原操作数扩展一位,用来存放进位或者借位。如: Wire [3:0] A,B; Wire [4:0] C; Assign C=A+B; C的最高位用来存放进位。 6、关系运算符: 关系运算符:<,>,<=,>= 和算术操作符一样,可以进行有符号和无符号运算,取决于数据类型是reg,net还是integer。 7、相等运算符:==,!= 注意:===和!==是不可综合的。 可以进行有符号或无符号操作,取决于数据类型 8、移位运算符: 左移,右移,右边操作数可以是常数或者是变量,二者综合出来的结果不同。 9、部分选择: 部分选择索引必须是常量。 10、BIT选择: BIT选择中的索引可以用变量,这样将综合成多路(复用)器。 11、敏感表: Always过程中,所有被读取的数据,即等号右边的变量都要应放在敏感表中,不然,综合时不能正确地映射到所用的门。 12、IF: 如果变量没有在IF语句的每个分支中进行赋值,将会产生latch。如果IF语句中产生了latch,则IF的条件中最好不要用到算术操作。Case语句类似。Case的条款可以是变量。 如果一个变量在同一个IF条件分支中先赎值然后读取,则不会产生latch。如果先读取,后赎值,则会产生latch。

一、整流稳压滤波电路: 1.电路图: 2.所用元件 整流二极管IN4007 四只 三端稳压器7805 一只 电解电容1000μF/16V 一只 470μF/16V 一只 瓷片电容0.1μF 两只 电阻470Ω一只 发光二极管Φ3 一只 3.电路原理: 220v交流电压经过变压器变为9v交流电压后,通过四个二极管组成的桥式整流电路变为10v左右的脉动直流电压,再利用电解电容组成滤波电路将其变为平滑的直流电压,再经三端稳压器组成的稳压电路使得输出为较稳定的5v直流电压(D5亮)。(波形见模电P502) 4.元件介绍: 1.二极管:具有单向导电性 ⑴.二极管的引脚的区分: ①.整流二极管引脚有“+”,“―”之分,在二极管外壳上一般有标记 端为“―”,另一端无标记的为“+”。 ②.发光二极管新的一般长引脚为“+”,短引脚端为“―”。如两脚同 长,与发光二极管圆柱体平口相近的引脚为“―”,另一引脚则为“+”。 ③.用数字万用表对二极管引脚的判断:将数字万用表测量档拨至“” 档,表笔接通两个引脚,如数字万用表无显示,则黑表笔接的引脚为“+”,红表笔接的引脚为“―”。如数字万用表有显示,则黑表笔接的引脚为 “―”,红表笔接的引脚为“+”。 ⑵.安装方法:采用“卧式”安装方法,要紧贴安装板面。注意板面上指示 的安装方向,有标志的地方接二极管“-”端,切不可装错方向。多个应排列整齐。 2.三端稳压器:一种起稳压作用的集成稳压块。78表示该集成块系列,也表示该集成块系列输出为正电压。05表示该集成块输出为5v电压。该系列输出固定的正电压有5、8、12、15、18及24v。79系列输出为负电压。 ⑴.三端稳压器的引脚的区分:正看有标有型号的一面,在左边的为输入 脚“1”,中间为接地脚“2”,右边为输出脚“3”。 ⑵.安装方法:既可采用“卧式”安装方法,也可采用“立式”安装方法。

功能电路 1、DA转换电路 题目要求信号发生器的频率从100Hz到10KHz,对DA转换速度要求不是很高,但设计要求电压值误差绝对值小于1%,所以应选用转换精度高的芯片。本系统使用12位D/A转换芯片MX7541的双极性电路接法,电路图如图所示 2、峰值检波电路 峰值检波电路是由二极管电路和电压跟随器组成,其工作原理为:当输入电压正半周通过时,检波管U2导通,对电容C1、C2充电,直到到达其峰值。三极管的基极由单片机或FPGA控制,产生10us的高电平使电容放电,以减少前一频率测量对后一频率测量的影响,提高幅值测量精度。其中U1为常导通,用以补偿U2上造成的压降。电容C1、C2的取值需根据被测信号的频率合适的选取,此电路中的二极管使用高频二极管,可大大提高测量范围的频率上限。 3、真有效值检测电路设计 对于有效值的检测,我们选用AD637来实现。AD637是真有效值测量 芯片。其有效值计算公式为 2 [] IN RMS RMS V V Avg V 。应用时只需在芯片的外围添 加适当的电阻、电容即可实现任意波形交变信号的有效值的测量。其中平均

电容C1可用来设定平均时间常数,并决定低频准确度,输出纹波大小和稳定时间。R1、R2、C1、C2及运放OPA277构成一二阶低通滤波滤除检波后的纹波。电路连接图如图所示: 4、滞回比较电路之一(MAX912) MAX912 是由MAXIM 公司生产的双组高速电压比较器。该器件传播速度快(典型值为10ns) ,能接受差动输入信号并具有互补性的TTL 兼容输出。为抑制干扰引起的误翻转,我们采取了带正反馈的滞回比较电路的形式。我们采用反相输入的方式,其正向阈值电压22 5F R u V R R +=?+,对应比较后信号的下降沿。负向阈值电平为0V ,对应于比较后信号的上升沿。故输出信号的上升沿仍属过零比较。示意图如图所示。故对两路信号进行相位测量时就不能采用平时的直接异或法,而应先利用上升沿进行分频再异或。电路图如图所示: 6、MAX195AD 采样 MAX195 是美国Maxim 公司推出的16 位逐次逼近式A/ D 转换器 。内置采样保持电路,三态串行数据输出,输出时高位在前。我们采用的是同步转换传输

实验三常用模块电路的设计 一、实验目的: 1、掌握QuartusII宏功能模块的设计方法。 2、掌握VHDL设计ROM和RAM的方法。 3、掌握三态总线的设计与使用方法。 4、掌握4×4键盘扫描模块设计方法。 5、掌握PS2接口电路设计方法。 6、了解640×480VGA显示控制电路的原理和设计方法。 二、实验的硬件要求: 1、EDA/SOPC实验箱。 2、计算机。 三、实验原理 1、QuartusII宏功能模块应用 Altera提供多种方法来获取Altera Megafunction Partners Program(AMPP?)和 MegaCore?宏功能模块,这些函数经严格的测试和优化,可以在Altera特定器件结构中发挥出最佳性能。可以使用这些知识产权的参数化模块减少设计和测试的时间。MegaCore 和AMPP宏功能模块包括应用于通信、数字信号处理(DSP)、PCI和其它总线界面,以及存储器控制器中的宏功能模块。 Altera提供的宏功能模块与LPM函数有: ①算术组件:包括累加器、加法器、乘法器和LPM算术函数; ②门电路:包括多路复用器和LPM门函数。 ③I/O组件:包括时钟数据恢复(CDR)、锁相环(PLL)、双数据速率(DDR)、千兆位 收发器块(GXB)、LVDS接收器和发送器、PLL重新配置和远程更新宏功能模块。 ④存储器编译器:包括FIFO Partitioner、RAM和ROM宏功能模块。 ⑤存储组件:包括存储器、移位寄存器宏模块和LPM 存储器函数。 宏功能模块应用可以通过元件库中的“Megafunctions/LPM”或“MegaWizard Plug-In Manager”进行参数化设置并使用。其操作方法请参考“QuartusII基于宏功能模块的设计”。 2、ROM和RAM存储器设计 用FPGA实现ROM和RAM存储器可以用逻辑单元,也可以用内含的EAB/ESB,一般用VHDL直接构造存储器时用的是逻辑单元,对于内含EAB/ESB的FPGA芯片,使用“MegaWizard Plug-In Manager”定制存储器,可选择使用EAB/ESB,这样可以节约大量的逻辑单元。 一般较大规模的ROM和RAM使用“MegaWizard Plug-In Manager”定制,而较小规模,且有特殊特性要求时用VHDL直接构造。 3、 四、实验内容: 1、QuartusII宏功能模块实现ROM存储器模块 ①新建一个原理图文件。 ②使用“MegaWizard Plug-In Manager”向导,按图3.1的步骤定制一个32×8bit的ROM

个人总结Verilog代码编写的25条经验 1、对所有的信号名、变量名和端口名都用小写,这样做是为了和业界的习惯保持一致;对常量名和用户定义的类型用大写; 2、使用有意义的信号名、端口名、函数名和参数名; 3、信号名长度不要太长; 4、对于时钟信号使用clk 作为信号名,如果设计中存在多个时钟,使用clk 作为时钟信号的前缀; 5、对来自同一驱动源的信号在不同的子模块中采用相同的名字,这要求在芯片总体设计时就定义好顶层子模块间连线的名字,端口和连接端口的信号尽可能采用相同的名字; 6、对于低电平有效的信号,应该以一个下划线跟一个小写字母b 或n 表示。注意在同一个设计中要使用同一个小写字母表示低电平有效; 7、对于复位信号使用rst 作为信号名,如果复位信号是低电平有效,建议使用rst_n; 8、当描述多比特总线时,使用一致的定义顺序,对于verilog 建议采用bus_signal[x:0]的表示; 9、尽量遵循业界已经习惯的一些约定。如*_r 表示寄存器输出,*_a 表示异步信号,*_pn 表示多周期路径第n 个周期使用的信号,*_nxt 表示锁存前的信号,*_z 表示三态信号等; 10、在源文件、批处理文件的开始应该包含一个文件头、文件头一般包含的内容如下例所示:文件名,作者,模块的实现功能概述和关键特性描述,文件创建和修改的记录,包括修改时间,修改的内容等; 11、使用适当的注释来解释所有的always 进程、函数、端口定义、信号含义、变量含义或信号组、变量组的意义等。注释应该放在它所注释的代码附近,要求简明扼要,只要足够说明设计意图即可,避免过于复杂; 12、每一行语句独立成行。尽管VHDL 和Verilog 都允许一行可以写多个语句,当时每个语句独立成行可以增加可读性和可维护性。同时保持每行小于或等于72 个字符,这样做都是为了提高代码得可读性; 13、建议采用缩进提高续行和嵌套语句得可读性。缩进一般采用两个空格,如西安交通大学SOC 设计中心2 如果空格太多则在深层嵌套时限制行长。同时缩进避免使用TAB 键,这样可以避免不同机器TAB 键得设置不同限制代码得可移植能力; 14、在RTL 源码的设计中任何元素包括端口、信号、变量、函数、任务、模块等的命名都不能取Verilog 和VHDL 语言的关键字; 15、在进行模块的端口申明时,每行只申明一个端口,并建议采用以下顺序: 输入信号的clk、rst、enables other control signals、data and address signals。然后再申明输出信号的clk、rst、enalbes other control signals、data signals; 16、在例化模块时,使用名字相关的显式映射而不要采用位置相关的映射,这样可以提高代码的可读性和方便debug 连线错误; 17、如果同一段代码需要重复多次,尽可能使用函数,如果有可能,可以将函数通用化,以使得它可以复用。注意,内部函数的定义一般要添加注释,这样可以提高代码的可读性;

电路设计的模块化与设计重利用 中兴通讯CDMA事业部眭诗菊 摘要: 随着电路设计复杂程度的增加,设计规模的增大,以及产品面市时间的压力。传统的以一个原理图设计工程师加一个PCB设计工程师的串行硬件设计方式,已经成为研发进度的难以逾越的瓶颈。并行的团队式硬件(包括PCB)设计方式,已经越来越显出其价值。随着EDA软件的并行设计功能的增强,以模块化方式的硬件团队设计技术已经日益成熟。 本文主要介绍了在Cadence Board Design System上实现电路设计模块化与设计重利用的设计方法。 1. 层次化设计中的子电路与模块化电路的区别 大家对电路的层次化设计并不陌生。为了使读图方便和电路设计任务的划分,功能复杂的电路常常采用层次化设计方法。层次化设计中子电路(Sub-Design),有时也称模块(Block),在原理图设计中可以方便地重复利用。 模块化电路设计则在层次化设计的基础上更进一步,即:将子电路的原理图与其物理设计(PCB)对应起来做成物理模块(Module)。模块不仅在原理图设计中可以被方便地被其它设计重复利用;而且,在PCB设计中,模块电路可以象调用器件封装一样方便,模块电路不需要重新布局布线。 可以这样比喻,层次化设计中的子电路,相当于软件中设计中的子程序。模块化电路则相当于软件中的函数。 2. 模块化电路的优点 简化设计过程 – 将复杂的电路分解成可重复利用的模块,对模块进行独立的测试。 提高电路设计质量; 实现团队协同设计 – 将大的电路划分为较小的模块,各个部分的设计者可以根据策划,并行原理图设计、PCB的布局布线设计。最后整合到一个PCB上。缩短单 板的设计周期; 便于设计的重利用 – 模块化的电路,其原理图和PCB可以方便地用于其它设计中,不仅省时,同时可以避免重新设计可能引入的差错。 Cadence 的模块化电路设计,不仅可以对模块直接利用,还可以很方便的对模块部分进行修改利用,如更换器件、改变连线关系。模块电路可以嵌套。 3. Cadence Board Design中的模块化设计与重利用流程 Cadence Board Design 中进行电路模块化和重利用的简化流程如图1: