基于Matlab的卷积码译码器的 设计与仿真 学生姓名:指导老师:** 摘要本课程设计主要解决对一个卷积码序列进行维特比(Viterbi)译码输出, 并通过Matlab软件进行设计与仿真,并进行误码率分析。在课程设计中,系统开发平台为Windows Vista Ultimate,程序设计与仿真均采用Matlab R2007a(7.4),最后仿真详单与理论分析一致。 关键词课程设计;卷积码译码器;Matlab;Simulink;设计与仿真 1引言 本课程设计主要解决对一个卷积码序列进行维特比(Viterbi)译码输出,并通 过Matlab软件进行设计与仿真。卷积码的译码有两种方法——软判决和硬判决,此课程设计采用硬判决的维特比译码。 1.1课程设计目的 卷积码是一种向前纠错控制编码。它将连续的信息比特序列映射为连续的编码器输出符号。这种映射是高度结构化的,使得卷积码的译码方法与分组码译码所采用的方法完全不同。可以验证的是在同样复杂度情况下,卷积码的编码增益要大于分组码的编码增益。对于某个特定的应用,采用分组编码还是采用卷积编码哪一种更好则取决于这一应用的具体情况和进行比较时可用的技术[1]。 本课程设计便是通过Matlab设计一个硬判决维特比译码输出的完整电路,并进行误码率分析。

1.2 课程设计的原理 卷积码,又称连环码,是由伊莱亚斯(P.elias)于1955年提出来的一种非分组码。 卷积编码的最佳译码准则为:在给定已知编码结构、信道特性和接收序列的情况下,译码器将把与已经发送的序列最相似的序列作为传送的码字序列的估值。对于二进制对称信道,最相似传送序列就是在汉明距离上与接收序列最近的序列。 卷积码的译码方法有两大类:一类是大数逻辑译码,又称门限译码(硬判决,编者注);另一种是概率译码(软判决,编者注),概率译码又分为维特比译码和序列译码两种。门限译码方法是以分组码理论为基础的,其译码设备简单,速度快,但其误码性能要比概率译码法差[2]。 当卷积码的约束长度不太大时,与序列译码相比,维特比译码器比较简单,计算速度快。维特比译码算法是1967年由Viterbi提出,近年来有大的发展。目前在数字通信的前向纠错系统中用的较多,而且在卫星深空通信中应用更多,该算法在卫星通信中已被采用作为标准技术。 2维特比译码原理 采用概率译码的基本思想是:把已接收序列与所有可能的发送序列做比较,选择其中码距最小的一个序列作为发送序列。如果发送L组信息比特,那么对于(n,k)卷积码来说,可能发送的序列有2kL个,计算机或译码器需存储这些序列并进行比较,以找到码距最小的那个序列。当传信率和信息组数L较大时,使得译码器难以实现。维特比算法则对上述概率译码做了简化,以至成为了一种实用化的概率算法。它并不是在网格图上一次比较所有可能的2kL条路径(序列),而是接收一段,计算和比较一段,选择一段最大似然可能的码段,从而达到整个码序列是一个最大似然值得序列。 下面以图2.1的(2,1,3)卷积码编码器所编出的码为例,来说明维特比解码的方法和运作过程。为了能说明解码过程,这里给出该码的状态图,如图2.2所

卷积码的编码及解码(Viterbi 解码) 一、实验目的 1、了解卷积码的基本原理; 2、掌握卷积码编码的电路设计方法; 2、掌握卷积码 Viterbi 译码的基本方法和电路设计方法。 二、实验仪器 1、移动通信实验箱一台; 2、台式计算机一台; 三、实验原理 1.卷积码编码原理 卷积码是一个有限记忆系统,它也将信息序列切割成长度 k的一个个分组,与分组码不 同的是在某一分组编码时,不仅参看本时刻的分组而且参看本时刻以前的 L 个分组。我们把 L+1 称为约束长度。 2.卷积码的译码算法(硬判决 Viterbi 译码) Viterbi译码算法是一种最大似然算法,它不是在网络图上依次比较所有可能的路径, 而是接收一段,计算,比较一段,保留最有可能的路径,从而达到整个码序列是一个最大似然序列。Viterbi解码算法的基本步骤如下: 1、从某一时间单位j=m开始,对进入每一状态的所有长为j段分支的部分路径,计算部分路径度量。对每一状态,挑选并存储一条有最大度量的部分路径及 其部分度量,称此部分路径为留选(幸存)路径。 2、j增加1,把此时刻进入每一状态的所有分支度量,和同这些分支相连的前一时刻的留选路径的度量相加,得到了此时刻进入每一状态的留选路径,加以存储并删去其他所有的路径。因此留选路径延长了一个分支。 3、若j 西南科技大学 方向设计报告 课程名称:通信工程方向设计 设计名称:2/3卷积码编译码器仿真与性能分析 姓名: 学号: 班级: 指导教师: 起止日期:2011.12.12-2012.1.6 西南科技大学信息工程学院制 方向设计任务书 学生班级:学生姓名:学号: 设计名称:2/3卷积码编译码器仿真与性能分析 起止日期:2011.12.12-2012.1.6指导教师: 设计要求: (1)分析2/3卷积码编码器结构; (2)分析2/3卷积码译码的Viterbi算法; (3)基于SIMULINK进行2/3卷积码的纠错性能仿真; 方向设计学生日志 时间设计内容 12.15-12.17 查看题目及设计要求。 12.18-12.23 查阅相关资料,设计方案。 12.23-12.27 编写报告及调试程序。 12.28-12.29 完善修改课程设计报告。 12.30-12.31 答辩。 方向设计考勤表 周星期一星期二星期三星期四星期五 方向设计评语表 指导教师评语: 成绩:指导教师: 年月日 2/3卷积码编译码器仿真与性能分析 摘要: 卷积码是一种性能优越的信道编码。它的编码器和译码器都比较容易实现,同时它具有较强的纠错能力。随着纠错编码理论研究的不断深入,卷积码的实际应用越来越广泛。本文简明地介绍了卷积码的编码原理和Viterbi译码原理。并在SIMULINK模块设计中,完成了对卷积码的编码和译码以及误比特统计整个过程的模块仿真。最后,通过在仿真过程中分别改变卷积码的重要参数来加深理解卷积码的这些参数对卷积码的误码性能的影响。经过仿真和实测,并对测试结果作了分析。 关键词: 卷积码编码器、viterbi译码器、SIMULINK 卷积码的编解码Matlab仿真摘要 卷积码是一种性能优越的信道编码。它的编码器和译码器都比较容易实现,同时它具有较强的纠错能力D随着纠错编码理论研究的不断深入,卷积码的实际应用越来越广泛。本文简明地介绍了卷积码的编码原理和译码原理o并在SIMULINK模块设计中,完成了对卷积码的编码和译码以及误比特统计整个过程的模块仿真。最后,通过在仿真过程中分别改变卷积码的重要参数来加深理解卷积码的这些参数对卷积码的误码性能的影响。经过仿真和实测,并对测试结果作了分析。得出了以下三个结论z (1)当改变卷积码的码率时,系统的误码性能也将随之发生变化。 (2)对于码率一定的卷积码,当约束长度N发生变化时,系统的误码性能也会随之发生变化。 (3)回溯长度也会不同程度上地影响误码性能。 关键词:卷积码:码率:约束长度:回溯长度 Simulation and Research on Encoding and Decoding of Convolution Code Abstract Convolution code has a superior performance of the channel code. It is easy to coding and decoding.An d it has a strong ability to correct e盯ors. As correcting coding theory has a long development,the practice of convolution code is more and more extensive.In由1S由esis,the principle of convolution coding and decoding is introduced simply白rstly. Then由e whole simulation module process of encoding,decoding and the Error Rate Calculation is completed in由is design. Finally,in order to understand 由eir performances of error rate,many changes in parameters of convolution code are calculated in the simulation process.Af ter simulation and me皿UTe,an analysis of test results is presented.Th e following由ree conclusions are draw: (l)Wh en the rate of convolution Code ch皿ges,HER performance of the systemwill change. (2) For a certain rate of convolution code,when由ere is a change in the constraint length of N,BER perfonnance of由e system will change. (3) Re位ospec咀ve length will affect BE R. Key words: convolution code; rate; cons缸aint leng由; retrospective length; 湖南文理学院 课程设计报告 课程名称:通信系统课程设计 专业班级:通信工程11102班09 学生姓名:朱涛 指导教师:侯清莲 完成时间:2014-11-18 报告成绩: 目录 一、设计要求 (1) 二、设计作用与目的 (1) 三、所用设备及软件 (1) 四、卷积码编码的概念 (1) 4.1卷积码的编码描述方法 (1) 4.2 卷积编码 (2) 4.3 卷积码的树状图 (3) 4.4 卷积码的网格图 (3) 五、 EDA设计方法及工具软件QUARTUSⅡ (4) 六、改变卷积编码器的参数仿真以及结论 (4) 6.1 不同回溯长度对卷积编码器性能的影响 (4) 6.2 不同码率对卷积编码器误码性能的影响 (5) 6.3 不同约束长度对卷积编码器的误码性能影响 (6) 七、卷积码编码器的VHDL设计与仿真 (8) 7.1 VHDL设计的优点与设计方法 (8) 7.2 卷积码编码器的VHDL实现 (10) 八、心得体会 (10) 九、参考文献 (11) 卷积编码器的设计 一、设计要求 (1)画出卷积码的原理框图,说明系统中各主要组成部分的功能。 (2)使用EDA技术及VHDL语言对卷积编码器进行设计与仿真并对结果分析。 二、设计作用与目的 (1)巩固加深对通信基本知识分析以及卷积码的掌握,提高综合运用通信知识的能力。(2)掌握采用仿真软件对系统进行仿真分析。 (3)培养学生查阅参考文献,独立思考,设计,钻研电子技术相关问题的能力。 (4)掌握相关电子线路工程技术规范以及常规电子元器件的性能技术指标。 (5)培养严肃认真的工作作风与科学态度,建立严谨的工程技术观念。 (6)了解电气图国家标准,并利用电子CAD等正确绘制电路图。 (7)培养工程实践能力,创新能力与综合设计能力。 三、所用设备及软件 (1)QUARTUSⅡ (2)PC机 四、卷积码编码的概念 4.1卷积码的编码描述方法 编码描述方法有5种:冲激响应描述法、生成矩阵描述法、多项式乘积描述法、状态图描述法和网格图描述法。卷积码的纠错能力随着N的增加而增大,而差错率随着N的增加而指数下降。在编码器复杂性相同的情况下,卷积码的性能优于分组码。分组码有严格的代数结构,但卷积码至今尚未找到如此严密的数学手段。分组码的译码算法可以由其代数特性得到。卷积码虽然可以采用适用于分组码的门限译码(即大数逻辑译码),但性能不如维特比译码和序列译码[2]。 以二元码为例,输入信息序列为u=(u0,u1,…),其多项式表示为u(x)=u0+u1x+…+…。编码器的连接可用多项式表示为g (1,1) (x)=1+x+x2和g(1,2)(x)=1+x2,称为码的子生 成多项式。它们的系数矢量g (1,1)=(111)和g (1,2) =(101)称作码的子生成元。以子生成多项式 为阵元构成的多项式矩阵G(x)=[g (1,1)(x),g (1,2) (x)],称为码的生成多项式矩阵。由生成 元构成的半无限矩阵。 湖南文理学院课程设计报告 课程名称:通信系统课程设计 院部:电气与信息工程学院 专业班级: 学生姓名: 指导教师: 完成时间: 2011 年 12 月 29日 报告成绩: 目录 目录 (2) 摘要 (3) Abstract (4) 一、引言 (5) 1.1设计任务及基本要求 (5) 1.2设计目的 (6) 1.3 设计所用仪器设备.................................................................................. 错误!未定义书签。 二、基本概念 (6) 2.1 卷积码的编码原理 (6) 2.2 卷积码编码描述 (6) 2.3 卷积码译码描述 (6) 三、卷积码的编译码原理 (6) 3.1卷积码的图形描述 (6) 3.1.1 树状图 (8) 3.1.2 网格图 (8) 3.1.3 状态图 (9) 3.2 卷积积码的编码算法 (9) 3.3卷积码的Viterbi译码 (10) 四、卷积码的仿真及性能分析 (12) 4.1 SIMULINK仿真模块 (12) 4.2 卷积码的参数对误码率的影响 (13) 4.2.1 码率对误码性能的影响 (13) 4.2.2 约束长度对误码性能的影响 (15) 4.2.3 回溯长度对卷积码性能的影响 (16) 4.3 仿真分析 (17) 总结 (18) 参考文献: (19) 摘要 卷积码是深度空间通信系统和无线通信系统中常用的一种差错控制编码。在编码过程中,卷积码充分利用了各码字间的相关性。在与分组码同样的码率和设备复杂性的条件下,无论从理论上还是从实践上都证明,卷积码的性能都比分组码具有优势。而且卷积码在实现最佳译码方面也较分组码容易。因此卷积码广泛应用于卫星通信,CDMA数字移动通信等通信系统,是很有前途的一种编码方式。对其进行研究有很大的现实意义。为了解决传统的维特比译码器结构复杂、译码速度慢、消耗资源大的问题,提出一种新型的适用于FPGA 特点,路径存储于译码输出并行工作,同步存储路径矢量和状态矢量的译码器设计方案。该设计方案通过在ISE.2i中仿真验证,译码结果正确,得到编码前的原始码元,速度显著提高,译码器复杂程度明显降低。并在实际的软件无线电通信系统中信道编解码部分得到应用,性能优良。 关键词:卷积码;误码性能;原理 No.15 (2,1,3)卷积码的编码及译码 摘要: 本报告对于(2,1,3)卷积码原理部分的论述主要参照啜刚教材和课件,编程仿真部分绝对原创,所有的程序都是在Codeblocks 8.02环境下用C语言编写的,编译运行都正常。完成了卷积码的编码程序,译码程序,因为对于短于3组的卷积码,即2 bit或4 bit纠错是没有意义的,所以对正确的短序列直接译码,对长序列纠错后译码,都能得到正确的译码结果。含仿真结果和程序源代码。 如果您不使用Codeblocks运行程序,则可能不支持中文输出显示,但是所有的数码输出都是正确的。 一、 卷积码编码原理 卷积码编码器对输入的数据流每次1bit 或k bit 进行编码,输出n bit 编码符号。但是输出的分支码字的每个码元不仅于此时可输入的k 个嘻嘻有关,业余前m 个连续式可输入的信息有关,因此编码器应包含m 级寄存器以记录这些信息。 通常卷积码表示为 (n,k,m). 编码率 k r n = 当k=1时,卷积码编码器的结构包括一个由m 个串接的寄存器构成的移位寄存器(成为m 级移位寄存器、n 个连接到指定寄存器的模二加法器以及把模二加法器的输出转化为穿行的转换开关。 本报告所讲的(2,1,3)卷积码是最简单的卷积码。就是2n =,1k =,3m =的卷积码。每次输入1 bit 输入信息,经过3级移位寄存器,2个连接到指定寄存器的模二加法器,并把加法器输出转化为串行输出。 编码器如题所示。 二、卷积码编码器程序仿真 C 语言编写的仿真程序。 为了简单起见,这里仅仅提供数组长度30 bit 的仿真程序,当然如果需要可以修改数组大小。为了更精练的实现算法,程序输入模块没有提供非法字符处理过程,如果需要也可以增加相应的功能。 进入程序后,先提示输入数据的长度,请用户输入int (整型数)程序默认用户输入的数据小于30,然后提示输入01数码,读入数码存储与input 数组中,然后运算输出卷积码。经过实验仿真,编码完全正确。 以下是举例: a.课件上的输入101 输出11 10 00 的实验 基于MATLAB的卷积码的分析与应用 毕业设计(论文)任务书 基于MATLAB的卷积码的分析与应用 摘要 随着现代通信的发展,特别是在未来4G通信网络中,高速信息传输和高可靠性传输成为信息传输的两个主要方面,而可靠性尤其重要。因为信道状况的恶劣,信号不可避免会受到干扰而出错。为实现可靠性通信,主要有两种途径:一种是增加发送信号的功率,提高接收端的信号噪声比;另一种是采用编码的方法对信道差错进行控制。前者常常受条件限制,不是所有情况都能采用。因此差错控制编码得到了广泛应用。 介绍了多种信道编码方式,着重介绍了卷积码的编码方法和解码方式。介绍了MATLAB的使用方法、编程方法、语句、变量、函数、矩阵等。介绍了TD-SCDMA通信系统和该系统下的卷积码,搭建了系统通信模型。编写卷积码的编码和解码程序。用MATLAB仿真软件对TD-SCDMA系统的卷积码编解码进行仿真。对其纠正错码性能进行验证,并且对误码率进行仿真和分析。卷积码的编码解码方式有很多,重点仿真Viterbi算法。Viterbi算法就是利用卷积码编码器的格图来计算路径度量,选择从起始时刻到终止时刻的惟一幸存路径作为最大似然路径。沿着最大似然路径回溯到开始时刻,所走过的路径对应的编码输出就是最大似然译码输出序列。它是一种最大似然译码方法,当编码约束长度不大、或者误码率要求不是很高的情况下,Viterbi译码器设备比较简单,计算速度快,因而Viterbi译码器被广泛应用于各种领域。 关键词:卷积码;信道编码;TD-SCDMA;MATLAB 目录 毕业设计(论文)任务书 ............................................................................................I 摘要........................................................................................................................... II Abstract......................................................................................... 错误!未定义书签。第1章绪论 . (1) 1.1课题研究的背景和来源 (1) 1.2主要内容 (2) 第2章相关理论介绍 (3) 2.1信道编码 (3) 2.1.1 信道编码的分类 (3) 2.1.2 编码效率 (3) 2.2线性分组码 (3) 2.3循环码 (5) 2.4卷积码 (6) 2.4.1 卷积码简介 (7) 2.4.2 卷积码的编码 (7) 2.4.3 卷积码的解码 (13) 第3章MATLAB应用 (21) 3.1数和算术的表示方法 (21) 3.2向量与矩阵运算 (21) 3.2.1 通过语句和函数产生 (21) 3.2.2 矩阵操作 (22) 3.3矩阵的基本运算 (22) 3.3.1 矩阵乘法 (22) 3.3.2 矩阵除法 (23) 3.4MATLAB编程 (23) 3.4.1 关系运算 (23) 3.4.2 控制流 (25) 第4章卷积码的设计与仿真 (27) 4.1TD-SCDMA系统 (27) 4.1.1 系统简介 (27) 4.1.2 仿真通信系统模型 (27) 实验九 (2,1,5)卷积码编码译码技术 一、实验目的 1、掌握(2,1,5)卷积码编码译码技术 2、了解纠错编码原理。 二、实验内容 1、(2,1,5)卷积码编码。 2、(2,1,5)卷积码译码。 三、预备知识 1、纠错编码原理。 2、(2,1,5)卷积码的工作原理。 四、实验原理 卷积码是将发送的信息序列通过一个线性的,有限状态的移位寄存器而产生的编码。通常卷积码的编码器由K级(每级K比特)的移位寄存器和n个线性代数函数发生器(这里是模2加法器)组成。 若以(n,k,m)来描述卷积码,其中k为每次输入到卷积编码器的bit数,n 为每个k元组码字对应的卷积码输出n元组码字,m为编码存储度,也就是卷积编码器的k元组的级数,称m+1= K为编码约束度m称为约束长度。卷积码将k 元组输入码元编成n元组输出码元,但k和n通常很小,特别适合以串行形式进行传输,时延小。与分组码不同,卷积码编码生成的n元组元不仅与当前输入的k元组有关,还与前面m-1个输入的k元组有关,编码过程中互相关联的码元个数为n*m。卷积码的纠错性能随m的增加而增大,而差错率随N的增加而指数下降。在编码器复杂性相同的情况下,卷积码的性能优于分组码。 编码器 随着信息序列不断输入,编码器就不断从一个状态转移到另一个状态并同时输出相应的码序列,所以图3所示状态图可以简单直观的描述编码器的编码过程。因此通过状态图很容易给出输入信息序列的编码结果,假定输入序列为110100,首先从零状态开始即图示a状态,由于输入信息为“1”,所以下一状态为b并输出“11”,继续输入信息“1”,由图知下一状态为d、输出“01”……其它输入信息依次类推,按照状态转移路径a->b->d->c->b->c->a输出其对应的编码结果“110101001011”。 译码方法 ⒈代数 代数译码是将卷积码的一个编码约束长度的码段看作是[n0(m+1),k0(m+1)]线性分组码,每次根据(m+1)分支长接收数字,对相应的最早的那个分支上的信息数字进行估计,然后向前推进一个分支。上例中信息序列 =(10111),相应的码序列 c=(11100001100111)。若接收序列R=(10100001110111),先根据R 的前三个分支(101000)和码树中前三个分支长的所有可能的 8条路径(000000…)、(000011…)、(001110…)、(001101…)、(111011…)、(111000…)、(110101…)和(110110…)进行比较,可知(111001)与接收 实验四 卷积码的编解码 一、实验目的 1、掌握卷积码的编解码原理。 2、掌握卷积码的软件仿真方法。 3、掌握卷积码的硬件仿真方法。 4、掌握卷积码的硬件设计方法。 二、预习要求 1、掌握卷积码的编解码原理和方法。 2、熟悉matlab 的应用和仿真方法。 3、熟悉Quatus 的应用和FPGA 的开发方法。 三、实验原理 1、卷积码编码原理 在编码器复杂度相同的情况下,卷积码的性能优于分组码,因此卷积码几乎被应用在所有无线通信的标准之中,如GSM , IS95和CDMA 2000 的标准中。 卷积码通常记作( n0 , k0 , m) ,它将k 0 个信息比特编为n 0 个比特, 其编码效率为k0/ n0 , m 为约束长度。( n0 , k0 , m ) 卷积码可用k0 个输入、n0 个输出、输入存储为m 的线性有限状态移位寄存器及模2 加法计数器来实现。 本实验以(2,1,3)卷积码为例加以说明。图1就是卷积码编码器的结构。 图1 (2,1,3)卷积码编码器 其生成多项式为: 21()1G D D D =++; 2 2()1G D D =+; 如图1 所示的(2,1,3)卷积码编码器中,输入移位寄存器用转换开关代替,每输入一个信息比特经编码产生二个输出比特。假设移位寄存器的初始状态为全0,当第一个输入比特为0时,输出比特为00;若输入比特为1,则输出比特为11。随着第二个比特输入,第一个比特右移一位,此时输出比特同时受到当前输入比特和前一个输入比特的影响。第三个比特输入时,第一、二个比特分别右移一位,同时输出二个由这三位移位寄存器存储内容所共同决定的比特。依次下去就完成了编码过程。 下面是卷积码的网格图表示。他是比较清楚而又紧凑的描述卷积码的一种方式,它是最常用的描述方 基于System View的卷积码译码器的设计 摘要本课程设计在SystemView 平台上设计了卷积码译码器,SystemView系统中提供了专门的卷积码编码和译码图符,使用户能快速地建立基于卷积码的仿真系统,本课程设计对(2,1,6)的大数逻辑译码原理,以及维比特译码原理进行了解释,利用SystemView 进行了(2,1,3)卷积码译码器的仿真。系统运行以后将译码后得到的波形与原始的码元输入信号进行比较,系统参数经过修改以后能够正确地将编码后的信号译码为原始的码元。 关键字卷积码译码器,System View,(2,1,3)卷积码译码器 1 引言 卷积码的译码方法主要有两类,代数译码和概率译码。代数译码是根据卷积码的本身编码结构进行译码,译码时不考虑信道的统计特性。概率译码在计算时要考虑信道的统计特性。典型的算法如:最大似然译码、维比特译码、序列译码等。本课程设计利用SystemView 平台进行卷积码译码器的实现,SystemView系统中提供了专门的卷积码编码和译码图符,使用户能快速地建立基于卷积码的仿真系统,本课程设计对(2,1,6)的大数逻辑译码原理,以及维比特译码原理进行了解释,利用System View进行了(2,1,3)卷积码译码仿真,系统参数经过修改以后能够正确地将编码后的信号译码为原始的码元。 1.1 卷积码简介 卷积码也称为连环码是一种非分组码,分组码编码时,先将输入的信息序列分为长度为k的码元的字段,然后按照一定的编码规则,给含k个信息元的段附加上r长的监督元,于是生成n 长的码组。在编码时,各n长码组是分别编码的,各码组之间没有约束关系,因此译码时各码组之间是分别独立进行的。卷积码则不同于此,卷积编码属于信道编码,主要用来纠正码元的随机差错,它是以牺牲效率来换取可靠性的,利用增加监督位,进行检错和纠错。卷积码把k个信息位编成n位,k和n通常很小,特别适宜于串行形式传输,延时小,n个码元与当前段的k个信息位有关,而且与前N-1段的信息有关,编码过程相互关联的码元为Nn个,N或Nn称为卷积码的约束长度,常把卷 卷积码 1、什么是卷积码? 卷积码作为一种编码方法,是将k个信息比特编成n个比特,但k和n通常很小,因此时延小,特别适合以串行形式进行传输。通常它更适合于前向纠错,因而对于许多实际情况它的性能优于分组码,而且运算较简单。 2、卷积码的编译原理? (1)编码原理 下图示出卷积码编码器一般原理方框图。编码器由三种主要元件构成,包括Nk级移存器、n个模2加法器和一个旋转开关。每个模2加法器的输入端数目可以不同,它连接到一些移存器的输出端。模2加法器的输出端接到旋转开关上。将时间分成等间隔的时隙,在每个时隙中有k比特从左端进入移存器,并且移存器各级暂存的信息向右移k位。旋转开关每时隙旋转一周,输出n比特(n)k)。 (2)译码原理 卷积码的解码方法可以分为两类:代数解码和概率解码。代数解码是利用编码本身的代数结构进行解码,不考虑信道的统计特性。概率解码则是基于信道的统计特性和卷积码的特点进行计算,其中一种概率解码方法是维特比算法。当码的约束长度较短时,它比序贯解码算法的效率更高、速度更快,目前得到广泛的使用。 维特比算法的基本原理是将接收到的信号序列和所有可能的发送信号序列比较,选择其中汉明距离最小的序列认为是当前发送信号序列。若发送一个k位序列,则有2k种可能的发送序列。计算机应存储这些序列,以便用作比较。当k较大时,存储量太大,使实用受到限制。维特比算法对此作了简化,使之能够实用。 3、与分组码相比,卷积码的优势是什么? 与分组码不同的是,卷积码编码后n个码元不但与本码组的k个信息码元有关,而且与前面的N-1段信息有关,编码的过程中相互关联的码元有N*n个。卷积码的纠错能力同样是随N的增大而增大,其差错率随N的增大而指数的下降。在编码器相同的情况下,卷积码的性能优于分组码。另一点不同是,分组码有严格的代数结构,但是卷积码至今没有严格的数学手段把纠错能力和码结构有机地联系起来,目前大都是采用计算机搜索来搜索好用的码组。 4、卷积码编译电路的组成结构? (1)信号发生器 (2)卷积码编码器 (3)信道 (4)卷积码译码器 参考文献: [1]通信原理(第6版)樊昌信、曹丽娜,国防工业出版社·北京,2012 [2]SystemView通信仿真开发手册,孙屹,国防工业出版社,2004 [3]SystemView动态系统分析及通信系统仿真设计,罗卫兵、孙桦、张捷,西安电子科技大学出版社,2001 卷积码的编解码仿真与研究 摘要 卷积码是一种性能优越的信道编码。它的编码器和译码器都比较容易实现,同时它具有较强的纠错能力。随着纠错编码理论研究的不断深入,卷积码的实际应用越来越广泛。本文简明地介绍了卷积码的编码原理和译码原理。并在SIMULINK模块设计中,完成了对卷积码的编码和译码以及误比特统计整个过程的模块仿真。最后,通过在仿真过程中分别改变卷积码的重要参数来加深理解卷积码的这些参数对卷积码的误码性能的影响。经过仿真和实测,并对测试结果作了分析。得出了以下三个结论: (1)当改变卷积码的码率时,系统的误码性能也将随之发生变化。 (2)对于码率一定的卷积码,当约束长度N 发生变化时,系统的误码性能也会随之发生变化。 (3)回溯长度也会不同程度上地影响误码性能。 关键词:卷积码;码率;约束长度;回溯长度 Simulation and Research on Encoding and Decoding of Convolution Code Abstract Convolution code has a superior performance of the channel code. It is easy to coding and decoding. And it has a strong ability to correct errors. As correcting coding theory has a long development, the practice of convolution code is more and more extensive. In this thesis, the principle of convolution coding and decoding is introduced simply firstly. Then the whole simulation module process of encoding, decoding and the Error Rate Calculation is completed in this design. Finally, in order to understand their performances of error rate, many changes in parameters of convolution code are calculated in the simulation process. After simulation and measure, an analysis of test results is presented. The following three conclusions are draw: (1) When the rate of convolution Code changes, BER performance of the system will change. (2) For a certain rate of convolution code, when there is a change in the constraint length of N, BER performance of the system will change. (3) Retrospective length will affect BER. Key words: convolution code; rate; constraint length; retrospective length; 本科生毕业论文(设计) 题目:MATLAB实现卷积码编译码 专业代码: 作者姓名: 学号: 单位: 指导教师: 年月日 目录 前言----------------------------------------------------- 1 1. 纠错码基本理论---------------------------------------- 2 1.1纠错码基本理论 ----------------------------------------------- 2 1.1.1纠错码概念 ------------------------------------------------- 2 1.1.2基本原理和性能参数 ----------------------------------------- 2 1.2几种常用的纠错码 --------------------------------------------- 6 2. 卷积码的基本理论-------------------------------------- 8 2.1卷积码介绍 --------------------------------------------------- 8 2.1.1卷积码的差错控制原理----------------------------------- 8 2.2卷积码编码原理 ---------------------------------------------- 10 2.2.1卷积码解析表示法-------------------------------------- 10 2.2.2卷积码图形表示法-------------------------------------- 11 2.3卷积码译码原理---------------------------------------------- 15 2.3.1卷积码三种译码方式------------------------------------ 15 2.3.2V ITERBI译码原理---------------------------------------- 16 3. 卷积码编译码及MATLAB仿真---------------------------- 18 3.1M ATLAB概述-------------------------------------------------- 18 3.1.1M ATLAB的特点------------------------------------------ 19 3.1.2M ATLAB工具箱和内容------------------------------------ 19 3.2卷积码编码及仿真 -------------------------------------------- 20 3.2.1编码程序 ---------------------------------------------- 20 3.3信道传输过程仿真-------------------------------------------- 21 3.4维特比译码程序及仿真 ---------------------------------------- 22 3.4.1维特比译码算法解析------------------------------------ 23 3.4.2V ITERBI译码程序--------------------------------------- 25 3.4.3 VITERBI译码MATLAB仿真----------------------------------- 28 3.4.4信噪比对卷积码译码性能的影响 -------------------------- 28 摘要 卷积码是一种性能优越的信道编码。它的编码器和译码器都比较容易实现,同时它具有较强的纠错能力。随着纠错编码理论研究的不断深入,卷积码的实际应用越来越广泛。本文对卷积码和卷积码的编译码有一个简单的介绍且给出了信道编码的发展历史及研究状况,然后详细讨论了(2,1,2)卷积码的编码过程和译码过程,通过状态转移方程和输出方程得出状态转移表和状态转移图,然后通过维特比译码器研究,总结出了维特比译码算法,最后通过Matlab软件进行设计与仿真,得到了编码程序和译码程序,其运行结果与理论分析一致。 关键字卷积码编码、信道编码、Viterbi译码、MATLAB仿真 目录 摘要........................................... 错误!未定义书签。 一、引言 (3) 1.1发展历史及研究状况 (3) 1.2设计目的和意义 (3) 1.3设计方法 (4) 二、卷积码编译码原理 (5) 2.1 卷积码编码原理 (5) 2.2编码器 (6) 2.3 卷积码译码原理 (7) 2.4 VITEBI 译码的关键步骤 (8) 2.4.1 输入与同步单元 (8) 2.4.2 支路量度计算 (8) 2.4.3 路径量度的存储与更新 (8) 2.4.4 信息序列的存储与更新 (8) 2.4.5 判决与输出单元 (8) 三、卷积码编码实现 (9) 3.1 编码原理分析 (9) 3.2 卷积码编码流程图 (10) 四、卷积码译码实现 (11) 4.1 译码编程思路 (11) 4.2 卷积码译码流程图 (11) 五、卷积码编译码程序的编译及仿真波形 (11) 5.1 卷积码编码仿真 (12) 5.2卷积码译码仿真 (13) 5.3卷积码纠错码仿真 (14) 六、总结 (15) 七、参考文献 (16) 附录 (17) 数字通信原理课程设计报告书 基于matlab的卷积码译码器的仿真设计 ) 1设计目的 卷积码是一种向前纠错控制编码。它将连续的信息比特序列映射为连续的编码器输出符号。这种映射是高度结构化的,使得卷积码的译码方法与分组码译码所采用的方法完全不同。可以验证的是在同样复杂度情况下,卷积码的编码增益要大于分组码的编码增益。对于某个特定的应用,采用分组编码还是采用卷积编码哪一种更好则取决于这一应用的具体情况和进行比较时可用的技术。 本课程设计便是通过Matlab设计一个硬判决维特比译码输出的完整电路,并进行误码率分析。 2设计的主要内容和要求 (1)要求能熟练地运用Matlab技术对卷积码译码器进行仿真。 (2)运用Matlab中Simulink单元来创建信源模块、信道模块、信宿模块、简易译码器模块等,并运用所有设计的模块来进行仿真。 3 设计原理 3.1卷积码 卷积码,又称连环码,是由伊莱亚斯(P.elias)于1955年提出来的一种非分组码。 卷积编码的最佳译码准则为:在给定已知编码结构、信道特性和接收序列的情况下,译码器将把与已经发送的序列最相似的序列作为传送的码字序列的估值。对于二进制对称信道,最相似传送序列就是在汉明距离上与接收序列最近的序列。 卷积码的译码方法有两大类:一类是大数逻辑译码,又称门限译码(硬判决,编者注);另一种是概率译码(软判决,编者注),概率译码又分为维特比译码和序列译码两种。门限译码方法是以分组码理论为基础的,其译码设备简单,速度快,但其误码性能要比概率译码法差。 当卷积码的约束长度不太大时,与序列译码相比,维特比译码器比较简单,计算速度快。维特比译码算法是1967年由Viterbi 提出,近年来有大的发展。目前在数字通信的前向纠错系统中用的较多,而且在卫星深空通信中应用更多,该算法在卫星通信中已被采用作为标准技术。 3.2 维特比译码原理 采用概率译码的基本思想是:把已接收序列与所有可能的发送序列做比较,选择其中码距最小的一个序列作为发送序列。如果发送L 组信息比特,那么对于(n,k )卷积码来说,可能发送的序列有2kL 个,计算机或译码器需存储这些序列并进行比较,以找到码距最小的那个序列。当传信率和信息组数L 较大时,使得译码器难以实现。维特比算法则对上述概率译码做了简化,以至成为了一种实用化的概率算法。它并不是在网格图上一次比较所有可能的2kL 条路径(序列),而是接收一段,计算和比较一段,选择一段最大似然可能的码段,从而达到整个码序列是一个最大似然值得序列。 下面以图3.2.1的(2,1,3)卷积码编码器所编出的码为例,来说明维特比解码的方法和运作过程。为了能说明解码过程,这里给出该码的状态图,如图3.2.2 示。维特比译码需要利用图来说明移码过程。根据卷积码画网格的方法,我们可以画出该码的网格图,如图3.2.3所示。该图设输入信息数目L=5,所以画L+N=8个时间单位,图中分别标以0至7。这里设编码器从a 状态开始运作。该网格图的每一条路径都对应着不同的输入信息序列。由于所有可能输入信息序列共有2kL 个,因而网格图中所有可能的路径也为2kL 条。这里节点a=00,b=01,c=10, b 图3.2.1 (2,1,3)卷积码编码器 图3.2.2 (2,1,3)卷积码状态图基于matlab的2-3卷积码编码译码设计与仿真

卷积码的编解码Matlab仿真

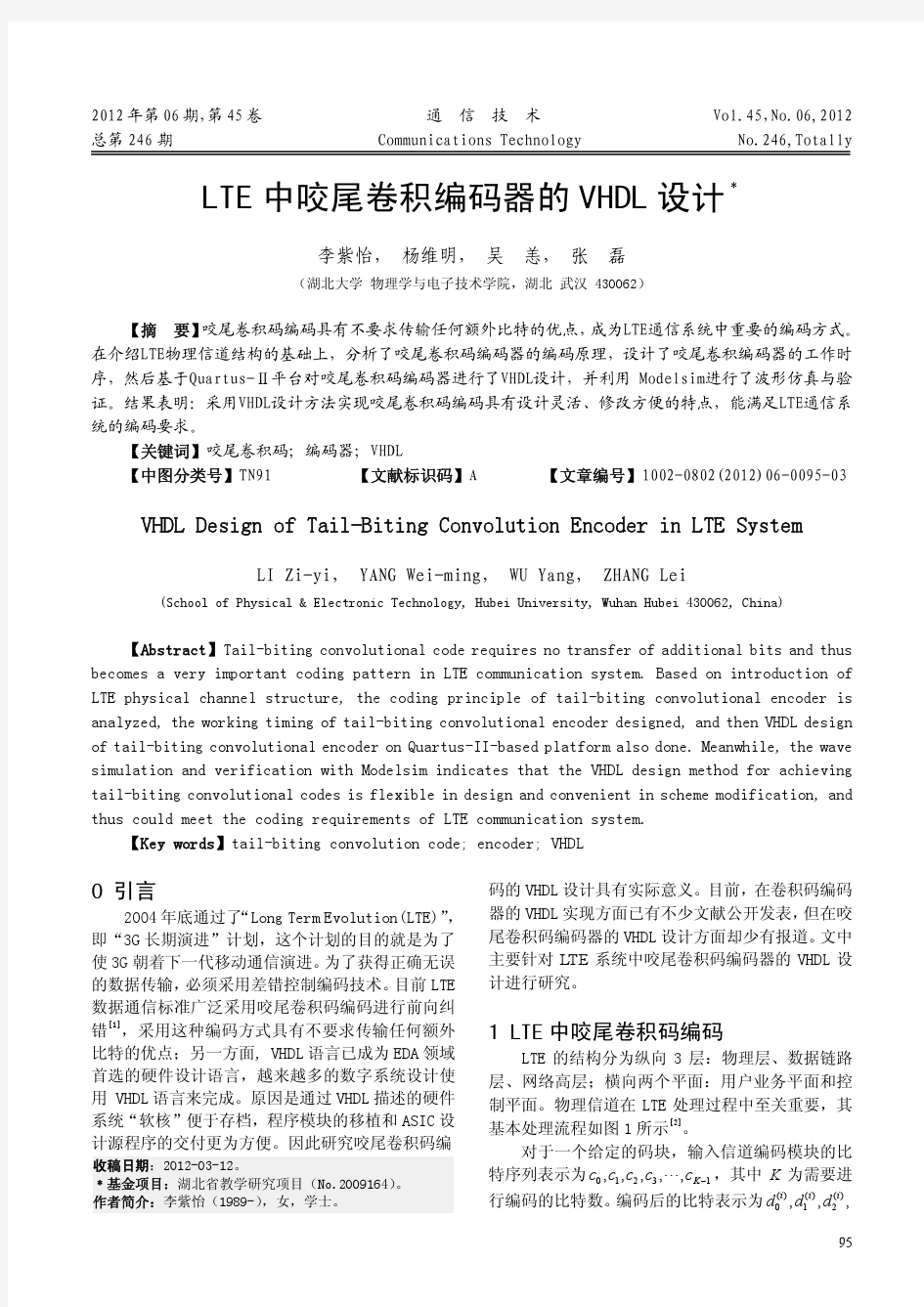

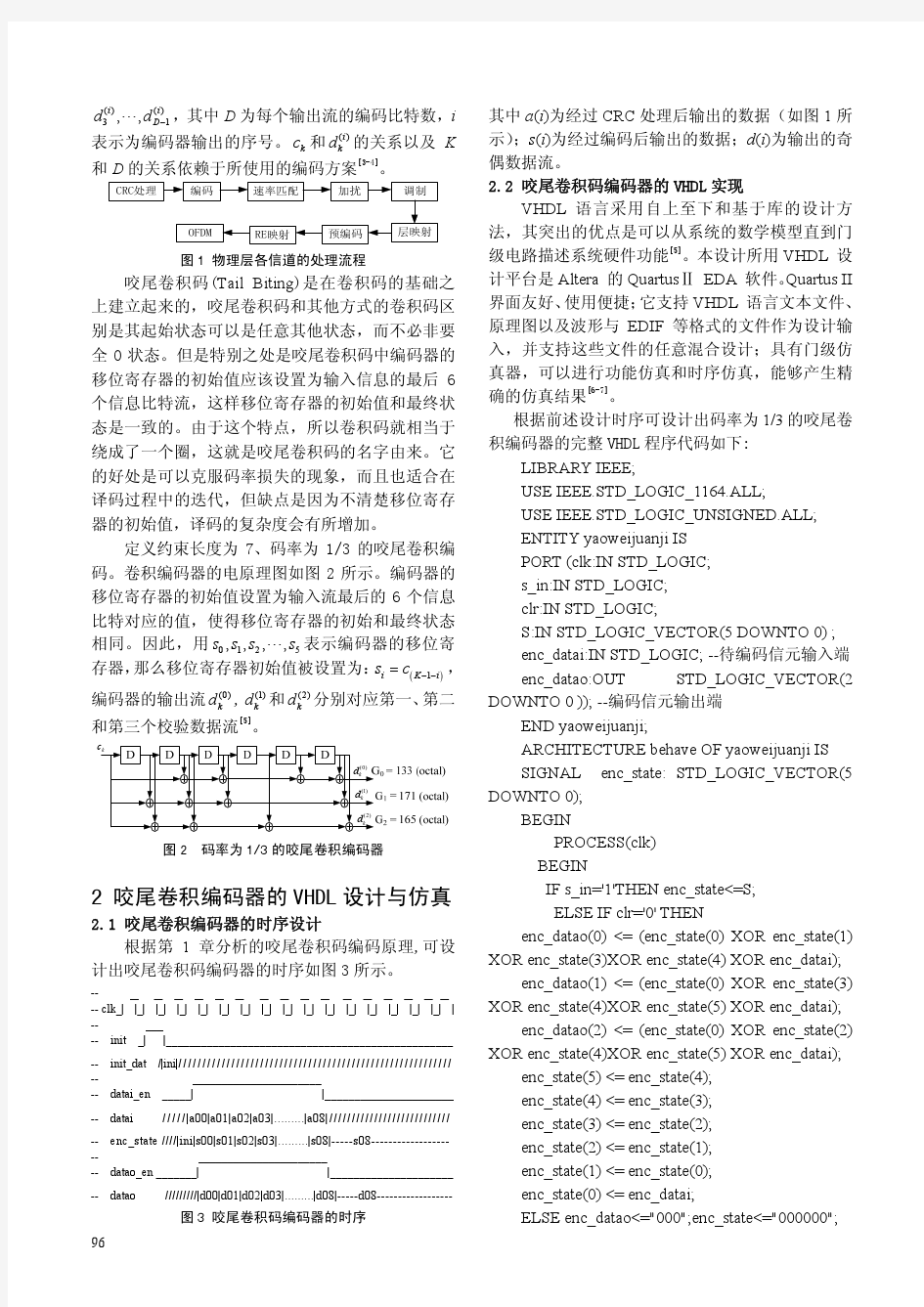

卷积码编码器的设计 (1)剖析

卷积码的设计与实现

213卷积码编码和译码

基于MATLAB的卷积码的分析与应用

实验九 (2,1,5)卷积码编码译码技术

14卷积码编解码

毕业设计61基于System View的卷积码译码器的设计

卷积码

卷积码的编解码仿真与研究

MATLAB实现卷积码编译码-

卷积码编译码课设 (2)

基于matlab的卷积码译码器的仿真设计