Document Title

A7105数据文件,2.4GHz FSK/GFSK 收发器2K~500 Kbps 传输能力

Revision History

Rev. No.

History

Issue Date

Remark

0.0Initial issue.

Dec 27th

,2007

Preliminary 0.1Modified specification and add section for TX power setting

Feb 20th ,2008Preliminary

0.2Add top marking info.,reflow profile ,Carry tape & reel

dimensions Oct. 9 th ,2008Preliminary 0.3

Modify description of state machine and FIFO mode

Rename IRQS1/IRQS2 to GIO1S/GIO2S Rename GPIO1/GPIO2 to GIO1/GIO2

Add Easy FIFO mode ,Segment FIFO mode

Delete thermal sensor function / external voltage measurement Delete TWWS function

Add State diagram of quick/normal/power saving FIFO mode Add State diagram of Direct mode Rename Master Clock F CSCK to F MCLK

Modify data rate support from 1K~500K to 2K ~ 500K

Jan. 7th ,2009

Preliminary 1.0

Revise description of state machine and FIFO mode Remove un-necessary components of application circuit Add RSSI curve Add layout guidance

August ,2009

Full Production

1.1

Revise min. operation voltage from 1.9V to 2.0V

Revise typical TX current (0dBm) from 19mA to 20mA

Feb.,2010

Full Production

1.2

Add note 9 in chapter 8, specification.

Fix typo in below pages (51, 52, 57, 62, 66, 78, 79).

Nov.,2010Full Production 1.3

Change English Company Name

Nov. 30, 2010Full Production 1.4

Revise pin description of VDA1, VDA2, VDA3 in Ch5.

Jan., 2011Full Production 1.5

Update block diagram and Ch19.Correct typo of Ch9, 18h.

Feb., 2012

Full Production

Important Notice :

AMICCOM reserves the right to make changes to its products or to discontinue any integrated circuit product or service without notice. AMICCOM integrated circuit products are not designed ,intended ,authorized ,or warranted to be suitable for use in life-support applications ,devices or systems or other critical applications. Use of AMICCOM products in such applications is understood to be fully at the risk of the customer.

A M

I C

C

O M

C

O

N

F I

D E N T I

A

L

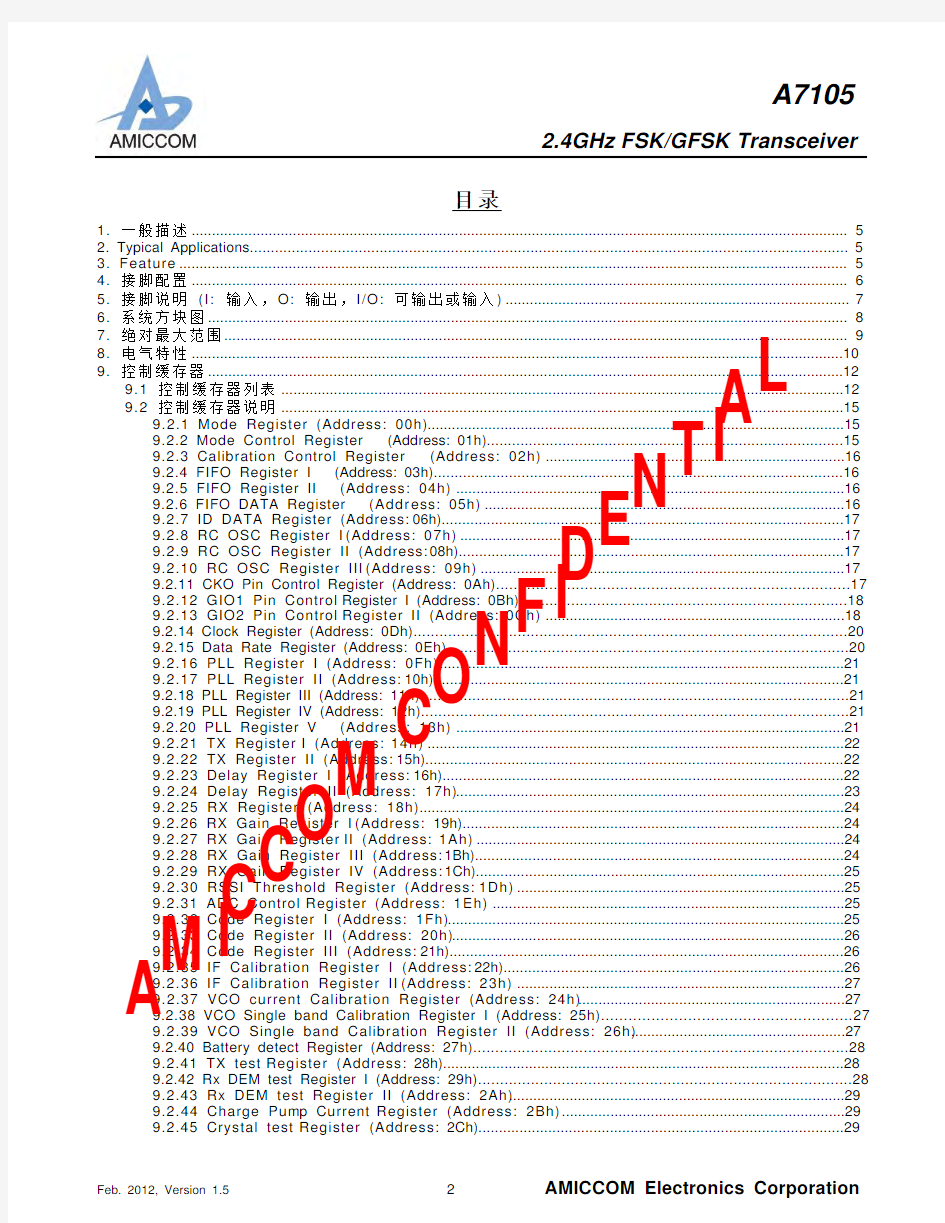

目录

1.一般描述..................................................................................................................................................................52. Typical Applications...............................................................................................................................................53. Feature .....................................................................................................................................................................54.接脚配置..................................................................................................................................................................65.接脚说明 (I:输入,O:输出,I/O:可输出或输入).....................................................................................76.系统方块图..............................................................................................................................................................87.绝对最大范围..........................................................................................................................................................98.电气特性.................................................................................................................................................................109.控制缓存器. (12)

9.1控制缓存器列表...........................................................................................................................................129.2控制缓存器说明. (15)

9.2.1 Mode Register (Address: 00h).......................................................................................................159.2.2 Mode Control Register (Address: 01h).....................................................................................159.2.3 Calibration Control Register (Address: 02h)..........................................................................169.2.4 FIFO Register I (Address: 03h)..................................................................................................169.2.5 FIFO Register II (Address: 04h)................................................................................................169.2.6 FIFO DATA Register (Addr ess: 05h).........................................................................................169.2.7 ID DATA Register (Address: 06h)..................................................................................................179.2.8 RC OSC Register I (Address: 07h)...............................................................................................179.2.9 RC OSC Register II (Address: 08h)..............................................................................................179.2.10 RC OSC Register III (Address: 09h)..........................................................................................179.2.11 CKO Pin Control Register (Address: 0Ah)................................................................................179.2.12 GIO1 Pin Control Register I (Address: 0Bh)............................................................................189.2.13 GIO2 Pin Control Register II (Address: 0Ch)..........................................................................189.2.14 Clock Register (Address: 0Dh)....................................................................................................209.2.15 Data Rate Register (Address: 0Eh)............................................................................................209.2.16 PLL Register I (Address: 0Fh).....................................................................................................219.2.17 PLL Register II (Address: 10h)....................................................................................................219.2.18 PLL Register III (Address: 11h)...................................................................................................219.2.19 PLL Register IV (Address: 12h)...................................................................................................219.2.20 PLL Register V (Address: 13h)................................................................................................219.2.21 TX Register I (Address: 14h).......................................................................................................229.2.22 TX Register II (Address: 15h)......................................................................................................229.2.23 Delay Register I (Address: 16h)..................................................................................................229.2.24 Delay Register II (Address: 17h)................................................................................................239.2.25 RX Register (Address: 18h).........................................................................................................249.2.26 RX Gain Register I (Address: 19h).............................................................................................249.2.27 RX Gain Register II (Address: 1Ah)...........................................................................................249.2.28 RX Gain Register III (Address: 1Bh)..........................................................................................249.2.29 RX Gain Register IV (Address: 1Ch)..........................................................................................259.2.30 RSSI Threshold Register (Address: 1Dh).................................................................................259.2.31 ADC Control Register (Address: 1Eh).......................................................................................259.2.32 Code Register I (Address: 1Fh)..................................................................................................259.2.33 Code Register II (Address: 20h).................................................................................................269.2.34 Code Register III (Address: 21h)................................................................................................269.2.35 IF Calibration Register I (Address: 22h)...................................................................................269.2.36 IF Calibration Register II (Address: 23h).................................................................................279.2.37 VCO current Calibration Register (Address: 24h)..................................................................279.2.38 VCO Single band Calibration Register I (Address: 25h).......................................................279.2.39 VCO Single band Calibration Register II (Address: 26h).....................................................279.2.40 Battery detect Register (Address: 27h).....................................................................................289.2.41 TX test Register (Address: 28h)..................................................................................................289.2.42 Rx DEM test Register I (Address: 29h).....................................................................................289.2.43 Rx DEM test Register II (Address: 2Ah)...................................................................................299.2.44 Charge Pum p Current Register (Address: 2Bh)......................................................................299.2.45 Crystal test Register (Address: 2Ch).. (29)

A M

I C

C

O M

C

O

N

F I

D E N T I

A

L

9.2.46 PLL test Register (Address: 2Dh) (29)

9.2.47 VCO test Register I (Address: 2Eh)...........................................................................................309.2.48 VCO test Register II (Address: 2Fh)..........................................................................................309.2.49 IFAT Register (Address: 30h).......................................................................................................309.2.50 RScale Register (Address: 31h)..................................................................................................309.2.51 Filter test Register (Address: 32h) (30)

10. SPI 界面 (31)

10.1 SPI Form at ..................................................................................................................................................3210.2 SPI 时序特性..............................................................................................................................................3210.3 SPI 时序图.. (33)

10.3.1 3线式 SPI 时序图......................................................................................................................3310.3.2 4线式SPI 时序图.......................................................................................................................3310.4 Strobe Comm ands . (34)

10.4.1 Strobe Command - Sleep Mod e...................................................................................................3410.4.2 Strobe Command - ldle Mode.......................................................................................................3410.4.3 Strobe Command - Standby Mode...............................................................................................3510.4.4 Strobe Command - PLL Mode.......................................................................................................3510.4.5 Strobe Command - RX Mode ........................................................................................................3610.4.6 Strobe Command - TX Mode.........................................................................................................3610.4.7 Strobe Command – FIFO Write Pointer Reset .........................................................................3710.4.8 Strobe Command – FIFO Read Pointer Reset .........................................................................3710.5 Reset Comm and.........................................................................................................................................3710.6 ID Accessing Command (38)

10.6.1 ID Write Comm and..........................................................................................................................3810.6.2 ID Read Command ..........................................................................................................................3810.7 FIFO Accessing Command . (39)

10.7.1 TX FIFO Write Comm and...............................................................................................................3910.7.2 Rx FIFO Read Command (39)

11.状态机 (41)

11.1主要的状态 (41)

11.1.1 Standby mode...................................................................................................................................4111.1.2 Sleep m ode .......................................................................................................................................4211.1.3 ldle m ode...........................................................................................................................................4211.1.4 PLL m ode...........................................................................................................................................4211.1.5 TX m ode.............................................................................................................................................4211.1.6 RX mode ............................................................................................................................................4311.1.7 CAL mode ..........................................................................................................................................4311.2 Norm al FIFO Mode ....................................................................................................................................4411.3 Quick FIFO Mode .......................................................................................................................................4611.4 Power Saving FIFO Mode ........................................................................................................................4811.5 Quick Direct Mode .....................................................................................................................................5012 Crystal Oscillator . (53)

12.1 Use Ext ernal Crystal.................................................................................................................................5312.2 Use ext ernal clock.....................................................................................................................................5313.系统频率 (54)

13.1不使用频率产生器的方法........................................................................................................................5513.2启动频率产生器的方法.............................................................................................................................5614.收发器 LO 频率 (58)

14.1 LO 频率设定...............................................................................................................................................5914.2 IF Side Band Select . (61)

14.2.1 Auto IF Exchange ............................................................................................................................6214.2.2 Fast Exchange .................................................................................................................................6314.3 Frequency Com pensation........................................................................................................................6415.校正.. (65)

15.1校正流程......................................................................................................................................................6515.2 IF Filter Bank 校正...................................................................................................................................6515.3 VCO Curr ent 校正. (65)

A M

I C

C

O M

C

O

N

F I

D E N T I

A

L

15.4 VCO Bank 校正..........................................................................................................................................6616. FIFO (First In First Out) (67)

16.1封包格式......................................................................................................................................................6716.2位串流流程(Bit Stream Process)...........................................................................................................6816.3传输时间......................................................................................................................................................6916.4 Usage of TX and RX FIFO.. (70)

16.4.1 Easy FIFO .........................................................................................................................................7116.4.2 Segm ent FIFO ..................................................................................................................................7216.4.3 FIFO Extension .. (74)

17. ADC (Analog to Digital Converter) (78)

17.1 RSSI 量测...................................................................................................................................................7817.2载波侦测(Carrier Detect)........................................................................................................................8018. Battery Detect......................................................................................................................................................8219 TX power setting ..................................................................................................................................................8320. Application circuit...............................................................................................................................................8421.缩写.......................................................................................................................................................................8622.订单(料号)信息...................................................................................................................................................8623.封装信息...............................................................................................................................................................8724.正印信息...............................................................................................................................................................8825. Refl ow 温度曲线.................................................................................................................................................8926.卷带规格...............................................................................................................................................................9027. Product Status.. (91)

A M

I C

C

O M

C

O

N

F I

D E N T I

A

L

1.一般描述

A7105是一颗低成本且高效能的收发器并适用于2.4GHz ISM 频段的无线应用。A7105内整合高感度的接收器(-95dbm @ 500Kbps)及高效率的功率放大器(最大1dBm )。当使用低传输率时,由于A7105内建极高的灵敏度的接收器(-107 dBm @ 2Kbps ,- 104 dBm @ 25Kbps),外部不需额外的LNA 或PA 就可有极优异的无线可视距离。使用者可藉由Data Rate 缓存器(0x0E)调整传输率(2kbps ~ 500kbps)。A7105采取快速变频设计(130 us @ settling tim e),相当适合跳频的系统。A7105内建 64-bytes 的

TX-FI FO 与RX-FIFO(经由设定,亦可以括展至256 bytes),对于开发者而言,接收与传送都有data buffer ,封包容易处理。A7105针对封包处理亦支持CRC ,FEC ,RSSI 与Data W hitening 。CRC 可以用于错误侦测,FEC 可针对每个code word 实现1-bi t 的错误更正,Data W hitening 相当于数据加解密。RSSI 用于通道干净指针(Cl ear channel assessm ent )。当开发一个无线系统时,这些功能非常便利使用。所有功能整合在一个QFN 4x4 20封装内。

A7105的所有缓存器可经由3线式或4线式的SPI 读写。在省电模式下,A7105支持sl eep m ode ,idle mode ,standby m ode 。A7105有一组独特的SPI 指令集用来控制芯片工作模式,这组命令称为Storbe comm and 。经由Str obe comm and ,MCU 可以控制A7105所有的功能,包含省电模式,数据传输与接收,信道监视,跳频功能,与自动校正。此外,A7105支持GIO1与GIO2用来通知MCU 目前芯片状态,因此MCU 可用使用轮询或中断的模式来控制发射与接收。因为GIO1与GIO2的数字接口,MCU 可以非常的便利监看A7105无线传输状态。

2. Typical Applications

n 无线键盘鼠标

n 2.4GHz RF 摇控器

n 无线直升机与飞机控制器

n 2400 ~ 2483.5 MHz ISM 系统n 无线表头与大楼自动化n 无线玩具跟游戏控制器

3. Feature

n 小封装 (QFN4 X4,20 pins)n 频率范围2400 ~ 2483.5MHz n FSK or GFSK 调变

n 低消耗电流: RX 16m A ,TX 20mA (at 0dBm 输出功率).n 低休眠电流 (1.5 uA)

n 内建稳压器,支持输入电压2.0 ~ 3.6 V n 可程序化数据传输速率:2Kbps ~ 500Kbps n 可程序化发射功率: – 20 dBm to 1 dBm n

高接收敏感度:u -95dBm at 500Kbps u -97dBm at 250Kbps u -104dBm at 25Kbps u -107dBm at 2Kbps

n 快速稳态时间(130 us)适合跳频系统n 内建电池侦测

n 支援多样石英振荡器 ( 8 /12 / 16 / 20 / 24MHz)n 可输出频率至MCU (1 / 2 / 4 / 8MHz)n 支持频率补偿n

使用便利u 支援3线式或4线式 SPI.u 独特SPI Str obe comm and 指令集u 改变一个缓存器设定就可换频

u 8-bi ts 数字 RSSI 用于信道干净指针

A M

I C

C

O M

C

O

N

F I

D E N T I

A

L

u 快速TX /RX 切换模式

u 自动RSSI 量测u 自动校正u 自动 IF function u 自动CRC 检查u 自动 FEC (7,4) Hamm ing code (每一个code word 有1 bit 错误更正)u Data W hitening 用于资料加密与解密u TX 跟RX 各有64 bytes FIFO u 一般 FIFO /区段 FIFO / FIFO 延展(最大256 bytes)u 在Direct 模式,支持recov ery 频率输出u 在FIFO 模式,支持fram e sync 讯号

4.接脚配置

DVDD SDIO SCS

BPBG RFI RSSI RFO VDA2

G I O 1

G I O 2

C K O

V T

G N D

V D A 3

X I

X O

SCK GND R E G I

V D A 1

Fig 4.1 A7105 QFN 包装上视图

A M

I C

C

E N T I

A

L

5.接脚说明 (I:输入,O:输出,I/O:可输出或输入)

Pin No.

Sym bol I/O Function Descri ption

1RSSI O 当要读取RSSI 时建议连接旁路电容2BPBG O 当要使用内建稳压器时建议连接旁路电容

3RFI I Low noise am plifier 输入

4RFO O Power am plifier 输出

5VDA2I/O RX/TX 部份电源(从内部LDO),连接电容到地

6VT I VCO 频率控制输入,连接至内部PLL charge pump

7GND G 接地8XI I 石英震荡输入9XO O 石英震荡输出

10VDA3I PLL 部份使用电源(从 VDA1,脚位 20)

11SCS I 3线SPI 芯片选择

12SCK I 3线SPI 频率输入脚位元

13DVDD I 数字部位的电源建议连接旁路电容

14SDIO I/O 3线 SPI 读/写资料脚位元

15GND G 接地

16GIO1I/O 多功能 GIO1或 4-wire SPI data output.17GIO2I/O 多功能GIO2或 4线式 SPI data output.

18CKO O 多功能频率输出.

19REGI I 内部稳压器输入(外部电源输入)

20

VDA1I/O 内部稳压器输出,用来供电VDA3 (脚位10)与 RFO (脚位4).

Back side

plate

G

接地

IC 背面应该妥善接地,否则会影响RF 效能.

A M

I C

C

O M

C

O

N

F I

D E N T I

A

L

6.系统方块图

SDIO

BPBG

RFI

RFO

VDA2

G I O 1

R E G I

V T

G N D

X O

GND

V D A 3

SCS

DVDD C K O

V D A 1

RSSI

G I O 2

SCK X I

Fig 6.1系统方块图

A M

I

7.绝对最大范围

Param eter

Wit h r espect to

Rati ng Unit 供应电源范围 (VDD)GND -0.3 ~ 3.6

V 数字 IO 接脚的电压范围GND -0.3 ~ VDD+0.3

V

模拟脚位元的电压范围GDN

-0.3 ~ 2.1V 输入RF 准位5

dBm 储存温度范围-55 ~ 125°C HBM ± 2K V ESD Rati ng

MM

± 100

V

*Stresses above thos e listed under “Absolute Maxim um Rating” m ay cause perm anent dam age to the devi ce. Thes e are stress r ati ngs only; functional operat ion of the devi ce at these or any other condi ti ons above those indi cated i n the op erat ional sections of this speci fi cati on is not im plied.Exposur e to absol ute-m aximum -rated conditi ons for ext end ed peri ods m ay affect devi ce reli ability.*Device is ESD sensitive. Use appropriate ESD precautions. HBM (Hum an Body Mode) is tested under MIL-STD-883F Method 3015.7. MM (Machine Mode) is tested under JEDEC EIA/JESD22-A115-A.

*Device is Moisture Sensitivity Level III (MSL 3).

A M

I C

C

O M

C

O

N

F I

D E N T I

A

L

8.电气特性

(Ta=25℃,VDD=3.0V ,data rate= 500Kbps ,IF bandwidth = 500KHz ,F XTAL =16MHz ,with Match Networking and low pass filter ,On Chip Regulator = 2.1V ,unless otherwise noted.)

Parameter

Description Min.

Type Max.Unit

General

Operating Temperature -40

85°C Supply Voltage (VDD)with internal regulator 2.0

3.6

V Sleep mode (RC OSC off) 1.5*1m A Idle Mode (Regulator on)0.3*1

mA Standby Mode

(XOSC on ,clock generator on) 1.9

mA PLL mode 9mA RX Mode

16mA TX Mode (@0dBm output)20mA TX Mode (@-3dBm output)16mA TX Mode (@-6dBm output)14.5mA TX Mode (@-11dBm output)13.9mA Current Consumption

TX Mode (@-20dBm output)

12.5mA PLL block

Crystal start up time *2

0.6

ms Crystal frequency 8,12,16,20,24

MHz without FW FC ±10ppm Crystal tolerance

with FW FC

±20

ppm Crystal ESR

80ohm VCO Operation Frequency 2400

2483.5

MHz PLL phase noise

Offset 10k Offset 100K Offset 1M

808590dBc

PLL settling time *

3

@Loop BW = 500Khz

70m S Transmitter

Output power range

-20

dBm 30MHz~1GHz -36dBm 1GHz~12.75GHz -30dBm 1.8GHz~ 1.9GHz -47dBm Out Band Spurious Emission *

4

5.15GHz~ 5.3GHz

-47

dBm Data rate > 50Kbps 186K Hz Frequency deviation *

5

Date rate <=50Kbps

124K

Hz Data rate

2K

500K

Bps @Loop BW = 500 KHz ,

LO fixed 10+60m S TX ready time *

6

(PLL to WPLL + WPLL to TX)

@Loop BW = 500 KHz ,

Hopping

70+60m S

Receiver

Data rate 500K (F IF = 500KHz)-95dBm Receiver sensitivity @ BER = 0.1%

Data rate 250K (F IF = 500KHz)

-97

dBm

A M

I C

C

O M

C

O

N

F I

D E N T I

A

L

Data rate 25K (F IF = 500KHz)

-104dBm Data rate 2K (F IF = 500KHz)

-107dBm IF frequency bandwidth 250/500KHz IF center frequency 250/500KHz Co-Channel (C/I 0)11dB ±1MHz Adjacent Channel - 20dB

±2MHz Adjacent Channel - 30dB >±5MHz Adjacent Channel

- 40dB Interference *

7

Image (C/I IM )

- 12

dB Maximum Operating Input Power

@RF input (BER=0.1%)

0dBm Spurious Emission *4

30MHz~1GHz

-57dBm 1GHz~12.75GHz -47RSSI Range

@RF input

-105

-50dBm Data rate < = 125 Kbps

10+40m s Data rate = 250 Kbps

10+100m s LO fixed Data rate = 500 Kbps

10+60m s Data rate < = 125 Kbps

70+40m s Data rate = 250 Kbps

70+100

m s RX Ready Time *

8

(PLL to WPLL + WPLL to RX)

Hopping Data rate = 500 Kbps

70+60m s RX Spurious Emission above 1GHz

-47dBm Regulator

Regulator settling time Pin 2 connected to 1.5 nF

500*9

m s Band-gap reference voltage 1.23V Regulator output voltage 1.8 2.1 2.3V Line regulation

Load current 30mA

3540

dBc Digital IO DC characteristics

High Level Input Voltage (V IH )0.8*VDD

VDD V Low Level Input Voltage (V IL )00.2*VDD V High Level Output Voltage (V OH )@I OH = -0.5mA VDD-0.4

VDD V Low Level Output Voltage (V OL )

@I OL = 0.5mA

0.4

V

Note 1: When digital I/O pins are configured as input ,those pins shall NOT be floating but pull either high or low (SCS shall be pulled high only); otherwise ,leakage current will be induced.Note 2:参考 Delay Register II (17h) to set up crystal settling delay.Note 3:参考 Delay Register I (17h) to set up PDL (PLL settling delay).

Note 4: With external RF filter that provides minimum 17dB of attenuation in the band: 30MHz ~ 2GHz and 3GHz ~12.75GHz.Note 5:参考TX Register II (15h) to set up FD [4:0].

Note 6:参考 Delay Register I (17h) to set up PDL and TDL delay.

Note 7: The power level of wanted signal is set at sensitivity level +3dB. The modulation data for wanted signal and interferer are PN9 and PN15,respectively. Channel spacing is 500KHz.

Note 8: For 250K/500Kbps ,set DCM[1:0]= [10b] by ID ,(29h). For <= 125Kbps ,set DCM[1:0]= [01b] by Preamble ,(29h).Note 9: When VDD < 2.1V and temperature < -30 degree C, the regulator settling time will arise up to 20ms .

A M

I C

C

O M

C

O

N

F I

D E N T I

A

L

9.控制缓存器

A7105共有51个 8-bi ts 的控制缓存器。MCU 可以使用3线式SPI (SCS ,SCK ,SDIO)或4线式SPI (SCS ,SCK ,SDIO ,GIO1/GIO2)来读写这些缓存器. A7105 SPI 的传输速度最快可至10 Mbp s 。关于更多的SPI 的数据可参考第十章。

9.1控制缓存器列表

Address /Nam e R/W

B it 7B it 6B it 5B it 4B it 3B it 2B it 1B it 0W R E S E T N

R E S E T N R E S E T N R E S E T N R E S E T N R E S E T N R E S E T N R E S E T N 00h Mode R --FE C F C R C F C E R X E R P L L E R T R S R T R E R W D D P C A R S S I AIF D F C D W W S E FMT FM S A D C M 01h

Mode control

R D D P C

A R S S I

AIF

C D

W W S E

FMT FM S A D C M 02h Calc R /W ----------

V C C

V B C FBC 03h FIFO I W FE P 7FE P 6FE P 5FE P 4FE P 3

FE P 2

FE P 1FE P 004h FIFO II W FP M 1FP M 0P S A 5P S A 4P S A 3

P S A 2

P S A 1P S A 005h FIFO Data

R /W F IF O 7F IF O 6F IF O 5F IF O 4F IF O 3F IF O 2F IF O 1F IF O 006h ID Data

R /W

I D 7

I D 6

I D 5

I D 4

I D 3

I D 2

I D 1I D 0

W

W W S _S L 7W W S _S L 6W W S _S L 5W W S _S L 4W W S _S L 3W W S _S L 2W W S _S L 1W W S _S L

007h RC OSC I

R ----R C O C 5R C O C 4R C O C 3R C O C 2R C O C 1R C O C 0

08h RC OSC II

W W W S _S L 9W W S _S L 8W W S _A C 5W W S _A C 4W W S _A C 3W W S _A C 2W W S _A C 1W W S _A C

009h

RC OSC III

W B B C K S 1B B C K S 0------R C O S C _

E T S E L T W W S _E 0Ah CKO Pin W E C K O E

C K O S 3

C K O S 2C K O S 1C K O S 0C K O I C K O E

S C K I

0Bh

GPIO1 Pin I

W ----G IO 1S 3G IO 1S 2G IO 1S 1G IO 1S 0G IO 1I G IO 1O E 0Ch

GPIO2 Pin II

W

----G IO 2S 3G IO 2S 2G IO 2S 1G IO 2S 0G IO 2I G IO 2O E

0Dh Clock R /W

G R C 3G R C 2G R C 1G R C 0C S C 1C S C 0C G S X S 0Eh Data rate

R /W

S D R 7S D R 6S D R 5S D R 4S D R 3S D R 2S D R 1S D R 00Fh PLL I R /W

C H N 7C H N 6C H N 5C H N 4C H N 3C H N 2C H N 1C H N 010h PLL II R /W

D B L R R C 1R R C 0C H R 3C H R 2C H R 1C H R 0IP 811h PLL III R /W IP 7IP 6IP 5IP 4IP 3IP 2IP 1IP 0W FP 15FP 14FP 13FP 12

FP 11FP 10FP 9FP 812h PLL IV R --A C 14A C 13A C 12A C 11A C 10A C 9A C 8W FP 7FP 6FP 5FP 4FP 3FP 2FP 1FP 013h PLL V R A C 7

A C 6A C 5A C 4A C 3A C 2A C 1A C 014h TX I W T XS M 1

T XS M 0T XD I T ME FS FD P 2FD P 1FD P 015h TX II W --P D V 1P D V 0F D 4F D 3F D 2F D 1F D 016h Delay I

W

D P R 2

D P R 1

D P R 0

T D L1

T D L0

P D L 2

P D L 1

P D L 0

A M

I C

C

O M

C

O

N

F I

D E N T I

A

L

17h

Delay II W

W S E L 2

W S E L 1W S E L 0A G C _D 1

A G C _D 0R S _D L Y 2R S _D L Y 1R S _D L Y 018h

RX W

--R XS M 1

R XS M 0FC R XD I D MG BW S U LS 19h

RX Gain I

R /W

MV G S --IG C MG C 1MG C 0LG C 2LG C 1LG C 01Ah

RX Gain II

W

R H 7R H 6R H 5R H 4R H 3R H 2R H 1R H 01Bh

RX Gain III

W

R L 7R L 6R L 5R L 4R L 3R L 2R L 1

R L 0

1Ch

RX Gain IV

W

E N G C ------MH C LH C 1LH C 0V G C E W R T H 7R T H 6R T H 5R T H 4R T H 3

R T H 2

R T H 1R T H 01Dh

RSSI

Threshol d

R

A D C 7A D C 6A D C 5A D C 4

A D C 3A D C 2A D C 1A D C 01Eh

ADC W

R S M1R S M0E R S S F SA R S --X A D S R S S C D M 1Fh

Code I W

--MC S W HT S FE C S C R C S I D L

P M L 1P M L 020h

Code II W

--D C L 2D C L 1D C L 0E T H 1E T H 0P M D 1P M D 021h

Code III

W

--W S 6W S 5W S 4

W S 3

W S 2

W S 1W S 0W ------M F B S MF B 3MF B 2MF B 1MF B 022h

IF Calibration I R

------FB C F FB 3FB 2FB 1FB 023h

IF Calibr ation

II R ------FC D 4

FC D 3FC D 2FC D 1FC D 0W ----V C C S MV C S V C O C 3V C O C 2V C O C 1V C O C 024h VCO current

Cali bration

R

------F VC C V C B 3V C B 2V C B 1V C B 0W ------

--M V B S M V B 2M V B 1M V B 025h VCO Single

band Cali bration I

R ----D V T 1

D V T 0

V B C F

V B 2

V B 1V B 0

26h

VCO Single

band

Cali bration II W

----V T H 2V T H 1

V T H 0

VT L2

VT L1VT L0

W R G S R G V 1R G V 0--B V T 2B V T 1B V T 0B D S 27h

Battery detect

R

R G S R G V 1R G V 0B D F B V T 2B V T 1B V T 0B D S 28h TX test W

----T XC S P A C 1P A C 0T B G 2T B G 1T B G 029h

Rx DEM test I

W D MT D C M 1D C M 0M LP 1M LP 0SL F2SL F1SL F02Ah

Rx DEM test II

W D C V 7D C V 6D C V 5D C V 4D C V 3D C V 2D C V 1D C V 02Bh CPC W ------------C P C 1C P C 02Ch

Crystal test

W --------D B D X C C X C P 1X C P 02Dh PLL test W --P M P E P R R C 1

P R R C 0P R IC 1P R IC 0S D P W N S D O 2Eh VCO test I

W ------T LB T LB R LB R LB V C B S 2Fh VCO test II

W --------R FT 3R FT 2R FT 1R FT 030h IFAT

W

IG FI 2

IG FI 1

IG FI 0

IG FQ 2

IG FQ 1

IG FQ 0

IFB C

LI MC

A M

I C

C

O M

C

O

N

F I

D E N T I

A

L

31h

RScale R /W

R S C 7R S C 6R S C 5R S C 4R S C 3R S C 2R S C 1R S C 032h

Filter test

W

FT 7FT 6

FT 5

FT 4

FT 3

FT 2

FT 1

FT 0

Legend: -- = unimplemented

A M

I C

C

O M

C

O

N

F I

D E N T I

A

L

9.2控制缓存器说明

9.2.1 Mode Register (Address: 00h)

Nam e R/W

Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0

R

--FECF CRCF CER XER PLLER TRSR TRER

Mode W

RESETN RESETN RESETN RESETN RESETN RESETN RESETN RESETN

Res et

----------------

RESETN:写入0x00就可以将IC 重置

FECF: FEC 旗标.

[0]:FEC 正确.[1]: FEC 错误. (FECF 对外是只读的,每当收到一个封包就会更新)

CRCF: CRC flag.

[0]:CRC 正确. [1]:CRC 错误. (CRCF 对外是只读的,每当收到一个封包就会更新)CER: RF chip enable status.

[0]: RF chip 已关闭.[1]: RF chip 已启动.

XER: I nternal crystal oscil lator enabled status.

[0]: Crystal oscillator 已关闭.[1]:Cryst al oscill ator 已启动.

PLLE: PLL enabled status.

[0]:PLL 已关闭.[1]: PLL 已启动.

TRER: TRX state enabled status.[0]:TRX 已关闭.[1]: TRX 已启动.

TRSR: TRX Stat us Register.[0]:RX 状态.[1]:TX 状态.

当TRER 是1时,是可读的 (TRX 已启动)

9.2.2 Mode Control Register (Address: 01h)

Nam e R/W Bit 7

Bit 6

Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0R DDPC ARSSI AIF DFCD WW SE FMT FMS ADCM Mode Control I

W

DDPC ARSSI AIF CD WW SE

FMT FMS ADCM Res et

DDPC (Di rect m ode data pin contr ol):使用Direct mode 时,若DDPC 设定为1,则MCU 必须选用SDIO 脚位来传送/接收收原始封包数据,并非使用GIO1或GIO2。[0]:关闭.[1]:启动.

ARSSI: (Auto RSSI measurem ent while entering RX m ode)当设定成RX m ode ,会自动量测RSSI.[0]:关闭.[1]:启动.

AIF (Auto IF Offset):当设定成RX m ode ,RF LO 频率会自动偏移一个IF 频率.[0]:关闭.[1]:启动.

CD / DFCD: DFCD (Data Fil ter by CD):当CD 是没有作用时,以接收的数据会被过滤The received packet will be filtered out if CD is inactive.[0]:关闭.[1]:启动.

CD (Read only): Carrier detector signal.

[0]: Input power below thr eshol d.[1]: Input power above thr eshol d.WWSE:保留内部使用.需设定为0.

A M

I C

C

O M

C

O

N

F I

D E N T I

A

L

FM T:保留内部使用.需设定为0.FM S: Direct/FIFO 模式设定.

[0]: Dir ect 模式.[1]: FIFO 模式.

ADCM : ADC 量测启动 (当完成时会自动清除).[0]:关闭量测或量测已完成.[1]:启动量测.ADCM A7105 @ Standby m ode A7105 @ RX m ode

[0]关闭ADC 关闭ADC

[1]没作用

量测RSSI ,carrier detect

第17章有更详细的说明.

9.2.3 Calibration Control Register (Address: 02h)

Nam e

R/W

Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Mode Control II R/W

----------VCC VBC FBC Res et

----------0

0VCC: VCO Current 校正功能 (当完成时会自动清除).[0]:关闭.[1]:启动.

VBC: VCO Bank 校正功能 (当完成时会自动清除).[0]:关闭.[1]:启动.

FBC: IF Filter Bank 校正功能 (当完成时会自动清除).[0]:关闭.[1]:启动.

9.2.4 FIFO Register I (Address: 03h)

Nam e R/W Bit 7

Bit 6

Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0FIFO I W

FEP7FEP6FEP5FEP4FEP3FEP2FEP1FEP0Res et

00

1

11

1

1

1FEP [7:0]: TX FIFO and Rx FIFO 结束指标.第16章有更详细的解说.

9.2.5 FIFO Register II (Address: 04h)

Nam e

R/W Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0FIFO II W

FPM1FPM0PSA5PSA4PSA3PSA2PSA1PSA0Res et

1

0FPM [1:0]: FIFO Pointer Margin PSA [5:0]: Used for Segm ent FIFO.第16章有更详细的解说.

9.2.6 FIFO DAT A Register (Address: 05h)

Nam e R/W

Bit 7

Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0FIFO DATA

R/W FIFO7

FIFO6FIFO5FIFO4FIFO3FIFO2FIFO1FIFO0Res et

FIFO [7:0]: FIFO data. TX FIFO (唯写)与 RX FIFO (只读).TX FIFO 与 RX FIFO 使用同一个地址 (05h).第16章有更详细的解说.

A M

I C

C

O M

C

O

N

F I

D E N T I

A

L

9.2.7 ID DAT A Register (Address: 06h)

Nam e R/W Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0ID DATA

R/W

ID7ID6ID5ID4ID3ID2ID1ID0Res et

ID [7:0]: ID data.

当这个地址被读取时,ID Data 是依序被读出或写入(ID Byte 0,1,2 and 3)读或写都是一致的.建议将ID Byte 0设成 5xh 或 Axh.10.6有更详细的说明.

9.2.8 RC OSC Register I (Address: 07h)

Nam e R/W Bit 7Bit 6Bit 5Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

R R C OC 5R C OC 4R C OC 3R C OC 2R C OC 1R C OC 0

RC OSC I W

W W S_SL 7W W S_SL 6W W S_SL 5W W S_SL 4W W S_SL 3W W S_SL 2W W S_SL 1W W S_SL

Res et

0000

RCOC [5:0]:保留内部使用.WWS_SL [7:0]:保留内部使用.

9.2.9 RC OSC Register II (Address: 08h)

Nam e R/W Bit 7Bit 6Bit 5

Bit 4Bit 3

Bit 2

Bit 1

Bit 0

RC OSC II W

W W S_SL 9W W S_SL 8W W S_A

C 5

W W S_A

C 4

W W S_A C 3

W W S_A

C 2

W W S_A C 1

W W S_A C 0

Res et

000000

00

WWS_AC [5:0]:保留内部使用.

WWS_SL [9:8]:保留内部使用.

9.2.10 RC OSC Register III (Address: 09h)

Nam e R/W Bit 7

Bit 6Bit 5Bit 4Bit 3Bit 2

Bit 1

Bit 0

RC OSC III W

BBCKS1BBCKS0

------RC O S C _

E

T SE L TW W S_E

Res et

--

--

--

1

1

BBCKS [1:0]:内部数字线路的频率选择.建议BBCKS 设成 [00][00]:F S Y C K / 8.[01]:F S Y C K / 16.[10]:F S Y C K / 32.[11]:F S Y C K / 64.

RCOSC_E: RC-oscillator 使用设定.保留内部使用.[0]:关闭.[1]:启动.

TSEL: Tim er select for TWWS function.保留内部使用.[0]:使用 WW S_AC.[1]:使用 WW S_SL.

TWWS_E: Enabl e TWWS funct ion.保留内部使用.[0]:关闭.[1]:启动.

9.2.11 CKO Pin Control Register (Address: 0Ah)

Nam e R/W Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0CKO Pin Control

W

ECKOE

CKOS3

CKOS2

CKOS1

CKOS0

CKOI CKOE SCKI Res et

1

1

1

1

1

A M

I C

C

O M

C

O

N

F I

D E N T I

A

L

ECKOE:外部频率输出设定CKOS [3:0]= [0100] ~ [0111].[0]:关闭.[1]:启动.

CKOS [3:0]: CKO pin output select.

[0000]:DCK (TX data clock) in TX mode ,RCK (RX recovery clock) in RX m ode.[0001]:DCK (TX data clock) in TX mode ,RCK (RX recovery clock) in RX m ode.[0010]:FPF (FI FO 指标旗标).

[0011]:EOP ,EOVBC ,EOFBC ,EOADC ,EOVCC ,OKADC (Int ernal usage only).[0100]:外部频率输出= F S Y C K .

[0101]:外部频率输出/ 2= F S Y C K / 2.[0110]:外部频率输出/ 4= F S Y C K / 4.[0111]:外部频率输出 / 8= F S Y C K / 8.[1xxx]:保留.

CKOI: CKO pin output signal invert.[0]:非反向输出.[1]:反向输出.CKOE: CKO pin Output Enable.[0]: High Z.[1]:启动.

SCKI: SPI clock input invert.[0]:非反向输入.[1]:反向输入.

9.2.12 GIO1 Pin Control Register I (Address: 0Bh)

Nam e R/W Bit 7Bit 6Bit 5

Bit 4

Bit 3

Bit 2

Bit 1Bit 0GIO1 Pin Control

I W

----GIO1S3GIO1S2GIO1S1GIO1S0

GIO1I GIO1OE

Res et

----

00

1

GIO1S [3:0]: GIO1功能选择表.GIO1S

[3:0]TX state RX state

[0000]W TR (W ait until TX or RX finished)[0001]EOAC (end of access code)

FSYNC (f ram e sync)

[0010]TMEO (TX modul ation enabl e)

CD (carrier detect)

[0011]Preamble Detect Output (PMDO)[0100](Res erved.)[0101]In phase dem odulator i nput (DMII)[0110]SDO ( 4 wires SPI data out)[0111]TRXD In/Out (Direct m ode)[1000]RXD (Direct m ode)[1001]TXD (Direct m ode)[1010]In phase dem odulator external input (EXDI0)[1011]Ext ernal FSYNC input in RX direct mode [11xx](Inhibited.)

GIO1I: GIO1 pin 输出反向设定.[0]:非反相输出.[1]:反相输出.GIO1OE: GIO1pin 输出设定.[0]: High Z.[1]:启动.

9.2.13 GIO2 Pin Control Register II (Address: 0Ch)

Nam e

R/W

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

A M

I C

C

O M

C

O

N

F I

D E N T I

A

L

GIO2 Pin Control

II W

----GIO2S3GIO2S2GIO2S1GIO2S0

GIO2I GIO2OE

Res et

----0

1

1

GIO2S [3:0]: GIO2 pin 功能选择表.GIO2S TX state RX state [0000]W TR (W ait until TX or RX finished)[0001]EOAC (end of access code)

FSYNC (f ram e sync)

[0010]TMEO (TX modul ation enabl e)

CD (carrier detect)

[0011]Preamble Detect Output (PMDO)[0100](Res erved.)[0101]Quadr ature phase d em odulator input (DMIQ)[0110]SDO (4 wires SPI data out)[0111]TRXD In/Out (Direct m ode)[1000]RXD (Direct m ode)[1001]TXD (Direct m ode)[1010]Quadr ature phase d em odulator ext ernal input

(EXDI1)

[1011]Ext ernal FSYNC input in RX direct mode [11xx](Inhibited.)

GIO2I: GIO2 pin 输出反向设定.[0]:非反相输出.[1]:反相输出.

GIO2OE: GIO2 pin 输出设定.[0]: High Z. [1]:启动.

In TX m ode

SPI

(SCS,SCK,SDIO)

T1

T2

GIO1 Pin -WTR (GIO1S[3:0]=0000)

RF Port

T3

GIO2 Pin - TMOE (GIO2S[3:0]=0010)

T0< 1us

(Output)

A O

N

F I

D E N T I

A

L

In RX m ode

SPI

(SCS,SCK,SDIO)

T1

T2

GIO1 Pin -WTR (GIO1S[3:0]=0000)

RF Port GIO2 Pin - FSYNC (GIO2S[3:0]=0001)

T0< 1us

(Input)9.2.14 Clock Register (Address: 0Dh)

Nam e

R/W

Bit 7

Bit 6Bit 5

Bit 4

Bit 3Bit 2Bit 1Bit 0Clock R/W GRC3GRC2GRC1GRC0CSC1CSC0CGS XS Res et 1

1

1

10

1

1

第14章有更详细的解说

XS: Crystal oscillator select.建议将XS 设定[1][0]:外部频率.[1]:Crystal.

CGS: Cl ock generator enable.建议将 CGS 设定 [0][0]:关闭.[1]:开启.

CGS = 0 (建议使用)

CGS = 1关闭内部32MHz PLL 频率F M C L K = 32 MHz

GRC [3:0]: Clock generation r efer ence counter.GRC[3:0]Note Don’t car e 当使用建议值,将 CGS 设定为 0F X TA L x (DBL+1) / (GRC+1)= 2M

W hen CGS = 1CSC [1:0]: system clock F S Y C K divider select.CSC [1:0]System Clock F S Y C K Note 00

F M C L K 01 (建议值)F M C L K / 210F M C L K / 211

F M C L K / 4

F S Y C K 用来侦测

1. D at a r at e (0E h)

2. AD C c l oc k (1E h)

3. In t ern al di gi t al c l oc k

(09h )

4.C KO pi n (0A h)

9.2.15 Data Rate Register (Address: 0Eh)

Nam e

R/W

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

A M

I C

C

O M

C

O

N

F I

D